A Dual Half-Bridge Converter with Adaptive Energy Storage to Achieve ZVS over Full Range of Operation Conditions

Abstract

:1. Introduction

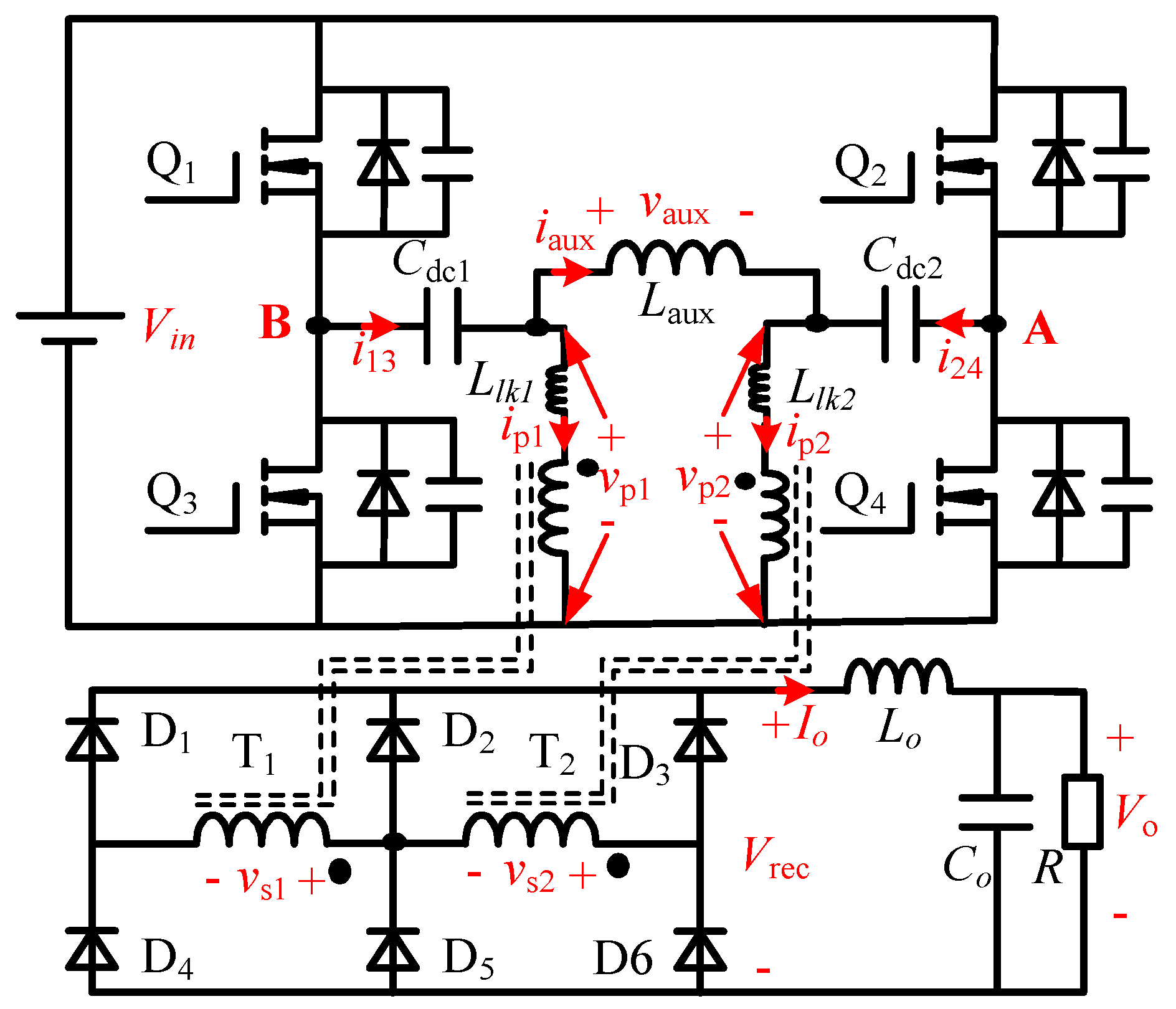

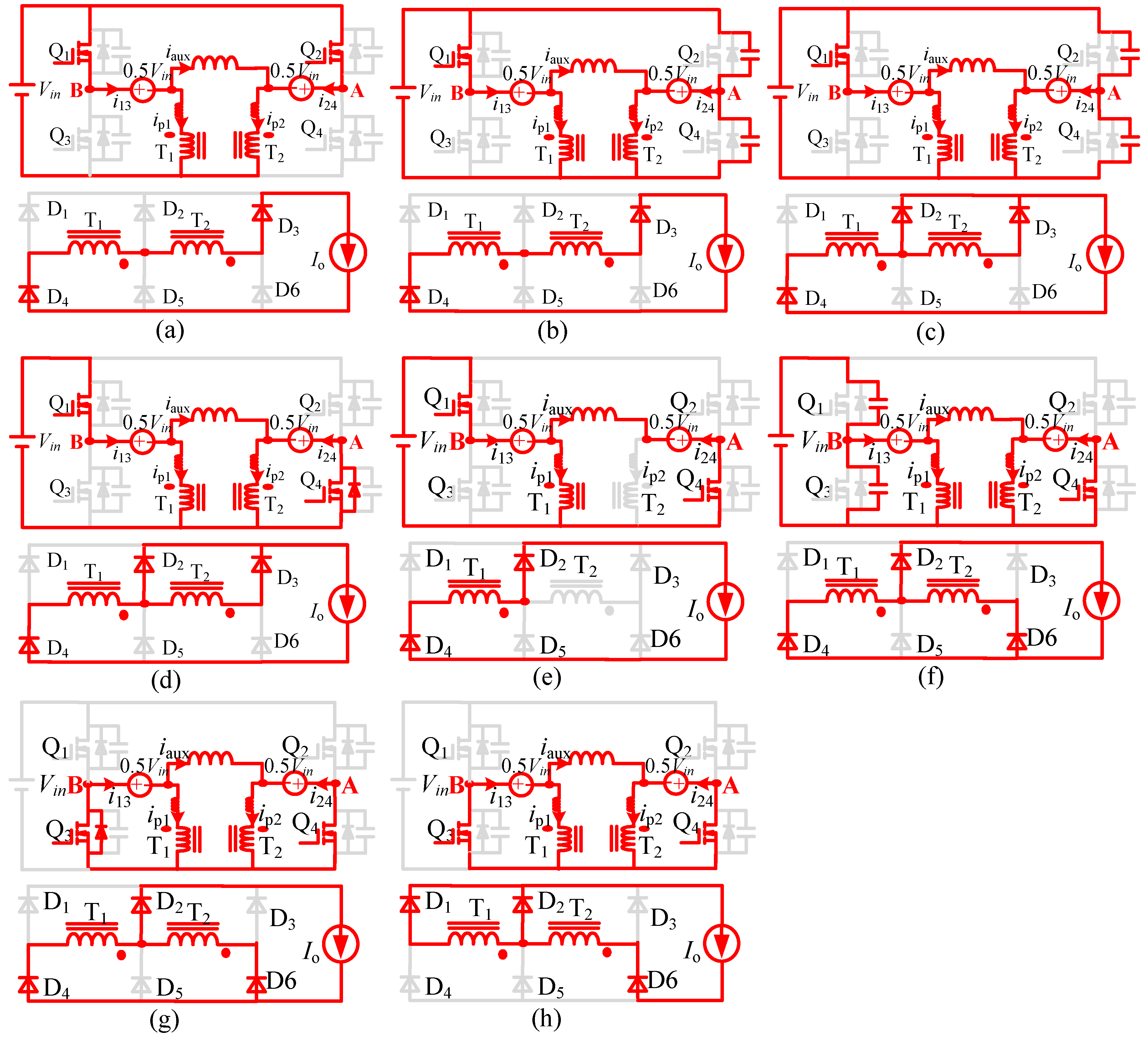

2. Operation Principle

- (1)

- The blocking capacitors Cdc1, Cdc2 are considered as two constant voltage sources of 0.5Vin.

- (2)

- All the output capacitances of MOSFETs have the same values, Coss.Llk1 and Llk2 also have the same values, Llk.

- (3)

- The output filter inductor Lo is large enough to be treated as a constant current source during a switching period.

3. Analysis of the Proposed Converter

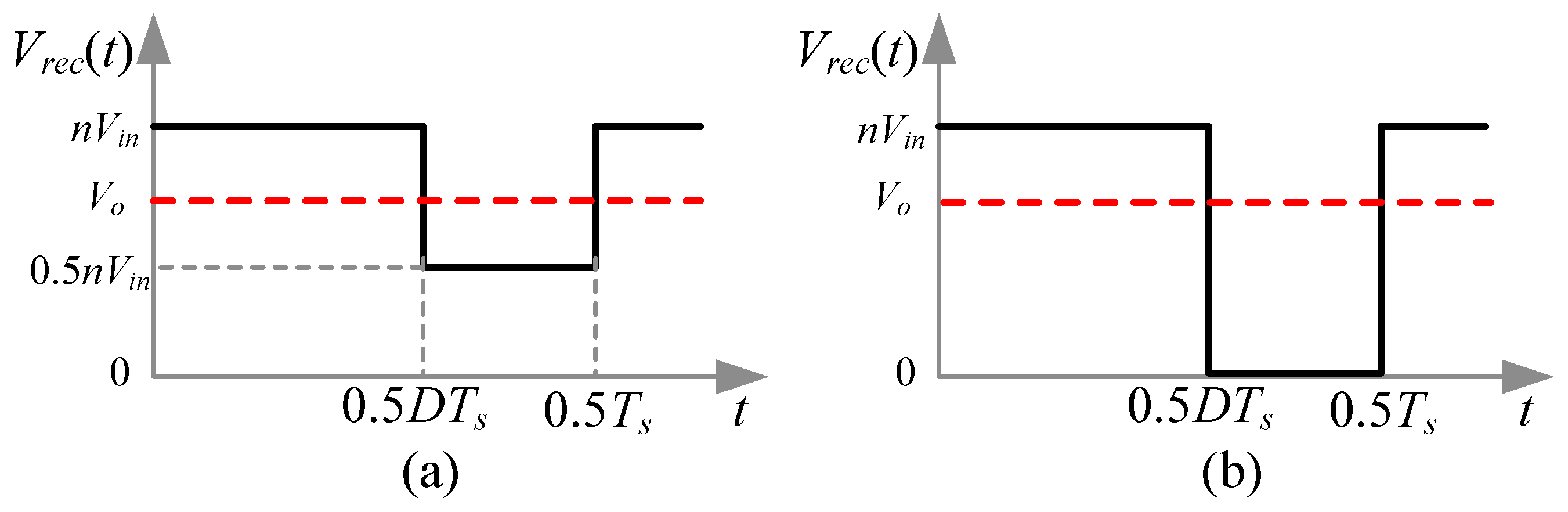

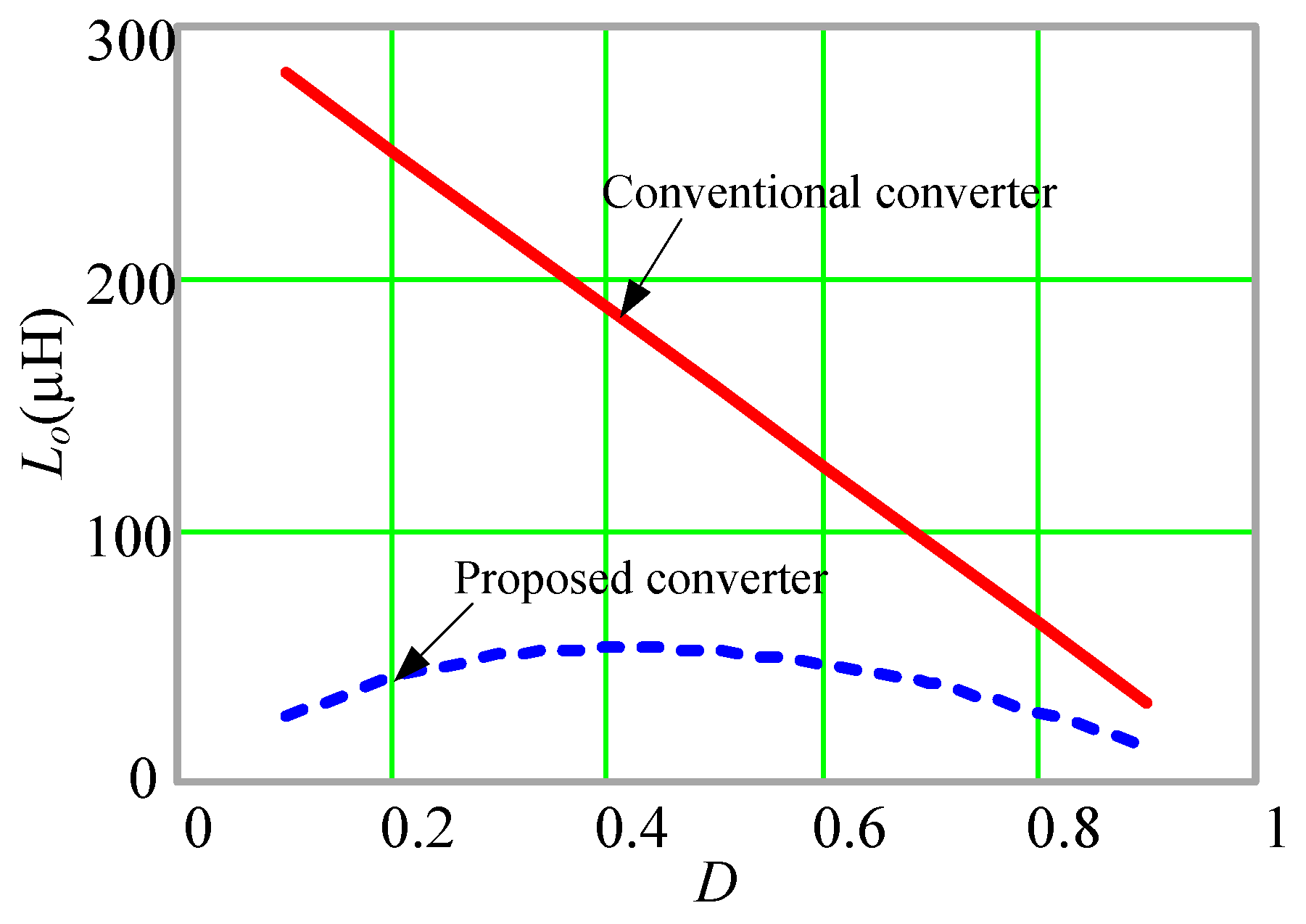

3.1. Voltage Gain Analysis

3.2. ZVS Characteristics

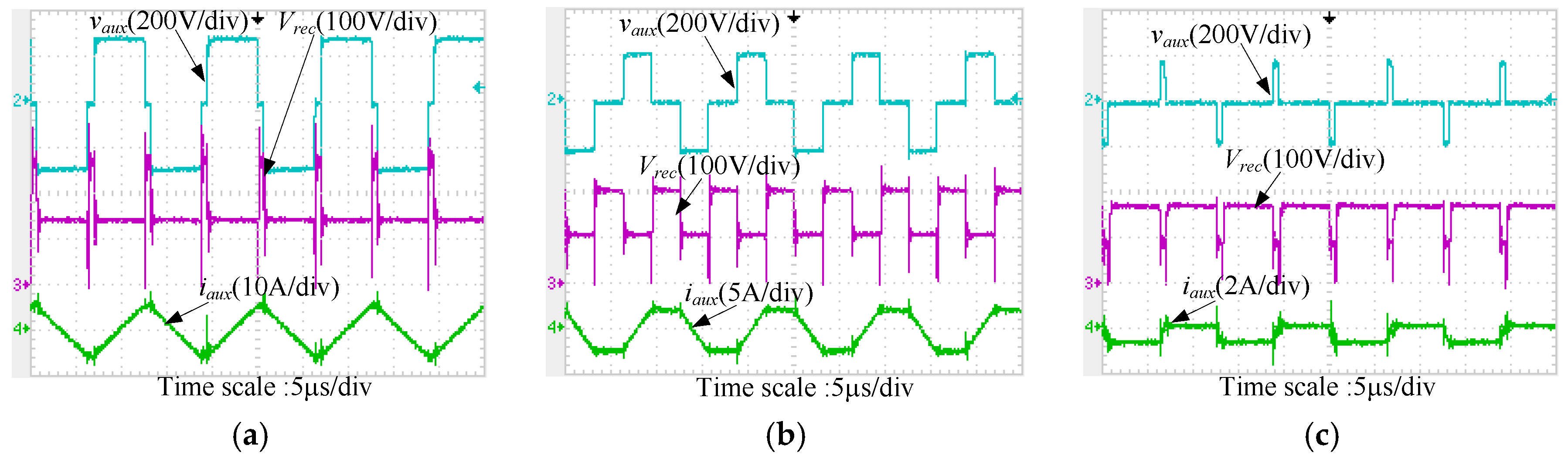

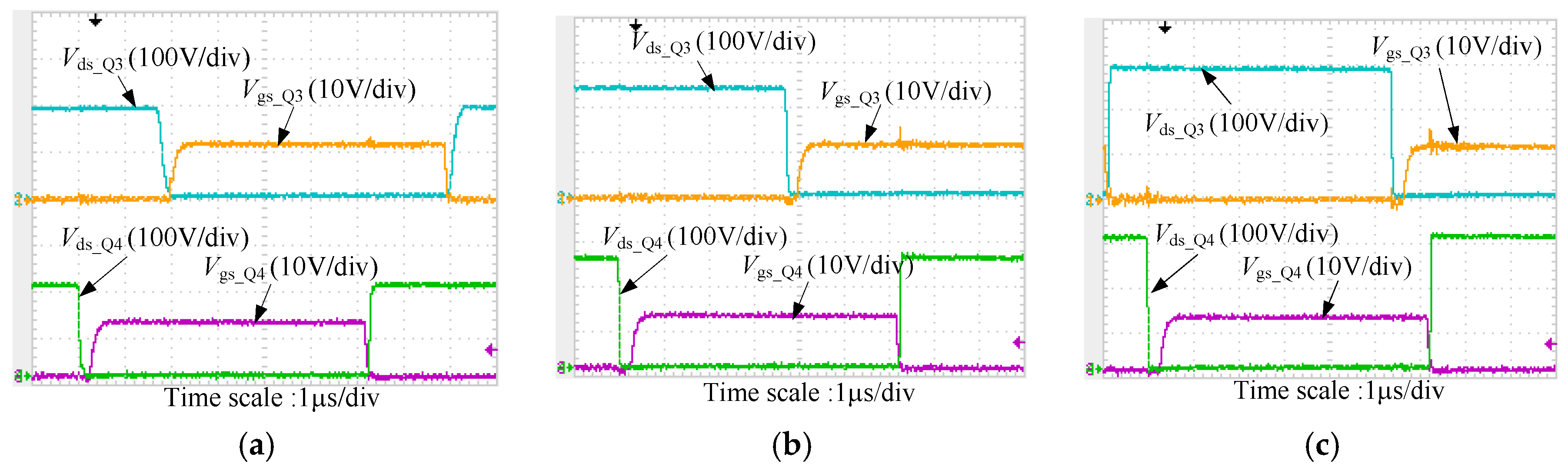

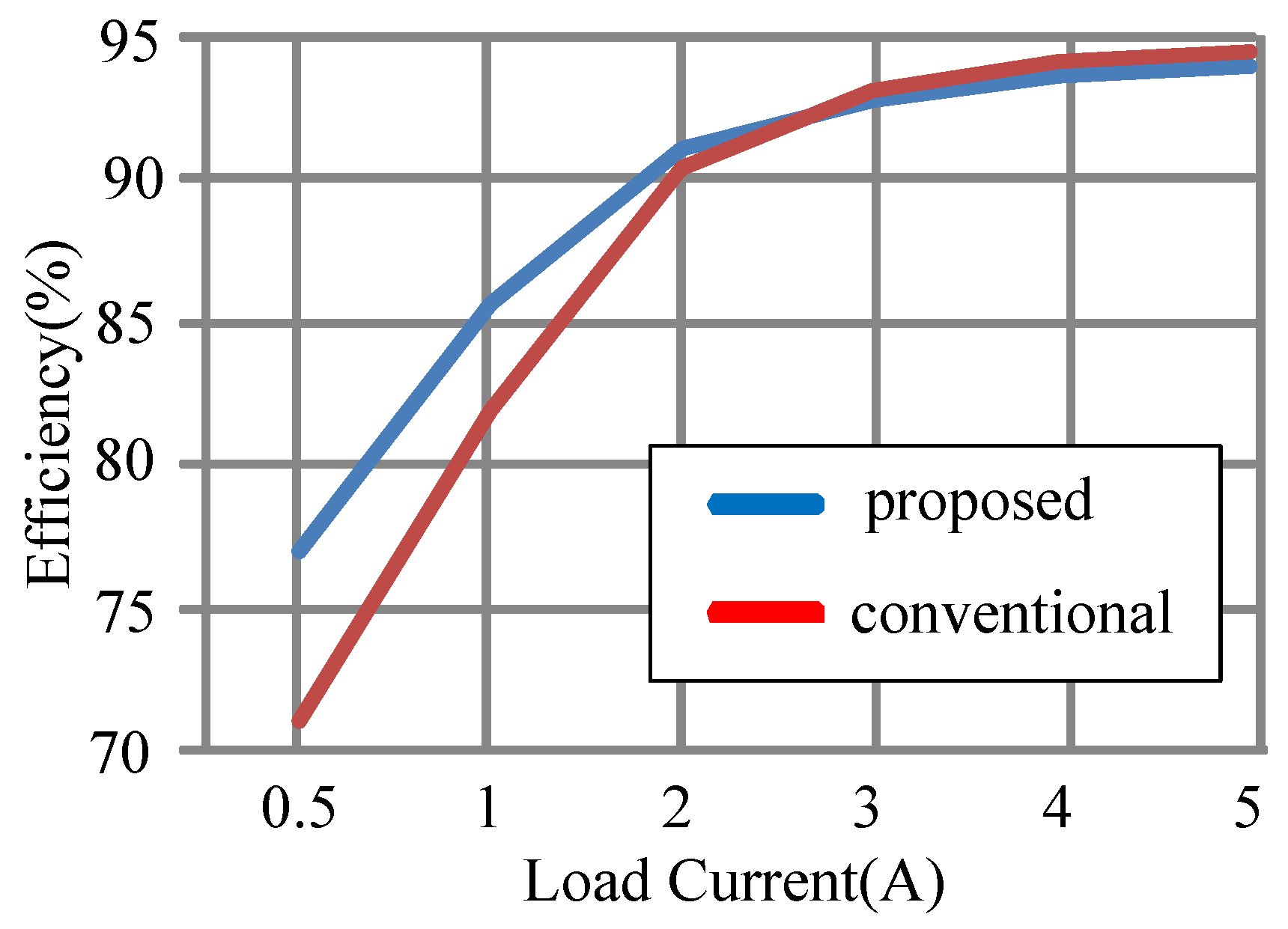

4. Experimental Results

- (1)

- Input voltage: Vin = 200–300 V

- (2)

- Output voltage: Vo = 150 V

- (3)

- Maximum output current Io(max) = 5 A

- (4)

- Switching frequency: fs = 80 kHz

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Kim, Y.D.; Cho, K.M.; Kim, D.-Y.; Moon, G.-W. Wide-range ZVS phase-shift full-bridge converter with reduced conduction loss caused by circulating current. IEEE Trans. Power Electron. 2013, 28, 3308–3316. [Google Scholar] [CrossRef]

- Hu, S.; Li, X.; Lu, M.; Luan, B.-Y. Operation modes of a secondary-side phase-shifted resonant converter. Energies 2015, 8, 12314–12330. [Google Scholar] [CrossRef]

- Kim, J.W.; Kim, D.Y.; Kim, C.E.; Moon, G.W. A simple switching control technique for improving light load efficiency in a phase-shifted full-bridge converter with a server power system. IEEE Trans. Power Electron. 2014, 29, 1562–1566. [Google Scholar] [CrossRef]

- Kim, D.Y.; Kim, C.E.; Moon, G.W. Variable delay time method in the phase-shifted full-bridge converter for reduced power consumption under light load conditions. IEEE Trans. Power Electron. 2013, 28, 5120–5127. [Google Scholar] [CrossRef]

- Zhao, L.; Li, H.; Hou, Y.; Yu, Y. Operation analysis of a phase-shifted full-bridge converter during the dead-time interval. IET Power Electron. 2016, 9, 1777–1783. [Google Scholar] [CrossRef]

- Chen, B.Y.; Lai, Y.S. Switching control technique of phase-shift-controlled full-bridge converter to improve efficiency under light-load and standby conditions without additional auxiliary components. IEEE Trans. Power Electron. 2010, 25, 1001–1012. [Google Scholar] [CrossRef]

- Borage, M.; Tiwari, S.; Kotaiah, S. A passive auxiliary circuit achieves zero-voltage-switching in full-bridge converter over entire conversion range. IEEE Trans. Power Electron. 2005, 3, 141–143. [Google Scholar] [CrossRef]

- Borage, M.; Tiwari, S.; Bhardwaj, S.; Kotaiah, S. A full-bridge DC-DC converter with zero-voltage-switching over the entire conversion range. IEEE Trans. Power Electron. 2008, 4, 1743–1750. [Google Scholar] [CrossRef]

- Safaee, A.; Jain, P.; Bakhshai, A. A ZVS pulse width modulation full-bridge converter with a low-RMS-current resonant auxiliary circuit. IEEE Trans. Power Electron. 2016, 31, 4031–4047. [Google Scholar] [CrossRef]

- Jang, Y.; Jovanovic, M.M. A new PWM ZVS full-bridge converter. IEEE Trans. Power Electron. 2007, 22, 987–994. [Google Scholar] [CrossRef]

- Gu, B.; Lai, J.S.; Kees, N.; Zheng, C. Hybrid-switching full-bridge DC–DC converter with minimal voltage stress of bridge rectifier, reduced circulating losses, and filter requirement for electric vehicle battery chargers. IEEE Trans. Power Electron. 2013, 28, 1132–1144. [Google Scholar] [CrossRef]

- Wu, X.; Xie, X.; Zhao, C.; Qian, Z.; Zhao, R. Low voltage and current stress ZVZCS full bridge DC-DC converter using center tapped rectifier reset. IEEE Trans. Ind. Electron. 2008, 55, 1470–1477. [Google Scholar] [CrossRef]

- Wang, J.; Ji, B.; Wang, H.; Chen, N.; You, J. An inherent zero-voltage and zero-current-switching full-bridge converter with no additional auxiliary circuits. J. Power Electron. 2015, 15, 610–620. [Google Scholar] [CrossRef]

- Seok, K.; Kwon, B. An improved zero-voltage and zero-current-switching full-bridge PWM converter using a simple resonant circuit. IEEE Trans. Ind. Electron. 2001, 48, 1205–1209. [Google Scholar] [CrossRef]

- Lee, I.O.; Moon, G.W. Soft-switching DC/DC converter with a full ZVS range and reduced output filter for high-voltage applications. IEEE Trans. Power Electron. 2013, 28, 112–122. [Google Scholar] [CrossRef]

- Lee, I.O.; Moon, G.W. Phase-shifted PWM converter with a wide ZVS range and reduced circulating current. IEEE Trans. Power Electron. 2013, 28, 908–919. [Google Scholar] [CrossRef]

- Ye, Z.Y. Dual half-bridge DC-DC converter with wide-range ZVS and zero circulating current. IEEE Trans. Power Electron. 2013, 28, 3276–3286. [Google Scholar] [CrossRef]

- SPW20N60C3 Datasheet; Infineon Technologies AG: Munich, Germany, 2010.

| Main switches (Q1–Q4) | SPW20N60C3 |

| Rectifier diodes (D1–D6) | IDH08SG60C |

| Blocking capacitor (Cdc1Cdc2) | 10 µF |

| Main transformers (T1 T2) | Core PQ3535 Turns ratio n = 0.9 Llk1 = Llk2 = 12 µH |

| Output inductor (Lo) | 60 µH |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, L.; Xu, C.; Zheng, X.; Li, H. A Dual Half-Bridge Converter with Adaptive Energy Storage to Achieve ZVS over Full Range of Operation Conditions. Energies 2017, 10, 444. https://doi.org/10.3390/en10040444

Zhao L, Xu C, Zheng X, Li H. A Dual Half-Bridge Converter with Adaptive Energy Storage to Achieve ZVS over Full Range of Operation Conditions. Energies. 2017; 10(4):444. https://doi.org/10.3390/en10040444

Chicago/Turabian StyleZhao, Lei, Chuangyu Xu, Xuemei Zheng, and Haoyu Li. 2017. "A Dual Half-Bridge Converter with Adaptive Energy Storage to Achieve ZVS over Full Range of Operation Conditions" Energies 10, no. 4: 444. https://doi.org/10.3390/en10040444