2.1. Operating Principle

In general, the SC DC–DC converter consists of capacitors and switches, which are driven by two non-overlapping clock signals. The clock signals are set as close as 50% duty cycle with a minimal dead-time (n-channel metal-oxide semiconductor (NMOS) and p-channel metal-oxide semiconductor (PMOS) switches are never closed at the same time to prevent the shoot-through current loss) for the maximum efficiency and the maximum charge transfer to the load.

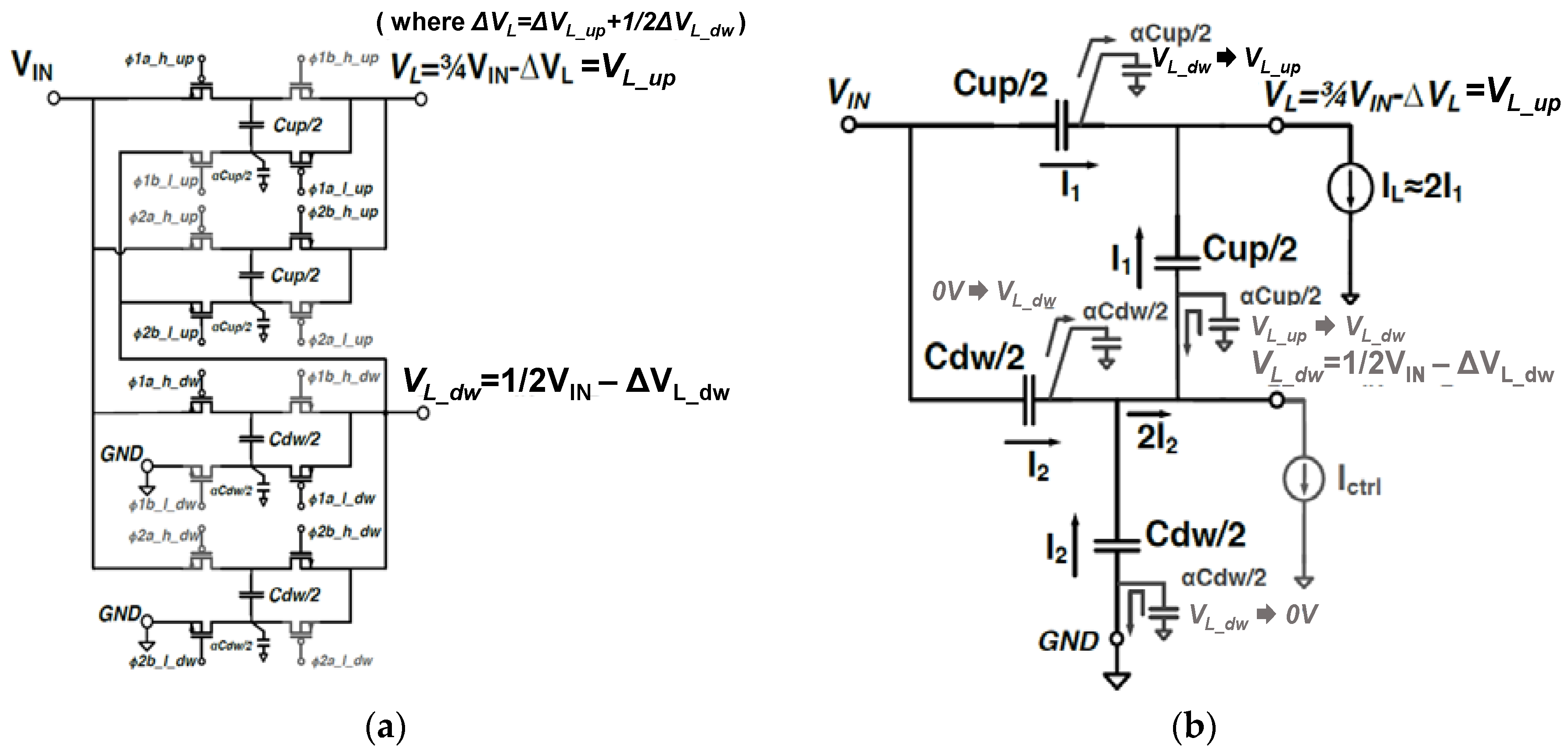

Figure 1a, b shows the conventional 2-to-1 topology and its low-swing gate-driving signals, respectively. The signals are generated from the level-shifters followed by the non-overlapping clock generators, which will be shown later in Figure 5 in

Section 3 to minimize the switching loss. To present the loss due to bottom-plate parasitic capacitors, a bottom-plate parasitic capacitor is modeled as α

Cfly, where

Cfly is the actual capacitance of a flying capacitor and is the process and layout-dependent parameter. For convenience,

Figure 1a can be symbolized as the one shown in

Figure 1c, which has two input terminals and one output terminal. Assuming that (1) all MOS switches have the same on-resistance of

Ron; (2) the time durations of phase1 and phase2 are the same with the minimal dead time; and (3) the time constant (

RL + 2

Ron)

Cfly is much larger than

1/(2

fsw), the average load voltage (

VL) in

Figure 1a,c, is defined as the average voltage between two input voltages (=(

VIN + 0 V)/2 =

VIN/2) minus Δ

VL, since the average voltage across the flying capacitor (

Cfly) is constant at

VIN/2 in steady-state. Δ

VL results from the conduction loss and can be given by:

As shown in Equation (1), if the MOS switches have zero on-resistance, ΔVL becomes zero; therefore, no conduction loss exists, and the average load voltage (VL) will be the same as the no-load voltage (VNL = VIN/2).

In a similar way, the proposed 4-to-3 topology is created in a combination of two 2-to-1 topologies as shown in

Figure 1d; one input terminal of the

2-to-1_up block is fed directly from the input voltage source (

VIN), and the other input terminal is fed out of the output (

VL_dw) of the

2-to-1_dw block. Therefore, the generated load voltage

VL_up (=(

VIN + VL_dw)/2 − Δ

VL_up) is the average value of

VIN and

VL_dw (=

1/2

VIN − Δ

VL_dw) minus Δ

VL_up. Δ

VL_up and Δ

VL_dw represent the voltage difference between the delivered load voltages when there is load and there is no load. Again, Δ

VL_up and Δ

VL_dw arise from the conduction loss, and they limit the maximum attainable efficiency to η

lin = VL_dw/(1/2

VIN) for

2-to-1_dw and η

lin = VL_up/{(

VIN + VL_dw)/2} for

2-to-1_up.

Figure 2a shows the transistor level implementations of the

2-to-1_dw(

up) blocks, and

Figure 2a shows the gate-driving signals. Since the gate-oxide breakdown voltage of 5 V CMOS transistors in 0.35 μm BCDMOS technology is 5.5 V, all switches can withstand any voltage levels between ground (0 V) and input (5 V). All the gate driving signals in

Figure 2b are generated from the level shifters and the non-overlapping clock generators to minimize the switching loss and shoot-through current loss, which will be shown in Figure 5 in

Section 3. The NMOS transistors (Mn1, Mn3, and Mn4) in

Figure 2a are implemented by means of a triple-well device to isolate the body voltage from the substrate (or bulk).

2.2. Charge Transfer and Loss Mechanisms

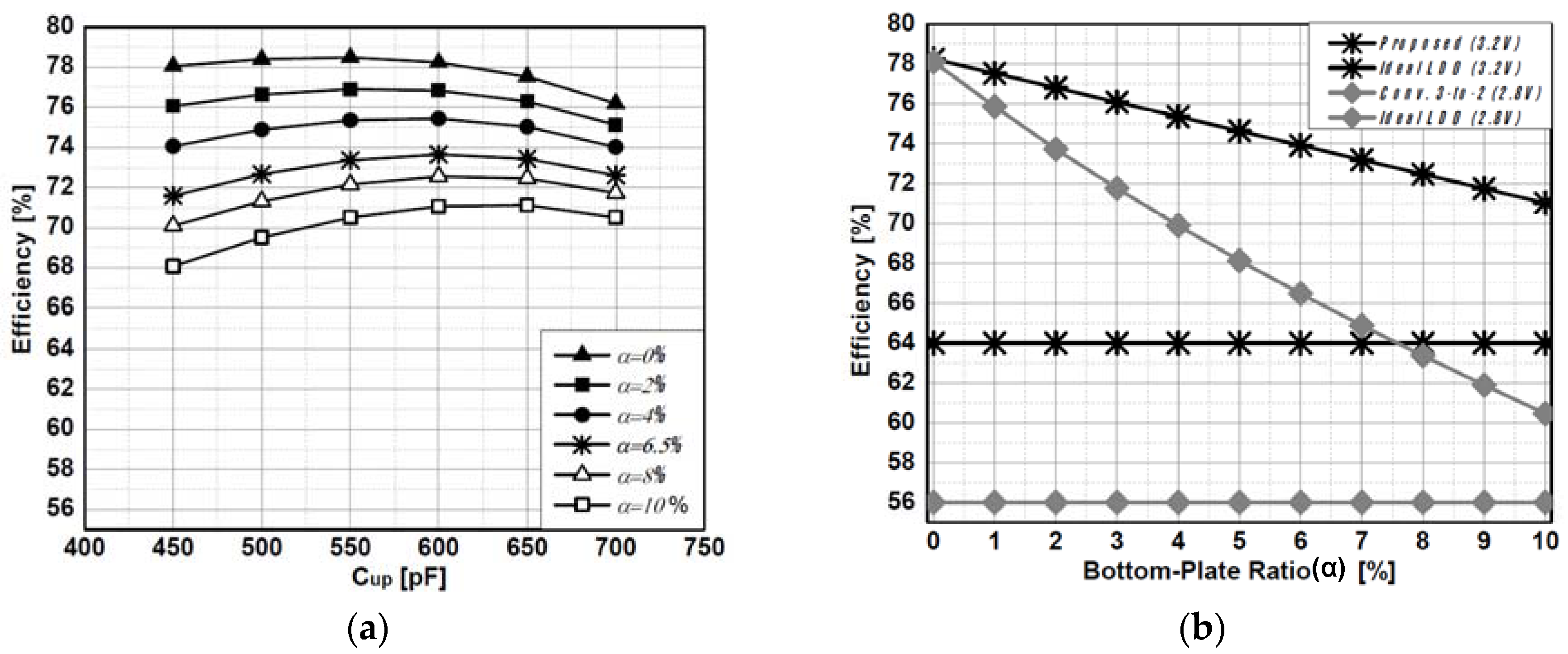

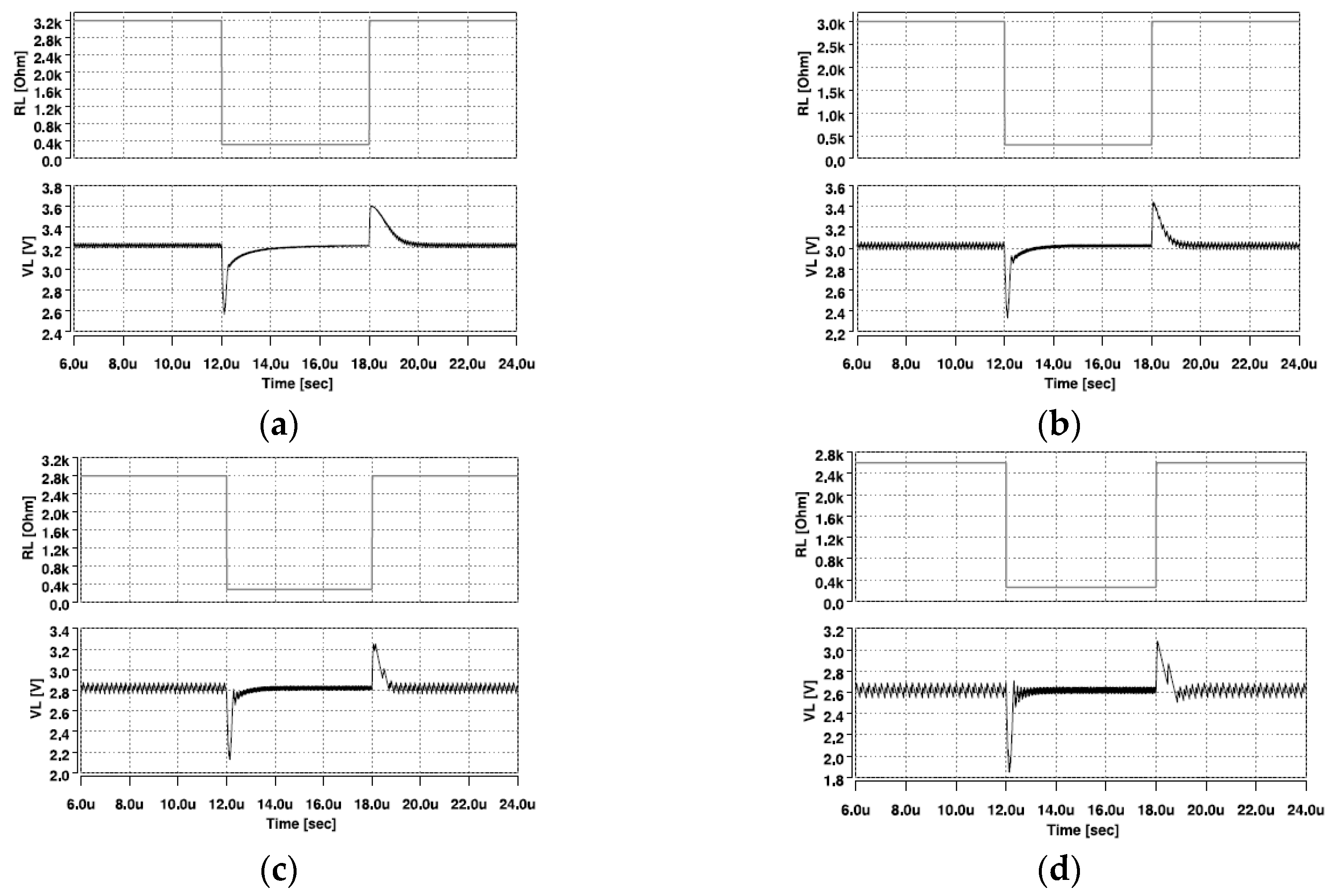

The 2-way interleaved structure of the proposed SC DC–DC converter shown in

Figure 3a is used for simplicity of the analysis. For the gate driving signals, ϕ1

a (ϕ1

b) and ϕ2

a (ϕ2

b) are 180° out of phase signals, while ϕ1

a (ϕ2

b) and ϕ1

b (ϕ2

b) represent non-overlapping clock signals, which are shown in

Figure 2b.

Figure 3b represents the equivalent circuit during every half period (phase1 and phase2) of the switching frequency. Assuming that the SC DC–DC converter delivers charge to the loads at average voltages of

VL_up (or

VL) and

VL_dw, the charge extracted from the input voltage source (

QEXT(VIN)) during every half period of the switching frequency (when the MOS transistors which have the gate-driving signals of ϕ1

a (ϕ1

b) and ϕ2

b (ϕ2

a) are on) can be derived as:

Since the total charge delivered to the load (

VL_up) is the sum of the charge transferred from both top flying capacitors (

Cup/2) as shown in

Figure 3b, the total charge transferred to the load is given by:

Considering only the charge transfer, the efficiency can be defined as the ratio of the total charge delivered to the load shown in Equation (3) to the charge extracted from the input voltage source shown in Equation (2). The relationship between ΔVL_up and ΔVL_dw is determined by the ratio between Cup and Cdw, which will be derived in Equation (6). By solving Equations (2) and (6) together, the efficiency of the proposed 4-to-3 step-down SC DC–DC converter is given by VL_up/(3/4VIN (=VNL)). It shows the upper limit of the efficiency of any kind of SC DC–DC converters; in other words, the maximum attainable efficiency decreases as the voltage drop between the no-load voltage (VNL) and the average load voltage (VL_up) increases.

In order to determine the minimum required capacitances for each flying capacitor that satisfy the design requirements (

IL(MAX) = 10 mA and

VL_up = 3.2 V @

ƒsw(MAX) = 13 MHz), the load current driving capability of the proposed SC DC–DC converter has to be derived in terms of

Cfly, Δ

VL, and

ƒsw(MAX). From Equations (2) and (3), and

Figure 3b, the load current driving capability at a fixed switching frequency (

ƒsw) and Δ

VL (=Δ

VL_up + 1/2Δ

VL_dw since Δ

VL =

VNL −

VL_up, where

VNL = 3/4

VIN and

VL_up = (

VIN +

VL_dw)/2 − Δ

VL_up) is given by:

From Equations (4) and (5), the relationship between Δ

VL_up and Δ

VL_dw is determined by the ratio between

Cup and

Cdw, which is given by:

There is an optimal ratio between

Cup and

Cdw, which yields the maximum load current (

IL) at a constant Δ

VL_dw,

ƒsw, and

Cfly. Since

VL_up is the summation of Δ

VL_up and 1/2Δ

VL_dw, Δ

VL_up can be express in terms of Δ

VL_dw,

Cup (=

Cfly −

Cdw), and

Cdw using Equation (6) as:

From Equations (4) and (7), the load current (

IL) is given by:

By taking the partial derivative of Equation (8) with respect to

Cdw and putting it to zero, the maximum load current (

IL(MAX)) is obtained when

Cfly is three times that of

Cdw. Therefore, the optimal ratio between

Cup and

Cdw, which yields the maximum load current (

IL) at a constant Δ

VL,

ƒsw, and

Cfly (=

Cup +

Cdw), is given by

Cup = 2

Cdw. Therefore, Equation (8) can be rewritten as:

where

,

.

From Equation (6), if Cup is twice the value of Cdw, ΔVL_up is equal to ΔVL_dw. Since our target load voltage is 3.2 V, ΔVL is determined to be 0.55 V (ΔVL = ΔVNL − VL_up). Therefore, both ΔVL_up and ΔVL_dw are determined to be about 0.367 V, since ΔVL is equal to the summation of ΔVL_up and 1/2 ΔVL_dw. For the given specifications, (1) ΔVL_up (=ΔVL_dw) is 0.367 V; (2) the maximum load current (IL(MAX)) is 10 mA; and (3) the maximum switching frequency (ƒsw) of the voltage controlled oscillator (VCO) is about 13 MHz, and the minimum required Cup can be estimated as about 455 pF. Considering process–voltage–temperature (PVT) variations, the Cup of 600 pF and Cdw of 300 pF are chosen. The MOS switches are sized with small margins to guarantee that the converter is able to deliver a 10 mA load current to the 3.2 V load.

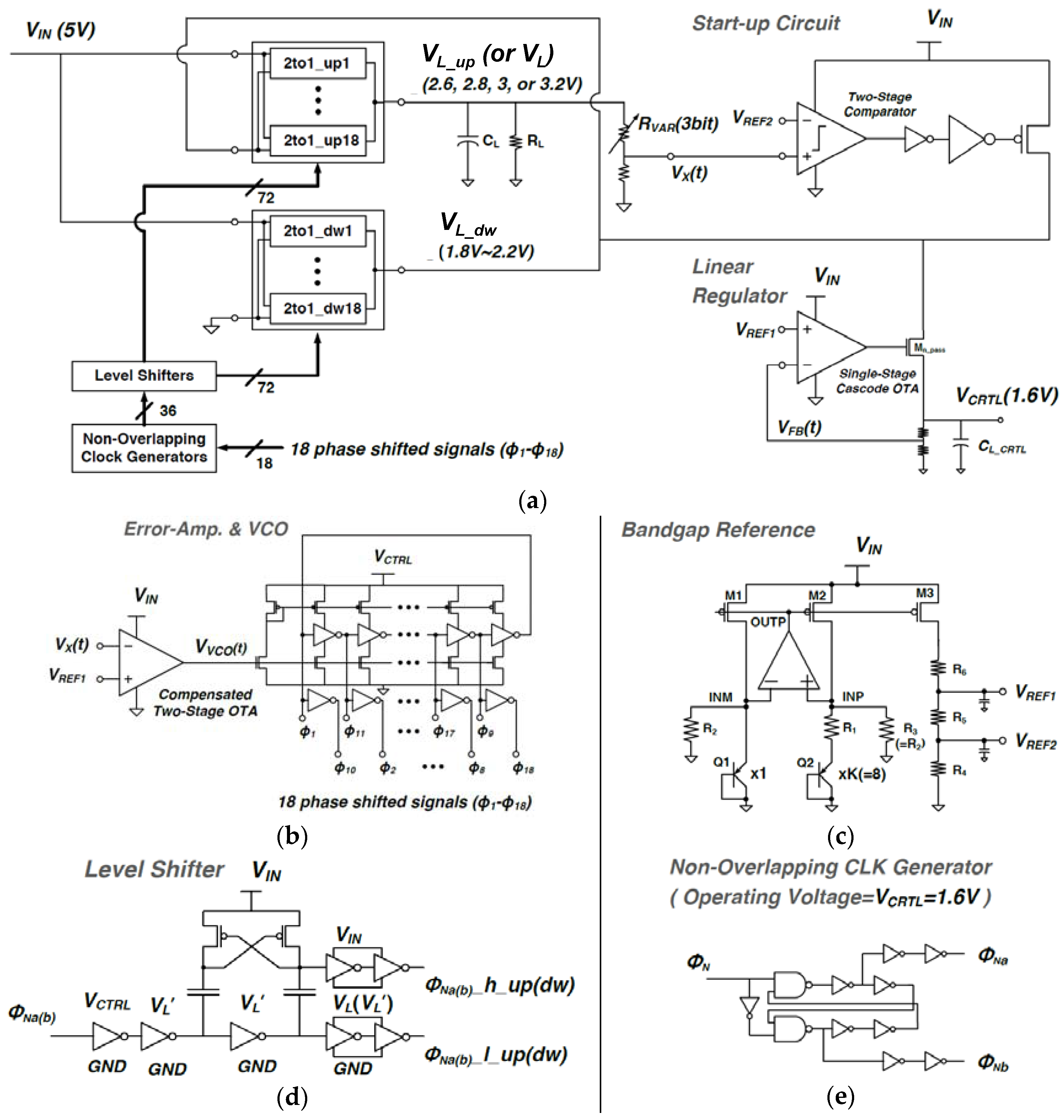

As can be observed from Equation (9), with the fixed values of ΔVL and Cup (Cdw), the load current (IL) can be controlled by changing switching frequency (ƒsw). Therefore, with a change in load current, the output load voltage can be regulated by means of pulse frequency modulation (PFM). In this design, the PFM control scheme is used with the compensated two-stage operational transconductance amplifier (OTA) and the current-starved voltage controlled oscillator (VCO) as shown in Figure 5, which are designed to be operating in the range of 0.44 MHz to 15 MHz. Therefore, switching and bottom-plate capacitance loss are the maximum at the heaviest load condition (IL = 10 mA at VL_up = 3.2 V) and scale down linearly with the decreasing load by means of PFM technique.

Besides the conduction loss, the loss due to the bottom-plate parasitic capacitors is significant, especially when on-chip capacitors are used as flying capacitors. Since MOS capacitors (2.7 fF/μm

2) have higher capacitance density than MIM capacitors (1 fF/μm

2) in BCDMOS 0.35 μm technology, only MOS capacitors are used as the flying and load capacitors. In this case, the bottom-plate capacitance ratio (α) is assumed to be 6.5% of an actual capacitance. As shown in

Figure 3b, during every half period of the switching frequency, each top bottom-plate capacitor α

Cup/2 (α

Cdw/2) in

2-to-1_up(

dw) is charged to

VL_up (

VL_dw), while each bottom bottom-plate capacitor α

Cup/2 (α

Cdw/2) is discharged to

VL_dw (0 V). While the charged electrons in the bottom-plate capacitors of the

2-to-1_dw block are discharged to ground, the charged electrons in the bottom-plate capacitors of

2-to-1_up block are discharged to the load

VL_dw. As a result, the energy lost per cycle due to those bottom-plate capacitors can be given by:

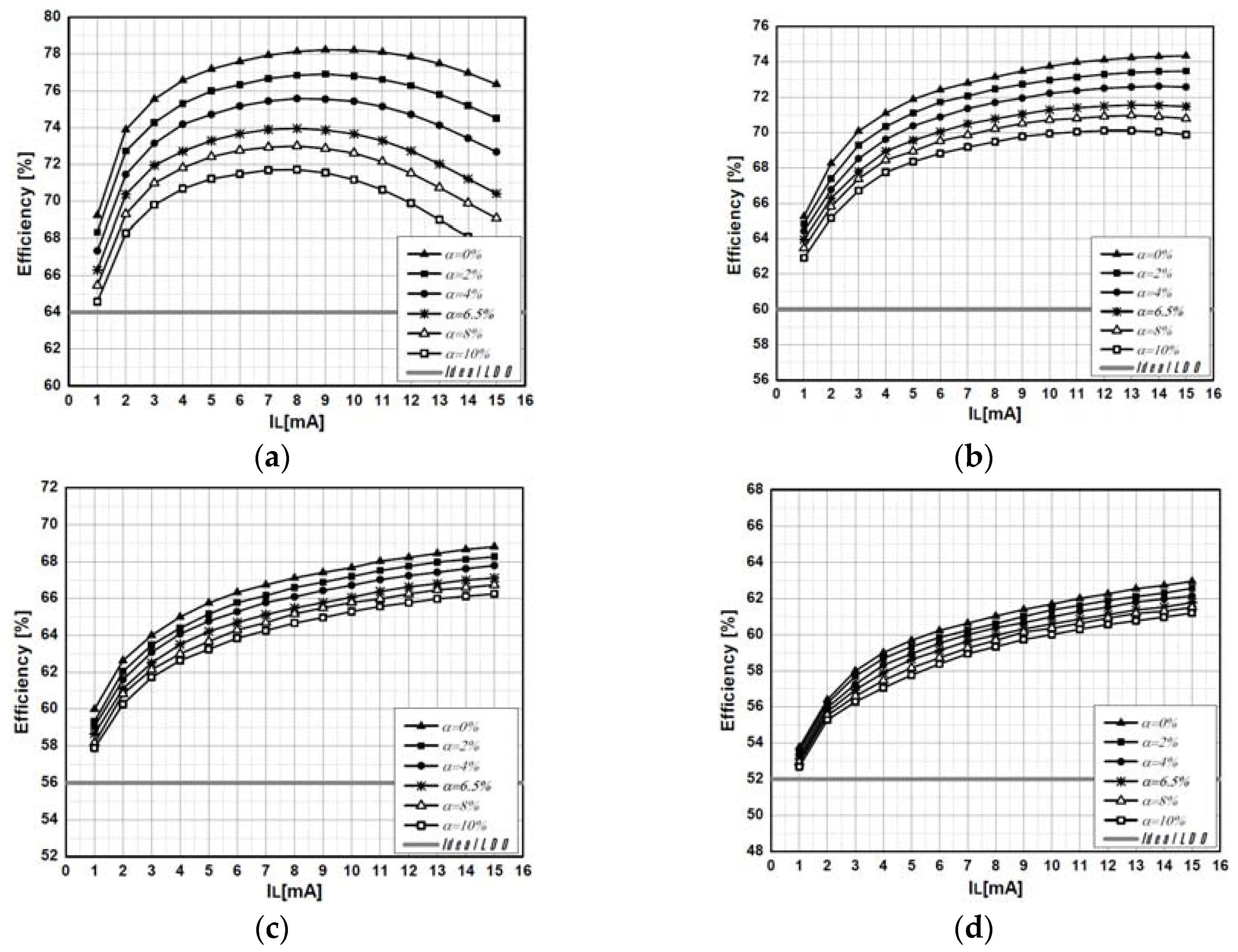

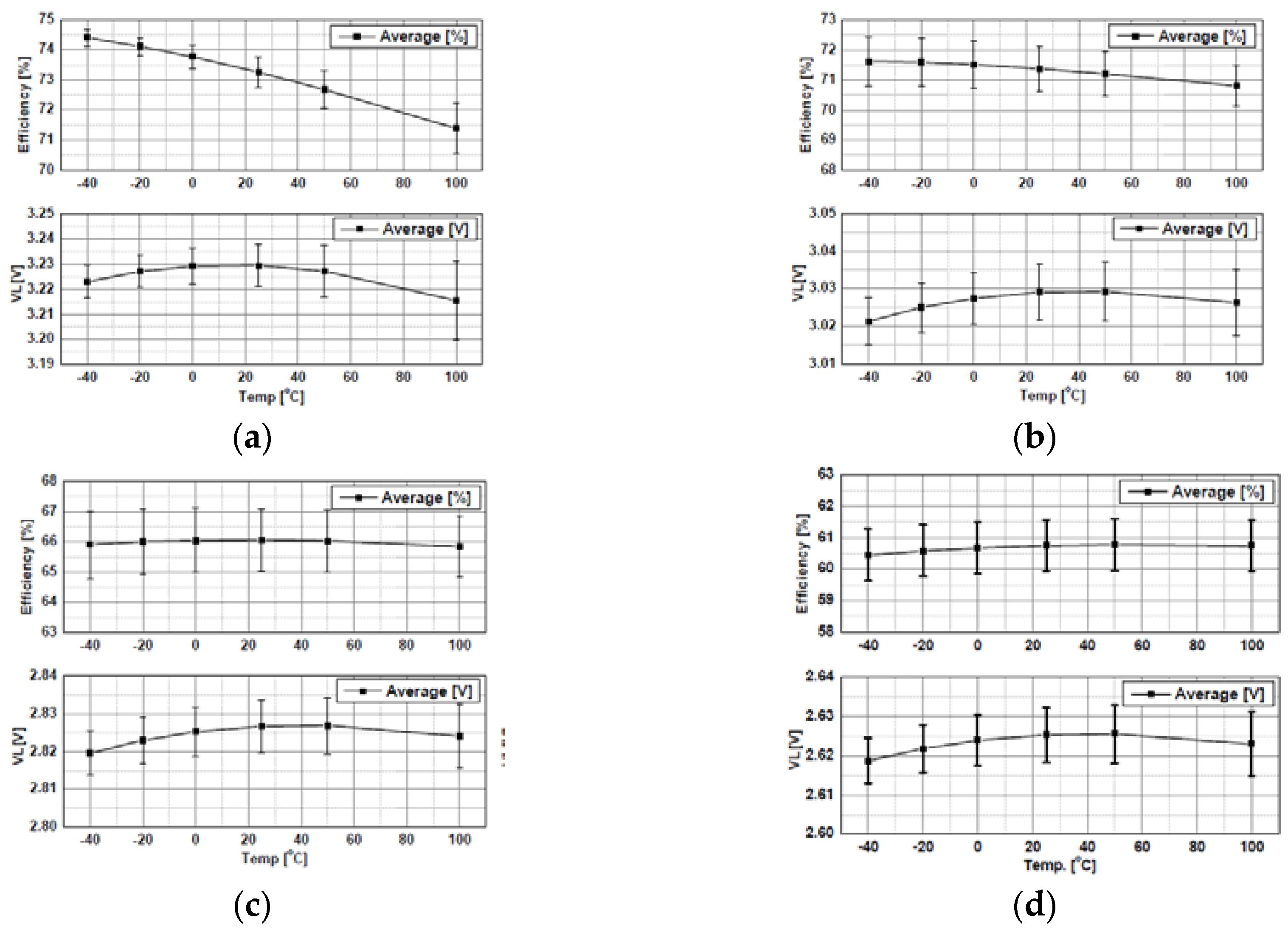

Assuming the bottom-plate capacitance ratio (α) is 0%, Equation (9) can be used to verify the previous analysis.To determine the optimum ratio between

Cup and

Cdw with non-zero,

Cup is swept from 450 pF to 700 pF at a different bottom-plate capacitance ratio (α).

Cup is altered from 0% to 10% while the total flying capacitance

Cfly is maintained at 900 pF. As shown in

Figure 4a, the maximum efficiency of 78.5% is obtained when

Cup is 550 pF and α is 0%. According to Equation (9), the maximum load is supposed to be obtained when

Cup is twice the value of

Cdw; that is,

Cup = 600 pF. The discrepancy can be explained from the neglected control current (

Ictrl) in Equation (5). However, as α increases from 0% to 10%, the maximum efficiency points in

Figure 4a moves to the right hand side of the x-axis while the overall efficiency decreases linearly, which can be explained with Equation (10). However, as shown in

Figure 3b, since the voltage swing (

VL_up −

VL_dw) at the top bottom-plate capacitors (

Cup/2) is always smaller than the voltage swing (

VL_dw) at the bottom bottom-plate capacitors (

Cdw/2) for the range of

Cup between 450 pF and 700 pF, the energy loss due to the bottom-plate capacitor is reduced as

Cup increases. As the maximum efficiency of 73.5% is obtained when

Cup is 600 pF and is 6.5% from

Figure 4a,

Cup and

Cdw are selected to be 600 pF and 300 pF, respectively, for the implementation.

Figure 4b shows the efficiency drop of the proposed 4-to-3 topology and the conventional 3-to-2 topology [

1] with respect to increasing α. In both cases, load voltages are regulated at ~85% of the no-load voltages (3.75 V for 4-to-3 topology and 3.33 V for 3-to-2 topology), while delivering a 10 mA load current using the same amount of flying and load capacitors, the same control scheme, and the same bias circuits for the implementation of both SC DC–DC converters. As shown in

Figure 4b, with an increasing bottom-plate capacitance ratio (α) from 0% to 10% of the flying capacitors, the efficiency drop of the proposed 4-to-3 topology is less than 8%, which is 2.25 times less than that of the conventional 3-to-2 topology.