Ultra-High-Speed Image Signal Accumulation Sensor

Abstract

:1. Introduction

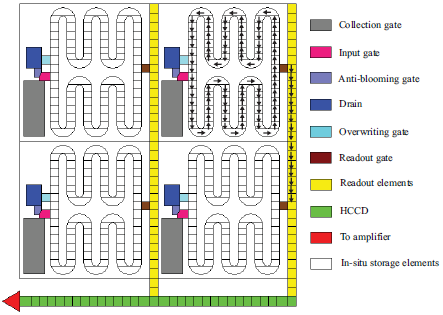

2. ISAS Structure Utilizing a Two-Phase Transfer System

2.1. Structure of the ISAS

- One CCD element consists of a channel element under a couple of alternately placed electrodes A1 and A2.

- Under each electrode, built-in potential barriers are alternately placed on the upper and the lower halves of the neighboring CCD channels.

- At each fold, a barrier is placed on the left half of the horizontally connecting CCD part to transfer the signal charge packet horizontally.

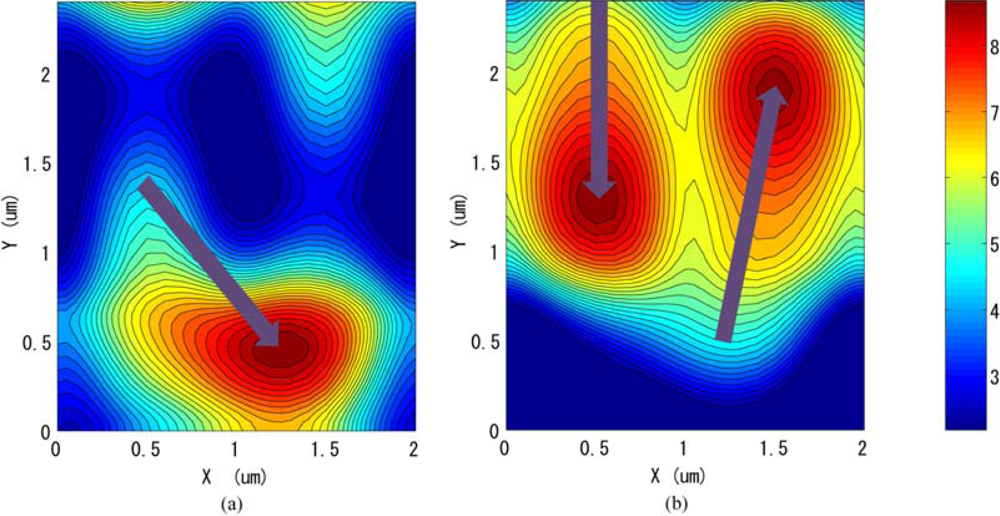

2.2. Simulation Result at a Fold of the Folded CCD Storage

3. ISAS Structure Utilizing a Four-Phase Transfer System

3.1. Structure

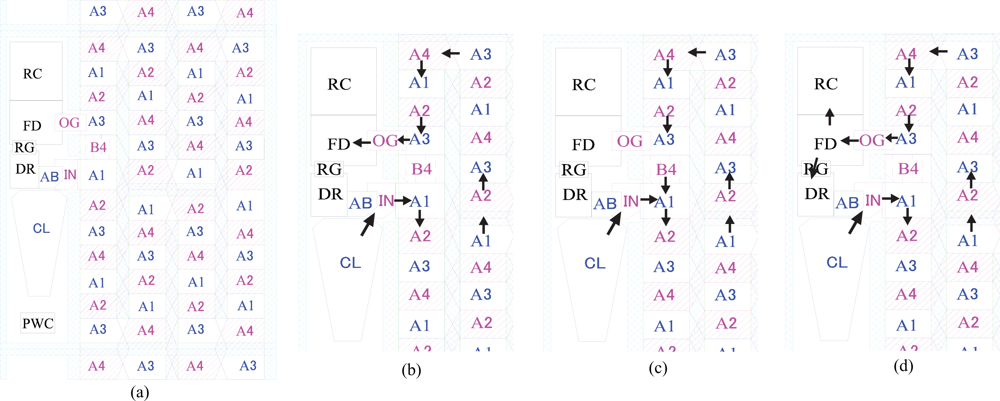

3.2. Gates and Their Basic Operations

3.3. Operation Modes of CCD-ISAS

3.4. Simulation Result at a Fold of the Folded CCD Storage

3.5. Frame Rate Limitation of the ISAS

- Employ a BSI (Backside Illumination) structure, and

- Place crossed differential buslines on the top of the front surface by using a couple of additional metal layers.

3.6. Expected Noise Performance

3.7. Hybrid CCD/CMOS-ISAS

4. Potential Applications

- The target event is reproducible.

- Light intensity is low which generates a signal electron packet much less than the full well capacity of a single storage element

- Number of frames required is up to 100 to 200 frames.

5. Conclusions

- A fold of a CCD with a simple and practical configuration.

- Connection of the first and the last elements of a topologically linear CCD.

References and Notes

- Morimoto, Y.; Tanaka, M.; Seguchi, I.Y.; Noguchi, H.; Ohba, S. Development of High-Speed Video Cameras and Study on Dynamic Deformation Behavior of Materials. Report of Grant-in-Aid for Developmental Scientific Research,. 1991; 24–25. (in Japanese). [Google Scholar]

- Elloumi, M.; Fauvet, E.; Goujou, E.; Gorria, P. The Study of a Photosite for Snapshot Video. Proceedings of SPIE International Congress on High Speed Imaging and Photonics (ICHSIP), Taejon, Korea, August 29-September 2, 1994; 2513, pp. 259–267.

- Kosonocky, W.K.; Yang, G.; Ye, C; Kabra, R.; Lawrence, J.; Mastrocolla, V.; Long, D.; Shallcross, F.; Patel, V. 360x360-Element Very High Burst-Frame Rate Image Sensor. IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers, San Francisco, CA, USA, February 6–8, 1996; pp. 182–183.

- Etoh, T.G.; Poggerman, D.; Ruckelshausen, A.; Theuwissen, A. J. P.; Kreider, G.; Folkerts, H.O.; Mutoh, H.; Kondo, Y.; Maruno, H.; Takubo, K.; Soya, H.; Takehara, K.; Okinaka, T.; Takano, Y.; Reisinger, T.; Lohman, C.B. A CCD Image Sensor of 1M Frames/s for Continuous Image Capturing of 103 Frames. IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers, San Francisco, CA, USA, February 4–6, 2002; pp. 46–47.

- Etoh, T.G.; Poggerman, D.; Kreider, G.; Mutoh, H.; Theuwissen, A.J.P.; Ruckelshausen, A.; Kondo, Y.; Maruno, H.; Takubo, K.; Soya, H.; Takehara, K.; Okinaka, T.; Takano, Y. An Image Sensor Which Captures 100 Consecutive Frames at 1,000,000 Frame/s. IEEE Trans. Electron Devices 2003, 50, 144–151. [Google Scholar]

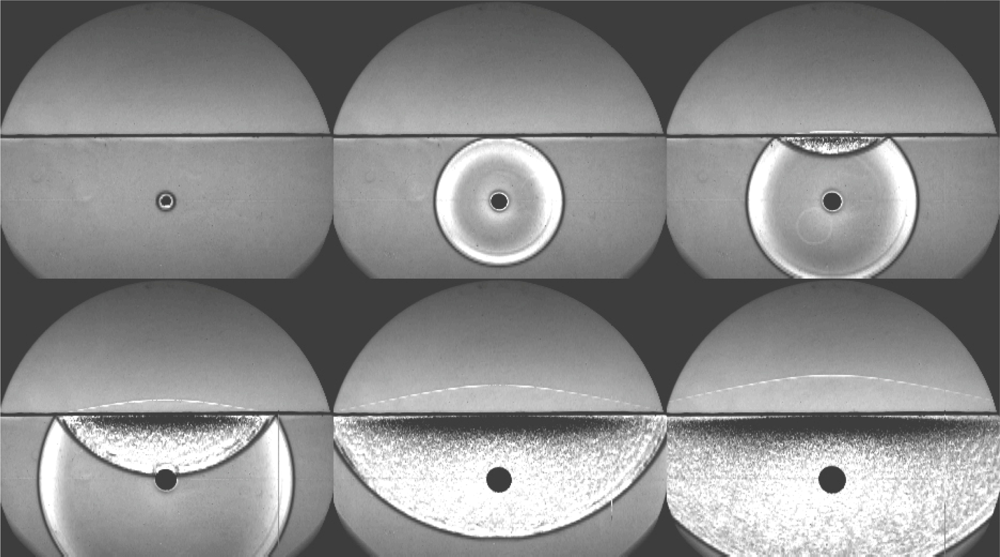

- Thoroddsen, S.T.; Etoh, T.G.; Takehara, K. High-Speed Imaging of Drops and Bubbles. Annu. Rev. Fluid Mech 2008, 40, 257–285. [Google Scholar]

- Kleine, H.; Hiraki, K.; Maruyama, H.; Hayashida, T.; Yonai, J.; Kitamura, K.; Kondo, Y.; Etoh, T.G. High-speed Time-Resolved Color Schlieren Visualization of Shock Wave Phenomena. Shock Waves 2005, 14, 333–341. [Google Scholar]

- Okinaka, T.; Karimov, P.; Etoh, T.G.; Oguni, K. Crack Propagation Imaging by the ISIS Camera and a Video Trigger System. Proceedings of SPIE: Videometrics IX, San Jose, CA, USA, January 29–30, 2007; pp. 64910Y.1–64910Y.10.

- Kureta, M; Arai, M; Etoh, T.G.; Akino, T; Etoh, K. High-speed Imaging Device with Pixels Each of Which Is Equipped with CCD Storage with a Signal Accumulation Function. Patent pending.

- Nakamura, M.; Kajimoto, R.; Inamura, Y.; Mizuno, F.; Fujita, M.; Yokoo, T.; Arai, M. First Demonstration of Novel Method for Inelastic Neutron Scattering Measurement Utilizing Multiple Incident Energies. J. Phys. Soc. Jpn 2009, 78, 093002-1–093002-4. [Google Scholar]

- Dao, V.T.S.; Etoh, T.G.; Tanaka, M.; Nguyen, H.D.; Vo, L.C.; Takehara, K.; Akino, T.; Nishi, K.; Aoki, H.; Nakai, J. Toward 100 Mega-Frames per Second: Design of an Ultimate Ultra-High-Speed Image Sensor. Sensors 2010, 10, 16–35. [Google Scholar]

- Damerell, C.J.S. Vertex Detectors and the Linear Collider. Nucl. Instrum. Meth. A 2006, 568, 240–251. [Google Scholar]

- Stefanov, K.D. CCD-based Vertex Detector for ILC. Nucl. Instrum. Meth. A 2006, 569, 48–52. [Google Scholar]

- Brouard, M.; Campbell, E.K.; Johnsen, A.J.; Vallance, C.; Yuen, W.H. Velocity Imaging in Time of Flight Mass Spectrometry. Rev. Sci. Instrum 2008, 79, 123115-1–123115-8. [Google Scholar]

- Zochowski, M.; Wachowiak, M.; Falk, C.X.; Cohen, L.B.; Lam, Y.W.; Antic, S.; Zecevic, D. Concepts in Imaging and Microscopy-Imaging Membrane Potential with Voltage Sensitive Dyes. Biol. Bull 2000, 198, 1–21. [Google Scholar]

Appendix 1

Appendix 2

- One CCD element of the four-phase system consists of a channel element with four driving electrodes. Therefore, if the size of the CCD element is the same, the width of the electrode is a half of that for the two-phase system, which requires a much finer fabrication process and causes lower DC-yield.

- The transfer speed of the four-phase transfer is a half or a quarter of that of the two-phase transfer.

- The charge handling capacity of the four-phase transfer is three to six times larger than that of the two-phase transfer.

- The four-phase transfer is much more stable than the two-phase transfer. Design of image sensors with the four-phase transfer is much easier.

Appendix 3

Appendix 4

- CL (collection gate): to collect photo-electrons generated from the backside of each pixel to the in situ storage on the front side.

- IN (input gate): to transfer signal charge packets to first element of the in situ storage.

- AB (anti-blooming gate): to drain excessive charges out of the sensor.

- DR (drain): n-substrate contact.

- A1/A2: two-phase transfer electrodes for the in situ storage.

- A1/B2: two-phase transfer electrodes for the readout VCCD.

- A1/A2/A3/A4: four-phase transfer electrodes for the in situ storage.

- A1/B2/A3/B4: four-phase transfer electrodes for the readout VCCD.

- OW (over-writing gate): to help to drain charge packets out of the sensor.

- SW (switching gate): to transfer image signals stored in the in situ storage to readout VCCD.

- PWC (p-well contact): to drain holes generated in the front side out of the sensor.

- RG (reset gate): to control reset operation.

- FD: floating diffusion node.

- RC (readout circuitry): conventional CMOS readout circuitry consisting of one source follower transistor, and row and/or column select transistor(s).

© 2010 by the authors; licensee MDPI, Basel, Switzerland. This article is an open-access article distributed under the terms and conditions of the Creative Commons Attribution license ( http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Etoh, T.G.; Son, D.V.T.; Akino, T.K.; Akino, T.; Nishi, K.; Kureta, M.; Arai, M. Ultra-High-Speed Image Signal Accumulation Sensor. Sensors 2010, 10, 4100-4113. https://doi.org/10.3390/s100404100

Etoh TG, Son DVT, Akino TK, Akino T, Nishi K, Kureta M, Arai M. Ultra-High-Speed Image Signal Accumulation Sensor. Sensors. 2010; 10(4):4100-4113. https://doi.org/10.3390/s100404100

Chicago/Turabian StyleEtoh, Takeharu Goji, Dao Vu Truong Son, Toshiaki Koike Akino, Toshiro Akino, Kenji Nishi, Masatoshi Kureta, and Masatoshi Arai. 2010. "Ultra-High-Speed Image Signal Accumulation Sensor" Sensors 10, no. 4: 4100-4113. https://doi.org/10.3390/s100404100

APA StyleEtoh, T. G., Son, D. V. T., Akino, T. K., Akino, T., Nishi, K., Kureta, M., & Arai, M. (2010). Ultra-High-Speed Image Signal Accumulation Sensor. Sensors, 10(4), 4100-4113. https://doi.org/10.3390/s100404100