Resonance Frequency Readout Circuit for a 900 MHz SAW Device

Abstract

:1. Introduction

2. Proposed Method

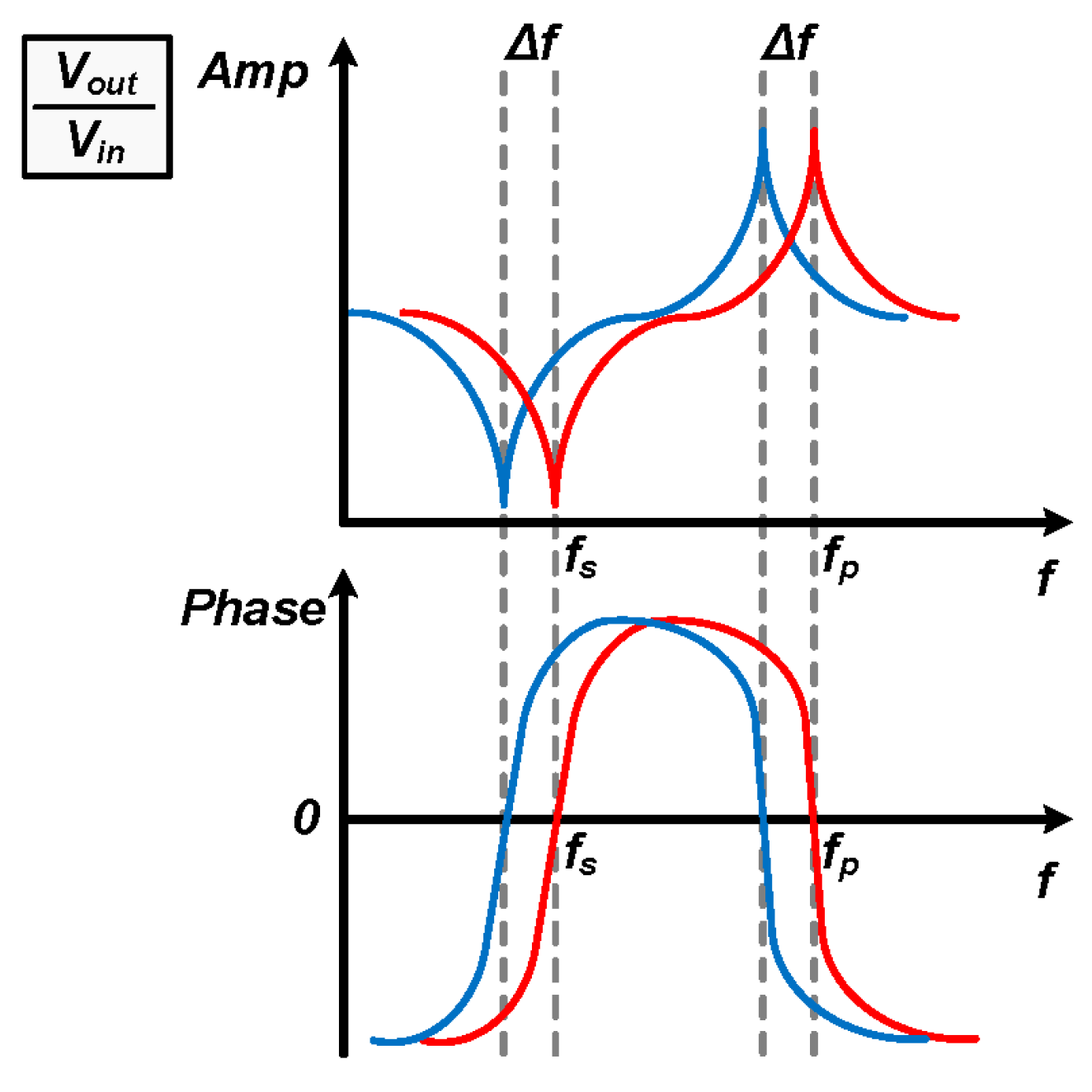

2.1. Working Principle

2.2. Circuit Architecture

2.3. Performance Analysis

3. Circuit Implementation

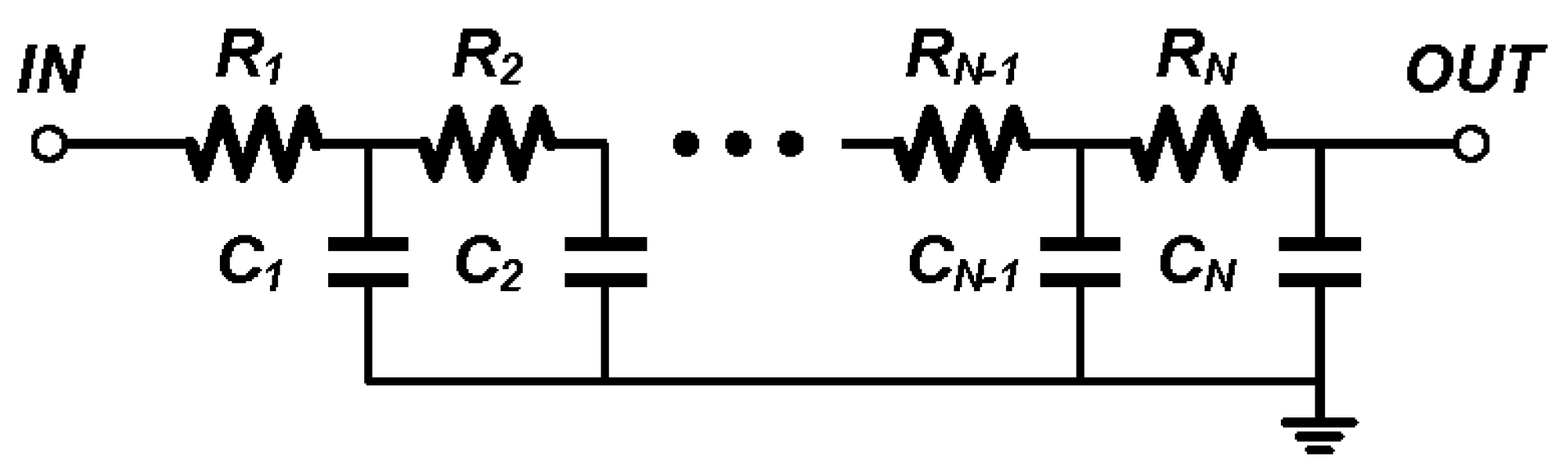

3.1. Connection Parasitics between the SAW Device

3.2. Fractional-N PLL

3.3. Mixer and I/Q Generator

3.4. Passive LPF and Comparator

3.5. BBPD and Control Logic

4. Experimental Results

4.1. Measurement Set-up

4.2. Experimental Results

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Vlassov, Y.N.; Kozlov, A.S.; Pashchin, N.S.; Yakovkin, I.D. Precision SAW pressure sensors. In Proceedings of the IEEE International Frequency Control Symposium, Salt Lake City, UT, USA, 2–4 June 1993. [Google Scholar]

- Ou, H.C.; Zaghloul, M. The SAW resonators on LiNbO3 for mass-sensing applications. In Proceedings of the IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010. [Google Scholar]

- Zhu, Y.; Zheng, Y.; Gao, Y.; Made, D.I.; Sun, C.; Je, M.; Gu, A.Y. An energy autonomous 400 MHz active wireless SAW temperature sensor powered by vibration energy harvesting. IEEE Trans. Circuits Syst. I 2015, 62, 976–985. [Google Scholar] [CrossRef]

- Qiu, X.; Tang, R.; Chen, S.J.; Zhang, H.; Pang, W.; Yu, H. pH measurements with ZnO based surface acoustic wave resonator. Electrochem. Commun. 2011, 13, 488–490. [Google Scholar] [CrossRef]

- Kulkarni, K.; Friend, J.; Yeo, L.; Perlmutter, P. Surface acoustic waves as an energy source for drop scale synthetic chemistry. Lab Chip 2009, 6, 754–755. [Google Scholar] [CrossRef] [PubMed]

- Franke, T.; Abate, A.A.; Weitz, D.A.; Wixforth, A. Surface acoustic wave (SAW) directed droplet flow in microfluidics for PDMS devices. Lab Chip 2009, 9, 2625–2627. [Google Scholar] [CrossRef] [PubMed]

- Mitsakakis, K.; Tserepi, A.; Gizeli, E. SAW device integrated with microfluidics for array-type biosensing. Microelectron. Eng. 2009, 86, 1416–1418. [Google Scholar] [CrossRef]

- Luo, J.T.; Xie, M.; Luo, P.X.; Zhao, B.; Du, K.; Fan, P. A sensitive glucose biosensor without using glucose test strips based on ZnO/SiO2/Si surface acoustic wave device. Mater. Lett. 2014, 130, 14–16. [Google Scholar] [CrossRef]

- Liu, H.; Jiang, H.; Xia, J.; Chi, Z.; Li, F.; Wang, Z. A fully integrated SoC for smart capsule providing in-body continuous pH and temperature monitoring. J. Semicond. Technol. Sci. 2016, 16, 542–549. [Google Scholar] [CrossRef]

- White, R.M.; Voltmer, F.W. Direct piezoelectric coupling to surface elastic waves. Appl. Phys. Lett. 1965, 7, 314–316. [Google Scholar] [CrossRef]

- Hagleitner, C.; Lange, D.; Hierlemann, A.; Brand, O.; Baltes, H. CMOS single-chip gas detection system comprising capacitive, calorimetric and mass-sensitive microsensors. IEEE J. Solid-State Circuits 2002, 37, 1867–1878. [Google Scholar] [CrossRef]

- Petrescu, V.; Pettine, J.; Karabacak, D.M.; Vandecasteele, M.; Crego Calama, M.; Van Hoof, C. Power-efficient readout circuit for miniaturized electronic nose. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 19–23 February 2012. [Google Scholar]

- Pettine, J.; Petrescu, V.; Karabacak, D.M.; Vandecasteele, M.; Crego-Calama, M.; Van Hoof, C. Power-Efficient Oscillator-Based Readout Circuit for Multichannel Resonance Volatile Sensors. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 542–551. [Google Scholar] [CrossRef] [PubMed]

- Pertijs, M.A.P.; Zeng, Z.; Karabacak, D.M.; Crego-Calama, M.; Brongersma, S.H. An energy-efficient interface for resonance sensors based on ring-down measurement. In Proceedings of the IEEE International Symposium on Circuits and Systems, Seoul, Korea, 20–23 May 2012. [Google Scholar]

- Yan, Y.; Zeng, Z.; Chen, C.; Jiang, H.; Chang, Z.-Y.; Karabacak, D.M.; Pertijs, M.A.P. An energy-efficient reconfigurable readout circuit for resonance sensors based on ring-down measurement. In Proceedings of the IEEE SENSORS, Valencia, Spain, 2–5 November 2014. [Google Scholar]

- Jiang, H.; Chang, Z.Y.; Pertijs, M.A.P. A 30 ppm < 80 nJ ring-down-based readout circuit for resonance sensors. IEEE J. Solid-State Circuits 2016, 51, 187–195. [Google Scholar] [CrossRef]

- Elhadidy, O.; Elkholy, M.; Helmy, A.A.; Palermo, S.; Entesari, K. A CMOS fractional-N PLL-based microwave chemical sensor with 1.5% permittivity accuracy. IEEE Trans. Microw. Theory Tech. 2013, 61, 3402–3416. [Google Scholar] [CrossRef]

- Helmy, A.A.; Jeon, H.-J.; Lo, Y.-C.; Larsson, A.J.; Kulkarni, R.; Kim, J.; Silva-Martinez, J.; Entesari, K. A self-sustained CMOS microwave chemical sensor using a frequency synthesizer. IEEE J. Solid-State Circuits 2012, 47, 2467–2483. [Google Scholar] [CrossRef]

- Tian, X.-G.; Liu, H.; Tao, L.-Q.; Yang, Y.; Jiang, H.; Ren, T.-L. High-resolution, high-linearity temperature sensor using surface acoustic wave device based on LiNbO3/SiO2/Si substrate. AIP Adv. 2016, 6, 095317. [Google Scholar] [CrossRef]

- Allidina, K.; Taghvaei, M.A.; Nabki, F.; Cicek, P.-V.; El-Gamal, M.N. A MEMS-based vacuum sensor with a PLL frequency-to-voltage converter. In Proceedings of the IEEE International Conference on Electronics, Circuits and Systems, Yasmine Hammamet, Tunisia, 13–16 December 2009. [Google Scholar]

- Hong, Y.; Kim, S.-G.; Kim, B.-H.; Ha, S.-J.; Lee, H.-J.; Yun, G.-H.; Yook, J.-G. Noncontact proximity vital sign sensor based on PLL for sensitivity enhancement. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 584–593. [Google Scholar] [CrossRef] [PubMed]

- Wang, H.; Chen, Y.; Hassibi, A.; Scherer, A.; Hajimiri, A. A frequency-shift CMOS magnetic biosensor array with single-bead sensitivity and no external magnet. In Proceedings of the Digest IEEE ISSCC, San Francisco, CA, USA, 8–12 February 2009; pp. 438–439. [Google Scholar]

- Jiang, H.; Wang, Z.; Zhang, C.; Liu, L.; Wang, Z. A combined low power SAR capacitance-to-digital analog-to-digital converter for multisensory system. Analog Integr. Circuits Signal Process. 2013, 75, 311–322. [Google Scholar] [CrossRef]

- Zhang, L.; Jiang, H.; Li, F.; Dong, J.; Cui, J.; Zhang, C.; Wang, Z. DC offset calibration method for zero-IF receiver removing the PGA-gain-correlated offset residue. AEUE-Int. J. Electron. Commun. 2013, 67, 578–584. [Google Scholar] [CrossRef]

- Soluch, W. Scattering matrix approach to one port SAW resonators. In Proceedings of the 1999 Joint Meeting of the European Frequency and Time Forum and the IEEE International Frequency Control Symposium, Besancon, France, 13–16 April 1999; Volume 2, pp. 859–862. [Google Scholar]

- Sauerbrey, G. Verwendung von Schwingquarzen zur Wägung dünner Schichten und zur Mikrowägung. Zeitschrift für Physik 1959, 155, 206–222. (In Germany) [Google Scholar] [CrossRef]

- Anand, T.; Makinwa, K.A.A.; Hanumolu, P.K. A VCO based highly digital temperature sensor with 0.034 °C/mV supply sensitivity. IEEE J. Solid-State Circuits 2016, 51, 2651–2663. [Google Scholar] [CrossRef]

- Woo, K.; Liu, Y.; Nam, E.; Ham, D. Fast-Lock Hybrid PLL Combining Fractional-N and Integer-N Modes of Differing Bandwidths. IEEE J. Solid-State Circuits 2008, 43, 379–389. [Google Scholar] [CrossRef]

- Zhang, L.; Jiang, H.; Wei, J.; Dong, J.; Li, F.; Li, W.; Gao, J.; Cui, J.; Chi, B.; Zhang, C.; Wang, Z. A reconfigurable sliding-IF transceiver for 400 MHz/2.4 GHz IEEE 802.15.6/ZigBee WBAN hubs with only 21% tuning range VCO. IEEE J. Solid-States Circuits 2013, 48, 2705–2716. [Google Scholar] [CrossRef]

- Yang, C.; Gao, S.; Dong, J.; Jiang, H.; Rhee, W.; Wang, Z. A 2.4 GHz two-point Delta-Sigma modulator with gain calibration and AFC for WPAN/BAN applications. In Proceedings of the 2015 IEEE International Conference on ASIC (ASICON), Chengdu, China, 3–6 November 2015. [Google Scholar] [CrossRef]

- Dong, J.; Jiang, H.; Yang, K.; Weng, Z.; Li, F.; Wei, J.; Ning, Y.; Chen, X.; Wang, Z. A wireless body sound sensor with a dedicated compact chipset. Circuits Syst. Signal Process. 2017, 36, 2341–2359. [Google Scholar] [CrossRef]

- Dong, J.; Jiang, H.; Zhang, L.; Wei, J.; Li, F.; Zhang, C.; Wang, Z. A low-power DC offset calibration method independent of IF gain for zero-IF receiver. Sci. China-Inf. Sci. 2014, 57, 1–10. [Google Scholar] [CrossRef]

- Yuan, J.; Svensson, C. High-speed CMOS circuit technique. IEEE J. Solid-State Circuits 1989, 24, 62–70. [Google Scholar] [CrossRef]

- Roshan, M.H.; Zaliasl, S.; Joo, K.; Souri, K.; Palwai, R.; Chen, W.; Pamarti, S.; Doll, J.C.; Miller, N.; Arft, C.; et al. Dual-MEMS-resonator temperature-to-digital converter with 40 K resolution and FOM of 0.12 pJK2. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 200–201. [Google Scholar]

| Reference | This Work | ISSCC ‘12 [14] | TBioCAS 2012 [15] | Sensors 2014 [17] | JSSC‘16 [18] | JSSC’12 [20] | TMTT‘13 [19] | ISSCC ‘16 [34] |

|---|---|---|---|---|---|---|---|---|

| CMOS technology (nm) | 180 | 250 | 250 | 350 | 350 | 90 | 90 | 180 |

| Architecture | Phase-based | Time-based | Time-based | Time-based | Time-based | Freq.-based | Freq.-based | Freq. ratio |

| Q factor | 130 | 280 | 450 | 386 | 376 | N/A | N/A | N/A |

| Resonant frequency (Hz) | 898 M | 1.98 M | 2.17 M | 535.8 k | 592 k | 7~9 G | 10.4 G | 45 M |

| Frequency resolution (Hz) | 733 | 53 | 5 | 26.8 | 17.6 | 2 M | 156 k | N/A |

| Relative freq. resolution 1 (ppm) | 0.82 | 26.77 | 2.3 | 50 | 29.8 | >222 | 15 | 0.00028 |

| Power cons. (mW) | 7 | 1.35 | 1.35 | 0.1 | 0.06 | 16.5 | 22 | 19 |

| Measurement time (ms) | 0.48 | 5000 | 10,000 | 6 | 1.1 | 0.9 | 25 | 3.85 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, H.; Zhang, C.; Weng, Z.; Guo, Y.; Wang, Z. Resonance Frequency Readout Circuit for a 900 MHz SAW Device. Sensors 2017, 17, 2131. https://doi.org/10.3390/s17092131

Liu H, Zhang C, Weng Z, Guo Y, Wang Z. Resonance Frequency Readout Circuit for a 900 MHz SAW Device. Sensors. 2017; 17(9):2131. https://doi.org/10.3390/s17092131

Chicago/Turabian StyleLiu, Heng, Chun Zhang, Zhaoyang Weng, Yanshu Guo, and Zhihua Wang. 2017. "Resonance Frequency Readout Circuit for a 900 MHz SAW Device" Sensors 17, no. 9: 2131. https://doi.org/10.3390/s17092131

APA StyleLiu, H., Zhang, C., Weng, Z., Guo, Y., & Wang, Z. (2017). Resonance Frequency Readout Circuit for a 900 MHz SAW Device. Sensors, 17(9), 2131. https://doi.org/10.3390/s17092131