Development of Low Parasitic Light Sensitivity and Low Dark Current 2.8 μm Global Shutter Pixel †

Abstract

:1. Introduction

2. Device Structure

3. Reduction of PLS

3.1. Structural Issue of Small GS Pixels in PLS Reduction

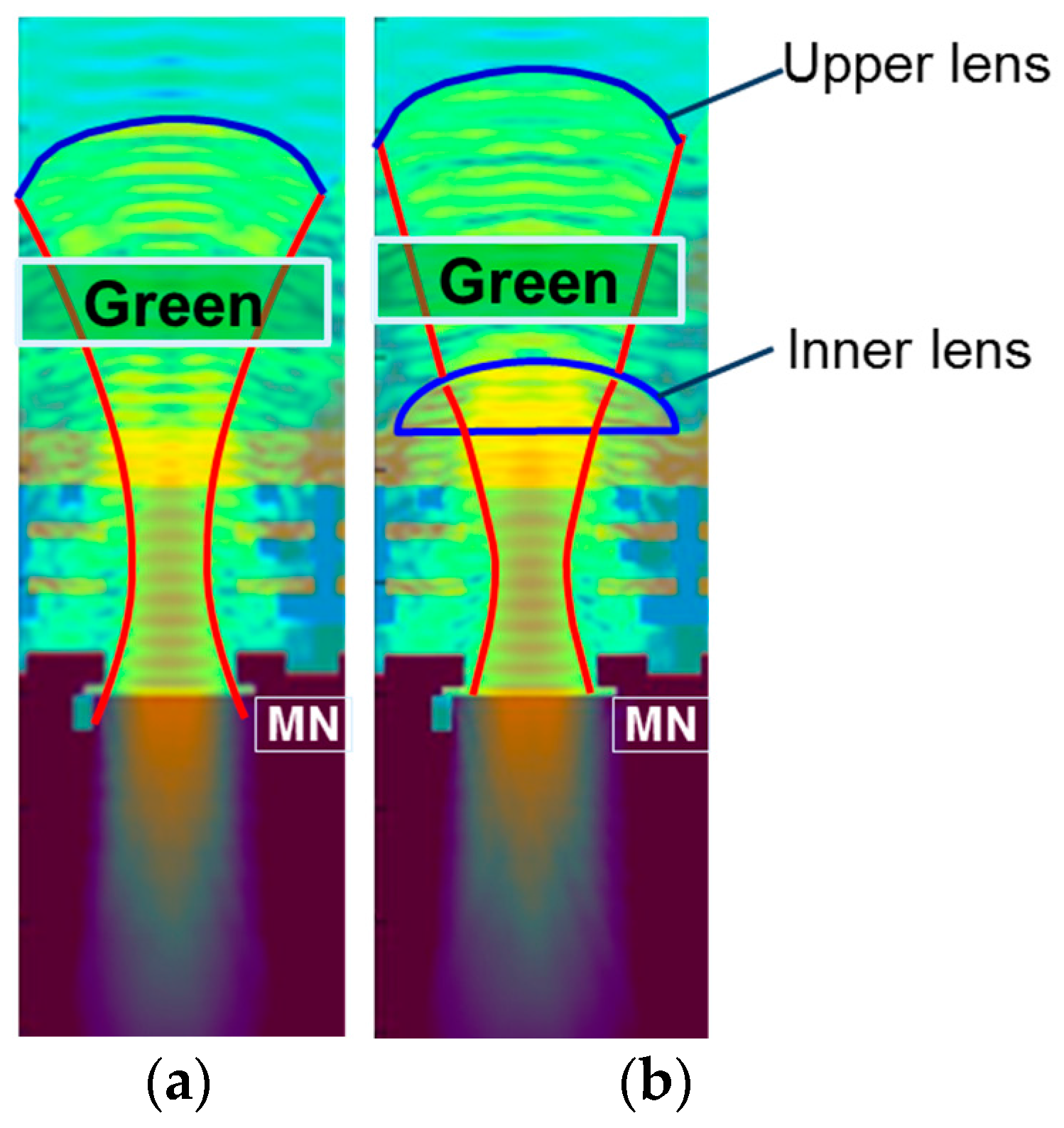

3.2. Effect of Double Micro Lens Structure

3.3. Analysis and Design Concept of Inner Lens (Our Proposal)

3.4. Results of Newly Developed Inner Lens Based on Our Design Concept for Low PLS

4. Reduction of Dark Current

4.1. Development of Low Noise MN Structures

4.2. Experimental Results of Dark Current

5. Conclusions

- (1)

- The incident light collected by the upper lens should be concentrated on the inner lens in order to improve the QE.

- (2)

- The inner lens should be designed so that light enters straight into the Si.

Author Contributions

Conflicts of Interest

References

- Lahav, A.; Birman, A.; Cohen, M.; Leitner, T.; Fenigstein, A. Design of photo-electron barrier for the Memory Node of a Global Shutter pixel based on a Pinned Photodiode. In Proceedings of the 2009 International Image Sensor Workshop, Bergen, Norway, 22–28 June 2009. [Google Scholar]

- Lahav, A.; Birman, A.; Veinger, D.; Fenigstein, A.; Zhang, D.; van Blerkom, D. IR Enhanced Global Shutter Pixel for High Speed Applications. In Proceedings of the 2013 International Image Sensor Workshop, Snowbird, UT, USA, 12–16 June 2013. [Google Scholar]

- Meynants, G. Global Shutter Image Sensors for Machine Vision Applications. In Proceedings of the Image Sensors Europe 2010, London, UK, 23–25 March 2010. [Google Scholar]

- Lauxtermann, S.; Lee, A.; Stevens, J.; Joshi, A. Comparison of Global Shutter Pixels for CMOS Image Sensors. In Proceedings of the 2007 International Image Sensor Workshop, Ogunquit, ME, USA, 7–10 June 2007. [Google Scholar]

- Yokoyama, T.; Suzuki, M.; Nishi, Y.; Mizuno, I.; Lahav, A. Design of Double micro lens structure for 2.8 μm Global Shutter Pixel. In Proceedings of the 2017 International Image Sensor Workshop, Hiroshima, Japan, 30 May–2 June 2017. [Google Scholar]

- Wang, X.; Bogaerts, J.; Vanhorebeek, G.; Ruythoren, K.; Ceulemans, B.; Lepage, G.; Willems, P.; Meynants, G. A 2.2M CMOS Image Sensor for High Speed Machine Vision Applications. In Proceedings of the IS&T/SPIE Electronic Imaging, San Jose, CA, USA, 26 January 2010; Volume 7536. [Google Scholar]

- Kawabata, K.; Kobayashi, M.; Onuki, Y.; Sekine, H.; Tsuboi, T.; Matsuno, Y.; Takahashi, H.; Inoue, S.; Ichikawa, T. A 1.8e− Temporal Noise Over 90 dB Dynamic Range 4k2k Super 35 mm Format Seamless Global Shutter CMOS Image Sensor with Multiple Accumulation Shutter Technology. In Proceedings of the 2016 International Electron Devices Meeting, San Francisco, CA, USA, 3–7 December 2016. [Google Scholar]

- Velichko, S.; Hynecek, J.J.; Johnson, R.S.; Lenchenkov, V.; Komori, H.; Lee, H.; Chen, F.Y.J. CMOS Global Shutter Charge Storage Pixels with Improved Performance. IEEE Trans. Electron Devices 2016, 63, 106–112. [Google Scholar] [CrossRef]

- Yasutomi, K.; Sadanaga, Y.; Takasawa, T.; Itoh, S.; Kawahito, S. Dark Current Characterization of CMOS Global Shutter Pixels Using Pinned Storage Diodes. In Proceedings of the 2011 International Image Sensor Workshop, Hokkaido, Japan, 8–11 June 2011. [Google Scholar]

- Teranishi, N.; Ishihara, Y. Smear reduction in the interline CCD image sensor. IEEE Trans. Electron Devices 1987, 34, 1052–1056. [Google Scholar] [CrossRef]

- Toyoda, A.; Suzuki, Y.; Orihara, K.; Hokari, Y. A novel tungsten light-shield structure for high-density CCD image sensors. IEEE Trans. Electron Devices 1991, 38, 965–968. [Google Scholar] [CrossRef]

- Mabuchi, K.; Nakamura, N.; Funatsu, E.; Abe, T.; Umeda, T.; Hoshino, T.; Suzuki, R.; Sumi, H. CMOS Image Sensor Using a Floating Diffusion Driving Buried Photodiode. In Proceedings of the 2004 International Solid-State Circuits Conference, San Francisco, CA, USA, 15–19 February 2004. [Google Scholar]

- Yamada, T.; Tanaka, H.; Henmi, K.; Kobayashi, M.; Mori, H.; Katoh, Y.; Miyata, Y.; Mutoh, N.; Kuriyama, T.; Teranishi, N. Improvement of Photo-Sensitivity and Smear Characteristics in 2.8-μm Square Pixel IT-CCD Image Sensor. In Proceedings of the IEEE Workshop on CCDs and Advanced Image Sensors, Oberbayern, Germany, 15–17 May 2003. [Google Scholar]

- Sano, Y.; Nomura, T.; Aoki, H.; Terakawa, S.; Kodama, H.; Aoki, T.; Hiroshima, Y. Submicron Spaced Lens Array Process Technology for a High Photosensitivity CCD Image Sensor. In Proceedings of the International Technical Digest on Electron Devices, San Francisco, CA, USA, 9–12 December 1990; pp. 283–286. [Google Scholar]

| Single Lens | Double Lens | |

|---|---|---|

| QE (%) | 54.1 | 58.9 |

| 1/PLS | 2700 | 3500 |

| Without Inner Lens | Conventional Inner Lens | Newly Developed Lens for GS | ||

|---|---|---|---|---|

| QE (%) | simulation | 54.1 | 58.9 | 58.6 |

| measurement | 62.0 | 62.0 | ||

| 1/PLS | simulation | 2700 | 3500 | 7100 |

| measurement | 4000 | 7700 | ||

| This Work | Ref. [10] | Unit | |

|---|---|---|---|

| Process node | 110 nm | - | - |

| Pixel pitch | 2.8 | 2.8 | μm |

| Linear Qsat | 7 | 6 | ke− |

| Dark current @ PD | 14 | - | e−/s |

| Dark current @ MN | 9.5 | 60 | e−/s |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yokoyama, T.; Tsutsui, M.; Suzuki, M.; Nishi, Y.; Mizuno, I.; Lahav, A. Development of Low Parasitic Light Sensitivity and Low Dark Current 2.8 μm Global Shutter Pixel. Sensors 2018, 18, 349. https://doi.org/10.3390/s18020349

Yokoyama T, Tsutsui M, Suzuki M, Nishi Y, Mizuno I, Lahav A. Development of Low Parasitic Light Sensitivity and Low Dark Current 2.8 μm Global Shutter Pixel. Sensors. 2018; 18(2):349. https://doi.org/10.3390/s18020349

Chicago/Turabian StyleYokoyama, Toshifumi, Masafumi Tsutsui, Masakatsu Suzuki, Yoshiaki Nishi, Ikuo Mizuno, and Assaf Lahav. 2018. "Development of Low Parasitic Light Sensitivity and Low Dark Current 2.8 μm Global Shutter Pixel" Sensors 18, no. 2: 349. https://doi.org/10.3390/s18020349

APA StyleYokoyama, T., Tsutsui, M., Suzuki, M., Nishi, Y., Mizuno, I., & Lahav, A. (2018). Development of Low Parasitic Light Sensitivity and Low Dark Current 2.8 μm Global Shutter Pixel. Sensors, 18(2), 349. https://doi.org/10.3390/s18020349