An Image Signal Accumulation Multi-Collection-Gate Image Sensor Operating at 25 Mfps with 32 × 32 Pixels and 1220 In-Pixel Frame Memory

Abstract

:1. Introduction

1.1. Fusion of Image Signal Accumulation and Multiple Collection Gate Image Sensors

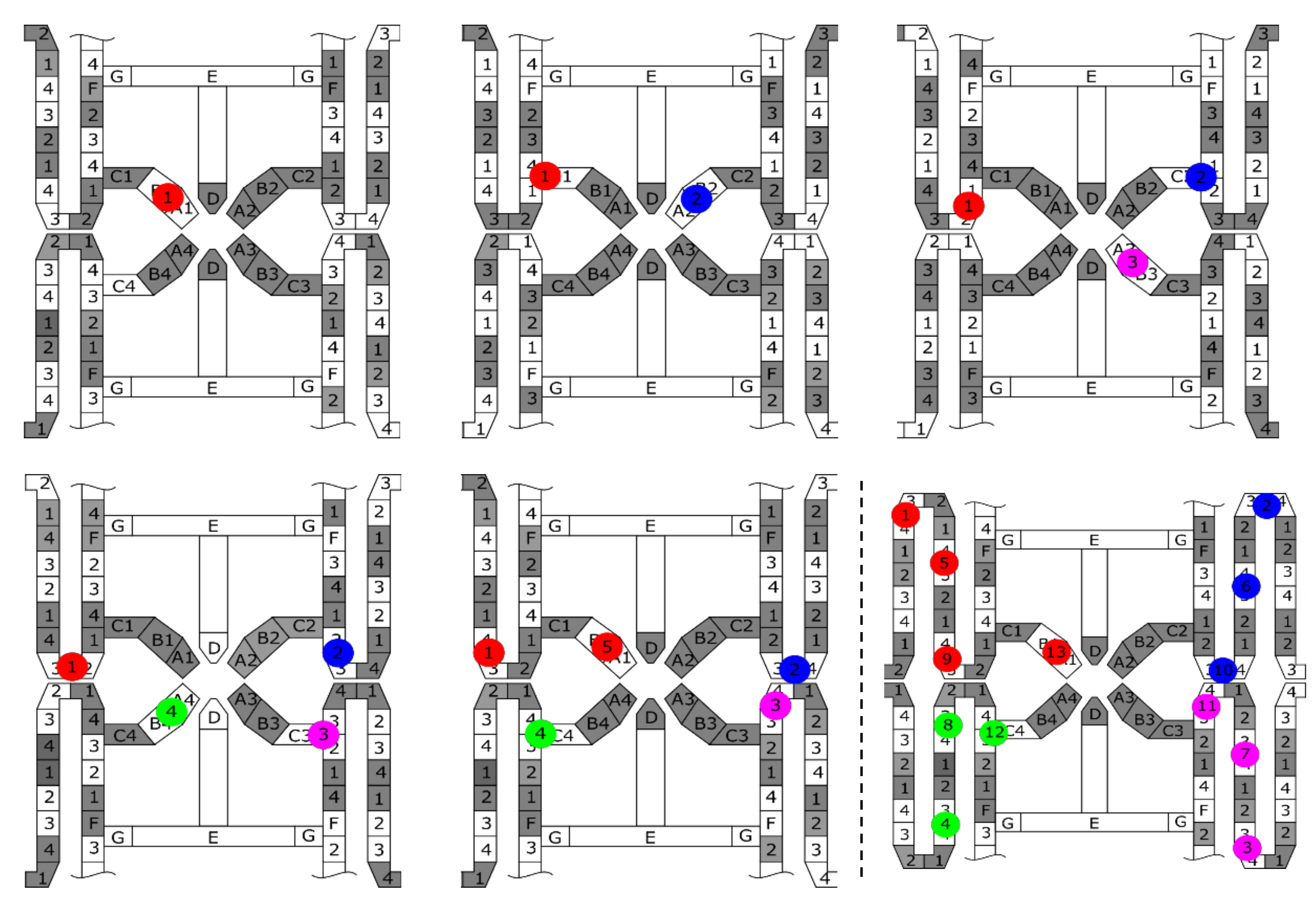

1.2. Pipeline Operation by Four Collection Gates and In-Pixel Four-Phase CCD Memories

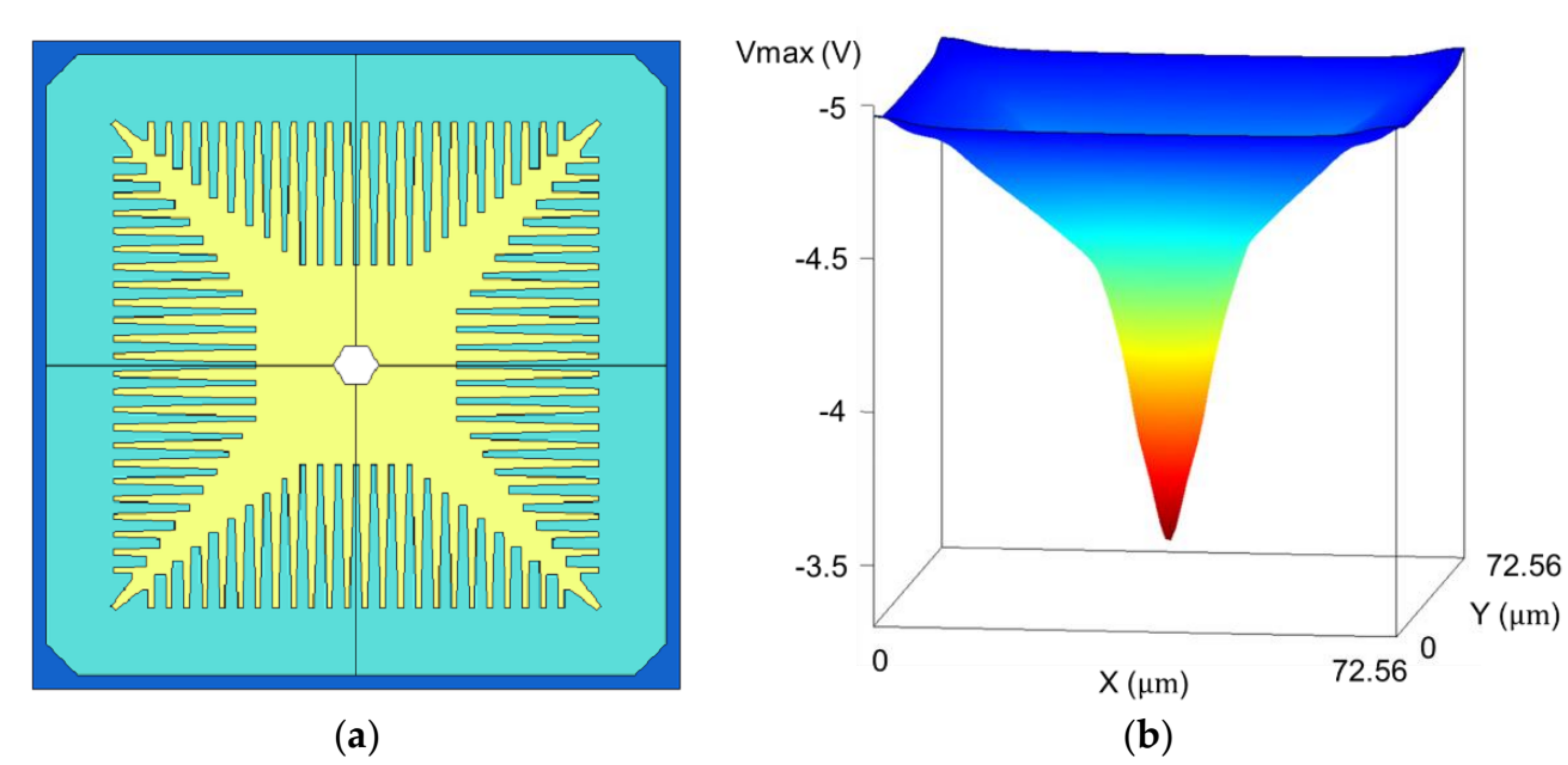

2. Design of Test Sensor

2.1. Specifications

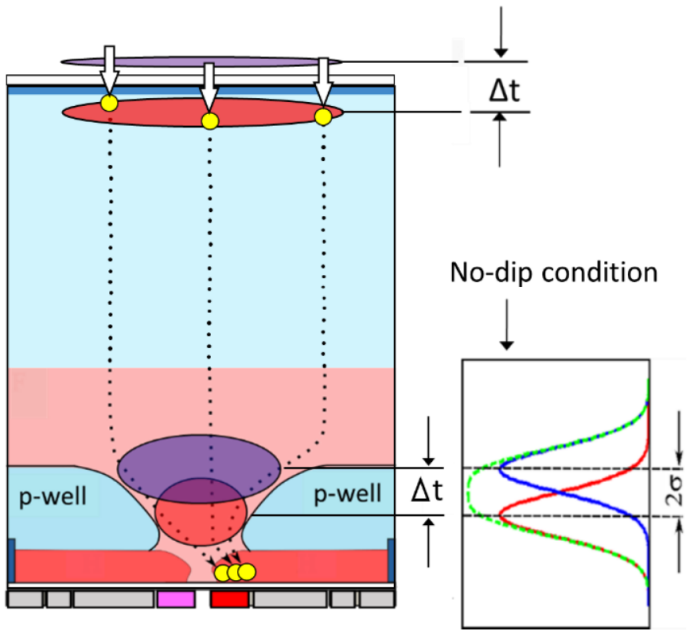

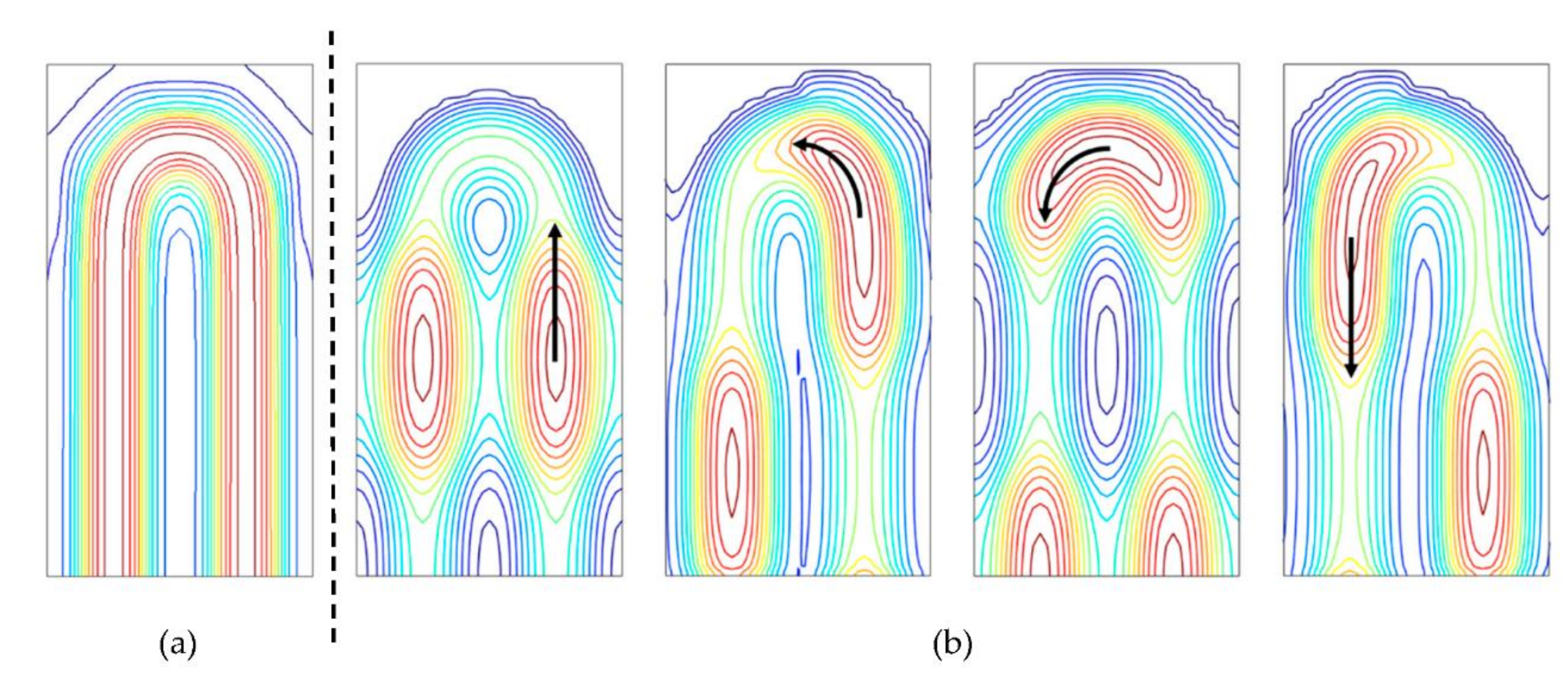

2.2. P-Well Design and Frame Rate Evaluation

- (1)

- p-well mask 1 (yellow): The first mask for the p-well covers the whole pixel area, except the center hole. The implantation energy is low.

- (2)

- p-well mask 2 (light blue): The second mask is designed like combs, with many straight twigs narrowing toward the tip from the four edges at the pixel boundaries.

- (3)

- p-well mask 3 (blue): The third mask simply covers the pixel boundary. The implantation energy was chosen at the practically highest value of the process provided by the foundry.

- (1)

- For the 100% fill factor, the frame interval of 18.1 ns (55.2 Mfps) can be achieved. Therefore, the design frame rate is set at 50 Mfps. Then, the design operation rate of the four collection gates and the in-pixel CCD memories are both 12.5 Mfps.

- (2)

- For the 10% fill factor, the frame interval of 2.75 ns (364 Mfps) can be achieved. The collection gates can be operated by a driver circuit on the driver chip stacked to the sensor chip.

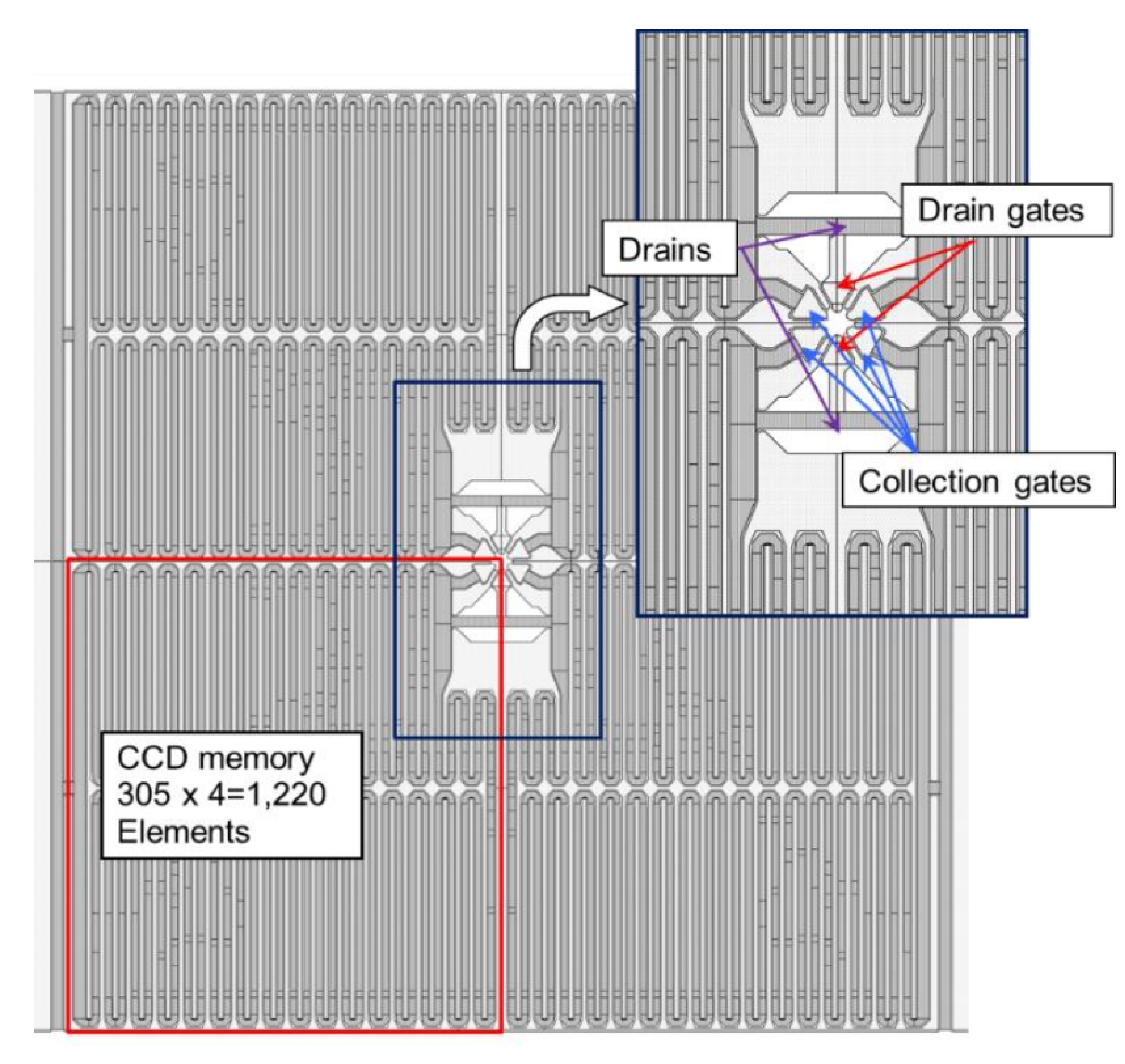

2.3. Folded Looped In-Pixel CCD Memory

3. Evaluation of Test Sensor

3.1. Pipe-Line Operation of Four Collection Gates and Four-Phase CCD

3.2. Frame Rate

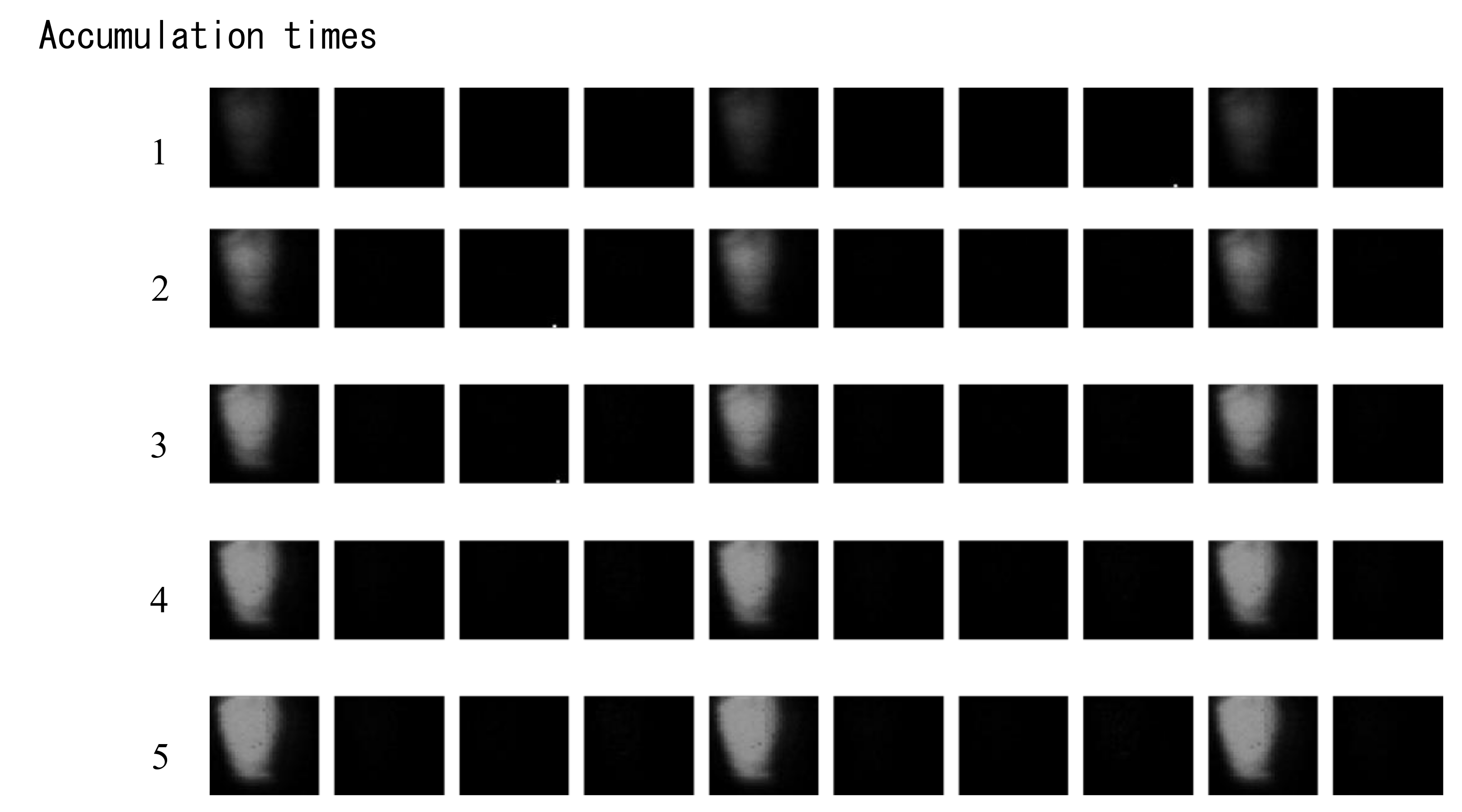

3.3. Image Signal Accumulation

3.4. Trouble Shooting of Major Problems

3.4.1. Maximum Frame Rate of the Sensor

3.4.2. Large Dark Current

4. Future BSI MCG ISAS

5. Concluding Remarks

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Etoh, T.G.; Dao, V.T.S.; Koike Akino, T.; Akino, T.; Nishi, K.; Kureta, M.; Arai, M. Ultra-high-speed image signal accumulation sensor. Sensors 2010, 10, 4100–4113. [Google Scholar] [CrossRef] [PubMed]

- Etoh, T.G.; Dao, V.T.S.; Yamada, T.; Charbon, E. Toward one giga frames per second-Evolution of in-Situ storage image sensors. Sensors 2013, 13, 4640–4658. [Google Scholar] [CrossRef] [PubMed]

- Etoh, T.G.; Nguyen, A.Q.; Kamakura, Y.; Shimonomura, K.; Le, T.H.; Mori, N. The theoretical highest frame rate of silicon image sensors. Sensors 2017, 17, 483. [Google Scholar] [CrossRef] [PubMed]

- Etoh, T.G.; Poggemann, D.; Kreider, G.; Mutoh, H.; Theuwissen, A.J.; Ruckelshausen, A.; Kondo, Y.; Maruno, H.; Takubo, K.; Soya, H.; et al. An image sensor which captures 100 consecutive frames at 1000000 frames/s. IEEE Trans. Electron Devices 2003, 50, 144–151. [Google Scholar] [CrossRef]

- Elloumi, M.; Fauvet, E.; Goujou, E.; Gorria, P. The study of a photosite for snapshot video. In Proceedings of the SPIE: International Congress on High Speed Imaging and Photonics (ICHSIP), Taejon, Korea, 29 August–2 September 1994; Volume 2513, pp. 259–267. [Google Scholar]

- Kosonocky, W.K.; Yang, G.; Ye, C.; Kabra, R.; Lawrence, J.; Mastrocolla, V.; Long, D.; Shallcross, F.; Patel, V. 360x360-element very high burst-frame rate image sensor. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 6–8 February 1996; pp. 182–183. [Google Scholar]

- Crooks, J.; Marsh, B.; Turchetta, R.; Taylor, K.; Chan, W.; Lahav, A.; Fenigstein, A. Kirana: A solid-state megapixel uCMOS image sensor for ultrahigh speed imaging. In Proceedings of the SPIE 8659(03), Sensors, Cameras, and Systems for Industrial and Scientific Applications XIV, Burlingame, CA, USA, 3 February 2013. [Google Scholar]

- Etoh, T.G.; Mutoh, H. Image Accumulation High-Speed Imaging Device. JP A 2011-082925, 9 October 2009. (In Japanese). [Google Scholar]

- Etoh, T.G.; Matshuoka, T. High-Sensitivity High-Speed Solid-State Image Sensor. JP A 2016-63530A, 20 September 2014. (In Japanese). [Google Scholar]

- Suzuki, M.; Suzuki, M.; Kuroda, R.; Sugawa, S. Electronic imaging, image sensors and imaging systems. In Proceedings of the Name of the 2018 IS&T International Symposium on Electronic Imaging, Burlingame, CA, USA, 28 January–1 February 2018; pp. 398-1–398-4. [Google Scholar]

| Sensor Structure | Functional Backside Illumination |

|---|---|

| Maximum Frame Rate | 25 Mfps (Target: 50 Mfps) |

| Pixel Count | 32 × 32 |

| Pixel Size | 72.56 µm × 72.56 µm |

| Fill Factor | 100% |

| Sensor Size | 3.6 mm × 4 mm |

| Number of Collection Gates | 4 |

| Number of Consecutive Frames | 1220 frames (305 memory elements/quadrant) |

| Size of CCD Elements | 1 µm × 3.2 µm |

| Charge Handling Capacity | 3000 electrons |

| Overwriting Drain | Installed |

| Transfer Scheme | four-phase transfer |

| Temperature of Sensor | −40 °C |

| Fill Factor | Mean | Standard Deviation σ | Temporal Resolution (Δt = 2σ) | 95% (t95) | t95/Δt |

|---|---|---|---|---|---|

| 100% | 7.81 ns | 5.51 ns | 11.02 ns | 18.1 ns | 1.64 |

| 25% | 2.62 ns | 1.99 ns | 3.98 ns | 6.60 ns | 1.66 |

| 10% | 1.31 ns | 0.81 ns | 1.62 ns | 2.75 ns | 1.70 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dao, V.T.S.; Ngo, N.; Nguyen, A.Q.; Morimoto, K.; Shimonomura, K.; Goetschalckx, P.; Haspeslagh, L.; De Moor, P.; Takehara, K.; Etoh, T.G. An Image Signal Accumulation Multi-Collection-Gate Image Sensor Operating at 25 Mfps with 32 × 32 Pixels and 1220 In-Pixel Frame Memory. Sensors 2018, 18, 3112. https://doi.org/10.3390/s18093112

Dao VTS, Ngo N, Nguyen AQ, Morimoto K, Shimonomura K, Goetschalckx P, Haspeslagh L, De Moor P, Takehara K, Etoh TG. An Image Signal Accumulation Multi-Collection-Gate Image Sensor Operating at 25 Mfps with 32 × 32 Pixels and 1220 In-Pixel Frame Memory. Sensors. 2018; 18(9):3112. https://doi.org/10.3390/s18093112

Chicago/Turabian StyleDao, Vu Truong Son, Nguyen Ngo, Anh Quang Nguyen, Kazuhiro Morimoto, Kazuhiro Shimonomura, Paul Goetschalckx, Luc Haspeslagh, Piet De Moor, Kohsei Takehara, and Takeharu Goji Etoh. 2018. "An Image Signal Accumulation Multi-Collection-Gate Image Sensor Operating at 25 Mfps with 32 × 32 Pixels and 1220 In-Pixel Frame Memory" Sensors 18, no. 9: 3112. https://doi.org/10.3390/s18093112