A High Full Well Capacity CMOS Image Sensor for Space Applications

Abstract

:1. Introduction

2. Sensor Architecture

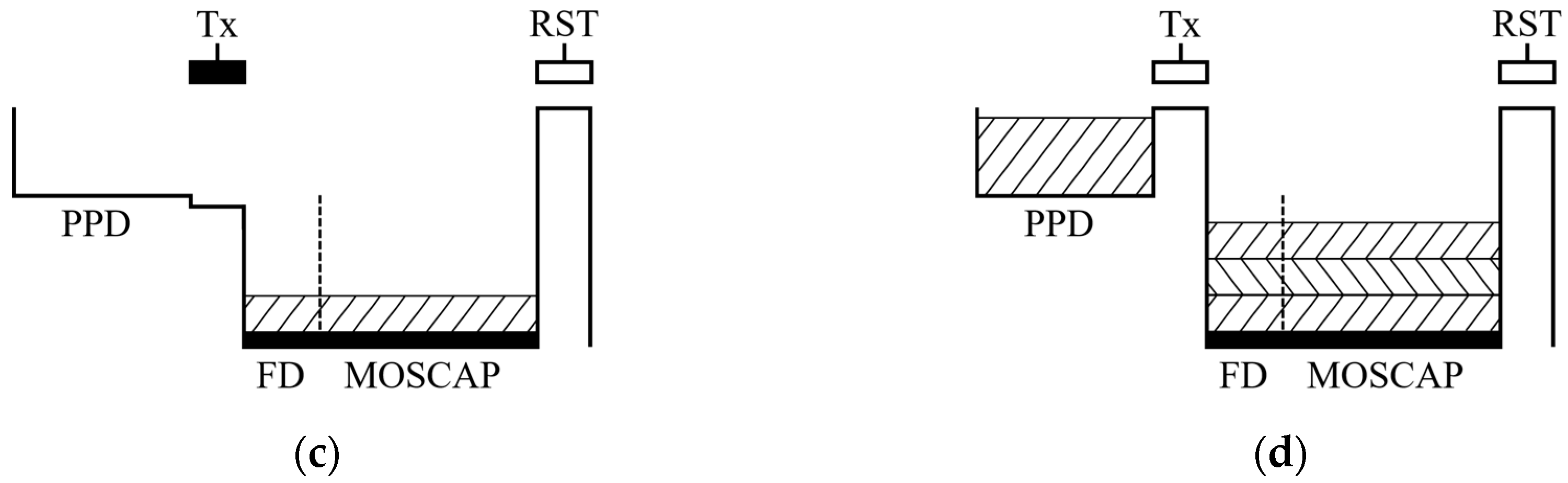

2.1. Proposed Pixel Design with Multiple Charge Transfer

2.2. Pixel Operation for Multiple Charge Transfer

2.3. Pixel Design for Modulation Transfer Function

2.4. Readout Circuit Design and Operation Procedure

2.5. Radiation Damage Effects on the Proposed Pixel Structure

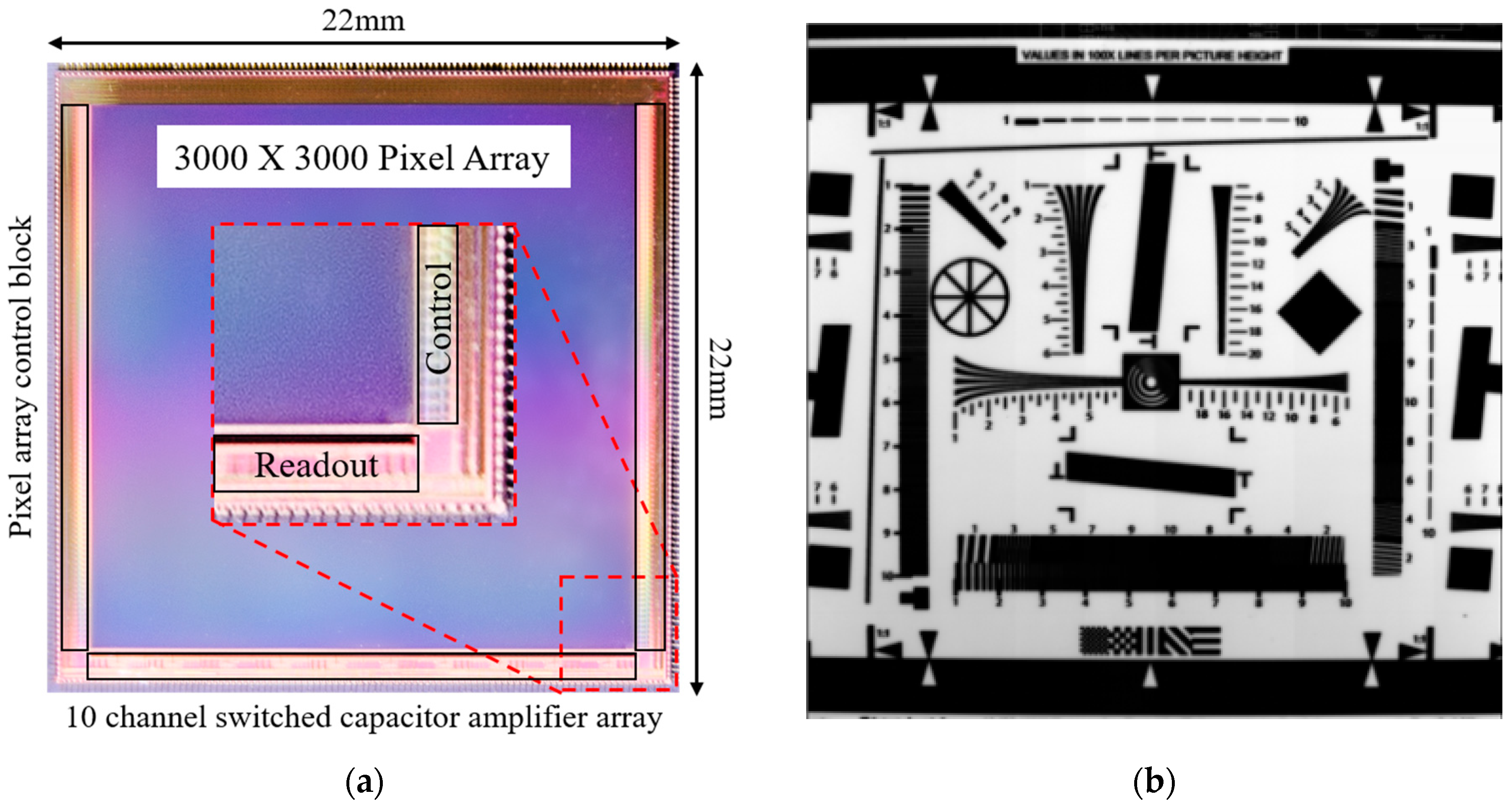

3. Experimental Results

3.1. Overall Performance with Enhanced Full Well Capacity

3.2. MTF Measurement Results

3.3. Radiation

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Bigas, M.; Cabruja, E.; Forest, J.; Salvi, J. Review of CMOS image sensors. Microelectron. J. 2006, 37, 433–451. [Google Scholar] [CrossRef] [Green Version]

- Hancock, B.R.; Stirbl, R.C.; Cunningham, T.J.; Pain, B.; Wrigley, C.J.; Ringold, P.G. CMOS active pixel sensor specific performance effects on star tracker/imager position accuracy. In Functional Integration of Opto-Electro-Mechanical Devices and Systems; International Society for Optics and Photonics: Bellingham, WA, USA, 2001; Volume 4284. [Google Scholar]

- Radhakrishnan, R.; Edmonson, W.W.; Afghah, F.; Rodriguez-Osorio, R.M.; Pinto, F.; Burleigh, S.C. Survey of Inter-Satellite Communication for Small Satellite Systems: Physical Layer to Network Layer View. IEEE Commun. Surv. Tutor. 2016, 18, 2442–2473. [Google Scholar] [CrossRef]

- Martin-Gonthier, P.; Magnan, P.; Corbière, F.; Estribeau, M.; Huger, N.; Boucher, L. Dynamic range optimisation of CMOS image sensors dedicated to space applications. Proc. SPIE 2007, 6744, 67440U. [Google Scholar] [CrossRef]

- Meynart, R.; Martin-Gonthier, P.; Neeck, S.P.; Magnan, P.; Corbiere, F.; Shimoda, H. Overview of CMOS process and design options for image sensor dedicated to space applications. In Sensors, Systems, and Next-Generation Satellites IX; International Society for Optics and Photonics: Bellingham, WA, USA, 2005. [Google Scholar]

- Beletic, J.; Holland, A.D.; Woffinden, C.; Swindells, I.; Pratlong, J.; Jerram, P.; Cassidy, R.; Bourke, D.; Jorden, P.R. Teledyne e2v sensors optimised for ground-based and space applications. In High Energy, Optical, and Infrared Detectors for Astronomy VIII; International Society for Optics and Photonics: Bellingham, WA, USA, 2018. [Google Scholar]

- Delabie, T.; De Schutter, J.; Vandenbussche, B. An Accurate and Efficient Gaussian Fit Centroiding Algorithm for Star Trackers. J. Astronaut. Sci. 2014, 61, 60–84. [Google Scholar] [CrossRef] [Green Version]

- Decker, S.; McGrath, R.D.; Brehmer, K.; Sodini, C.G. A 256 × 256 CMOS imaging array with wide dynamic range pixels and column-parallel digital output. IEEE J. Solid-State Circuits 1998, 33, 2081–2091. [Google Scholar] [CrossRef]

- Kavadias, S.; Dierickx, B.; Scheffer, D.; Alaerts, A.; Uwaerts, D.; Bogaerts, J. A logarithmic response CMOS image sensor with on-chip calibration. IEEE J. Solid-State Circuits 2000, 35, 1146–1152. [Google Scholar] [CrossRef]

- Bae, M.; Jo, S.H.; Choi, B.S.; Lee, H.H.; Choi, P.; Shin, J.K. Wide dynamic range linear-logarithmic CMOS image sensor using photogate and cascode MOSFET. Electron. Lett. 2016, 52, 198–199. [Google Scholar] [CrossRef]

- Lepage, G.; Materne, A.; Renard, C. A CMOS image sensor for Earth observation with high efficiency snapshot shutter. In Proceedings of the 2007 International Image Sensor Workshop, Ogunquit, ME, USA, 7–10 June 2007. [Google Scholar]

- Ogiers, W.; Uwaerts, D.; Dierickx, B.; Scheffer, D.; Meynants, G.; Truzzi, C. COMPACT CMOS VISION SYSTEMS FOR SPACE USE. In Proceedings of the 2nd Roundtable Micro-Nano Technol. Space ESA/ESTEC, Noordwijk, The Netherlands, 15–17 October 1999. [Google Scholar]

- Meynart, R.; Estribeau, M.; Neeck, S.P.; Magnan, P.; Shimoda, H. CMOS pixels crosstalk mapping and its influence on measurements accuracy for space applications. In Sensors, Systems, and Next-Generation Satellites IX; International Society for Optics and Photonics: Bellingham, WA, USA, 2005. [Google Scholar]

- Hsu, T.H.; Fang, Y.K.; Lin, C.Y.; Chen, S.F.; Lin, C.S.; Yaung, D.N.; Wuu, S.G.; Chien, H.C.; Tseng, C.H.; Lin, J.S.; et al. Light Guide for Pixel Crosstalk Improvement in Deep Submicron CMOS Image Sensor. IEEE Electron Device Lett. 2004, 25, 22–24. [Google Scholar] [CrossRef]

- Furumiya, M.; Ohkubo, H.; Muramatsu, Y.; Kurosawa, S.; Okamoto, F.; Fujimoto, Y.; Nakashiba, Y. High-sensitivity and no-crosstalk pixel technology for embedded CMOS image sensor. IEEE Trans. Electron Devices 2001, 48, 2221–2227. [Google Scholar] [CrossRef]

- Fleetwood, D.M. Evolution of Total Ionizing Dose Effects in MOS Devices With Moore’s Law Scaling. IEEE Trans. Nucl. Sci. 2018, 65, 1465–1481. [Google Scholar] [CrossRef]

- Schwank, J.R.; Shaneyfelt, M.R.; Fleetwood, D.M.; Felix, J.A.; Dodd, P.E.; Paillet, P.; Ferlet-Cavrois, V. Radiation Effects in MOS Oxides. IEEE Trans. Nucl. Sci. 2008, 55, 1833–1853. [Google Scholar] [CrossRef]

- Ma, C.; Liu, Y.; Li, Y.; Zhou, Q.; Wang, X.; Chang, Y. A 4-M Pixel High Dynamic Range, Low-Noise CMOS Image Sensor with Low-Power Counting ADC. IEEE Trans. Electron Devices 2017, 64, 3199–3205. [Google Scholar] [CrossRef]

- Fujihara, Y.; Nasuno, S.; Wakashima, S.; Aoyagi, Y.; Kuroda, R.; Sugawa, S. 190–1100 nm Waveband multispectral imaging system using high light resistance wide dynamic range CMOS image sensor. In Proceedings of the 2016 IEEE Sensors, Orlando, FL, USA, 30 October–3 November 2016; pp. 1–3. [Google Scholar]

- Wakashima, S.; Kusuhara, F.; Kuroda, R.; Sugawa, S. A linear response single exposure CMOS image sensor with 0.5 e− readout noise and 76 ke− full well capacity. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. C88–C89. [Google Scholar]

- Yeh, S.-F.; Hsieh, C.-C. Novel Single-Slope ADC Design for Full Well Capacity Expansion of CMOS Image Sensor. IEEE Sens. J. 2013, 13, 1012–1017. [Google Scholar] [CrossRef]

- Seo, M.-W.; Suh, S.-H.; Iida, T.; Takasawa, T.; Isobe, K.; Watanabe, T.; Itoh, S.; Yasutomi, K.; Kawahito, S. A Low-Noise High Intrascene Dynamic Range CMOS Image Sensor With a 13 to 19b Variable-Resolution Column-Parallel Folding-Integration/Cyclic ADC. IEEE J. Solid-State Circuits 2012, 47, 272–283. [Google Scholar] [CrossRef]

- Sakakibara, M.; Oike, Y.; Takatsuka, T.; Kato, A.; Honda, K.; Taura, T.; Machida, T.; Okuno, J.; Ando, A.; Fukuro, T.; et al. An 83dB-dynamic-range single-exposure global-shutter CMOS image sensor with in-pixel dual storage. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 380–382. [Google Scholar]

- Blouke, M.M.; Estribeau, M.; Magnan, P. Pixel crosstalk and correlation with modulation transfer function of CMOS image sensor. In Sensors and Camera Systems for Scientific and Industrial Applications VI; International Society for Optics and Photonics: Bellingham, WA, USA, 2005. [Google Scholar]

- Culurciello, E.; Etienne-Cummings, R.; Boahen, K. High dynamic range, arbitrated address event representation digital imager. In Proceedings of the 2001 IEEE International Symposium on Circuits and Systems, Sydney, NSW, Australia, 6–9 May 2001; Volume 2, pp. 505–508. [Google Scholar] [CrossRef]

- Mizobuchi, K.; Adachi, S.; Akahane, N.; Sawada, H.; Ohta, K.; Oshikubo, H.; Sugawa, S. 4.5 µm Pixel Pitch 154 ke- Full Well Capacity CMOS Image Sensor. In Proceedings of the International Image Sensor Workshop, Bergen, Norway, 25–28 June 2009; pp. 235–238. [Google Scholar]

- Goiffon, V.; Estribeau, M.; Michelot, J.; Cervantes, P.; Pelamatti, A.; Marcelot, O.; Magnan, P. Pixel Level Characterization of Pinned Photodiode and Transfer Gate Physical Parameters in CMOS Image Sensors. IEEE J. Electron Devices Soc. 2014, 2, 65–76. [Google Scholar] [CrossRef] [Green Version]

- El Gamal, A.; Eltoukhy, H. CMOS image sensors. IEEE Circuits Devices Mag. 2005, 21, 6–20. [Google Scholar] [CrossRef]

- Catrysse, P.B.; Blouke, M.M.; Liu, X.; Sampat, N.; Williams, J.G.M.; El Gamal, A.; Yeh, T. QE reduction due to pixel vignetting in CMOS image sensors. In Sensors and Camera Systems for Scientific, Industrial, and Digital Photography Applications; International Society for Optics and Photonics: Bellingham, WA, USA, 2000. [Google Scholar]

- Hopkins, I.H.; Hopkinson, G.R. Random telegraph signals from proton-irradiated CCDs. IEEE Trans. Nucl. Sci. 1993, 40, 1567–1574. [Google Scholar] [CrossRef]

- Virmontois, C.; Goiffon, V.; Magnan, P.; Girard, S.; Inguimbert, C.; Petit, S.; Rolland, G.; Saint-Pe, O. Displacement Damage Effects Due to Neutron and Proton Irradiations on CMOS Image Sensors Manufactured in Deep Submicron Technology. IEEE Trans. Nucl. Sci. 2010, 57, 3101–3108. [Google Scholar] [CrossRef]

- Virmontois, C.; Goiffon, V.; Magnan, P.; Saint-Pe, O.; Girard, S.; Petit, S.; Rolland, G.; Bardoux, A. Total Ionizing Dose Versus Displacement Damage Dose Induced Dark Current Random Telegraph Signals in CMOS Image Sensors. IEEE Trans. Nucl. Sci. 2011, 58, 3085–3094. [Google Scholar] [CrossRef] [Green Version]

- Eid, E.S.; Chan, T.Y.; Fossurn, E.R.; Tsai, R.H.; Spagnuolo, R.; Deily, J.; Byers, W.B.; Peden, J.C. Design and characterization of ionizing radiation-tolerant CMOS APS image sensors up to 30 Mrd (Si) total dose. IEEE Trans. Nucl. Sci. 2001, 48, 1796–1806. [Google Scholar] [CrossRef] [Green Version]

- Goiffon, V.; Virmontois, C.; Magnan, P.; Cervantes, P.; Place, S.; Gaillardin, M.; Girard, S.; Paillet, P.; Estribeau, M.; Martin-Gonthier, P. Identification of Radiation Induced Dark Current Sources in Pinned Photodiode CMOS Image Sensors. IEEE Trans. Nucl. Sci. 2012, 59, 918–926. [Google Scholar] [CrossRef] [Green Version]

- Becker, H.N.; Johnston, A.H. Dark current degradation of near infrared avalanche photodiodes from proton irradiation. IEEE Trans. Nucl. Sci. 2004, 51, 3572–3578. [Google Scholar] [CrossRef]

- Goiffon, V.; Magnan, P.; Saint-pe, O.; Bernard, F.; Rolland, G. Total Dose Evaluation of Deep Submicron CMOS Imaging Technology Through Elementary Device and Pixel Array Behavior Analysis. IEEE Trans. Nucl. Sci. 2008, 55, 3494–3501. [Google Scholar] [CrossRef] [Green Version]

- Winokur, P.S.; Boesch, H.E.; McGarrity, J.M.; McLean, F.B. Field- and Time-Dependent Radiation Effects at the SiO2/Si Interface of Hardened MOS Capacitors. IEEE Trans. Nucl. Sci. 1977, 24, 2113–2118. [Google Scholar] [CrossRef]

- Benedetto, J.M.; Boesch, H.E. Mosfet and MOS Capacitor Responses to Ionizing Radiation. IEEE Trans. Nucl. Sci. 1984, 31, 1461–1466. [Google Scholar] [CrossRef]

- Saks, N.S.; Ancona, M.G.; Modolo, J.A. Radiation Effects in MOS Capacitors with Very Thin Oxides at 80 degK. IEEE Trans. Nucl. Sci. 1984, 31, 1249–1255. [Google Scholar] [CrossRef]

- Winokur, P.S.; Schwank, J.R.; McWhorter, P.J.; Dressendorfer, P.V.; Turpin, D.C. Correlating the Radiation Response of MOS Capacitors and Transistors. IEEE Trans. Nucl. Sci. 1984, 31, 1453–1460. [Google Scholar] [CrossRef]

- Saks, N.S.; Ancona, M.G.; Modolo, J.A. Generation of Interface States by Ionizing Radiation in Very Thin MOS Oxides. IEEE Trans. Nucl. Sci. 1986, 33, 1185–1190. [Google Scholar] [CrossRef] [Green Version]

- Bhat, N.; Vasi, J. Interface-state generation under radiation and high-field stressing in reoxidized nitrided oxide MOS capacitors. IEEE Trans. Nucl. Sci. 1992, 39, 2230–2235. [Google Scholar] [CrossRef] [Green Version]

- Boukhayma, A.; Peizerat, A.; Enz, C. A Sub-0.5 Electron Read Noise VGA Image Sensor in a Standard CMOS Process. IEEE J. Solid-State Circuits 2016, 51, 2180–2191. [Google Scholar] [CrossRef]

- Magali Estribeau, P.M. Fast MTF measurement of CMOS imagers at the chip level using ISO 12233 slanted-edge methodology. In Sensors, Systems, and Next-Generation Satellites VIII, (4 November 2004); International Society for Optics and Photonics: Bellingham, WA, USA, 2004; Volume 5570. [Google Scholar] [CrossRef]

- Gomez Rojas, L.; Chang, M.; Hopkinson, G.; Duvet, L. Radiation effects in the LUPA4000 CMOS image sensor for space applications. In Proceedings of the 2011 12th European Conference on Radiation and Its Effects on Components and Systems, Sevilla, Spain, 19–23 September 2011; pp. 800–805. [Google Scholar]

- Semiconductor, O. NOIH2SM1000A: HAS2 Image Sensor. Available online: https://upverter.com/datasheet/1dbf6474f4834c5ac73294b488ac44ae8ac1f8ca.pdf (accessed on 3 March 2019).

- CYPRESS. STAR1000: 1M Pixel Radiation Hard CMOS Image Sensor. Available online: https://www.cypress.com/file/98376/download (accessed on 3 March 2019).

- Innocent, M.; Cools, T.; Luypaert, C.; Esquenet, C.; Janssens, S.; Vroom, W.; De Bondt, J.; Mudegowdar, I.C.; Pintens, P.; Deruytere, P.; et al. HAS3: A Radiation Tolerant CMOS Image Sensor for Space Applications. In Proceedings of the International Image Sensor Society, Hiroshima, Japan, 30 May–2 June 2017. [Google Scholar]

| Parameter | Value |

|---|---|

| Technology | 0.11 μm CMOS |

| Pixel Pitch | 6.5 μm × 6.5 μm |

| Resolution | 3000 × 3000 pixels |

| Chip size | 22 mm × 22 mm |

| Fill factor | 67% |

| Output voltage swing Vsat (gain=1) | 1 V |

| Modulation transfer function (MTF) at Nyquist | 0.4 |

| Conversion gain | 8.55 μV/e− |

| FD capacitance | 19.6 fF |

| Full well capacity | 103,448 e− |

| CIS read noise | 24.7 e− |

| Dynamic range | 72.4 dB |

| Quantum efficiency @ 550 nm | 68.4% |

| MTF (Horizontal) | MTF (Vertical) | |

|---|---|---|

| Metal covering | 0.402 | 0.406 |

| Without covering | 0.131 | 0.406 |

| Improvement (%) | 307 | 0 |

| This work | [45] | [46] | [47] | [48] | ||

|---|---|---|---|---|---|---|

| Pre-Rad | 133 | 6600 | 190 | 3135 | 20 | |

| TID * (Percentage increase) | 491 (368%) | 932 (700%) | 180,000 (2727%) | 1554 (818%) | 6110 (195%) | N/A |

| Proton ** (Percentage increase) | 623 (468%) | 2585 (1941%) | N/A | N/A | N/A | 500 (2500%) |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, W.-T.; Park, C.; Lee, H.; Lee, I.; Lee, B.-G. A High Full Well Capacity CMOS Image Sensor for Space Applications. Sensors 2019, 19, 1505. https://doi.org/10.3390/s19071505

Kim W-T, Park C, Lee H, Lee I, Lee B-G. A High Full Well Capacity CMOS Image Sensor for Space Applications. Sensors. 2019; 19(7):1505. https://doi.org/10.3390/s19071505

Chicago/Turabian StyleKim, Woo-Tae, Cheonwi Park, Hyunkeun Lee, Ilseop Lee, and Byung-Geun Lee. 2019. "A High Full Well Capacity CMOS Image Sensor for Space Applications" Sensors 19, no. 7: 1505. https://doi.org/10.3390/s19071505