Small-Area Radiofrequency-Energy-Harvesting Integrated Circuits for Powering Wireless Sensor Networks

Abstract

:1. Introduction

2. Circuit Topology of RF-Energy-Harvesting Integrated Circuit

2.1. Matching Network

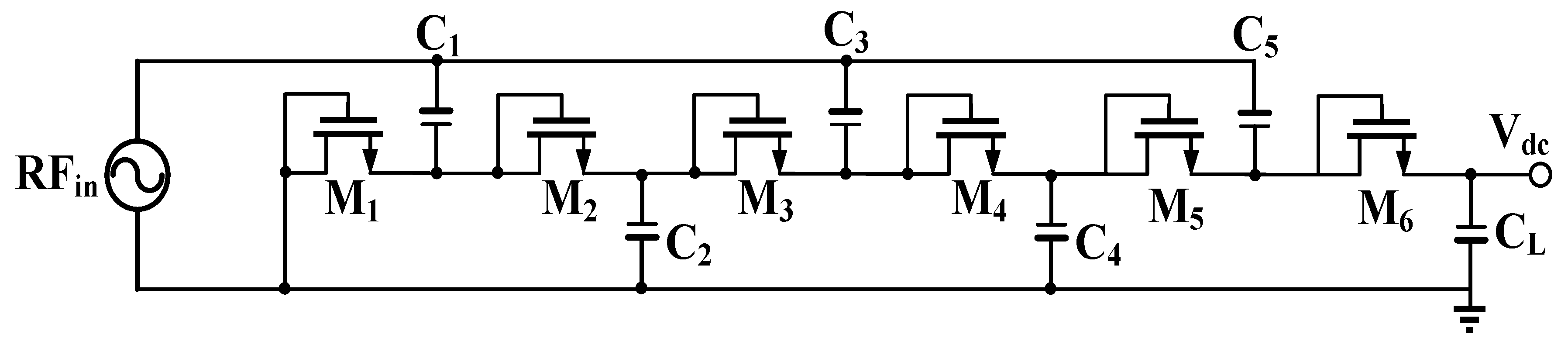

2.2. RF-DC Rectifier

2.3. Over-Voltage Protection Circuit

2.4. Low-Voltage Low-Dropout Regulator

2.5. Charge Control Circuit

3. Simulated and Measured Results

4. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Bito, J.; Hester, J.G.; Tentzeris, M.M. Ambient RF energy harvesting from a two-way talk radio for flexible wearable wireless sensor devices utilizing inkjet printing technologies. IEEE Trans. Microw. Theory Tech. 2015, 63, 4533–4543. [Google Scholar] [CrossRef]

- Tian, M.; Wang, N.; Wang, K.; Jia, H.; Li, Z.; Yang, X.; Wang, L. A wire-embedded converter used for wearable devices. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 121–125. [Google Scholar]

- Nguyen, S.H.; Ellis, N.; Amirtharajah, R. Powering smart jewelry using an RF energy harvesting necklace. In Proceedings of the IEEE MTT-S International Microwave Symposium (IMS), San Francisco, CA, USA, 22–27 May 2016; pp. 1–4. [Google Scholar]

- Rastmanesh, M. High Efficiency RF to DC Converter with Reduced Leakage Current for RFID Applications. Master’s Thesis, Dalhousie University, Halifax, NS, Canada, April 2013. [Google Scholar]

- Le, T.; Mayaram, K.; Fiez, T. Efficient far-field radio frequency energy harvesting for passively powered sensor networks. IEEE J. Solid-State Circuits 2008, 43, 1287–1302. [Google Scholar] [CrossRef]

- Papotto, G.; Carrara, F.; Palmisano, G. A 90-nm CMOS threshold-compensated RF energy harvester. IEEE J. Solid-State Circuits 2011, 46, 1985–1997. [Google Scholar] [CrossRef]

- Udupa, S.S.; Sushma, P.S. An orthogonally switching charge pump rectifier for RF energy harvester. In Proceedings of the 2nd IEEE International Conference on Recent Trends in Electronics Information & Communication Technology (RTEICT), Bangalore, India, 19–20 May 2017; pp. 447–450. [Google Scholar]

- Pasha, M.A.; Derrien, S.; Sentieys, O. A complete design-flow for the generation of ultra low-power WSN node architectures based on micro-tasking. In Proceedings of the Design Automation Conference, Anaheim, CA, USA, 13–18 June 2010; pp. 693–698. [Google Scholar]

- Shigeta, R.; Sasaki, T.; Quan, D.M.; Kawahara, Y.; Vyas, R.J.; Tentzeris, M.M.; Asami, T. Ambient RF energy harvesting sensor device with capacitor-leakage-aware duty cycle control. IEEE Sens. J. 2013, 13, 2973–2983. [Google Scholar] [CrossRef]

- Harpawi, N. Design energy harvesting device of UHF TV stations. In Proceedings of the 2014 8th International Conference on Telecommunication Systems Services and Applications (TSSA), Denpasar, Indonesia, 23–24 October 2014; pp. 1–6. [Google Scholar]

- Jesus, A.L.G.; Agustin, C.L.; Angel, F.M.; Javier, J.M.F.; Marco, T.P.; Antonia, C.C.; Alfredo, M.S.; Jaime, A.Q. Medium and short wave RF energy harvester for powering wireless sensor networks. Sensors 2018, 18, 768. [Google Scholar]

- Vullers, R.J.M.; Van Schaijk, R.; Doms, I.; Van Hoof, C.; Mertens, R. Micropower energy harvesting. Solid State Electron. 2009, 53, 684–693. [Google Scholar] [CrossRef]

- Harb, A. Energy harvesting: State-of-the-art. Renew. Energy 2011, 36, 2641–2654. [Google Scholar] [CrossRef]

- Piñuela, M.; Mitcheson, P.D.; Lucyszyn, S. Ambient RF energy harvesting in urban and semi-urban environments. IEEE Trans. Microw. Theory Tech. 2013, 61, 2715–2726. [Google Scholar]

- Zhang, Y.; Zhang, F.; Shakhsheer, Y.; Silver, J.D.; Klinefelter, A.; Nagaraju, M.; Boley, J.; Pandey, J.; Shrivastava, A.; Carlson, E.J.; et al. A batteryless 19 uW MICS/ISM-band energy harvesting body sensor node SoC for ExG applications. IEEE J. Solid-State Circuits 2013, 48, 199–213. [Google Scholar] [CrossRef]

- Zeng, Z.; Li, X.; Bermak, A.; Tsui, C.Y.; Ki, W.H. A WLAN 2.4-GHz RF energy harvesting system with reconfigurable rectifier for wireless sensor network. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 1–5. [Google Scholar]

- Aboueidah, H.; Abbas, N.; El-Nachar, N.; Al-Yousef, A.; Alhawari, M.; Mohammad, B.; Saleh, H.; Assaf, T.; Ismail, M. Characterization of RF energy harvesting at 2.4 GHz. In Proceedings of the 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Batumi, Georgia, 5–8 December 2017; pp. 446–449. [Google Scholar]

- RF Energy Harvesting and Wireless Power for Micro-Power Applications/Powercaster Transmitter/TX91501-3W User Manual. Powercast Corp. 2018. Available online: http://www.powercastco.com/products/ powercaster-transmitter/ (accessed on 1 January 2019).

- Ouda, M.H.; Arsalan, M.; Marnat, L.; Shamim, A.; Salama, K.N. 5.2-GHz RF power harvester in 0.18 um CMOS for implantable intraocular pressure monitoring. IEEE Trans. Microw. Theory Tech. 2013, 61, 2177–2184. [Google Scholar] [CrossRef]

- Yuan, F.; Soltani, N. Design techniques for power harvesting of passive wireless microsensors. In Proceedings of the 51st Midwest Symposium on Circuits and Systems, Knoxville, TN, USA, 10–13 August 2008; pp. 289–293. [Google Scholar]

- Hsieh, P.H.; Chou, C.H.; Chiang, T. An RF energy harvester with 44.1% PCE at input available power of-12 dBm. IEEE Trans. Biomed. Circuits Syst. 2015, 62, 1528–1537. [Google Scholar] [CrossRef]

- Yi, J.; Ki, W.H.; Tsui, C.Y. Analysis and design strategy of UHF micro-power CMOS rectifiers for micro-sensor and RFID applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 153–166. [Google Scholar] [CrossRef]

- Liu, C.C.; Chen, C.H. An ultra-low power voltage regulator for RFID application. In Proceedings of the IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS), Columbus, OH, USA, 4–7 August 2013; pp. 780–783. [Google Scholar]

- Zhuang, H.; Zhu, Z.; Yang, Y. A 19-nW 0.7-V CMOS voltage reference with no amplifiers and no clock circuits. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 830–834. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuits; International Edition; McGRAW-HILL: New York, NY, USA, 2001. [Google Scholar]

- Sun, M.; Ranasinghe, D.; Said, F.; Al-Sarawi, S.F. RF energy harvester with peak power conversion efficiency tracking. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Jeju, Korea, 25–28 October 2016; pp. 107–110. [Google Scholar]

- Li, M.; Zhou, Y.; Wang, D.; Yuan, S.; Luan, W.; Lin, X.; Wang, Z.; Zhang, C.; Xie, X. A max mode control LDO with a good behavior at PSRR and line regulation and load regulation. In Proceedings of the 13th International Conference on Electron Devices and Solid-State Circuits (EDSSC), Hsinchu, Taiwan, 18–20 October 2017; pp. 1–2. [Google Scholar]

- Yao, C.Y.; Hsia, W.C. A-21.2 dBm dual-channel UHF passive CMOS RFID tag design. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1269–1279. [CrossRef]

- Lu, Y.; Dai, H.; Huang, M.; Law, M.K.; Sin, S.W.; U, S.P.; Martins, R.P. A wide input range dual-path CMOS rectifier for RF energy harvesting. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 166–170. [Google Scholar]

- Noghabaei, S.M.; Radin, R.L.; Savaria, Y.; Sawan, M. A high-efficiency ultra-low-power CMOS rectifier for RF energy harvesting applications. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–4. [Google Scholar]

- Chang, Y.W.; Yu, M.C.; Lin, H.J.; Li, C.H. Compact low-cost five-band RF energy harvester using system-in-package integration. In Proceedings of the IEEE Radio and Wireless Symposium (RWS), Anaheim, CA, USA, 15–18 January 2018; pp. 284–286. [Google Scholar]

- Vamsi, N.; Priya, V.; Dutta, A.; Singh, S.G. A 1 V, −26 dBm sensitive auto configurable mixed converter mode RF energy harvesting with wide input range. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 1534–1537. [Google Scholar]

- Moghaddam, A.K.; Chuah, J.H.; Ramiah, H.; Ahmadian, J.; Mak, P.I.; Rui, P.; Martins, R.P. A 73.9%-efficiency CMOS rectifier using a lower DC feeding (LDCF) self-body-biasing technique for far-field RF energy-harvesting systems. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 992–1002. [Google Scholar] [CrossRef]

- Lau, W.W.Y.; Siek, L. 2.45 GHz wide input range CMOS rectifier for RF energy harvesting. In Proceedings of the 2017 IEEE Wireless Power Transfer Conference (WPTC), Taipei, Taiwan, 10–12 May 2017; pp. 1–4. [Google Scholar]

- Dallago, E.; Barnabei, A.L.; Liberale, A.; Malcovati, P.; Venchi, G. An interface circuit for low-voltage low-current energy harvesting systems. IEEE Trans. Power Electron. 2015, 30, 1411–1420. [Google Scholar] [CrossRef]

- Ghosh, S.; Wang, H.T.; Leon-Salas, W.D. A circuit for energy harvesting using on-chip solar cells. IEEE Trans. Power Electron. 2014, 29, 4658–4671. [Google Scholar] [CrossRef]

| Reference (year) | [19] 2013 | [28] (2014) | [29] (2017) | This Work |

|---|---|---|---|---|

| Process | 0.18 μm | 0.18 μm | 65 nm | 0.18 μm |

| Input power | −7 dBm | −21.2 dBm | −17.7 dBm | −7 dBm |

| RF frequency | 5.2 GHz | 925 MHz | 900 MHz | 915 MHz |

| Rectifier stages | 5 | 7 | 5 | 6 |

| Matching circuit | On-chip | Off-chip | Off-chip | Off-chip |

| Maximum PCE | 42% | 43% | 36.5% | 43.6% |

| Parameters | Designed Specifications |

|---|---|

| Technology process | TSMC 0.18 μm 1P6M CMOS process |

| RF frequency (fin) | 915 MHz |

| Input power range (Pin) | −13 ~ +20 dBm |

| Output dc voltage (Vdc) | 1.773 ~ 1.809 V |

| Maximum PCE of rectifier | 43.603% |

| LDO output voltage (Vdd) | 1.50 V |

| Charging current (Ibat) | 16 μA |

| Maximum PCE of RF IC | 29.873% |

| Chip area (include pads) | 0.58 × 0.49 mm2 |

| Distance (m) | Zin (Ω) | Matching Circuits | Pin (dBm) | S11 (dB) | Vdc (V) | |

|---|---|---|---|---|---|---|

| Parallel (L) | Series (C) | |||||

| 5.45 | 50.548 − j × 2.294 | 2.4 nH | 38 pF | −20 | −28.1 | 0.291 |

| 5.12 | 52.043 − j × 2.893 | 3.6 nH | 32 pF | −17 | −28.4 | 0.535 |

| 4.66 | 53.916 − j × 1.260 | 6.8 nH | 29 pF | −14 | −32.6 | 0.792 |

| 4.25 | 51.784 − j × 2.789 | 8.6 nH | 26 pF | −11 | −29.8 | 1.019 |

| 3.93 | 52.784 − j × 2.699 | 6.6 nH | 24 pF | −8 | −28.4 | 1.223 |

| 3.60 | 48.561 − j × 6.422 | 5.6 nH | 22 pF | −5 | −33.0 | 1.450 |

| 3.30 | 52.109 + j × 3.382 | 5.6 nH | 22 pF | −4 | −28.3 | 1.509 |

| 3.15 | 53.942 − j × 1.324 | 6.2 nH | 22 pF | −3 | −28.0 | 1.623 |

| 2.90 | 54.226 + j × 2.072 | 6.2 nH | 22 pF | −2 | −26.9 | 1.682 |

| 2.70 | 53.369 − j × 11.324 | 6.8 nH | 22 pF | −1 | −29.0 | 1.700 |

| 2.45 | 51.464 − j × 1.307 | 7.5 nH | 22 pF | 0 | −34.3 | 1.702 |

| 2.25 | 51.581 + j × 7.158 | 10 nH | 10 pF | 1 | −35.4 | 1.706 |

| 1.68 | 49.710 − j × 4.909 | 10 nH | 10 pF | 2 | −26.1 | 1.712 |

| 1.50 | 53.573 + j × 1.835 | 12 nH | 10 pF | 3 | −28.2 | 1.714 |

| 1.00 | 54.669 − j × 1.756 | 22 nH | 10 pF | 6 | −26.4 | 1.716 |

| 0.68 | 53.350 − j × 2.136 | 68 nH | 10 pF | 9 | −28.3 | 1.723 |

| 0.55 | 50.655 − j × 4.093 | 100 nH | 10 pF | 10 | −27.7 | 1.725 |

| Parameters (unit) | Values |

|---|---|

| RF frequency (MHz) | 915 |

| Input impedance (Ω) | 51.464 − j × 1.3071 |

| Input power (dBm) | 0 |

| Distance between Powercastand PCB (m) | 2.45 |

| Matching components | L=7.5 nH and C=22 pF |

| Load resistor (kΩ) | 30 |

| Measured PCB (cm2) | 15.576 × 7.906 |

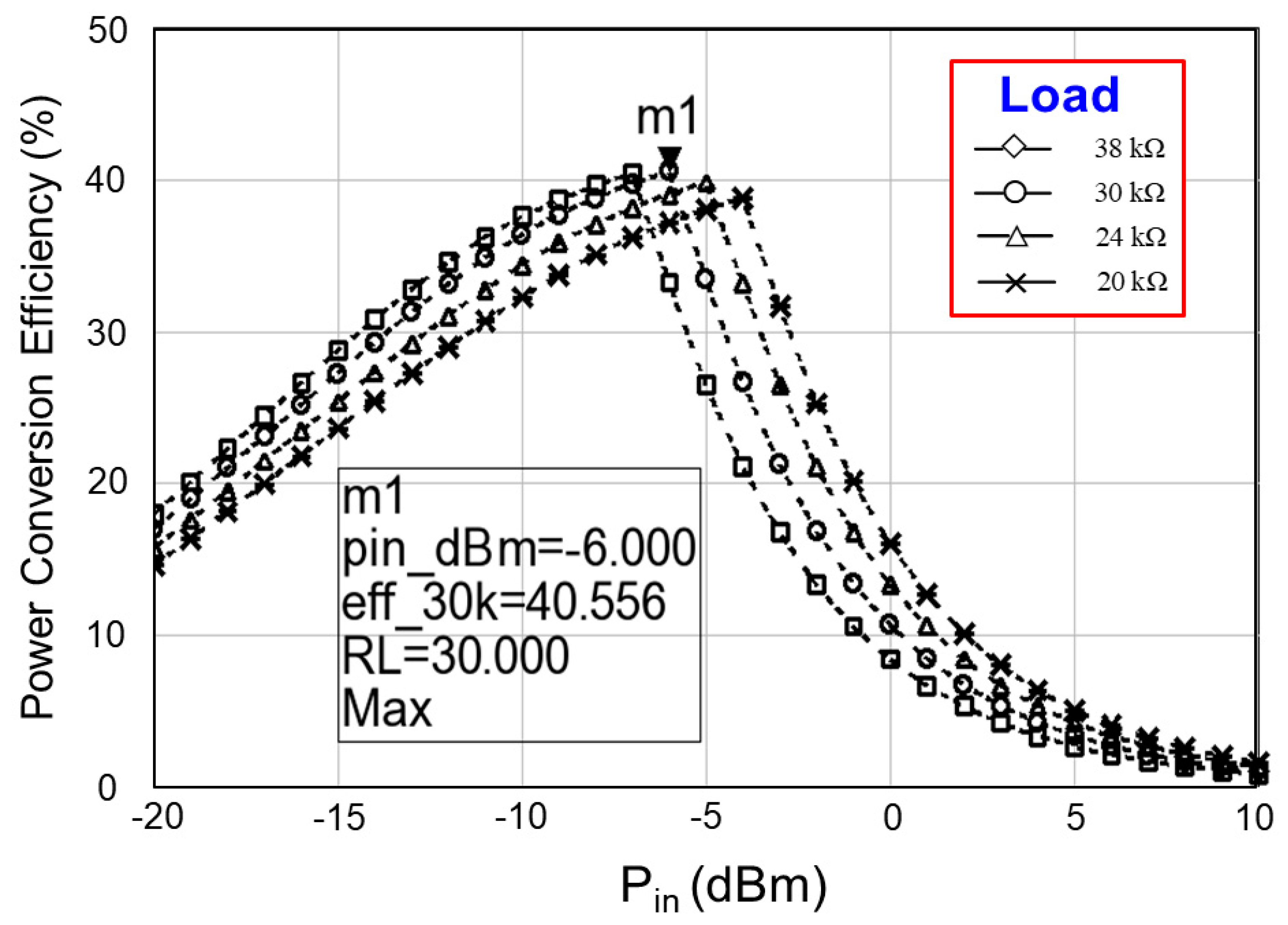

| Maximum PCE | 40.566% @Pin = −6 dBm |

| Output voltage (V) | 1.50 |

| Power consumption (μW) | 42 |

| Chip area (mm2) | 0.58 × 0.49 |

| Reference (year) | [30] (2018) | [31] (2018) | [32] (2016) | [33] (2017) | This Work |

|---|---|---|---|---|---|

| Process (μm) | 0.13 | 0.18 | 0.18 | 0.13 | 0.18 |

| RF frequency (MHz) | 915 | 900 | 900 | 2000 | 915 |

| Matching circuits | Off-chip | Off-chip | Off-chip | Off-chip | Off-chip |

| Input power range (dBm) | −35 ~ −15 | −30 ~ +0 | −26 ~ −8 | −35 ~ +5 | −20 ~ +10 |

| Stages (Rectifier) | 10 | 5 | 2 | 3 | 6 |

| Maximum PCE (Rectifier) | 42.8%@ Pin = −16 dBm | — | 78.2%@ Pin = −12 dBm | 73.9%@ Pin = 4.34 dBm | 43.6%@ Pin = −7 dBm |

| Output voltage (V) (Rectifier) | 2.32 | — | 1.0 | 3.5 | 1.725 |

| Maximum PCE (RF harvesting IC) | — | 32.8%@ Pin = −2 dBm | — | — | 40.56%@ Pin = −6 dBm |

| Output voltage (V)(RF harvesting IC) | — | 1.77 | — | — | 1.50 |

| Load resistor (kΩ) | 500 | 500 | — | 2 | 30 |

| Chip area (mm2) | 0.0296 | 16.56 | — | 0.954 | 0.2842 |

| Power (μW) | — | — | — | — | 42 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sung, G.-M.; Chung, C.-K.; Lai, Y.-J.; Syu, J.-Y. Small-Area Radiofrequency-Energy-Harvesting Integrated Circuits for Powering Wireless Sensor Networks. Sensors 2019, 19, 1754. https://doi.org/10.3390/s19081754

Sung G-M, Chung C-K, Lai Y-J, Syu J-Y. Small-Area Radiofrequency-Energy-Harvesting Integrated Circuits for Powering Wireless Sensor Networks. Sensors. 2019; 19(8):1754. https://doi.org/10.3390/s19081754

Chicago/Turabian StyleSung, Guo-Ming, Chao-Kong Chung, Yu-Jen Lai, and Jin-Yu Syu. 2019. "Small-Area Radiofrequency-Energy-Harvesting Integrated Circuits for Powering Wireless Sensor Networks" Sensors 19, no. 8: 1754. https://doi.org/10.3390/s19081754

APA StyleSung, G.-M., Chung, C.-K., Lai, Y.-J., & Syu, J.-Y. (2019). Small-Area Radiofrequency-Energy-Harvesting Integrated Circuits for Powering Wireless Sensor Networks. Sensors, 19(8), 1754. https://doi.org/10.3390/s19081754