Abstract

It is very challenging to design the capacity-approaching labeling schemes for large constellations, such as 32-QAM, in delayed bit-interleaved coded modulation (DBICM). In this paper, we investigate the labeling design for 32-QAM DBICM with various numbers of bits delayed by one time slot. In particular, we aim to obtain the labeling schemes with a high DBICM channel capacity by searching the possible labeling schemes. To reduce the search space of the candidate labeling schemes, we propose the criteria that are necessary for good labeling. Based on the proposed criteria, a three-step search algorithm is proposed to obtain the candidate labeling efficiently. Numerical results demonstrate that the DBICM with our proposed labeling scheme can approach the capacity of 32-QAM within 0.015 dB at an information rate greater than 2.5 bits/symbol.

1. Introduction

Bit-interleaved coded modulation (BICM) [1] has been widely used in practical systems for its simplicity. It is a bandwidth efficient coded modulation scheme and has been well investigated in point-to-point communications [1,2,3,4,5,6,7]. Compared to trellis-code modulation [8], BICM introduces a random interleaver between the encoder and modulator, which enables researchers to design the encoder and the modulator separately [7]. Therefore, BICM reduces the implementation complexity and attracts enormous attention.

In BICM, the dependence between transmitted bits is ignored by introducing the ideal bit-interleaver. This character is convenient for code design. However, due to the loss of dependence between transmitted bits, the channel capacity of BICM is less than that of coded modulation (CM), which is the constellation capacity. For squared constellations that have Gray labeling schemes, the gap between BICM capacity and constellation capacity is negligible [1]. For non-squared constellations, e.g., eight-quadrature amplitude modulation (QAM) and 32-QAM, Gray labeling is impossible, and the capacity gap is significant. The work [1] proposed the concept of quasi-Gray labeling, and this labeling means to be the best choice for cross constellations. The works [9,10] proposed a design method for quasi-Gray labeling based on the edge-profile. The other newer related works about the labeling focus on the BICM-iterative decoding (ID) [11,12,13,14] or the other constellation [15,16,17,18,19].

To reduce the gap, an improved BICM scheme, namely delayed BICM (DBICM), was proposed in [20]. DBICM maps bits from multiple consecutive codewords to a transmit symbol, which introduces dependence among the codewords. In decoding the consecutive codewords, the decoded result of a codeword is fed back to the demapper as a priori information for the next codeword. Therefore, the DBICM scheme can achieve a considerable gain over BICM. In [20], DBICM was verified to have a higher channel capacity and achieved about 0.7 dB and 0.5 dB gain over the corresponding BICM in eight-amplitude-shift keying (ASK) and half 16-QAM, respectively. It was pointed out in [20] that the labeling scheme is essential to DBICM design, the same as BICM [11,12,15,16,17,18]. However, different from BICM, delay pattern can also affect the performance of DBICM. The DBICM capacity with various delay pattern was investigated in [21]. In [22], the authors proposed the criteria for designing the bit labeling scheme for DBICM with iterative decoding. One of their criteria was based on the harmonic mean of the minimum squared Euclidean distance with a priori information. The other criterion was based on the bit-wise mutual information metrics. Numerical results showed that a 0.5 dB gain was achieved by the optimal labeling scheme designed with their criteria compared to BICM-ID in 16-QAM. A low density parity check (LDPC) code design for DBICM based on the paragraph extrinsic information transfer (EXIT) was proposed in [23]. They achieved a signal-to-noise ratio gain of 0.5 dB to 0.1 dB over the BICM counterparts at a code rate ranging from 0.25 to 0.5. In [24], the authors proposed a pipeline decoding structure of LDPC-DBICM in a two-way relay channel. In the 8-PSK constellation, DBICM with specific delay patterns had about 0.8 dB and 0.35 dB over the BICM scheme, respectively.

Though the DBICM scheme can achieve considerable gain over BICM, it is a great challenge to find the optimal labeling scheme for large constellations, such as 32-QAM. In this work, we attempt to tackle this problem. We consider the cross 32-QAM constellation for its wide application in practical systems and its high energy efficiency [25,26,27,28]. To design the labeling scheme for 32-QAM DBICM in order to maximize the DBICM capacity, a straightforward way is to enumerate all the 32-QAM labeling schemes for each number of delayed bits. However, this is computationally infeasible for the huge number of labeling schemes. Therefore, the search space should be reduced to make the search feasible. Our work focuses on how to reduce the search space and find the good labeling schemes for the 32-QAM constellation. To the best of our knowledge, this is the first work focused on designing labeling for such a large constellation. We summarize the main contributions of this work as follows:

1. We propose three criteria for good labeling schemes that have a high DBICM capacity for 32-QAM based on the Gray labeling rule. In particular, Criterion 1 requires that the partial labels of delayed bits satisfy the Gray labeling rule in the 32-QAM constellation and the partial labels of undelayed bits satisfy the Gray labeling rule in the sub-constellations determined by the values of delayed bits. Criterion 2 requires that both the partial labels of delayed bits and undelayed bits satisfy the Gray labeling rule in the 32-QAM constellation. Criterion 3 requires that 4 bit partial labeling satisfy the Gray labeling in 32-QAM. These proposed criteria significantly reduce the search space for good labeling schemes.

2. We propose an efficient three-step search algorithm to find all candidate labeling schemes based on the proposed criteria. In the first step, we propose a depth-first search algorithm to find the partial labeling based on Criterion 3. Then, we construct the full labeling from that partial labeling. In the end, by eliminating the labeling not satisfying Criterion 1,2, we obtain the candidate labeling. For 32-QAM, the proposed algorithm can find the candidate labeling schemes in a short period of time.

3. We propose to use the sum Hamming distance between all constellation pairs with the minimum Euclidean distance to evaluate the bit error rate (BER) performance of two capacity equivalent labeling schemes. The labeling with a smaller sum Hamming distance is expected to have a better BER performance.

4. Numerical results show that our designed labeling scheme can approach the capacity of 32-QAM within 0.015 dB at an information rate larger than 2.5 bits/symbol. In addition, for the labeling scheme with the same DBICM capacity, the labeling scheme with a smaller sum Hamming distance has a better BER performance than that with a larger Hamming distance.

The remaining parts of this paper are as follows. Section 2 introduces the concept of DBICM. Section 3 analyzes the channel capacity of DBICM and explains why we focus on the delay patterns with various bits delayed by one time slot. Section 4 introduces the proposed criteria for good labeling schemes and the proposed labeling search algorithm. Section 5 demonstrates the designed labeling schemes, the DBICM channel capacity, and the BER results of LDPC coded DBICM schemes. Section 6 draws the conclusion.

2. Delayed Bit-Interleaved Coded Modulation

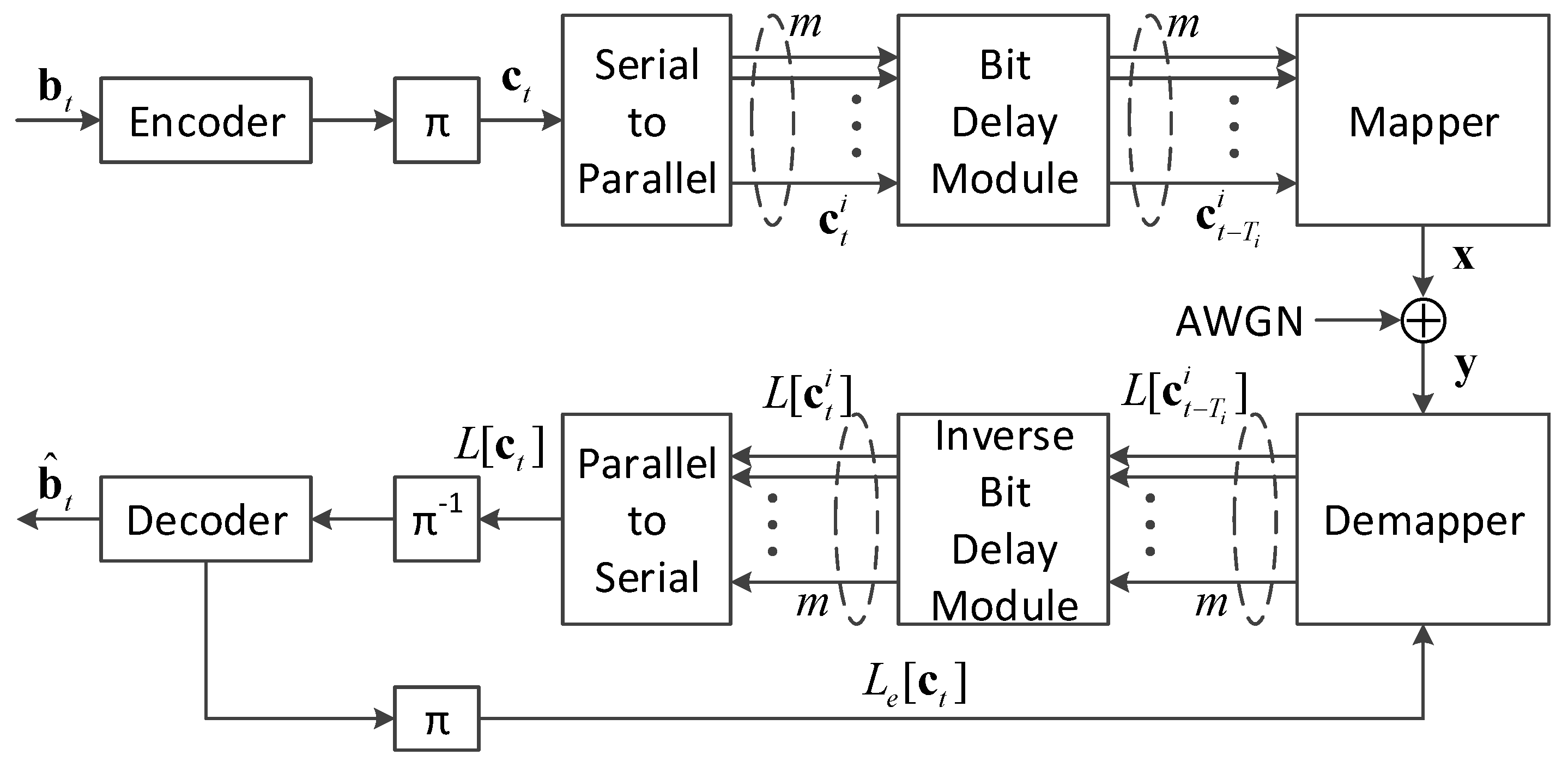

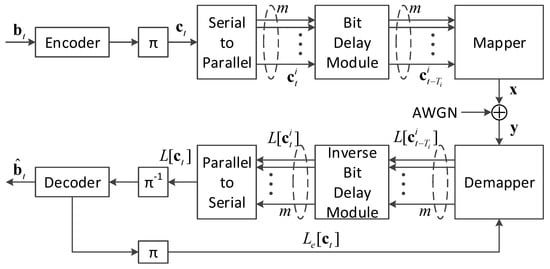

Figure 1 depicts the system model of a DBICM system. At the transmitter side, an information sequence of length k is encoded and interleaved in time slot t. The resultant codeword is of length n. Then, for a constellation of size , is passed through a one-to-m serial-to-parallel converter, leading to m length sub-sequences . Here, we assume that n is a multiple of m for simplicity. All sub-sequences are sent to a bit delay module, in which is delayed by time slots. Here, a time slot contains symbol periods. Finally, every m bit, in which the bit is drawn from , is mapped to a symbol x and transmitted through an additive white Gaussian noise (AWGN) channel. In DBICM, the vector of length m is defined as the delay pattern. It determines the dependence between multiple consecutive codewords.

Figure 1.

System model of a DBICM system.

At the receiver side, noisy signals are received and fed to the demapper. The demapper calculates the log-likelihood ratios (LLRs) for each bit in based on and the extrinsic information about the delayed bits of the previous codewords, denoted by , from the decoder. The resultant LLRs are denoted by . The LLRs are fed to an inverse bit delay module to reconstruct the LLRs for the codeword , which are denoted by . After an m-to-one parallel-to-serial converter and a deinterleaver, the LLRs of the codeword are fed to the decoder to obtain the estimated information sequence . The extrinsic information associated with the delayed bits, i.e., , is fed back to the demapper to facilitate the demapping of the undelayed bits, i.e., , of the next codeword.

It can be seen from Figure 1 that two extra modules, a bit delay module and an inverse delay module, are introduced in a DBICM system compared to a BICM system. The bit delay module introduces a coupling effect between consecutive codewords. The receiver explores this coupling effect by demapping the undelayed bits of a codeword with the a priori information associated with the delayed bits from the previous coupled codewords. This leads to a potential SNR gain of DBICM over BICM.

3. Channel Capacity Analysis and Delay Pattern Selection

In this section, we analyze the channel capacity of BICM and DBICM. Then, the delay patterns considered in this paper for DBICM will be specified.

The channel capacity for BICM is a function of the constellation , the labeling scheme , and the SNR. In this work, we only consider the cross 32-QAM constellation for a given SNR. Therefore, determines the BICM channel capacity.

Denote the label of a constellation point . Let , be the bit of , which is transmitted on the bit channel. Let be the mutual information (MI) between the label bit and the received signal y. The BICM capacity for 32-QAM is written as [1]:

In BICM, all label bits are considered to be independent. The reason is the introducing of the ideal bit-interleaver between the encoder and the mapper. As a result, the BICM channel capacity is less than the constellation capacity C in AWGN channel, which is written as:

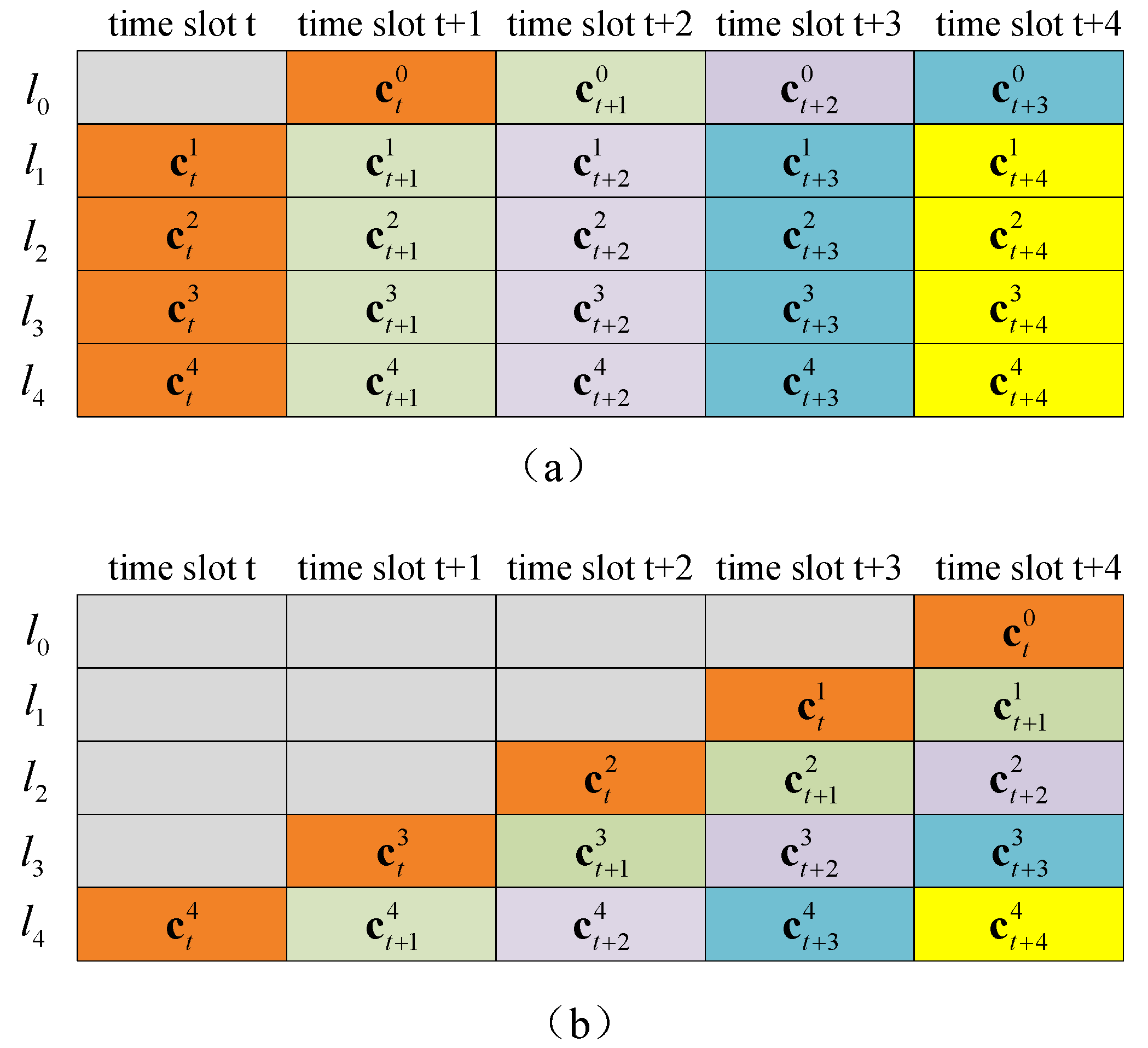

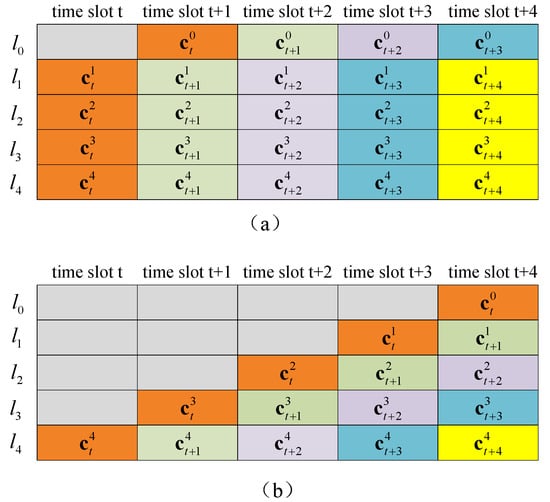

In DBICM, the channel capacity is not only a function of the constellation , the labeling scheme , and the SNR. It is also a function of the delay pattern . Denote the indexes of the delayed bits, i.e., with , by and the indexes of the undelayed bits, i.e., with , by . As explained in Section 2, the demapping of delayed bits only depends on the received signals, and therefore, the bit channel capacities for these bits are the same as those in BICM. However, the demapper utilizes the a priori information associated with the delayed bits in previous codewords to calculate the LLRs of the undelayed bits . Therefore, the bit channel capacities of the undelayed bits are different from those in BICM. In the following, we show two example delay patterns in Figure 2. By assuming that the delayed bits from previous codewords are perfectly known by the demapper, the DBICM capacities of these delay patterns are calculated.

Figure 2.

Two delay patterns for 32-QAM. (a) The delay pattern . (b) The delay pattern .

In Figure 2a, is delayed by one time slot. For this delay pattern, the DBICM channel capacity is written as:

In Figure 2b, is delayed by time slots. In this case, the DBICM channel capacity is written as:

It can be seen from Equation (4) that the DBICM capacity for the delay pattern in Figure 2b is equal to the 32-QAM constellation capacity C (as shown in Equation (2)) regardless of the labeling scheme. Therefore, it is optimal in the sense that it maximizes the DBICM capacity. However, this delay pattern has a large decoding latency since the codeword transmitted in time slot t cannot be decoded until time slot . In this paper, we consider the delay patterns in which the delayed bits are delayed by only one time slot, i.e., for . This minimizes the decoding latency introduced by DBICM. More importantly, we will show in Section 5 that by carefully designing the labeling scheme for this type of delay patterns, the DBICM capacity can almost achieve the constellation capacity at a moderate to high information rate. For this type of delay patterns, the DBICM capacity is written as:

4. Design of the Labeling Scheme

In this section, we consider the design of labeling schemes for the delay patterns of interest in this work. In particular, we aim to maximize the DBICM capacity by designing labeling schemes and their associated delay patterns. To achieve this, a straightforward way is to enumerate all possible combinations of the considered delay patterns and the labeling schemes and calculate the capacity for each combination. The one that maximizes the DBICM capacity is selected as the optimized labeling scheme and the associated delay pattern. However, this is computationally infeasible since there are labeling schemes for 32-QAM. Here, represents the permutation of m elements from n elements. By considering the delay patterns, the number of combinations is even larger.

In the following, we propose the criteria that should be satisfied by a good labeling scheme for a given delay pattern. Based on the proposed criteria, the size of the candidate labeling set will be small enough. Then, we propose an efficient three-step search algorithm, which utilizes the proposed criteria to obtain the candidate labeling. After we eliminate some equivalent labeling from the candidate set, we enumerate all the candidate labeling and choose the one with the highest DBICM capacity and the best BER performance as our designed labeling.

4.1. Labeling Search Criteria

To present the search criteria, let us first introduce the concepts of the partial label (PL), partial labeling scheme (PLS), and partial Gray labeling scheme (PGLS).

4.1.1. Partial Gray Labeling Scheme

Definition 1.

(PL): For a given non-empty index set , the PL of a constellation point x is defined as excluding , which is denoted by . Here, is the complementary set of in , i.e., .

Definition 2

(PLS): For a given non-empty index set and a labeling scheme of , by replacing with for all , the resultant labeling scheme is a PLS of , denoted by .

Note that in PLS , distinct labels are mapped to constellation points, where obtains the cardinality of . Therefore, each label is mapped to points.

Definition 3.

(PGLS): If a PLS satisfies the Gray labeling rule, it is called a PGLS. Here, the Gray labeling rule means that for any pair of constellation points , which have the minimum Euclid distance in , their PLs and have at most one bit in difference.

Note that, since each label in PLS is mapped to points, there might be pairs of constellation points , which have the minimum Euclid distance in , which have the same PLs. In this case, PLS still satisfies the Gray labeling rule as explained in Definition 3. Therefore, is a PGLS.

In [1], it was conjectured that Gray labeling maximizes the BICM capacity. Based on this principle, we propose the criterion for optimal labeling schemes of a given delay pattern next.

4.1.2. Criterion for Optimal Labeling Schemes

It can be seen from Equation (5) that the DBICM capacity is the sum of the bit channel capacities of delayed bits , i.e., , and the bit channel capacities of undelayed bits , i.e., . To optimize the DBICM capacity, the capacities of delayed and undelayed bits should be maximized simultaneously.

For the delayed bits , their bit channel capacities are equal to those in BICM. Based on the Gray labeling rule for BICM, the PLS for , i.e., , should be a PGLS in order to maximize .

For the undelayed bits , if the values of the delayed bits are given, i.e., , where , their bit channel capacities are equal to the BICM capacities in the sub-constellation . Here, . Therefore, in order to maximize the channel capacity of undelayed bits, i.e., , the labeling of should satisfy the Gray labeling rule in the sub-constellations for all .

In summary, the criterion for optimal labeling schemes is as follows:

Criterion 1:

- The PLS of delayed bits , i.e., , should be a PGLS.

- The labeling of undelayed bits should satisfy the Gray labeling rule in the sub-constellations for all .

Let be the set of labeling schemes that satisfy the first item of Criterion 1 and be the set of labeling schemes that satisfy the second item of Criterion 1, respectively. The set of candidate optimal labeling schemes is . To obtain , we can first find and then eliminate the labeling schemes that are not in , i.e., .

Though Criterion 1 is optimal in the sense that the optimal label scheme should be in , the search space, i.e., , is still too large. To see this, let us consider the delay patterns in which one bit is delayed, i.e., . We first examine the space of and then . For , for the delayed bits , all possible PLSs are PGLSs since the PLs for have only one bit. Therefore, the PLs of all constellation points have at most one bit in difference, which means they satisfy the Gray labeling rule. To find a labeling scheme , we first select 16 points arbitrarily and denote the sub-constellation by . There are choices for , where is the number of combinations of selecting m elements from n elements. Then, for each , let PL . For the undelayed bits , distinct PLs will be assigned to . There are ways to label . For the other 16 points , denote them by , and let their PLs . There are also ways to label the undelayed bits of . Therefore, . Turning to , we cannot calculate the exact number of labeling schemes that satisfy Criterion 1(b). However, our simulations showed that could not be found in a reasonable time frame. Therefore, by only considering Criterion 1 for optimal labeling schemes, the size of is still too large.

In order to reduce the search space, we propose more criteria for good labeling schemes in the following.

4.1.3. Criteria for Good Labeling Schemes

Criterion 2: The PLS of the undelayed bits should be a PGLS.

Note that Criterion 2 is different from the second item of Criterion 1. In Item 2 of Criterion 1, the labeling of undelayed bits is required to satisfy the Gray labeling rule only in the sub-constellations. However, in Criterion 2, the PLS of the undelayed bits should satisfy the Gray labeling rule in the whole constellation so that it is a PGLS.

Denote as the set of labeling schemes that satisfy Criterion 2. It can be seen that since if a labeling scheme satisfies Criterion 2, it must satisfy Item 2 of Criterion 1, but the inverse is not true. Therefore, the search space for good labeling schemes is reduced by replacing Item 2 of Criterion 1 with Criterion 2, i.e., . Note that by introducing Criterion 2, the optimal labeling scheme may not be found since the optimal labeling scheme is guaranteed to be within , but not guaranteed to be within . Therefore, we say that Criterion 2 is for a good labeling scheme instead of for the optimal labeling scheme. However, the simulation results in Section 5 showed that the obtained good labeling scheme could almost approach the constellation capacity at a mid-to-high information rate regime.

Though the proposed Criterion 2 reduced the search space for good labeling schemes, it was still too large. To see this, let us consider the delay patterns in which two bits are delayed as an example. For , in order to find , we first search for all PLSs that satisfy Criterion 2. Note that for each PLS , unique PLs are assigned to the 32 constellation points, and each of the unique PLs are assigned to constellation points. Then, for each , the full labeling schemes are constructed by assigning the labels of the delayed bits to the four points with the same PL. For each group of four points with the same PL, there are ways to label the delayed bits. By considering that there are eight groups of points with different PLs for the delayed bits, each can generate full labeling schemes. We found the number of PLSs that satisfy Criterion 2 by simulations. It was approximately equal to . Therefore, for . To find , we first found all PLSs that satisfied Item 1 of Criterion 1. Then, for each , the full labeling schemes could be constructed in the same way as that for finding . Finally, we found that . Obviously, the sizes of and were still very large. In order to further reduce the search space, we propose the following criterion.

Criterion 3: For a good labeling scheme , there exists an index set , and PLS is a PGLS.

Denote as the set of the labeling that satisfies the Criterion 3. Now, our target for obtaining the set of good labeling candidates is to find . To show that Criterion 3 must be satisfied by a good labeling, we will prove that the following proposition holds.

Proposition 1.

For each undelayed bit , its channel capacity in DBICM is larger than or equal to its channel capacity in BICM, i.e.,

Proof.

The left-hand-side of Equation (6) can be written as:

where is the comentropy function. In both DBICM and BICM, for using an ideal bit-interleaver, all bits are independent, i.e., for all and . Therefore, and Equation (7) can be written as:

Note that does not imply since y can be regarded as a function of and . When y is known, the MI between and depends on the structure of y. □

Based on Proposition 1 and Equation (5), the following proposition holds.

Proposition 2.

For a given constellation , labeling scheme , and SNR, the DBICM capacity is larger than or equal to the BICM capacity, i.e.,

It can be seen from Proposition 2 that the BICM capacity is the lower bound of the DBICM capacity. If a labeling scheme satisfies Criterion 3, it can maximize the BICM capacities of four bits and expect to have a high BICM capacity. Therefore, Criterion 3 can optimize the lower bound of the DBICM capacity and should be satisfied by a good labeling scheme.

4.2. Good Labeling Search Guideline

The proposed criteria for good labeling are summarized in Table 1. To find the candidate labeling set , one can find the set with the minimum number of elements in , and first. Then, the labeling schemes in the smallest set are checked against the other two criteria. The labeling that does not belong to L is eliminated.

Table 1.

The proposed criteria for good labeling.

In this paper, we find first. To achieve this, all the four bit PGLS are enumerated and are denote by . Then, the full labeling schemes are constructed from , and is obtained. Then, the labeling that does not belong to is eliminated from .

Note that with , various delayed patterns should be considered. For each delay pattern, all labeling schemes in are checked against Item 1 of Criteria 1 and Criterion 2. Take the delay patterns with one delayed bit as an example. For each labeling , there are delay patterns to be considered. If no delay patterns can let the labeling satisfy Item 1 of Criteria 1 and Criterion 2 simultaneously, is eliminated from . With this process, all the candidate labeling schemes and the associated delay patterns are obtained. Then, for each and the associated delay patterns, the DBICM capacity is calculated. The labeling and its associated delay pattern that achieve the highest DBICM capacity for a given SNR are considered to be the designed bit labeling scheme. In the following, an efficient three-step algorithm is proposed to implement this search guideline for good labeling schemes.

4.3. Search Algorithm for Good Labeling Schemes

In this section, we propose a three-step algorithm to find the candidate labeling schemes. In the PGLS search step, we find the set of 4 bit PGLSs by utilizing an efficient depth-first search algorithm. In the full labeling generation step, we utilize the PGLSs to construct the full labeling. The final step is to eliminate the labeling that does not belong to simultaneously. Furthermore, we eliminate some strictly equivalent labeling schemes (SELS), which are defined as below, from the candidate set.

For two DBICM labeling schemes and of a constellation , the sets of delayed and undelayed bits are , respectively. The partial labels of a point x for associated with and are denoted by , respectively. The partial labels of a point x for associated with and are denoted by , respectively. Let be the Hamming distance between two (partial) labels y and z of x.

Definition 4.

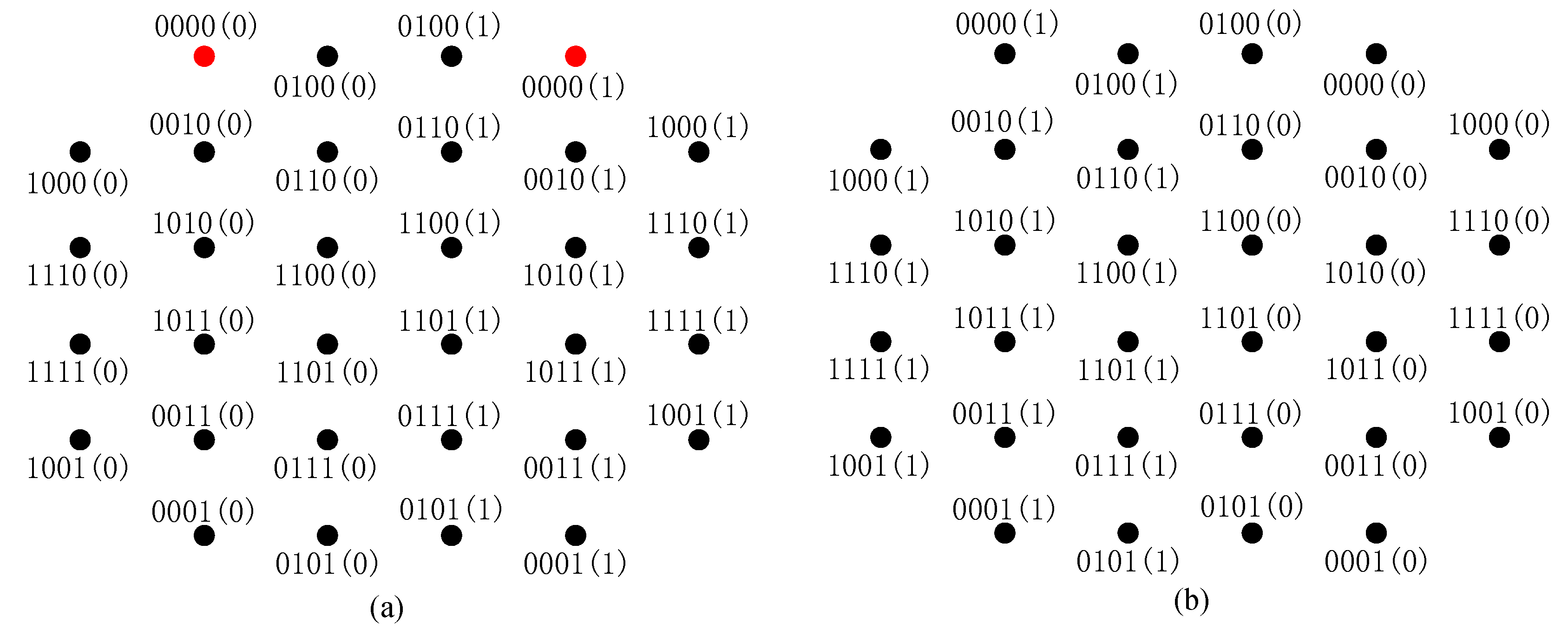

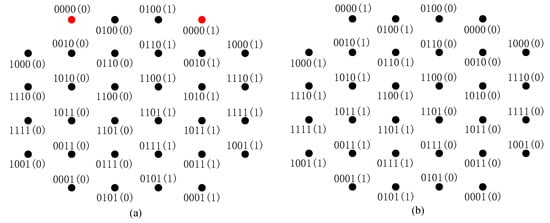

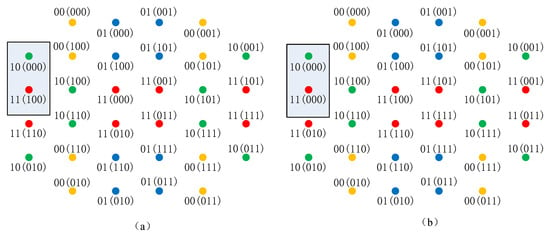

(SELS): If for any pair of constellation points , and are satisfied simultaneously, are called SELS (an example of the SELS is shown in Figure 3.

Figure 3.

An example of the SELS. (a) Labeling scheme. . (b) Labeling scheme

Note that for a pair of SELS and , their DBICM capacities are the same. This is because with , the capacities of the delayed bits for are the same, and with , the capacities of the undelayed bits for are the same. Based on (5), and have the same DBICM capacity. In addition, and have the same BER performance since for any pair of constellation points, the correspondence between the Hamming distance of their labels and their Euclidean distance remains the same.

The derivation of the three-step algorithm is shown in the Appendix A.

4.4. Capacity Equivalent Labeling Schemes

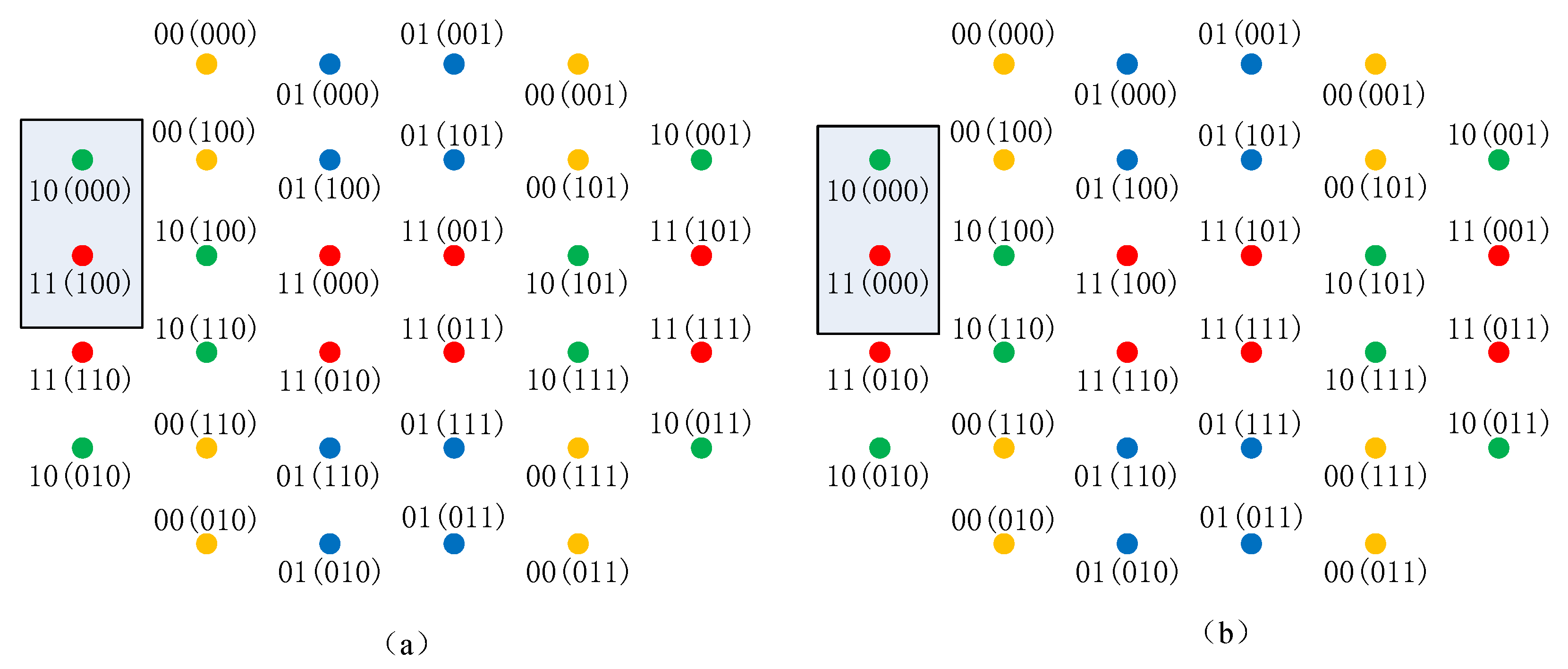

Although we excluded the SELS in the final step of constructing L, there are still some labeling schemes that have the same DBICM capacity, but are not SELS. We call these labeling schemes capacity equivalent labeling schemes (CELS). We investigate CELS since though they are equivalent in the sense of DBICM capacity, they have different BER performance. In this work, we aim to find the labeling scheme that not only has a high DBCIM capacity, but also a good BER performance. In the following, CELS is defined.

Definition 5.

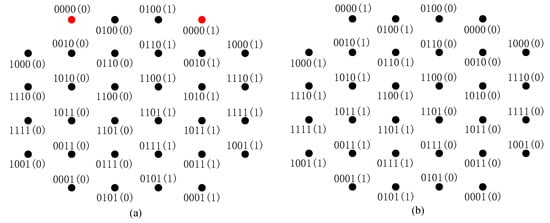

(CELS): For two DBICM labeling schemes and with the same PLS of delayed bits, i.e., . For each sub-constellation determined by the values of delayed bits , if for any pair of constellation points , holds. The two labeling are called CELS.

It can be seen from Equation (5) that the capacity of undelayed bits is the average of the BICM capacities in each sub-constellation . A pair of CELS has the same BICM capacity in each sub-constellation ; therefore, they have the same capacity of undelayed bits. Their capacities of delayed bits are also the same since they have the same PLS of delayed bits. To sum up, a pair of CELS has the same DBICM capacity.

Note that a pair of SELS is a pair of CELS, but the inverse is not necessarily true. For example, two labeling schemes are shown in Figure 4a,b, respectively. The delayed bits are . The undelayed bits are , which are in the parentheses. The two labeling have the same PLS of delayed bits, i.e., . Each eight points with the same color constitute a sub-constellation . It can be seen that, for any two points , holds. Therefore, the two labeling are CELSs. In Figure 4a, the labels of the two points in the box are , and the Hamming distance of the undelayed PL is one. In Figure 4b, the labels of the same two points are , and the Hamming distance of the undelayed PL is 0. Therefore, are not SELS, and they will have different BER performance.

Figure 4.

An example CELS. (a) The labeling . (b) The labeling .

The calculation of DBICM capacity in Equation (5) is based on the hypothesis that all the delayed bits are perfectly known by the demapper. This holds in a high SNR region. However, in a low SNR region, the hypothesis is not valid. Therefore, if the delayed bits have errors, the demodulation structure of DBICM for the undelayed bits is destroyed, i.e., we cannot obtain the full DBICM capacities of the undelayed bits in the wrong sub-constellation. The demodulation results depend on the received value and the labeling of the whole constellation.

In this paper, we only consider the minimum Euclidean distance in the constellation as the error radius, which is held in most instances. This is because the probability of making decision errors from one point to another point decreases exponentially w.r.t the Euclidean distance between two points. In the 32QAM constellation, for a signal s mapped by constellation point x, if the error happens in the transmission process, the received value y can be demodulated to the neighbor constellation points, which have the distance away from x. The cost of this error is the Hamming distance of the labels between x and its neighbor. Therefore, we employ the sum Hamming distance to evaluate the CELS, which is the total cost of the errors with a radius of .

The labeling schemes and in Figure 4 are CELS, and the sum Hamming distances for and are 68 and 60, respectively. Therefore, is expected to have a better BER performance in a low SNR regime than . In a high SNR regime, will have almost the same BER. Numerical results in Figures 7 and 8 will confirm this expectation.

Note that we focus on the 32-QAM constellation in this paper for its bandwidth efficiency and wide use in practical systems [25,26,27,28], e.g., optical communication. The proposed method can also be extended to higher order modulation such as 128-QAM and 512-QAM, but the complexity becomes prohibitively high. The reason is that our search method is based on the algebraic structure of 32-QAM. For 128-QAM and 512-QAM, there is an exponential growth of the constellation points. Therefore, applying our method to these constellations will lead to the exponential growth of the complexity. For example, the numbers of candidate labeling schemes associated with a PGLS in 128-QAM and 512-QAM are and , respectively. Contrary to the number of in 32-QAM, the search spaces of 128-QAM and 512-QAM are too large.

5. Numerical Results

In this section, we first show our designed labeling schemes with the associated delay patterns. Then, the DBICM capacities of these labeling schemes are compared to the constellation capacity and that of the quasi-Gray labeling in [10]. BICM capacity with the quasi-Gray labeling is also demonstrated for comparison. Finally, we show the BER performance of LDPC coded DBICM and BICM with the proposed labeling schemes and the quasi-Gray labeling scheme.

5.1. The Proposed Labeling Schemes

We utilize the proposed labeling search algorithm in Section 4.4 to find the candidate labeling schemes that have a high DBICM capacity. In the 4 bit PGLS search step, 174,792 4 bit PGLSs are found. By executing the full labeling generation step and eliminating the SELS, = 33,292,288 candidate labeling schemes are found. For the delay patterns with , or 4 bits delayed by one time slot, the numbers of candidate labeling are 7,891,148, 16,683,242, 16,683,242, and 7,891,148, respectively.

Then, the DBICM capacities for these labeling schemes with their delay patterns at the SNR of 7 dB and 9.2 dB were calculated. We considered this SNR since the DBICM channel capacity was around 2.5, three bits/symbol or the code rate was around 0.5, 0.6 at this point, respectively, which is practical for high order coded modulation schemes. To eliminate the CELS introduced in Section 4.4, the sum Hamming distances of these labeling schemes were calculated. The one with the minimum sum Hamming distance was selected as our designed labeling scheme.

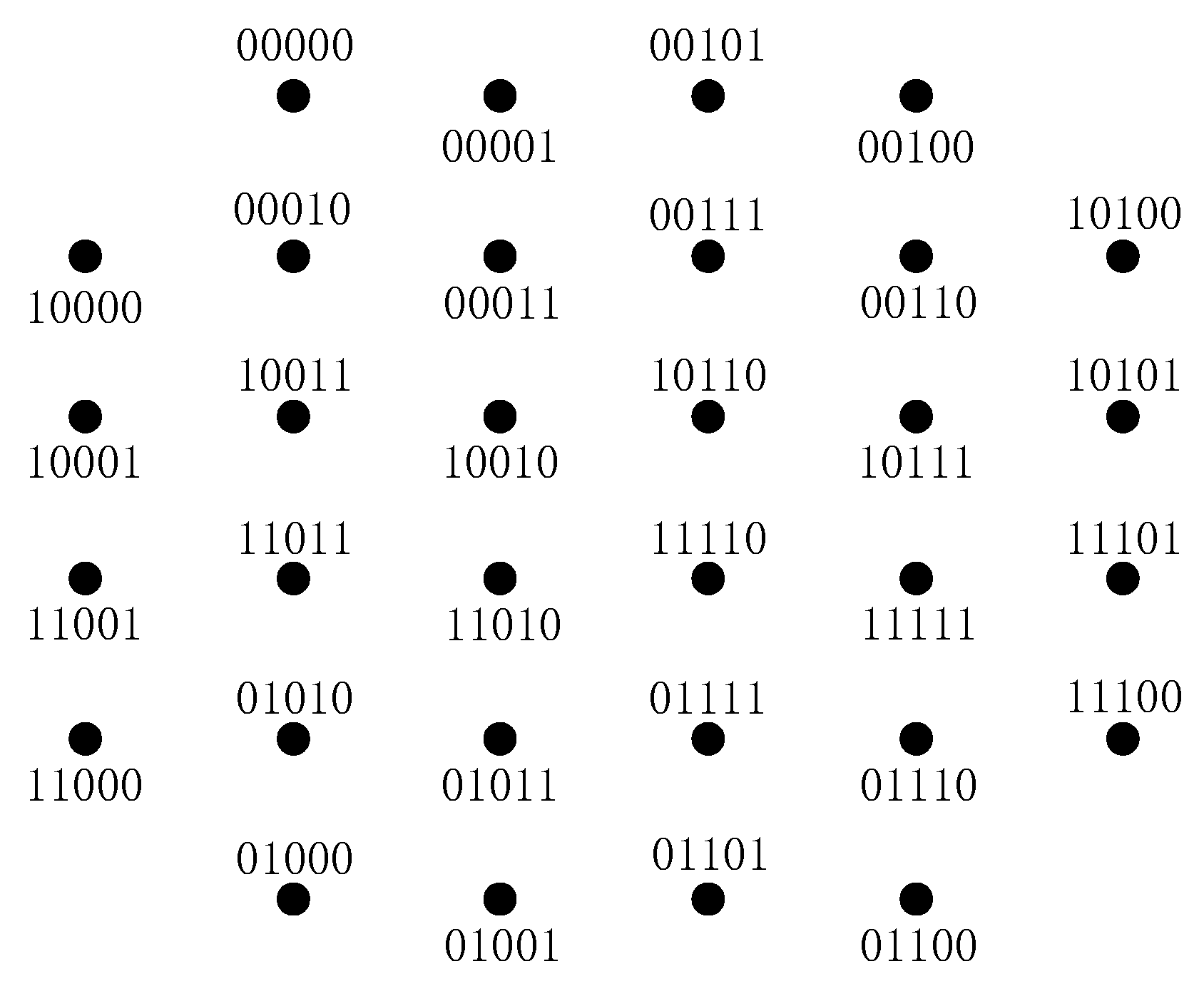

Our designed labeling scheme for the delay patterns with , and 3 bits delayed was the same, which is shown in Figure 4b. The designed labeling scheme for the delay patterns with 4 bits delayed is shown in Figure 5. The associated delay patterns were , , , and , respectively.

Figure 5.

Designed labeling scheme with delayed pattern .

We also found the optimal delay patterns for the quasi-Gray labeling by enumerating all possible delay patterns. The associated delay patterns were , , , and , respectively.

5.2. The Channel Capacity

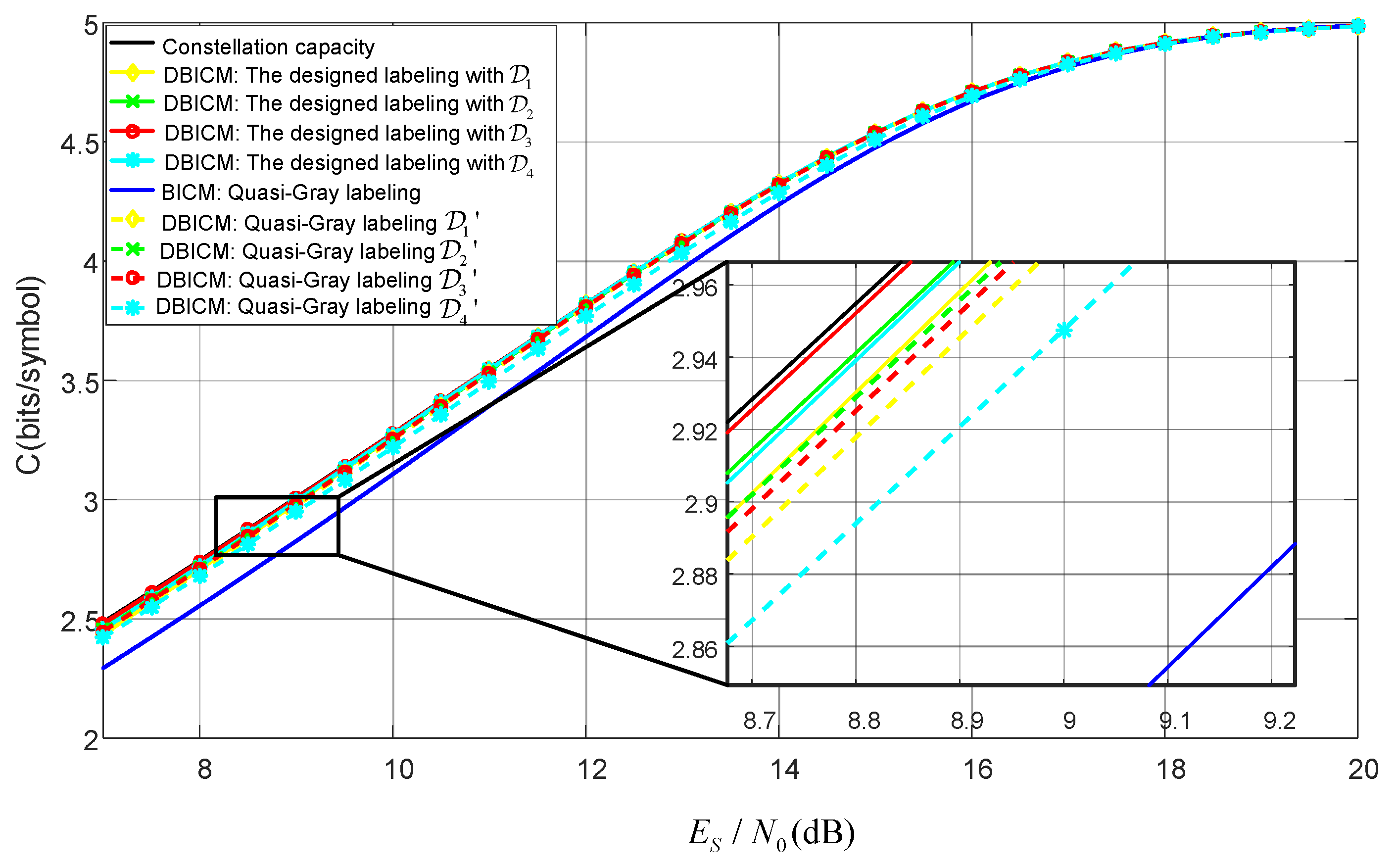

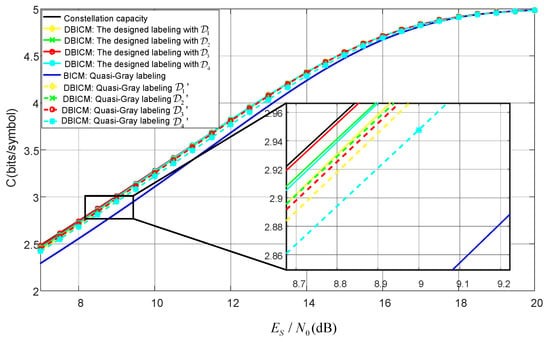

The DBICM channel capacities with our designed labeling schemes and the quasi-Gray labeling scheme are shown in Figure 6. The BICM channel capacity of the quasi-Gray labeling scheme is also shown in Figure 6 for comparison.

Figure 6.

Channel capacity for our designed labeling and quasi-Gray labeling.

It can bee seen from Figure 6 that for the same number of delayed bits, our designed labeling scheme outperformed the quasi-Gray labeling scheme in terms of DBICM capacity. It is notable that for our designed labeling scheme with three bits delayed by one time slot, the DBICM capacity was only 0.015 dB away from the constellation capacity at an information rate greater than 2.5 bits/symbol.

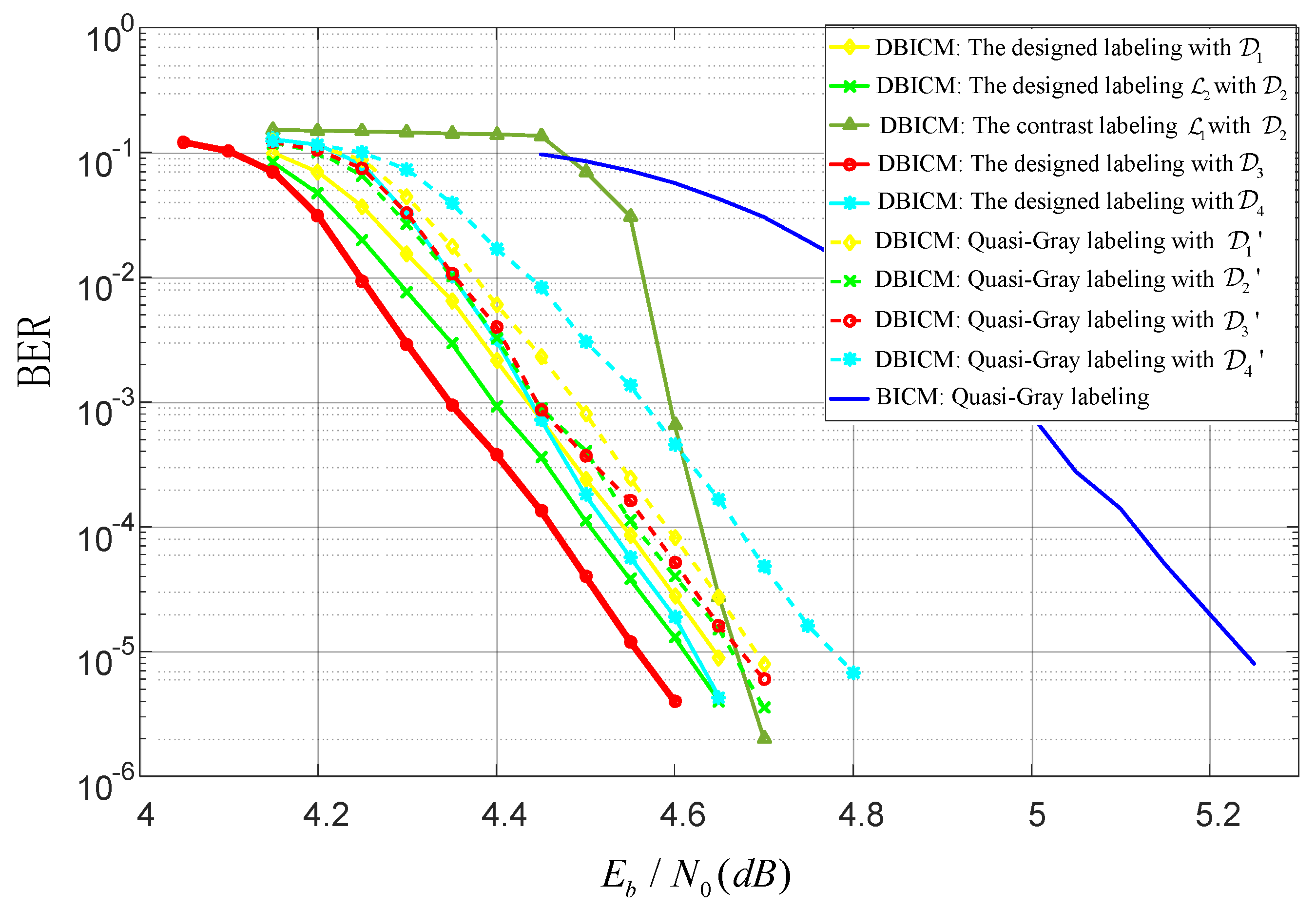

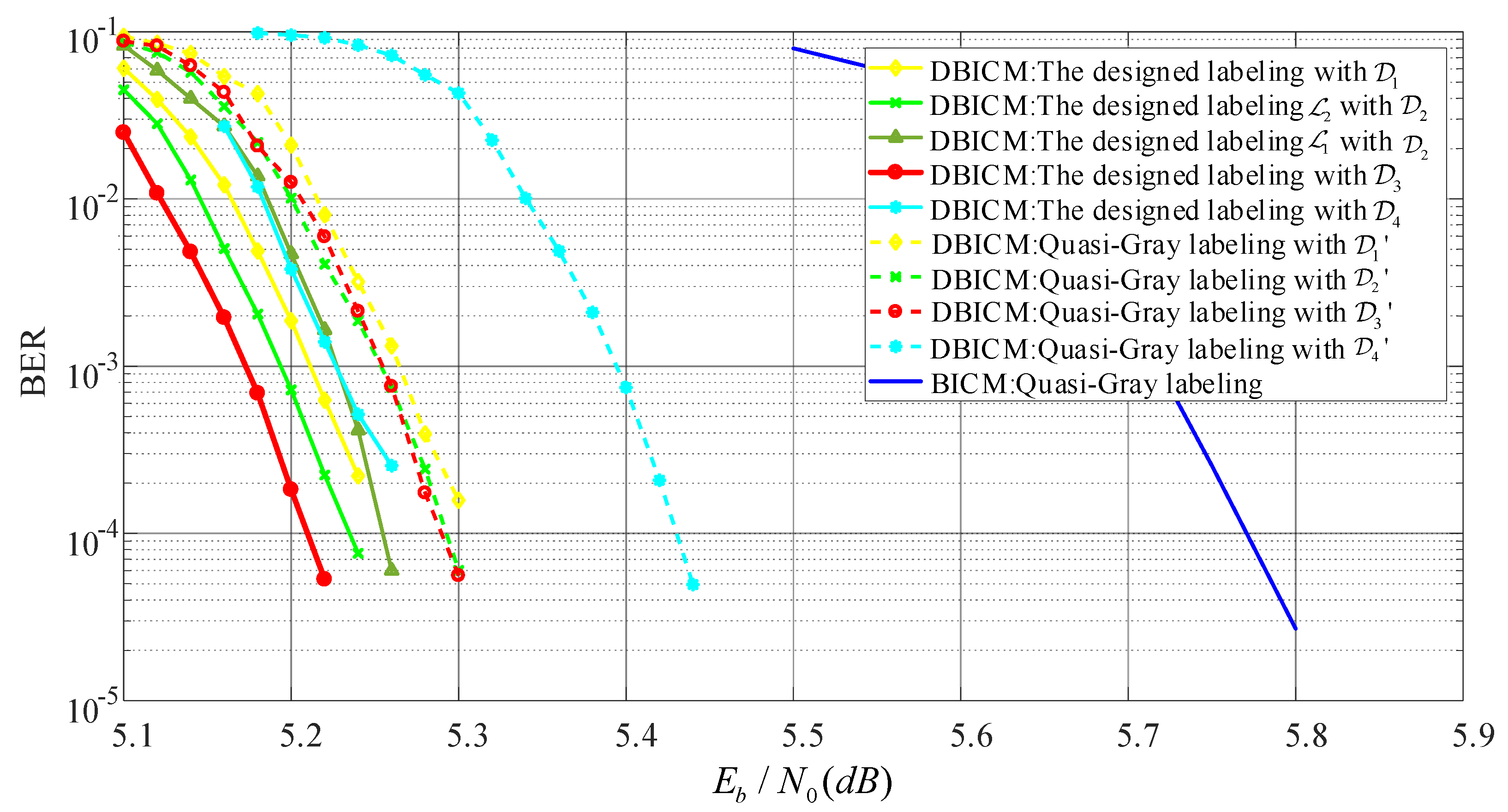

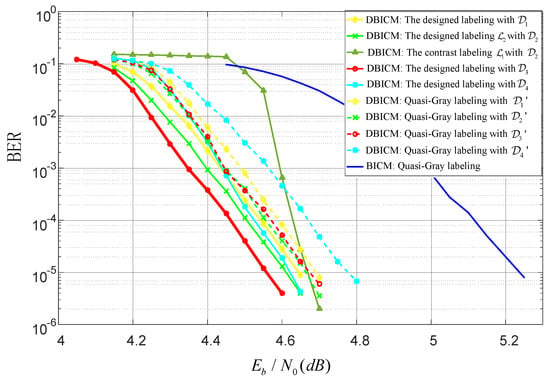

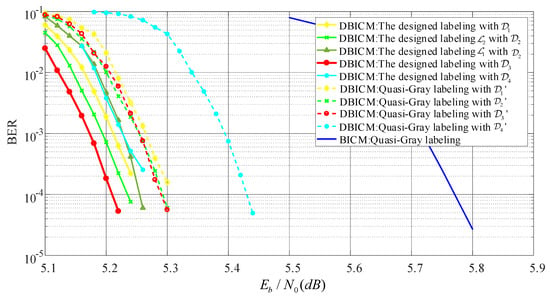

5.3. BER Performance

In this subsection, we evaluate the BER performance of LDPC coded DBICM and BICM with various labeling schemes. For the DBICM capacity of 2.5bits/symbol, an LDPC code with code length 10,000 and code dimension was constructed by the progressive edge-growth (PEG) algorithm [29], where the distribution of the variable node degree is optimized by the differential evolution algorithm [30]. For the DBICM capacity of three bits/symbol, the LDPC code from DVB-S2 [31] with the code rate 3/5 and code length 64,800 was employed. The interleaver used the consecutive mapping [3] in the coded modulation. Figure 7 and Figure 8 show the BER performance of the DBICM capacities of 2.5 bits/symbol and three bits/symbol, respectively. We can see that our designed labeling schemes had better BER performance compared to that of quasi-Gray labeling.

Figure 7.

BER performance with code rate 0.5.

Figure 8.

BER performance with code rate 0.6.

In Figure 7 and Figure 8, we also compare the labeling schemes in Figure 4a,b to show the difference of the BER of CELS. We can see that in the low SNR region, had worse BER performance than that of . In the high SNR regime, had nearly the same BER as . This agreed with the expectation described in Section 4.4 that the one with the minimum Hamming distance would have better performance in the low SNR region.

6. Conclusions

In this paper, we considered the bit labeling design for 32-QAM DBICM. We aimed to obtain the labeling that had a high DBICM capacity and a good BER performance. To reduce the search space for the good labeling, three criteria were proposed. An efficient labeling search algorithm was proposed to obtain the labeling schemes that satisfied the proposed criteria. Then, we evaluated the candidate labeling with DBICM capacity in a fixed SNR point and selected the best one as our designed labeling. This SNR point must correspond to the most efficient capacity of the constellation. Capacity analysis showed that the designed labeling with three bits delayed by one time slot approached the 32-QAM constellation capacity within 0.015 dB at a mid-to-high information rate regime. BER simulation results also demonstrated that the designed labeling achieved a 0.1dB gain in terms of BER performance over the benchmark scheme.

Author Contributions

Conceptualization, Z.Z. and L.Z.; methodology, Z.Z. and J.D.; software, Z.Z. and Y.Z.; validation, Z.Z., L.Z., and J.D.; formal analysis, Z.Z. and J.D.; investigation, Z.Z.; resources, L.Z.; data curation, Y.Z.; writing, original draft preparation, Z.Z.; writing, review and editing, Z.Z., L.Z., and J.D.; visualization, Z.Z. and Y.Z.; supervision, L.Z.; project administration, L.Z.; funding acquisition, L.Z. All authors read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Conflicts of Interest

The authors declare no conflict of interest.

Abbreviations

The following abbreviations are used in this manuscript:

| QAM | Quadrature amplitude modulation |

| DBICM | Delayed bit-interleaved coded modulation |

| BICM | Bit-interleaved coded modulation |

| CM | Coded modulation |

| ASK | Amplitude-shift keying |

| BICM-ID | Bit-interleaved coded modulation iterative decoding |

| BER | Bit error rate |

| LDPC | Low density parity check |

| AWGN | Additive white Gaussian noise |

| LLR | Log-likelihood ratio |

| SNR | Signal-to-noise ratio |

| MI | Mutual information |

| PL | Partial label |

| PLS | Partial labeling scheme |

| PGLS | Partial Gray labeling scheme |

| SELS | Strictly equivalent labeling schemes |

| CELS | Capacity equivalent labeling schemes |

| PEG | Progressive edge-growth |

Appendix A. The Three-Step Search Algorithm

Appendix A.1. The PGLS Search Step

In the PGLS search step, we propose a depth-first search algorithm (Algorithm 1) to obtain the set of 4 bit PGLSs . Let be the set of 4 bit PLs. Denote as the PL assignment order to the 32 points in the 32-QAM constellation, i.e., is the index of a point in the 32-QAM constellation that will be assigned a 4 bit PL first, and is the index of a point in the 32-QAM constellation that will be assigned a 4 bit PL last. The algorithm finds the set of 4 bit PGLSs in a few recursive steps.

In the first step, the constellation point is assigned an arbitrary 4 bit PL in B. Without loss of generality, let , where is the indexes of the four bits that their PLS is a PGLS. Then, let , where represents that the set B excludes the element .

In the second step, find all legal PLs of point from B and denote them by . Here, legal PLs means that by assigning the PL to , the PLs of and satisfy the partial Gray labeling rule. Then, assign a PL to , and let .

In the step, , find all legal PLs of point from B, and denote them by . If is not empty, assign a PL to , and let . Otherwise, go back to the step, and assign another PL to .

The above process continues. If steps are executed successfully, a 4 bit PGLS is found and recorded in . The algorithm goes back to the 31st step and tries another PL in . If in the step, is empty, then go back to the step, and assign another PL in to . When all the PLs in have been exhausted, the set of 4 bit PGLSs is obtained. The proposed depth-first search algorithm is summarized in Algorithm 1.

| Algorithm 1 Depth-first bit-labeling search. |

| Input:The assignment order I; |

| The label candidate set B. |

| Output: The 4 bit PGL schemes set . |

| 1: begin procedure |

| 2: initialize: let , ; set ; |

| 3: find ; |

| 4: if then |

| 5: go to 14; |

| 6: end if |

| 7: for do |

| 8: , , ; |

| 9: if then |

| 10: record the partial Gray labeling schemes in ; |

| 11: go to 14; |

| 12: end if |

| 13: return to 3; |

| 14: , ; |

| 15: end for |

| 16: return . |

It can be seen from Algorithm 1 that in each step, if is chosen so that the size of is minimized, the search complexity will be reduced significantly. This is because the PLs that do not satisfy the Gray labeling rule are excluded in an earlier stage and will not be considered in the following search process. Therefore, the label assignment order I is essential for reducing the complexity of Algorithm 1.

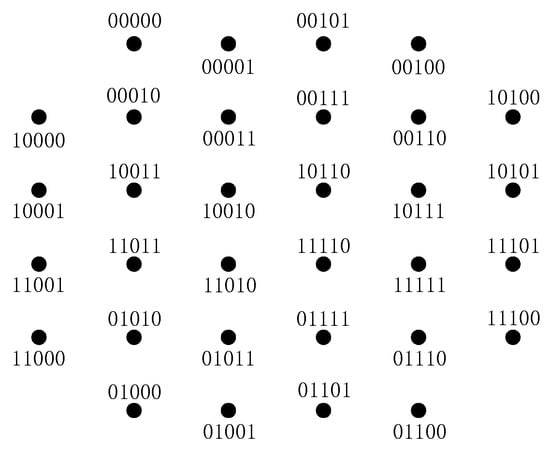

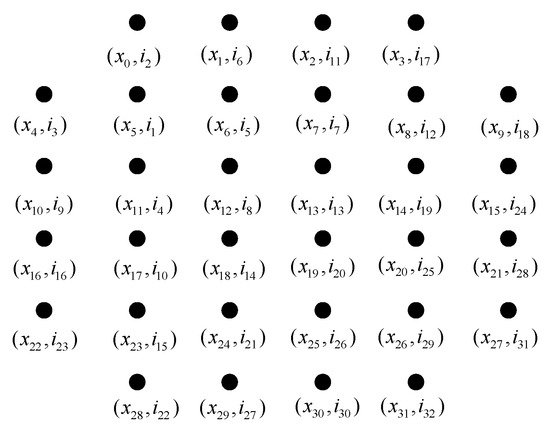

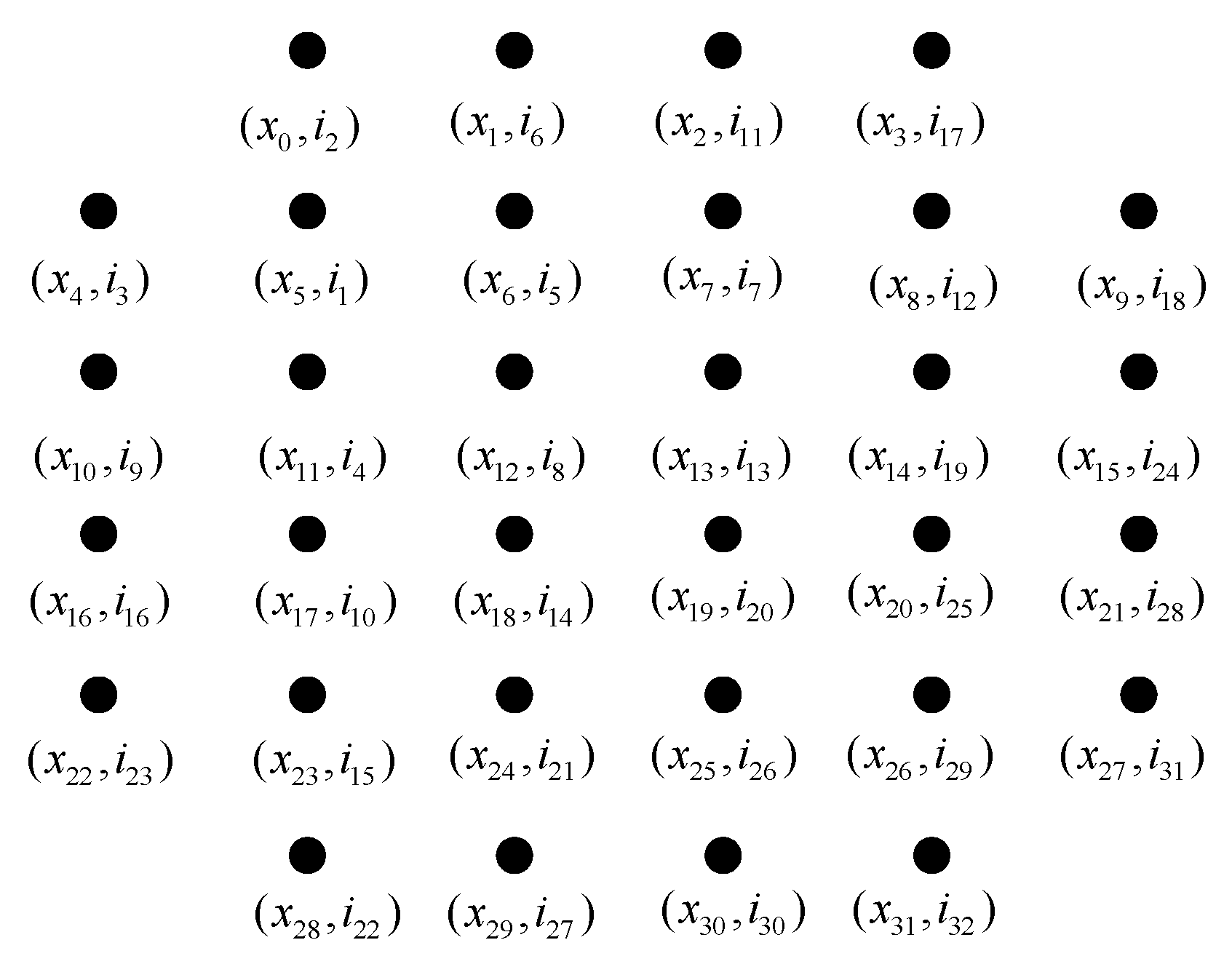

In the following proposed Algorithm 2, we obtain the label assignment order I to minimize the complexity of Algorithm 1. For Algorithm 2, the inputs are the numbered points of constellation and the set of 4 bit PL candidates B. The output is the assignment order I. The constellation point numbering rule is arbitrary. For example, in Figure A1, the points are numbered from 0 to 31 from left to right and top to bottom.

Firstly, one constellation point is selected as the first one to be labeled in an arbitrary manner. For example, in Figure A1, is selected. In this case, . Let . Then, eliminate from B, and eliminate from . Go to the step .

In the step, for each of the remaining points , find the set of legal PLs in B, and denote it by . Within all the non-empty sets , choose the one with the minimum number of elements, and let the associated constellation point be the next one to be labeled. For example, if is the chosen one, let . If there are multiple sets that have the minimum number of legal PLs, one is selected randomly. When is obtained, is assigned with a random PL , and let , . When , the assignment order I is generated.

| Algorithm 2 The assignment order. |

| Input:The numbered points of constellation ; |

| The label candidate set B. |

| Output:The assignment order . |

| 1: begin procedure |

| 2: initialize: let , , , ; set ; |

| 3: for do |

| 4: find for ; |

| 5: end for |

| 6: find one with minimum size in , and denote it as ; |

| 7: if there are multiple sets having the minimum number of legal PLs, one is selected randomly; |

| 8: let ; |

| 9: assign with a random label in ; |

| 10: , ; |

| 11: if then |

| 12: go to 16; |

| 13: else |

| 14: , go to 3; |

| 15: end if |

| 16: return I. |

Figure A1 depicts an example of the assignment order I generated by Algorithm 2. In the figure, a pair of numbers , is associated with each constellation point. In particular, represents the numbering of a point in the 32-QAM constellation, while represents the numbering order of a point. For example, means that the point will be assigned a PL first, and means that the point will be assigned a PL in the second step of Algorithm 1.

Figure A1.

An example of the assignment order.

Figure A1.

An example of the assignment order.

In Algorithm 1, by employing this assignment order, only 1,244,160 attempts are executed for obtaining the set of 4 bit PGLSs . This is completed in a few minutes on a personal computer.

Appendix A.1.1. The Full Labeling Generation Step

In this step, we construct the full labeling from the 4 bit PGLSs by assigning the label to the bit that was not included in the PL. Without loss of generality, we assume that the 4 bit PLs are assigned to . In this case, a value of zero or one will be assigned to of each constellation point to obtain the full labeling schemes.

For a 4 bit PGLS , it maps the 4 bit PLs to 32 constellation points. Therefore, each unique PL is assigned to a pair of constellation points. For each pair of points that have the same 4 bit PL, is assigned to a point, and is assigned to the other one. In this way, a full labeling is constructed from a PGLS . For example, in Figure 3a, the two red points have the same 4 bit PL . By assigning to the left one and to the right one, the full labels (00000) and (00001) for these two points are constructed.

For a 4 bit PGLS , there are 16 distinct PLs. For each unique PL, can be assigned a value of zero or one. Therefore, there are ways to assign the values to of the 16 distinct PLs. Denote the set of those labeling as . For each labeling , there must be a labeling that the values of its for all constellation points are the inverses of those of .

Note that these two labeling schemes are SELS since the Hamming distance between any two PLs does not change by inverting the value of . Figure 3 demonstrates an example, and the labeling schemes in Figure 3a,b are SELS. The values of for all points in these two labeling are inverted.

By considering the above SELS, there are only distinct labeling schemes in . As a result, the number of full labeling schemes constructed from is , i.e.,

Appendix A.1.2. The Final Step

For the delay patterns with , or 4 delayed bits, each labeling in is checked against Item 1 of Criterion 1 and Criterion 2. If the check fails, the labeling is excluded from . By now, the good labeling candidate set L for all delayed patterns is obtained.

Note that the candidate set L still contains many SELS. In L, as the cross 32-QAM constellation is central symmetry, a labeling scheme in L and the labeling schemes that are generated by rotating itself by are SELS. Furthermore, a labeling scheme and its reflection are SELS. By excluding these SELS, the size of L is small, which is shown in Section 5.

In the end, for each labeling in L, its DBICM capacity is calculated. The labeling scheme and its associated delay pattern that achieves the maximum DBICM capacity are selected as our designed labeling for 32-QAM.

References

- Caire, G.; Taricco, G.; Biglieri, E. Bit-interleaved coded modulation. IEEE Trans. Inf. Theory 1998, 44, 927–946. [Google Scholar] [CrossRef]

- Du, J.; Zhou, L.; He, X. The joint demodulation and decoding for BICM-ID system with BEC approximation and optimized bit mapping. In Proceedings of the 2015 IEEE Global Communications Conference (GLOBECOM), San Diego, CA, USA, 6–10 December 2015. [Google Scholar]

- Du, J.; Yang, L.; Yuan, J.; Zhou, L.; He, X. Bit mapping design for LDPC coded BICM schemes with multi-edge type EXIT chart. IEEE Commun. Lett. 2017, 21, 722–725. [Google Scholar] [CrossRef]

- Hou, J.; Siegel, P.H.; Milstein, L.B.; Pfister, H.D. Capacity-approaching bandwidth-efficient coded modulation schemes based on low-density parity-check codes. IEEE Trans. Inf. Theory 2003, 49, 2141–2155. [Google Scholar]

- Zhao, Y.; Fang, Y.; Yang, Z. Interleaver Design for Small-Coupling-Length Spatially Coupled Protograph LDPC-Coded BICM Systems Over Wireless Fading Channels. IEEE Access 2020, 8, 33500–33510. [Google Scholar] [CrossRef]

- He, Y.; Jiang, M.; Ling, X.; Zhao, C. Robust BICM Design for the LDPC Coded DCO-OFDM: A Deep Learning Approach. IEEE Trans. Commun. 2020, 68, 713–727. [Google Scholar] [CrossRef]

- Zehavi, E. 8-PSK trellis codes for a Rayleigh channel. IEEE Trans. Commun. 1992, 40, 873–884. [Google Scholar] [CrossRef]

- Ungerboeck, G. Channel coding with multilevel/phase signals. IEEE Trans. Inf. Theory 1982, 28, 55–67. [Google Scholar] [CrossRef]

- Wesel, D.; Liu, X. Edge profile optimal constellation labeling. In Proceedings of the 2000 IEEE International Conference on Communications (ICC 2000): Global Convergence Through Communications, Conference Record, New Orleans, LA, USA, 18–22 June 2000. [Google Scholar]

- Wesel, D.; Liu, X.; Cioffi, J.M.; Komninakis, C. Constellation labeling for linear encoders. IEEE Trans. Inf. Theory 2001, 47, 2417–2431. [Google Scholar] [CrossRef]

- Yang, Z.; Xie, Q.; Peng, K.; Song, J. Labeling schemes optimization for BICM-ID systems. IEEE Commun. Lett. 2010, 14, 1047–1049. [Google Scholar] [CrossRef]

- Muhammad, N.S.; Speidel, J. Joint optimization of signal constellation bit labeling schemes for bit-interleaved coded modulation with iterative decoding. IEEE Commun. Lett. 2005, 9, 775–777. [Google Scholar]

- Zhang, J.; Djordjevic, I.B. Mapping design of a four-dimensional 32-ary signal constellation over an AWGN channel. Chin. Commun. 2014, 11, 775–777. [Google Scholar] [CrossRef]

- Navazi, H.M.; Hossain, M.J. Novel Method for Multi-Dimensional Mapping of Higher Order Modulations for BICM-ID Over Rayleigh Fading Channels. IEEE Trans. Wirel. Commun. 2019, 18, 1142–1154. [Google Scholar] [CrossRef]

- Yang, F.; Yan, K.; Xie, Q.; Song, J. Non-equiprobable APSK constellation labeling schemes design for BICM systems. IEEE Comm. Lett. 2013, 17, 1276–1279. [Google Scholar] [CrossRef]

- Bocherer, G. Labeling Non-Square QAM Constellations for One-Dimensional Bit-Metric Decoding. IEEE Commun. Lett. 2014, 18, 1515–1518. [Google Scholar] [CrossRef]

- Markiewicz, T.G. Construction and Labeling of Triangular QAM. IEEE Commun. Lett. 2017, 21, 1751–1754. [Google Scholar] [CrossRef]

- Colman, G.W.K.; Gohary, R.H.; El-Azizy, M.A.; Willink, T.J.; Davidson, T.N. Quasi-Gray Labelling for Grassmannian Constellations. IEEE Trans. Wirel. Commun. 2011, 10, 626–636. [Google Scholar] [CrossRef]

- Jia, L.; Shu, F.; Chen, M.; Zhang, W.; Li, J.; Wang, J. Joint Constellation-Labeling Optimization for VLC-CSK Systems. IEEE Wirel. Commun. Lett. 2019, 8, 1280–1284. [Google Scholar] [CrossRef]

- Ma, H.; Leung, W.K.; Yan, X.; Law, K.; Fossorier, M. Delayed bit interleaved coded modulation. In Proceedings of the 2016 9th International Symposium on Turbo Codes and Iterative Information Processing, Brest, France, 5–9 September 2016. [Google Scholar]

- Yan, X.; Machado, R.G.; Huang, K.; Gabry, F.; Fossorier, M.; Hafermann, H.; Zhang, H.; Land, I.; Leung, W.K. Capacity Analysis of Delayed Bit Interleaved Coded Modulation. In Proceedings of the 2018 IEEE 10th International Symposium on Turbo Codes &Iterative Information Processing (ISTC), Hong Kong, China, 3–7 December 2018. [Google Scholar]

- Wang, L.; Cai, S.; Ma, H.; Leung, W.K.; Ma, X. Bit-labeling schemes for delayed BICM with iterative decoding. In Proceedings of the 2018 IEEE International Symposium on Information Theory (ISIT), Vail, CO, USA, 17–22 June 2018. [Google Scholar]

- Liao, Y.; Yang, L.; Yuan, J.; Huang, K.; Leung, R.; Du, J. LDPC Code Design for Delayed Bit-Interleaved Coded Modulation. In Proceedings of the 2019 IEEE Information Theory Workshop (ITW), Visby, Sweden, 25–28 August 2019. [Google Scholar]

- Du, J.; Wang, Z.; Xiao, L.; Wang, L.; Qiao, W. LDPC coded DBICM Scheme for Two Way Relay Channel with a Pipeline Decoding Structure. In Proceedings of the 2018 IEEE International Conference on Communication Systems (ICCS), Chengdu, China, 19–21 December 2018. [Google Scholar]

- Yang, R.; Sherratt, R.S. Enhancing MB-OFDM throughput with dual circular 32-QAM. IEEE Trans. Consum. Electron. 2008, 54, 1640–1646. [Google Scholar] [CrossRef]

- Wake, D.; Dupont, S.; Lethien, C.; Vilcot, J.-P.; Decoster, D. Radiofrequency transmission of 32-QAM signals over multimode fibre for distributed antenna system applications. Electron. Lett. 2001, 37, 1087–1089. [Google Scholar] [CrossRef]

- Zhalehpour, S.; Guo, M.; Lin, J.; Zhang, Z.; Qiao, Y.; Shi, W.; Rusch, L.A. System Optimization of an All-Silicon IQ Modulator: Achieving 100-Gbaud Dual-Polarization 32QAM. J. Lightwave Technol. 2020, 38, 256–264. [Google Scholar] [CrossRef]

- Hamaoka, F.; Nakamura, M.; Nagatani, M.; Kobayashi, T.; Matsushita, A.; Wakita, H.; Yamazaki, H.; Nosaka, H.; Miyamoto, H. 120-GBaud 32QAM Signal Generation using Ultra-Broadband Electrical Bandwidth Doubler. In Proceedings of the Optical Fiber Communication Conference, San Diego, CA, USA, 3–7 March 2019. [Google Scholar]

- Hu, X.; Eleftheriou, E.; Arnold, D.M. Regular and irregular progressive edge-growth tanner graphs. IEEE Trans. Info. Theory 2005, 51, 386–398. [Google Scholar] [CrossRef]

- Storn, R.; Price, K. Differential evolution simple and efficient heuristic for global optimization over continuous spaces. J. Global Optim. 1997, 11, 341–359. [Google Scholar] [CrossRef]

- Morello, A.; Mignone, V. DVB-S2: The Second Generation Standard for Satellite Broad-Band Services. Proc. IEEE 2006, 94, 210–227. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).