Design of an Edge-Detection CMOS Image Sensor with Built-in Mask Circuits

Abstract

:1. Introduction

2. Design of the Proposed Edge-Detection CMOS Image Sensor

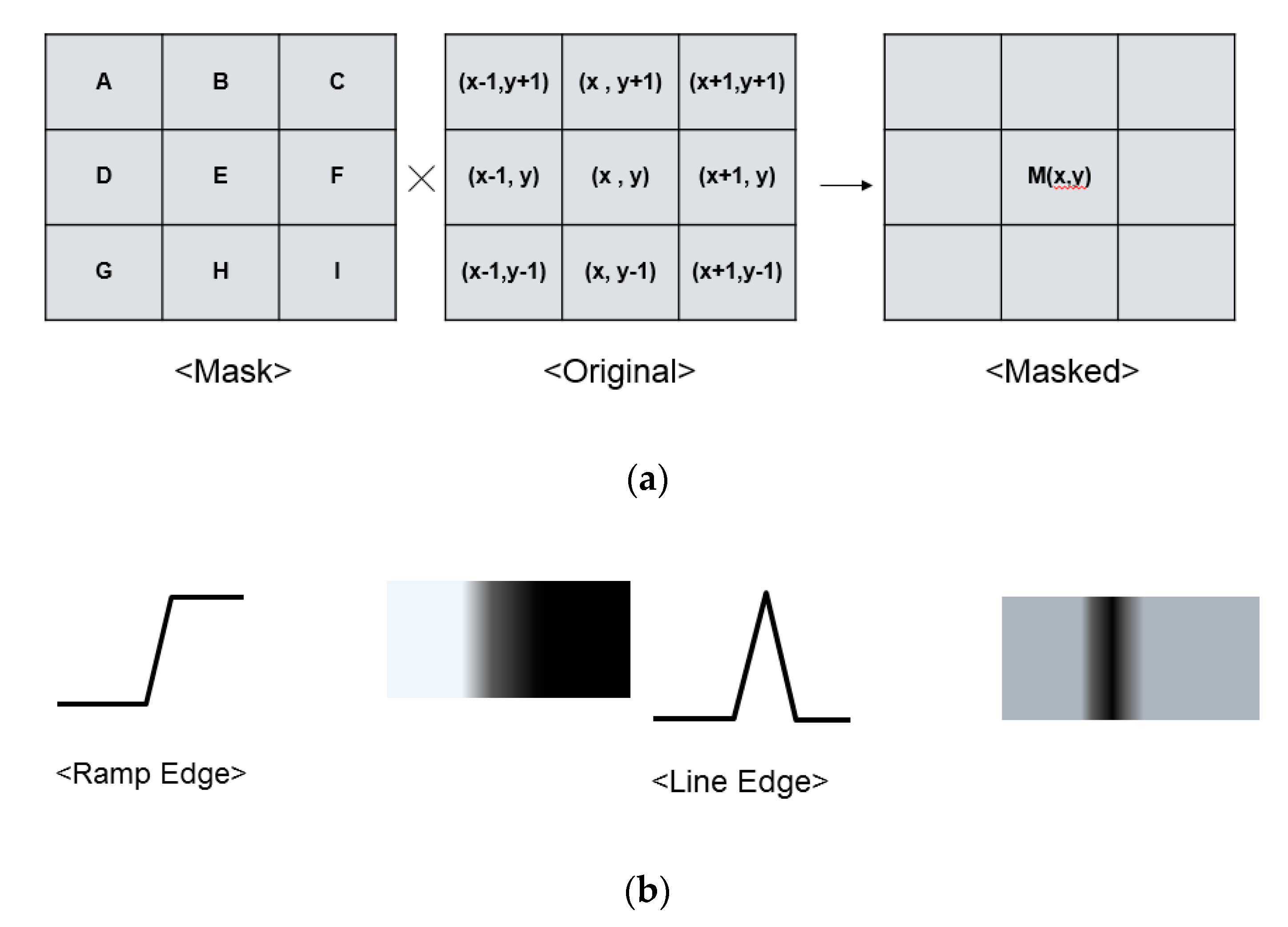

2.1. Existing Edge-Detection Mask Algorithm

2.2. Proposed Algorithm for Edge Detection

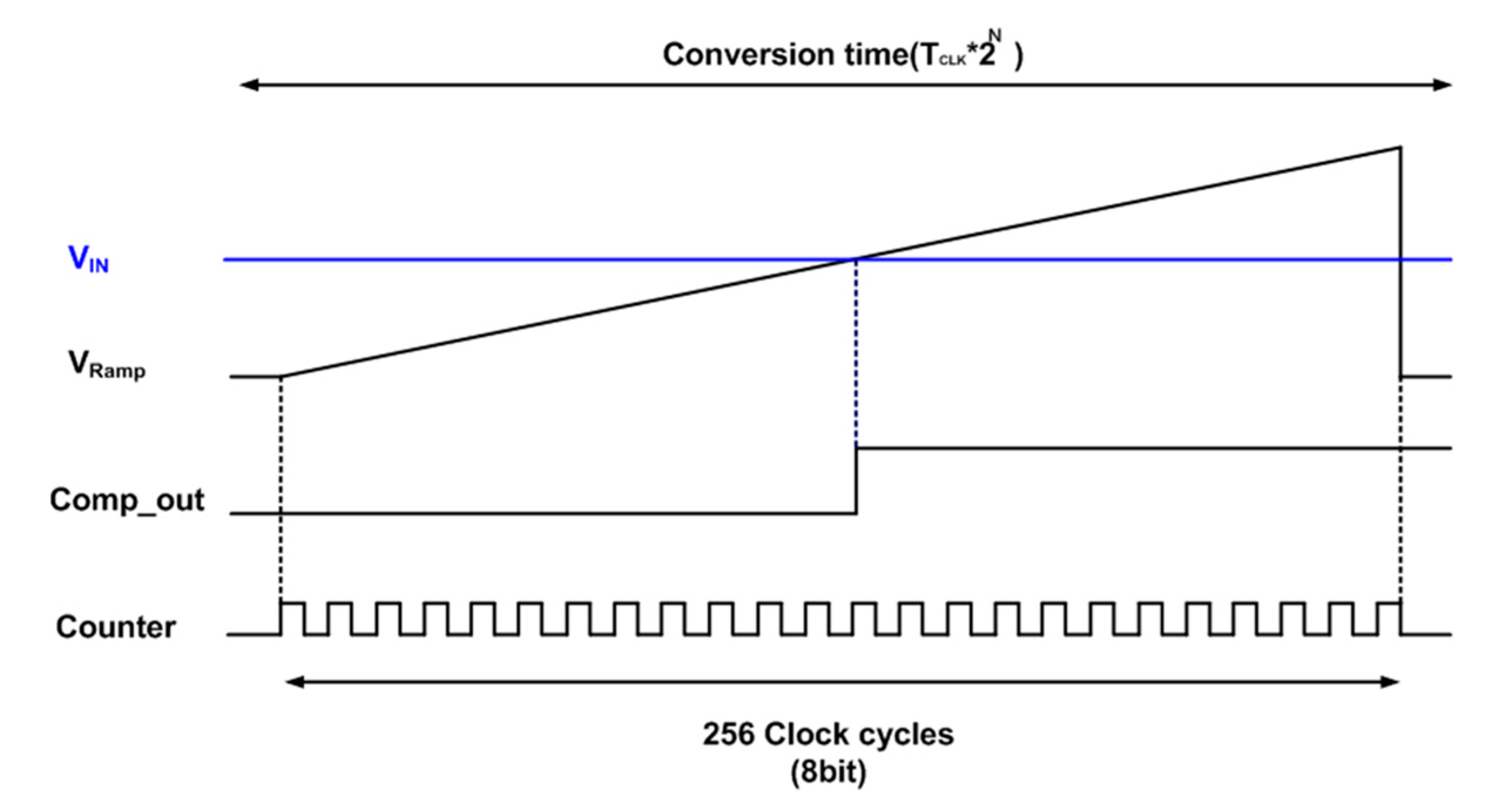

2.3. Operation Principle of the Edge-Detection CMOS Image Sensor

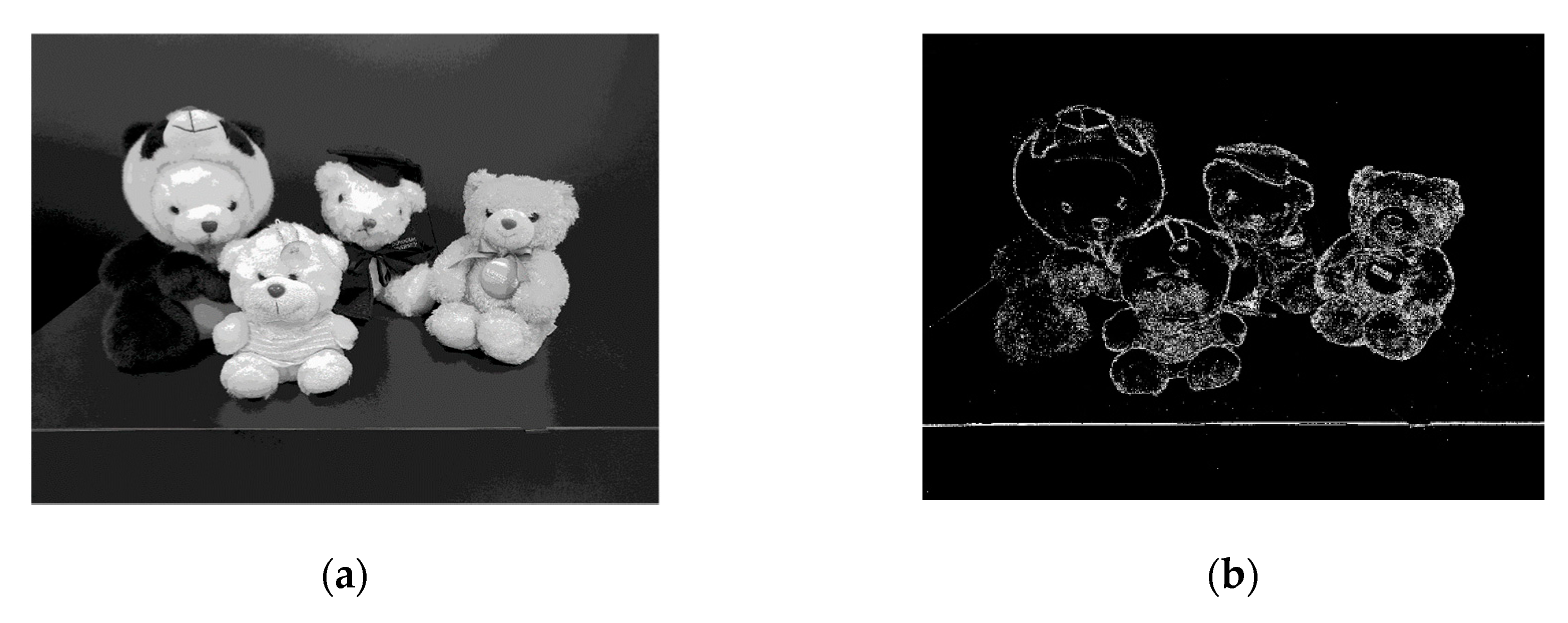

3. Experimental Results

3.1. Simulation Results and a Chip Photograph

3.2. Measurement Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Qu, C.; Bi, D.-Y.; Sui, P.; Chao, A.-N.; Wang, Y.-F. Robust Dehaze Algorithm for Degraded Image of CMOS Image Sensors. Sensors 2017, 17, 2175. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Park, C.; Kim, W.; Yeo, I. An event detection module with a low-power, small-size CMOS image sensor with reference scaling. Analog Integr. Circuits Signal Process. 2019, 99, 359–369. [Google Scholar] [CrossRef]

- Kim, D.; Song, M.; Choe, B.; Kim, S.Y. A Multi-Resolution Mode CMOS Image Sensor with a Novel Two-Step Single-Slope ADC for Intelligent Surveillance Systems. Sensors 2017, 17, 1497. [Google Scholar] [CrossRef] [PubMed]

- Choi, J.; Shin, J.; Kang, D.; Park, D. Always-On CMOS Image Sensor for Mobile and Wearable Devices. IEEE J. Solid-State Circuits 2016, 51, 130–140. [Google Scholar] [CrossRef]

- Norihiro, T.; Shibata, T. A row-parallel cyclic-line-access edge detection CMOS image sensor employing global thresholding operation. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010; pp. 625–628. [Google Scholar]

- Lee, C.; Chao, W.; Lee, S.; Hone, J.; Molnar, A.H.; Hong, S. A Low-Power Edge Detection Image Sensor Based on Parallel Digital Pulse Computation. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 1043–1047. [Google Scholar] [CrossRef]

- Park, K.; Song, M.; Kim, S.Y. The Design of a Single-Bit CMOS Image Sensor for Iris Recognition Applications. Sensors 2018, 18, 669. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Choi, J.; Park, S.; Cho, J.; Yoon, E. A 1.36 W adaptive CMOS image sensor with reconfigurable modes of operation from available energy/illumination for distributed wireless sensor network. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 112–114. [Google Scholar]

- Choi, J.; Park, S.; Cho, J.; Yoon, E. A 3.4 μW Object-Adaptive CMOS Image Sensor with Embedded Feature Extraction Algorithm for Motion-Triggered Object-of-Interest Imaging. IEEE J. Solid-State Circuits 2014, 49, 289–300. [Google Scholar] [CrossRef]

- Posch, C.; Matolin, D.; Wohlgenannt, R. A QVGA 143 dB dynamic range frame-free PWM image sensor with lossless pixel-level video compression and time-domain CDS. IEEE J. Solid-State Circuits 2011, 46, 259–275. [Google Scholar] [CrossRef]

- Brandli, C.; Berner, R.; Yang, M.; Liu, S.-C.; Delbruck, T. A 240 × 180 130dB 3us Latency Global Shutter Spatiotemporal Vision Sensor. IEEE J. Solid-State Circuits 2014, 49, 2333–2341. [Google Scholar] [CrossRef]

- Lichtsteiner, P.; Posch, C.; Delbruck, T. A 128 × 128 120dB 30mW asynchronous vision sensor that responds to relative intensity change. In Proceedings of the 2006 IEEE International Solid State Circuits Conference, San Francisco, CA, USA, 6–9 February 2006; pp. 2060–2069. [Google Scholar]

- Ni, Z.; Pacoret, C.; Benosman, R.; Ieng, S.-H.; Régnier, S. Asynchronous event-based high speed vision for microparticle tracking. J. Microsc. 2012, 245, 236–244. [Google Scholar] [CrossRef]

- Delbruck, T.; Lang, M. Robotic Goalie with 3 ms reaction time at 4% CPU load using event-based dynamic vision sensor. Front. Neurosci. 2013, 7, 223. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Park, K.; Jin, M.; Kim, S.Y.; Song, M. Design of a high speed CMOS image sensor with a hybrid single-slope column ADC and a finite state machine. In Proceedings of the 2017 International SoC Design Conference (ISOCC), Seoul, Korea, 5–8 November 2017; pp. 95–96. [Google Scholar]

- Shin, M.; Kim, J.; Kim, M.; Jo, Y.; Kwon, O. A 1.92-Mega pixel CMOS Image Sensor with Column-Parallel Low-Power and Area Efficient SA-ADCs. IEEE Trans. Electron Devices 2012, 59, 1693–1700. [Google Scholar] [CrossRef]

- Canny, J. A computational approach to edge detection. IEEE Trans. Pattern Anal. Mach. Intell. 1986, 8, 679–698. [Google Scholar] [CrossRef] [PubMed]

- Hongfei, L.; Yongshun, H.; Mingfeng, L.; Lin, W. A Simple and Impactful Approach to Detect the Edge of Space Images. In Proceedings of the International Conference on Information Engineering and Computer Science, Wuhan, China, 19–20 December 2009; pp. 1–4. [Google Scholar]

- Suzuki, A.; Shimamura, N.; Kainuma, T.; Kawazu, N.; Okada, C.; Oka, T.; Koise, K.; Masagaki, A.; Yagasaki, Y.; Gonoi, S.; et al. 6.1 A 1/1.7-inch 20Mpixel Back-Illuminated Stacked CMOS Image Sensor for New Imaging Applications. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 110–111. [Google Scholar]

- Kłosowski, M.; Jendernalik, W.; Jakusz, J.; Blakiewicz, G.; Szczepański, S. A CMOS Pixel with Embedded ADC, Digital CDS and Gain Correction Capability for Massively Parallel Imaging Array. IEEE Trans. Circuits Systems-I: Regul. Pap. 2016, 64, 38–49. [Google Scholar] [CrossRef]

- Totsuka, H.; Tsuboi, T.; Muto, T.; Yoshida, D.; Matsuno, Y.; Ohmura, M.; Takahashi, H.; Sakurai, K.; Ichikawa, T.; Yuzurihara, H.; et al. 6.4 An APS-H-Size 250Mpixel CMOS Image Sensor Using Column Single-Slope ADCs with Dual-Gain Amplifiers. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 31 January–4 February 2016; pp. 116–117. [Google Scholar]

- Liu, C.C.-M.; Mhala, M.M.; Chang, C.-H.; Tu, H.; Chou, P.-S.; Chao, C.; Hsueh, F.-L. 6.8 A 1.5V 33Mpixel 3D-Stacked CMOS Image Sensor with Negative Substrate Bias. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 31 January–4 February 2016; pp. 124–125. [Google Scholar]

- Boukhayma, A.; Peizerat, A.; Enz, C. A Sub-0.5 Electron Read Noise VGA Image Sensor in a Standard CMOS Process. IEEE J. Solid-State Circuits 2016, 51, 2180–2191. [Google Scholar] [CrossRef]

- Spivak, A.; Belenky, A.; Yadid-Pecht, O. Very Sensitive Low-Noise Active-Reset CMOS Image Sensor with In-Pixel ADC. IEEE Trans. Circuits Syst.-II Express Briefs 2016, 63, 939–943. [Google Scholar] [CrossRef]

- Chiou, A.Y.-C.; Hsieh, C.-C. A 137 dB Dynamic Range and 0.32 V Self-Powered CMOS Imager with Energy Harvesting Pixels. IEEE J. Solid-State Circuits 2016, 51, 2769–2776. [Google Scholar] [CrossRef]

- Kobayashi, M.; Onuki, Y.; Kawabata, K.; Sekine, H.; Tsuboi, T.; Matsuno, Y.; Takahashi, H.; Koizumi, T.; Sakurai, K.; Yuzurihara, H.; et al. 4.5 A 1.8e-rms Temporal Noise over 110dB Dynamic Range 3.4μm Pixel Pitch Global Shutter CMOS Image Sensor with Dual-Gain Amplifiers, SS-ADC and Multiple Accumulation Shutter. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 74–75. [Google Scholar]

- Kim, H.-J.; Hwang, S.I.; Kwon, J.W.; Jin, D.H.; Choi, B.S.; Lee, S.G.; Park, J.-H.; Shin, J.-K.; Ryu, S.-T. A delta-readout scheme for low-power CMOS image sensors with multi-column-parallel SAR ADCs. IEEE J. Solid-State Circuits 2016, 51, 2262–2273. [Google Scholar] [CrossRef]

- Park, K.; Kim, S.Y. Low-power column counter with a logical-shift algorithm for CMOS image sensors. Electron. Lett. 2020, 56, 232–234. [Google Scholar] [CrossRef]

- Pande, S.; Bhadouria, V.S.; Ghoshal, D. A study on edge marking scheme of various standard edge detectors. Int. J. Comput. Appl. 2012, 44, 33–37. [Google Scholar] [CrossRef]

| Corner | Max. | Min. | Mean | Std. Dev |

|---|---|---|---|---|

| Best | 1.010 | 0.969 | 0.980 | 6.16 × 10−3 |

| Nominal | 1.010 | 0.970 | 0.981 | 5.17 × 10−3 |

| Worst | 1.250 | 0.924 | 0.983 | 1.80 × 10−2 |

| PFOM (%) | Sobel | Roberts | Prewitt | This Work |

|---|---|---|---|---|

| Sobel (reference) | 100 | 96.50 | 99.75 | 94.96 |

| Array Format | FHD (1920 × 1440) |

|---|---|

| Pixel Size | 1.4 µm × 1.4 µm |

| ADC Resolution | 8-bit |

| Frame Rate | 60 fps |

| Dynamic Range | 61 dB |

| Power Supply | 3.3 V (analog)/2.8 V (pixel)/1.2 V (digital) |

| Power Consumption | 9.4 mW |

| 90 µW (per column) | |

| 0.4 µW (per column at power shutoff) | |

| Area | 26.57 mm2 (5.15 mm × 5.15 mm) |

| Process | 90-nm 1P5M BSI CIS |

| [5] | [6] | [7] | This Work | |

|---|---|---|---|---|

| Edge Image |  |  |  |  |

| Process | 0.18-µm 1P 5M CMOS | 0.18-µm 1P 4M CIS | 0.18-µm 1P 4M CIS | 90-nm 1P 5M CIS |

| Resolution | 70 × 68 | 105 × 92 | 174 × 144 | 1920 × 1440 |

| Pixel Pitch | 25.7 µm | 8 µm | 2.2 µm | 1.4 µm |

| Voltage Supply | 1.8 V | 1.6 V | 3.3 V | 3.3 V |

| Frame/s | 28 | 30 | 520 | 60 |

| Power | 110 mW | 8 mW | 2.8 mW (60 fps) | 9.4 mW (60 fps) |

| Fill Factor | 17% | 11.69% | 40% | 52.55% |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jin, M.; Noh, H.; Song, M.; Kim, S.Y. Design of an Edge-Detection CMOS Image Sensor with Built-in Mask Circuits. Sensors 2020, 20, 3649. https://doi.org/10.3390/s20133649

Jin M, Noh H, Song M, Kim SY. Design of an Edge-Detection CMOS Image Sensor with Built-in Mask Circuits. Sensors. 2020; 20(13):3649. https://doi.org/10.3390/s20133649

Chicago/Turabian StyleJin, Minhyun, Hyeonseob Noh, Minkyu Song, and Soo Youn Kim. 2020. "Design of an Edge-Detection CMOS Image Sensor with Built-in Mask Circuits" Sensors 20, no. 13: 3649. https://doi.org/10.3390/s20133649

APA StyleJin, M., Noh, H., Song, M., & Kim, S. Y. (2020). Design of an Edge-Detection CMOS Image Sensor with Built-in Mask Circuits. Sensors, 20(13), 3649. https://doi.org/10.3390/s20133649