Author Contributions

Conceptualization and patent, S.M. and D.Y.; investigation, T.Z. and S.M.; package structure design and fabrication, S.M. and T.Z.; reliability analysis, S.M., T.Z. and T.H.; writing—original draft preparation, T.Z. and T.H.; writing—review and editing, D.Y., S.M. and M.L.; supervision, D.Y. and M.L.; project administration, S.M. All authors have read and agreed to the published version of the manuscript.

Figure 1.

Image devices used in ADAS for automotive application.

Figure 1.

Image devices used in ADAS for automotive application.

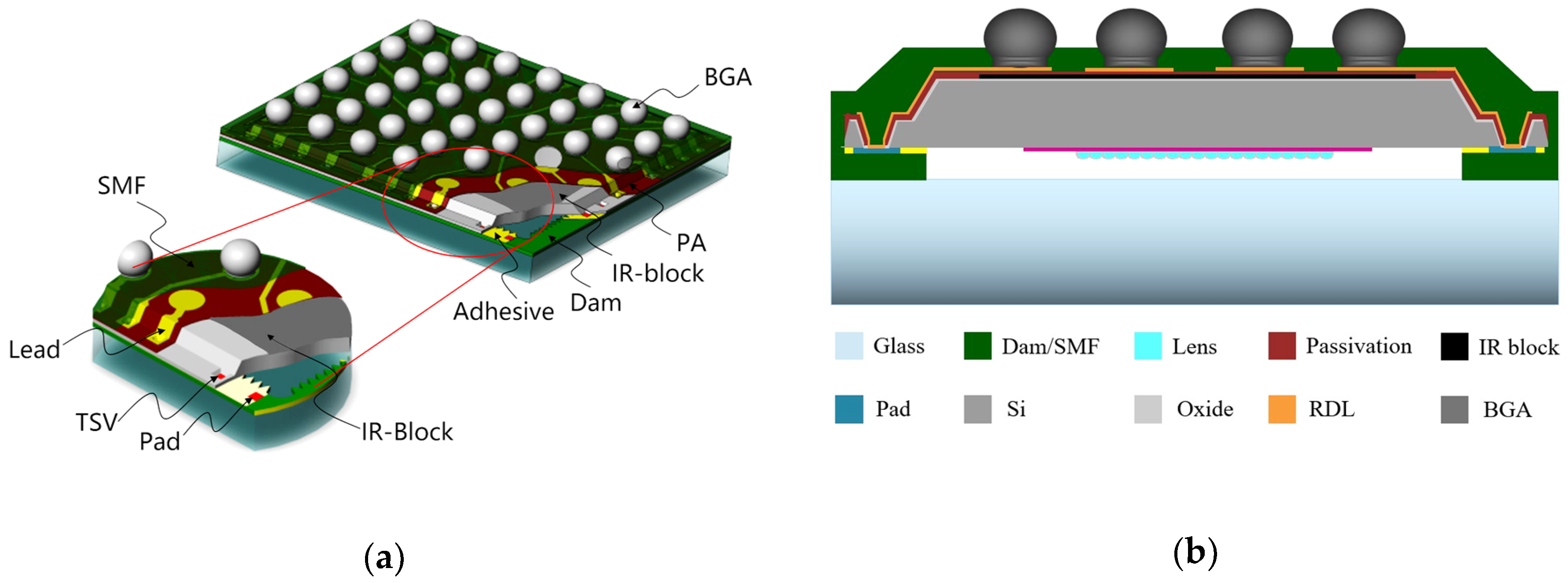

Figure 2.

The schematic of the package (a) 3D view of the CIS-WLCSP structure; (b) Cross-section of the CIS-WLCSP structure.

Figure 2.

The schematic of the package (a) 3D view of the CIS-WLCSP structure; (b) Cross-section of the CIS-WLCSP structure.

Figure 3.

The schematic of CIS-WLCSP process flow.

Figure 3.

The schematic of CIS-WLCSP process flow.

Figure 4.

Package failure modes after TC test. (a) Pad delamination in the bottom of the TSV; (b) RDL crack near the UBM neck.

Figure 4.

Package failure modes after TC test. (a) Pad delamination in the bottom of the TSV; (b) RDL crack near the UBM neck.

Figure 5.

The strip model of the WLSCP in ABAQUS.

Figure 5.

The strip model of the WLSCP in ABAQUS.

Figure 6.

Stress distribution of pad in one TC cycle.

Figure 6.

Stress distribution of pad in one TC cycle.

Figure 7.

The strip model of WLCSP for different UBM design.

Figure 7.

The strip model of WLCSP for different UBM design.

Figure 8.

Stress distribution of pad in one TC cycle.

Figure 8.

Stress distribution of pad in one TC cycle.

Figure 9.

(a) Adhesive overflowed the CV dam; (b) flare image issue caused by dam glue reflection.

Figure 9.

(a) Adhesive overflowed the CV dam; (b) flare image issue caused by dam glue reflection.

Figure 10.

(a) Schematic of adhesive glue stencil print; (b) Adhesive glue control within CV dam tooth.

Figure 10.

(a) Schematic of adhesive glue stencil print; (b) Adhesive glue control within CV dam tooth.

Figure 11.

(a) Transmittance and (b) reflectance spectra of the double coating AR glass.

Figure 11.

(a) Transmittance and (b) reflectance spectra of the double coating AR glass.

Figure 12.

(a) Schematic of IR-block; (b) OM image of IR-block process.

Figure 12.

(a) Schematic of IR-block; (b) OM image of IR-block process.

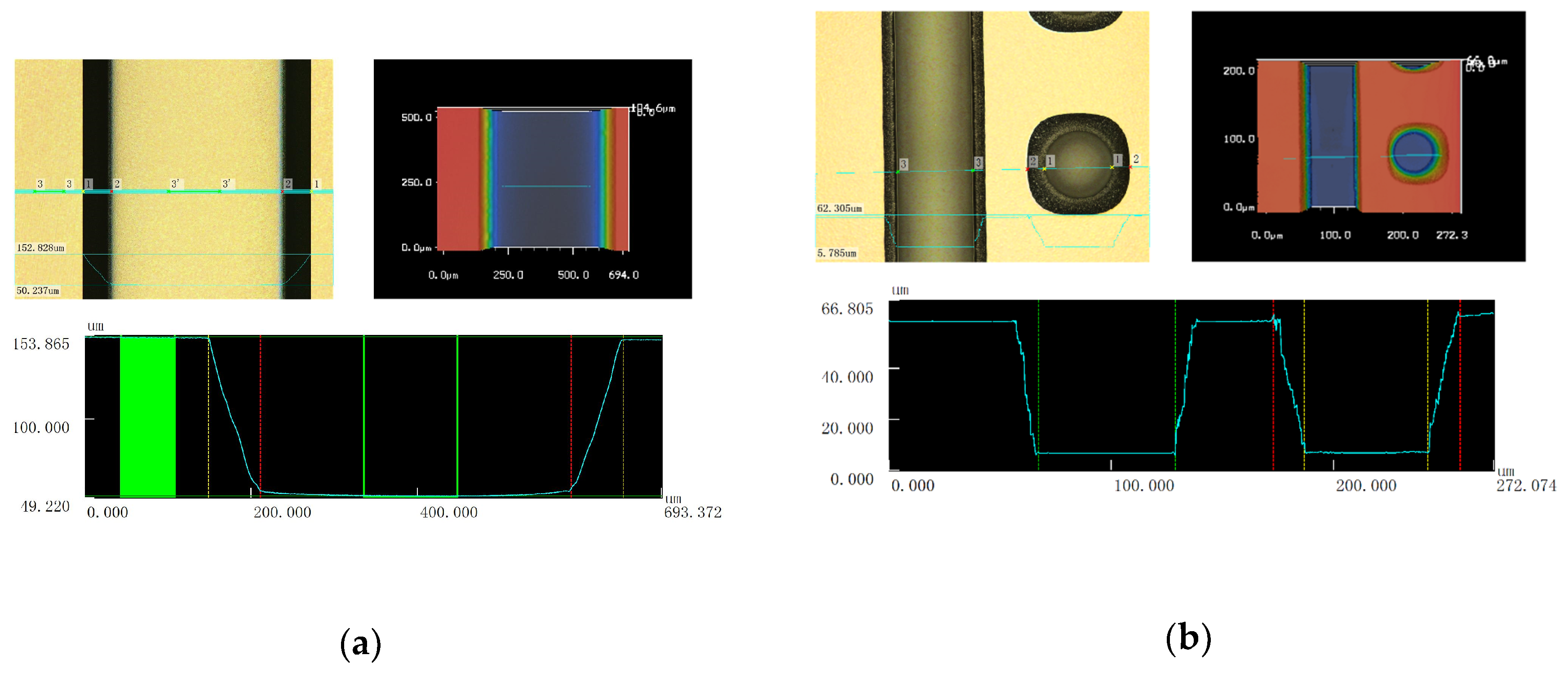

Figure 13.

Three-dimensional microscope image of (a) the silicon trench and (b) the trench and tapered via.

Figure 13.

Three-dimensional microscope image of (a) the silicon trench and (b) the trench and tapered via.

Figure 14.

(a) The outlook of the wafer after PECVD process. (b) The SEM cross-section images of die surface, trench sidewall and via corner.

Figure 14.

(a) The outlook of the wafer after PECVD process. (b) The SEM cross-section images of die surface, trench sidewall and via corner.

Figure 15.

The outlook of the via after second passivation layer formation.

Figure 15.

The outlook of the via after second passivation layer formation.

Figure 16.

The outlook of the wafer after electroless-plating Ni/Au.

Figure 16.

The outlook of the wafer after electroless-plating Ni/Au.

Figure 17.

The OM image of SMF and UBM opening.

Figure 17.

The OM image of SMF and UBM opening.

Figure 18.

OM image and cross-section SEM image of the solder ball.

Figure 18.

OM image and cross-section SEM image of the solder ball.

Figure 19.

The outlook of CIS-WLCSP (a) BGA side; (b) Sensor side.

Figure 19.

The outlook of CIS-WLCSP (a) BGA side; (b) Sensor side.

Figure 20.

The cross-section SEM image of CIS-WLCSP.

Figure 20.

The cross-section SEM image of CIS-WLCSP.

Table 1.

Material property related to the package.

Table 1.

Material property related to the package.

| Property/Material | Si | SiO2 | PA | Cu | SMF |

|---|

| CTE (ppm/°C) | 2.8 | 0.5 | 54.0 | 16.9 | 58.0 |

| Young’s module (GPa) | 131.0 | 70.0 | 2.5 | 129.0 | 4.6 |

Table 2.

The max S33 stress in the pad center for different structure design.

Table 2.

The max S33 stress in the pad center for different structure design.

| Value/Condition | 1 | 2 | 3 | 4 |

|---|

| Si_T1/Si_T2 (μm) | 90/60 | 100/50 | 100/50 | 100/50 |

| Via opening (μm) | 55 | 55 | 50 | 45 |

| Max stress (MPa) | 71.8 | 70.2 | 65.8 | 61.5 |

Table 3.

The max von Mises stress of different UBM design.

Table 3.

The max von Mises stress of different UBM design.

| Value/θ | 0° | 45° | 90° | 120° | 135° |

|---|

| Max stress (MPa) | 437.7 | 458.2 | 428.2 | 410.7 | 406.5 |

| Failure rate of TC 1000 cycle | 6.7% | 8.9% | 4.4% | 0 | 0 |

Table 4.

The silicon thickness in Grind and E1 process.

Table 4.

The silicon thickness in Grind and E1 process.

| Process | Point 1 | Point 2 | Point 3 | Point 4 | Point 5 | AVG. | SPEC |

|---|

| Grind/μm | 157 | 157 | 158 | 159 | 157 | 158 | 160 ± 5 |

| E1/μm | 147 | 153 | 154 | 150 | 150 | 151 | 150 ± 5 |

Table 5.

The top opening and depth of the trench in E2 process.

Table 5.

The top opening and depth of the trench in E2 process.

| Item | Point 1 | Point 2 | Point 3 | Point 4 | Point 5 | AVG. | SPEC |

|---|

| Top opening/μm | 504 | 503 | 496 | 504 | 500 | 501 | 500 ± 20 |

| Depth/μm | 102 | 101 | 101 | 102 | 101 | 101 | 100 ± 5 |

Table 6.

The top opening width, bottom opening width and depth of via in the E3 process.

Table 6.

The top opening width, bottom opening width and depth of via in the E3 process.

| Item | Point 1 | Point 2 | Point 3 | Point 4 | Point 5 | AVG. | SPEC |

|---|

| Top opening/μm | 84 | 84 | 86 | 87 | 89 | 86 | 85 ± 10 |

| Bottom opening/μm | 49 | 52 | 53 | 53 | 52 | 52 | 50 ± 5 |

| Depth/μm | 49 | 50 | 53 | 52 | 53 | 51 | 50 ± 5 |

Table 7.

The thicknesses of oxide in die surface, trench sidewall and via corner in PECVD process.

Table 7.

The thicknesses of oxide in die surface, trench sidewall and via corner in PECVD process.

| Item | Point 1 | Point 2 | Point 3 | Point 4 | Point 5 | AVG. | SPEC |

|---|

| Die surface/μm | 0.87 | 0.88 | 0.87 | 0.90 | 0.93 | 0.89 | 0.9 ± 0.2 |

| Trench sidewall/μm | 1.03 | 0.73 | 1.01 | 0.83 | 0.92 | 0.90 | >0.3 |

| Via corner/μm | 0.39 | 0.40 | 0.36 | 0.50 | 0.42 | 0.41 | >0.3 |

Table 8.

The thicknesses of PA in die surface, trench sidewall and via corner in second PA process.

Table 8.

The thicknesses of PA in die surface, trench sidewall and via corner in second PA process.

| Item | Point 1 | Point 2 | Point 3 | Point 4 | Point 5 | AVG. | SPEC |

|---|

| Die surface/μm | 6.1 | 6.3 | 6.1 | 5.8 | 6.5 | 6.2 | 6 ± 2 |

| Trench sidewall/μm | 6.2 | 5.5 | 5.3 | 5.7 | 6.5 | 5.8 | >2 |

| Via corner/μm | 2.6 | 3.4 | 2.0 | 3.3 | 3.3 | 2.9 | >2 |

Table 9.

The thicknesses of Cu, Ni, and Au in RDL formation process.

Table 9.

The thicknesses of Cu, Ni, and Au in RDL formation process.

| Item | Point 1 | Point 2 | Point 3 | Point 4 | Point 5 | AVG. | SPEC |

|---|

| Cu/μm | 2.5 | 2.3 | 2.4 | 2.7 | 2.6 | 2.5 | 2.5 ± 1 |

| Ni/μm | 3.3 | 3.1 | 3.2 | 3.3 | 3.1 | 3.2 | 3 ± 1 |

| Au/nm | 99 | 98 | 97 | 96 | 97 | 97 | >60 |

Table 10.

The ball height, ball diameter and ball shear strength of solder ball in BGA process.

Table 10.

The ball height, ball diameter and ball shear strength of solder ball in BGA process.

| Item | Point 1 | Point 2 | Point 3 | Point 4 | Point 5 | AVG. | SPEC |

|---|

| Height/μm | 248 | 250 | 260 | 245 | 251 | 251 | 250 ± 30 |

| Diameter/μm | 307 | 312 | 310 | 306 | 306 | 308 | 300 ± 30 |

| Shear strength /gf | 330 | 322 | 291 | 287 | 309 | 308 | >200gf |

Table 11.

Reliability test items and results.

Table 11.

Reliability test items and results.

| Test Item | Condition | Read Point | Samples | Failure |

|---|

| Pre-con | MSL3(30 °C /60%RH) | 192 h | 231 ea/lot*3 | 0 |

| HTS | 125 °C | 1008 h | 77 ea/lot*3 | 0 |

| LTS | −40 °C | 1008 h | 0 |

| THS | 85 °C/85%RH | 1008 h | 0 |

| THB | 85 °C/85%RH +Bias | 1008 h | 0 |

| TC-B | −55 °C~125 °C | 1000 cycles | 0 |