Abstract

This paper introduces a new current-controlled current-amplifier suitable for precise measurement applications. This amplifier was developed with strong emphasis on linearity leading to low total harmonic distortion (THD) of the output signal, and on linearity of the gain control. The presented circuit is characterized by low input and high output impedances. Current consumption is significantly smaller than with conventional quadratic current multipliers and is comparable in order to the maximum processed input current, which is ±200 µA. This circuit is supposed to be used in many sensor applications, as well as a precise current multiplier for general analog current signal processing. The presented amplifier (current multiplier) was designed by an uncommon topology based on linear sub-blocks using MOS transistors working in their linear region. The described circuit was designed and fabricated in a C035 I3T25 0.35-µm ON Semiconductor process because of the demand of the intended application for higher supply voltage. Nevertheless, the topology is suitable also for modern smaller CMOS technologies and lower supply voltages. The performance of the circuit was verified by laboratory measurement with parameters comparable to the Cadence simulation results and presented here.

1. Introduction

The adjustable current amplifiers [1,2] have significant application over many electronic circuits and systems. Several interesting solutions have been introduced during the last decades as shown in comparison Table 1. The development of these devices goes in parallel with development of so-called current conveyors (CC) and their adjustable features [2]. The first attempts were evaluated in works [3,4] as parts of CCs (partial two-port transfer available by the device). Both cases implement a ratio of two bias currents for current gain adjustment. This way of adjustment is used very often also in further solutions. More advanced devices were proposed in [5,6,7,8,9,10,11,12,13,14,15,16,17,18,19,20] for example. They offer interesting features discussed in detail in Table 1 Work [8] presents current amplifier feature allowing gain setting by ratio of resistors (no electronic adjustment is shown). However, this concept of current gain setting (unfortunately of the fixed value) is also possible. This can be extended to adjustable control through the replacement of passive element (appropriate replacement is a digital potentiometer or linear operational transconductance amplifier). Many concepts intend digital adjustment of the current gain [5], [14,15,16,17] that is useful for direct cooperation with microprocessors. However, continuous adjustment of the gain is more beneficial for many applications (smooth tuning of filters or automatic amplitude stabilization in oscillators [18]).

Table 1.

Comparison of features of adjustable current amplifiers or active devices including transfer response of adjustable current amplifier reported in recent works.

Table 1 shows that the majority of solutions is based on bipolar junction transistors, exploiting the benefit of exponential characteristics specially in the accurate current multipliers discussed below. These bipolar topologies meet well the requirements for the exact functionality, good dynamic range and speed (commonly in tens of MHz and more), but at the cost of a large area and current consumption (standardly not mentioned), which is no longer acceptable in the small CMOS technologies [3,4,7,9,10,11,12,16,17]. A large number of previous concepts (CMOS especially) was not tested experimentally, mostly just simple simulation results are shown (without modeling of real effects in many cases) [5,6,7,8,10,11,13,14,15,17]. Very high input impedance (DC resistive component) as well as low output impedance indicate significant drawback of many previous solutions. Special cases are the solutions presented in [7,15]. However, the adjustability of any parameter, but especially the gain, can be often welcomed for electronic tuning of applications in many cases [12,13,16,17]. The output impedance of current output circuits is the most significant issue because of the parasitic behavior occurring in high-impedance nodes of applications (typically in active filters [9]). We can see that situation of state-of-the-art is insufficient in many BJT-based cases [9,11,15,17]. The CMOS-based topologies have significantly better output features, see [21,22]. Work presented by Esparza-Alfaro [21] demonstrates a concept using two CCs and resistor feedback for current gain setting.

The current-mode multipliers are important for our discussion due to similarity of newly proposed concept also using principle of two-quadrant multiplier. Comprehensive comparison [28,29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51,52,53,54,55,56,57,58,59,60,61,62,63,64,65,66,67,68] in Table 2 indicates missing details and incomplete topologies for full implementation in current multiplication or amplification because structures are not designed as fully symmetrical form. They operate with intentional superposition of DC component or principal topology, not including all important parts, in order to obtain behavior required in this work. However, many works [31,33,47,60,67,68] use single or two partial active devices (specified types of current conveyors) in design of current-mode multipliers and fully symmetrical operation (processing of both signal polarities) is easily possible in this form. Usage of OTA-based structures seems to be also very interesting in these nonlinear designs [32,39,44]. It offers building blocks for many nonlinear functions [69]. Logarithmic-domain-based structures are also known in reported concepts [32]. Also, concepts combining conveyors and operational transconductance amplifiers are known [34,64]. There are many possible design approaches exist. However, each of them can be used differently for various purposes and requirements on resulting circuit and application.

Table 2.

Comparison of recent current-mode multipliers.

Many works from Table 2 suffer from very limited input range of current (below 100 µA), some solutions operate even in nA range that is really insufficient in many practical cases. Despite extremely low power consumption, there are issues with noise and bandwidth limitations. Advantages of the newly proposed solution include quite large input range of linearity ±200 µA (in comparison with other works in Table 2), very low total harmonic distortion (THD) below 0.25%, extremely low input resistance (below 2 Ω), very high output resistance (4 MΩ), and beneficial power consumption. The linearity error is expressed as the ratio error between the maximum and minimum value of the parameter obtained by derivation of the transfer function in the given linearity range and was measured below 6% for the presented circuit. There are solutions having even lower power requirements, unfortunately, there are costs (bandwidth, input range, DC accuracy, etc.) for such benefit in corresponding works. Unfortunately, many detailed parameters of compared solutions are unknown.

As the objective of this work, the precise highly linear current amplifier has been requested for measurement applications handling current signal, conveniently in current sensor processing circuits, especially for the smart sensor ASIC measurement solution. Currently, the main intended usage of the circuit is an automatic gain control current amplifier for precise harmonic reference generator used in Capacitive sensor measurement. The similar solution of the precise sinus reference source like in [70] is assumed to be used and is just under development. While, the referenced circuit is based on the digitally generated voltage reference signal with tunable low-pass filter, the new solution uses the current reference generator, with fixed frequency filter, followed by the current amplifier with gain controlled by the similar principle as is described in the paper [70]. Due to the demand of the supposed capacitive measurement method, this amplifier was developed serving the very low THD as the main parameter because of the assumed derivative signal processing, emphasizing any higher harmonic components of the reference signal.

Furthermore, many modern sensor applications use a high-quality ADC for digitization of the signal where any signal distortion during the analog pre-processing degrades the performance of the ADC.

Generally, this type of circuit is especially suitable to realize tunable multi-output current-mode generators as well, where good accuracy and low THD is also requested. Amplitude modulation of the current signal is another tailor-made application for the presented circuit. However, the designed amplifier prototype has been optimized for use in precise measurement applications processing high current signals.

With respect to the intended application requirements an objective of the work was to develop and design an adjustable accurate current amplifier for current sensor signal processing, and other precise current measurement application, having fulfilled these features simultaneously:

- (a)

- low total harmonic distortion of the processed current signal as the most considered parameter (<1%)

- (b)

- wide and linear input range (about ±200 µA)

- (c)

- very low input resistance (<10 Ω)

- (d)

- high output impedance (>1 MΩ)

- (e)

- adjustability of current gain (theoretically 0–2)

- (f)

- high linearity of the gain control for current gain B < 0.8

- (g)

- acceptable power consumption (comparing to the process signal current) below 5 mW

2. Circuit Principle and Design

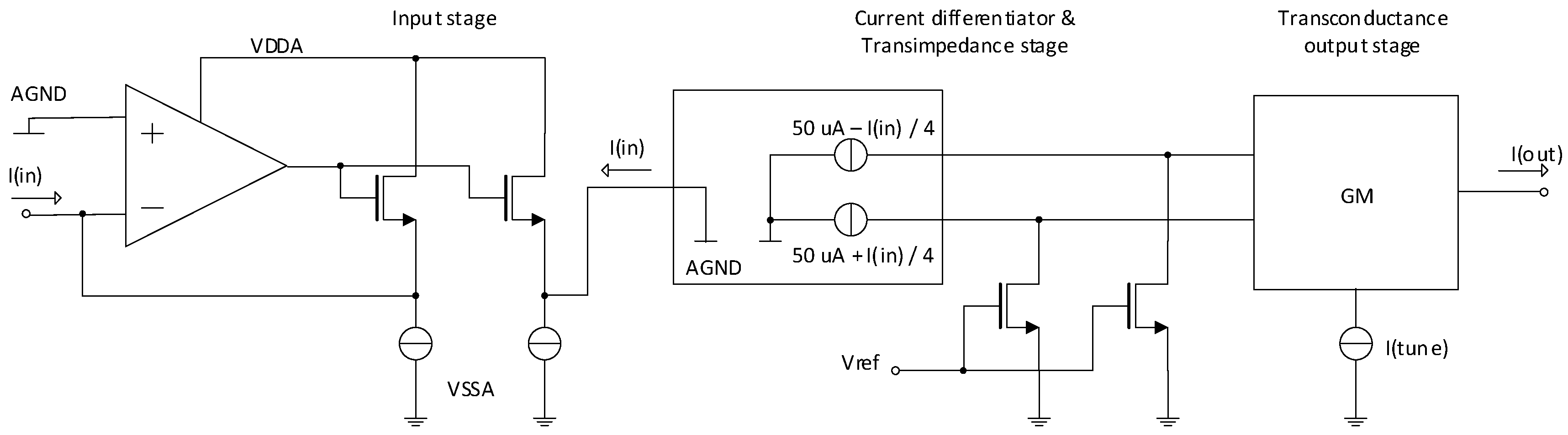

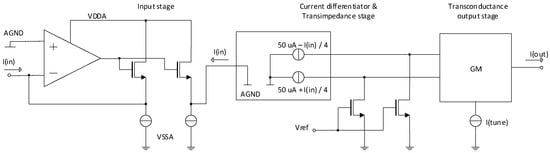

Considering all requirements, the idea of the classical quadratic current multiplier topology was rejected mainly because of the high linearity (low THD) demand, simultaneously with wide input range and lower current consumption. With an experience with design of linear or trans-linear circuits using modular approach for compiling the convenient blocks we decided to build-up the current amplifier from a highly linear transimpedance stage, followed by the tunable transconductance stage, both exploiting MOS transistors in their linear region. To meet the requirement of low input impedance a feedback topology based on the differential Miller-OTA amplifier was used. Unfortunately, this solution reduces the frequency bandwidth of the final circuit, but sufficient for many sensor measurement applications. A principal topology of the presented circuit is shown in Figure 1.

Figure 1.

A principal topology of the current amplifier with tunable gain.

The operational amplifier structure at the input provides low impedance for input current I(in). The input current is then copied to the output of the block. In fact, this input block works as a current conveyor CCII. The conveyed input current is converted to two differential currents in differentiator and lowered by factor 4 because of lowering current consumption and transistor area. All the procedure is made by the high accuracy and high output impedance cascoded current mirrors. Differential currents flow to the fixed impedances created by NMOS transistors. As obvious, playing with Vref brings the other degree of freedom to set gain. As it can come with degradation of linearity for unadvised large changes and is not necessary, it stays fixed in the presented design. Voltage signals at the outputs of the transimpedance stage are then processed by the adjustable gm stage. All parts have been designed with maximum respect to linearity and accuracy. Although, the transconductance output stage gives its best THD parameter in the differential connection, therefore the differentiator and differential transimpedance stage was used.

2.1. Input Stage and Transimpedance Stage in Detail

The target of this block is to provide low impedance current input and then transfer the input current to defined impedance where it is converted to the voltage driving the following transconductance stage.

The main requirement for the transimpedance stage is to make this conversion as much linear as possible but conveniently also dual to the transconductance stage in the sense of the total amplifier gain stabilization with respect to manufacture and temperature corners. Considering utilization of the NMOS transistor as the active component in the transconductance stage, it has been used also here. As long as the main components of both stages have the same technology parameters (mainly ) and temperature characteristics, the effect of corners is minimized.

The full principle turns around the generally known equation for MOS transistor working in the linear region, mentioned in (1),

from which, by solving the quadratic equation, we obtain,

Derivation according to ID gives the RDS value of the MOS serving as the resistor,

From Equation (3) there it is obvious that the RDS is dependent on the ID. For good linearity it is necessary to keep much smaller than . Satisfying that condition requires high VGS and low ID and brings linear MOS transistor resistance of the “ideal” value:

Unfortunately, when reasonably high current is processed by this way then it is very difficult to keep linearity under 10%. On the other hand, if the differential topology is used at the cell output, the differential output voltage VPN = VZP − VZN corresponds to the sum of both linear MOS resistances. However, when ID current increases through one of them, as a result of the input current change, the second one decreases simultaneously. It suppresses the parasitic non-linear phenomenon significantly. With respect to the developed presented topology the ID current in (3), flowing through the linear transistors, is represented by some part of input current added to and/or subtracted from a pre-biasing current respectively in the individual branches. Considering that the input current IIN is reduced 4 times (lower consumption as well as the non-linearity effect) the differential transimpedance exhibits value,

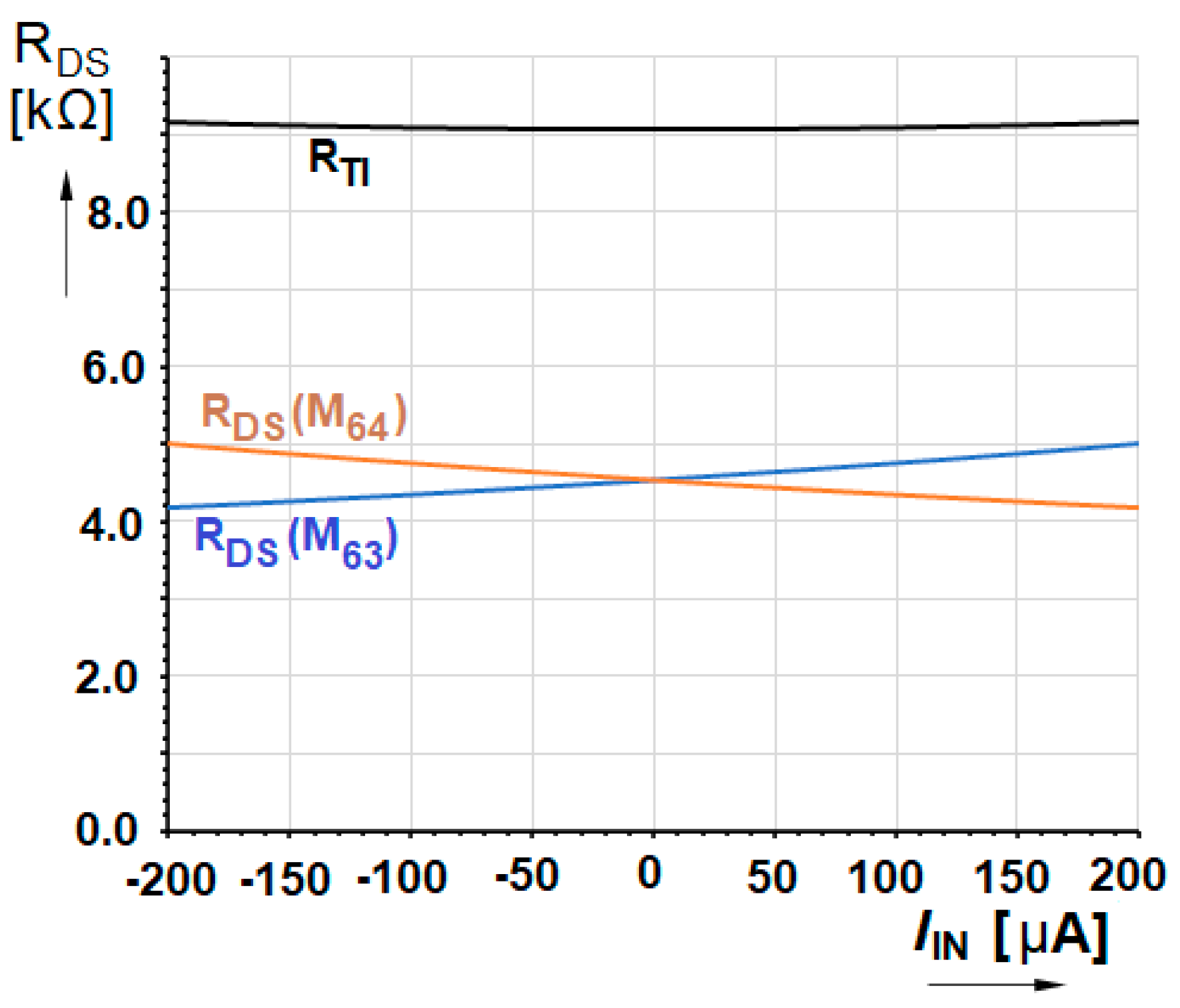

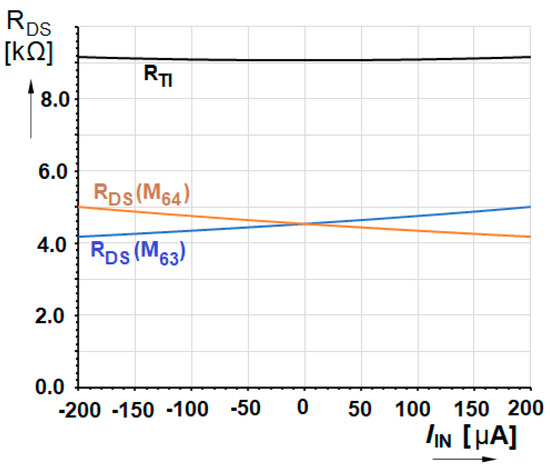

with opposite effect of the parasitic part for each linear MOS resistance. The graphic solution of this effect is presented in Figure 2.

Figure 2.

Differential transimpedance as the sum of the linear transistors RDS with their dependences on IIN calculated by Equation (5).

Now there is seen that the non-linearity reduction depends on the ratio of the fixed part of the equation and the input current dependent part . The IBIAS current should be designed as small as possible to maximize the fixed part of the transimpedance. In the presented circuit the IBIAS = 50 µA and then the appropriate currents through each transistor vary in range (0 ÷ 100) µA.

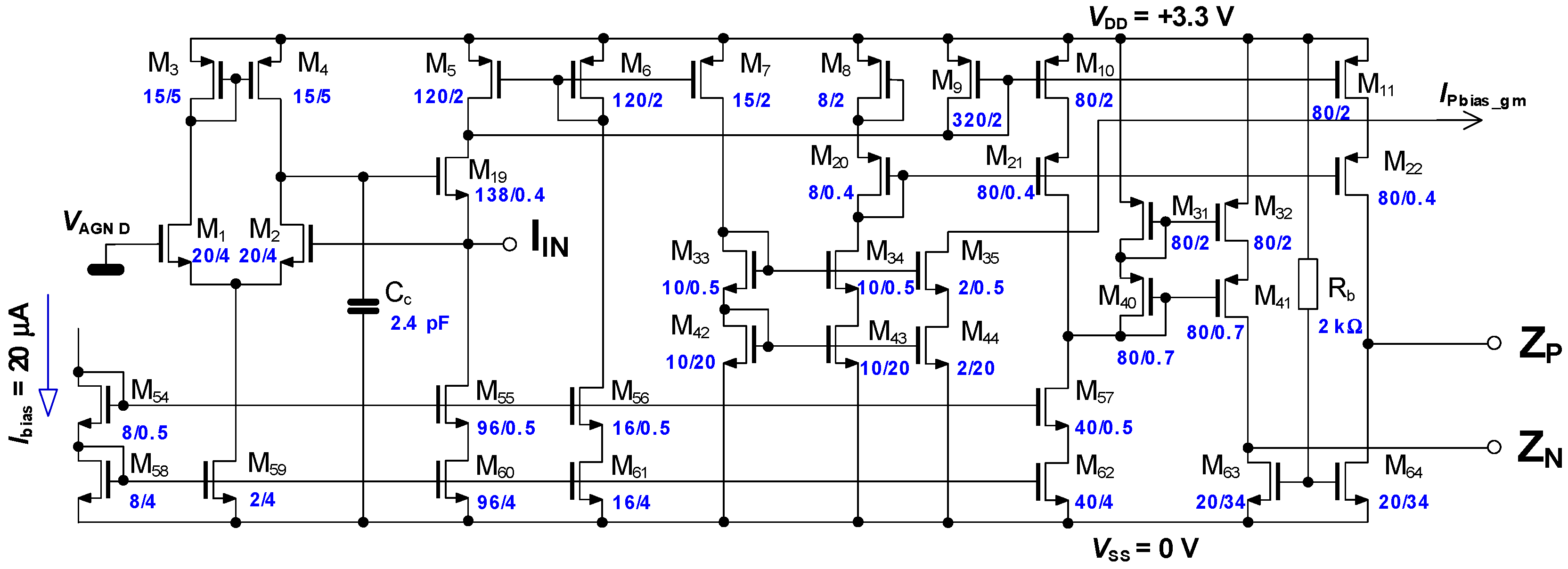

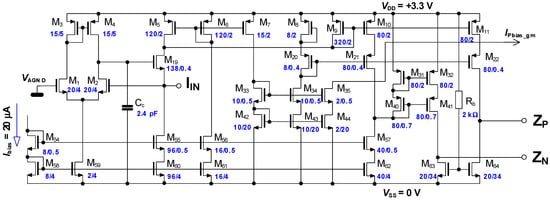

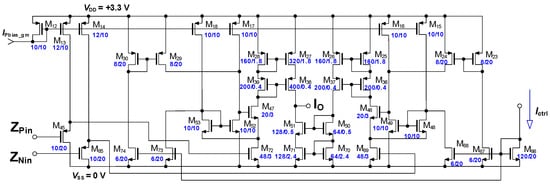

The final schematic of the presented input transimpedance stage is shown in Figure 3. The low input IIN impedance is satisfied by operational amplifier consisting of M1–M4, M59 with follower M19, working in the unity feedback. M9 senses the input current change (as the difference of fixed current of bias source M60, while M5 makes some small pre-bias due to linearity) and mirrors it by factor 1/4 to current sources M10, M11. While M11 sources the current directly to transimpedance transistor M64, the second transimpedance transistor M63 is sourced by the complementary current. The output differential voltage VPN is taken between the terminals ZP and ZN. The realized circuit differs only in matters of ESD protection.

Figure 3.

Slightly simplified schematic of the input and transimpedance stage.

As the sensed input current has been decreased by factor 4 before it is applied to the transimpedance transistors M63, M64, because of the linearity demand discussed above, then the same factor must be included in the full circuit transimpedance gain equation. The differential output voltage of the whole input transimpedance block is then ideally:

The differential transimpedance gain of the realized circuit is calculated as RTIG = 2400 Ω.

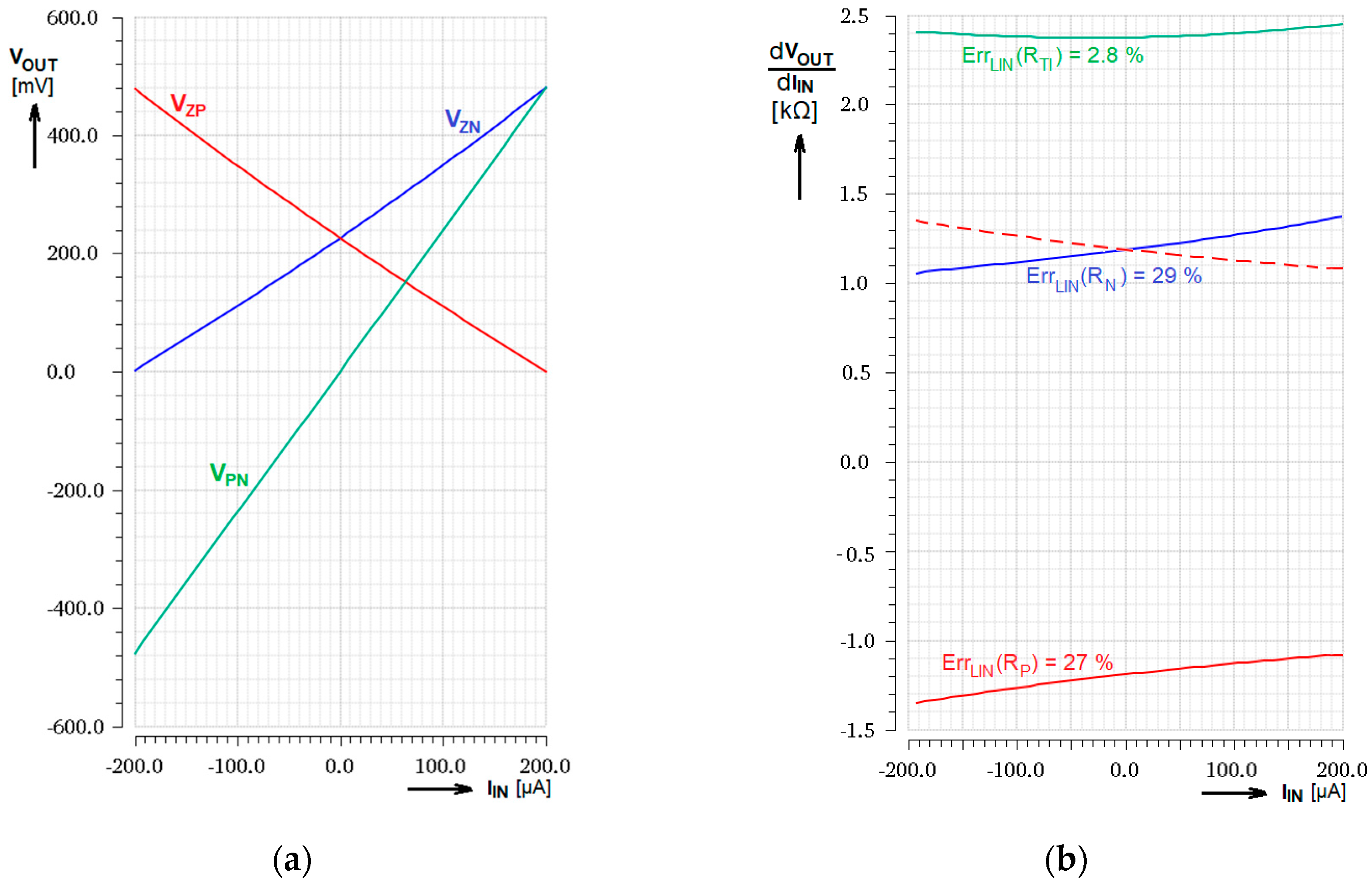

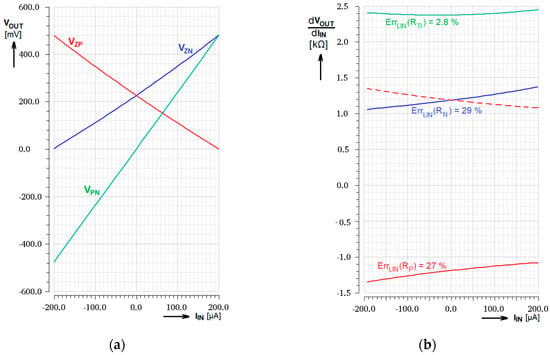

Figure 4a presents the simulated output voltages VZP and VZN together with differential output voltage VPN as the functions of the input current IIN. Derivations of these voltages according to input current, representing the transconductance gain of the whole block, are presented in Figure 4b. The red dashed line represents the transconductance gain of the ZP output branch re-calculated to the differential transconductance gain. Then, it corresponds to Figure 2, considering the factor 4. Due to the differential topology the linearity error is decreased from approx. 28% at one transistor to 2.8% in differential signal.

Figure 4.

Simulated transimpedance response of the input stage (a) Output voltages as the function of IIN; (b) Transimpedance gain as the derivation of the transimpedance transfer functions.

2.2. Tunable Transconductance Stage

As the base topology for the transconductance stage the circuit presented and thoroughly discussed in [71] has been used in its differential connection. This introduced topology was improved, compared to the original version, in tunability, current output impedance and in linearity of the regulation as well. All these improvements have led to the circuit introduced in Figure 5.

Figure 5.

Slightly simplified schematic of the tunable transconductance stage.

The circuit operation consists of a differential connection of two transconducting transistors M72, M69 working in their linear region. It means, they both work according to the Equation (1) as well. From that equation can be seen that if VDS is kept constant then the drain current ID is controlled just by VGS of the transistor with strongly linear dependence, called transconductance gm. The transconductance is then adjusted by VDS as a parameter.

Drain to source voltage VDS across these transistors must be kept low to stay in triode operation and is equal to the difference between the overdrive voltages of transistors M53, M52 (and M49, M48 respectively), which both work in their saturation region and draw a constant current. The feedback loop consisting of transistors M53, M52 and M47 (and M49, M48 and M46) keeps the voltage VDS of the main M72, M69 transistors constant when an input signal is applied [71]. Despite this topology there stays a parasitic effect of the small VDS variation (contemplating the branch of M72 for instance) caused by VGS shift of M47 due to the ID modulation. It corresponds to the M47 transconductance and is compensated by the feedback loop gain. In case of infinity feedback gain the error is zero. Inspecting the real ∆VDS of M72, we get,

where rd is a dynamic impedance of the net of M52 drain and together with transconductance of that transistor they define the feedback gain. As it should be kept high the lower currents and long channels of the connected transistors are recommended.

In the presented case of the differential topology usage the equation for transconductance stage output current is then as follows, assuming VINdiff is the differential input voltage of the stage,

with (and complementary about M49 in the opposite branch too) as the gain of the closed feedback loop that regulates voltage across the main linear transistors as it is set by difference of the M53 and M52 drain-to-source voltages. The respective rd is dynamic impedance of the nets where drains of M52 (M49) are connected to and can be calculated as the parallel connection of all impedances connected to that net. For the discussed case it can be expressed as the appropriate MOS transistors output impedance combination like .

| ||

| Linearity error |

The deliberation of the Equation (8) gives us the recommendations for design to minimize the linearity error. For the best linearity result we need to keep VGS of the M72, M69 high and their VDS sufficiently low to keep these transistors in true linear region. Simultaneously the high gm of M47, M46 is convenient as well as the feedback gain AFBloop.

In [71], just modifying the current through M52 (M49) causes the VDS of M72, (M69) change and in this manner it allows to tune transconductance parameter gm of the circuit. Unfortunately, the higher tunability needs a high range of the control current within which tuning nonlinearity comes. The presented improved transconductance circuit changes both appropriate currents differentially, through current sources consisting of M73, M74, M30, M29 (and M67, M68, M23, M24 in the opposite branch) which increase/decrease the current in both transistors, setting the ∆VDS across the main linear MOS. It brings high gm tuning range as well as linearity of the control with lower control current ICTRL amplitude. Another improvement was done in the output stage to increase current output impedance by cascoded mirror as well as input level-shifter adapting circuit to the more convenient input range and setting the higher quiescent VGS of the M72, M69 to ensure the linear region.

3. Results

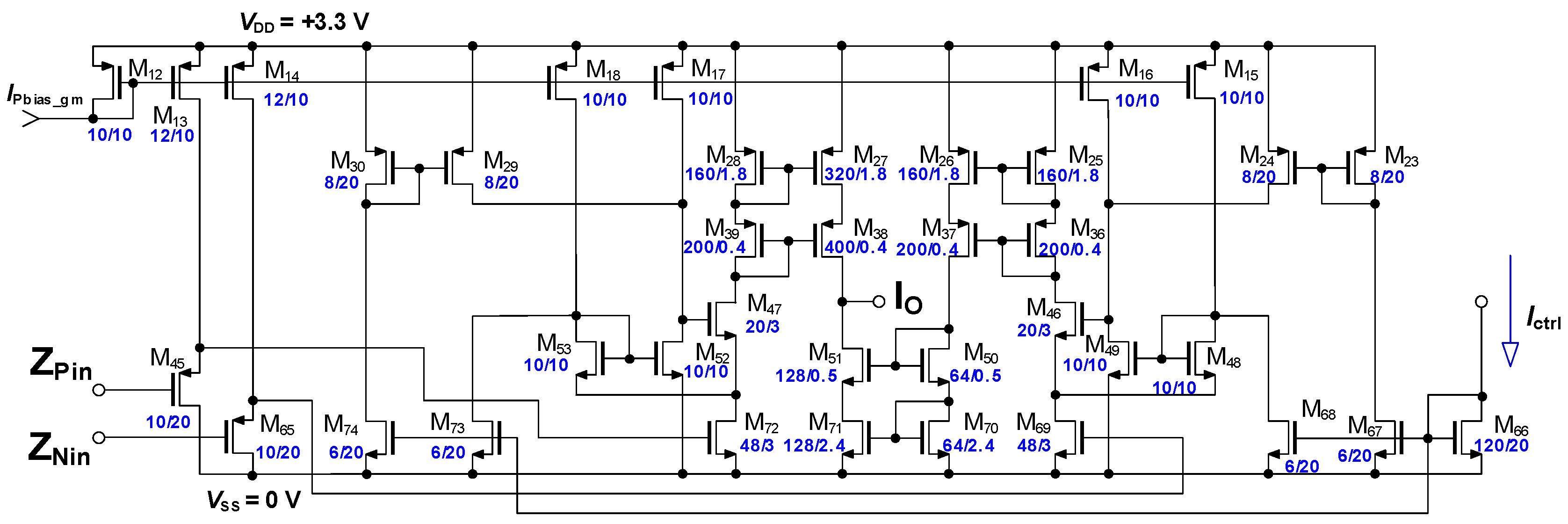

The introduced amplifier has been designed and thereafter fabricated by the Europractice project in ON Semiconductor I3T25 process suitable for the intended application. Features of this circuit were verified by experimental measurements and compared with the design simulations. The obtained parameters, and simulation to measurement comparison, are given in this chapter.

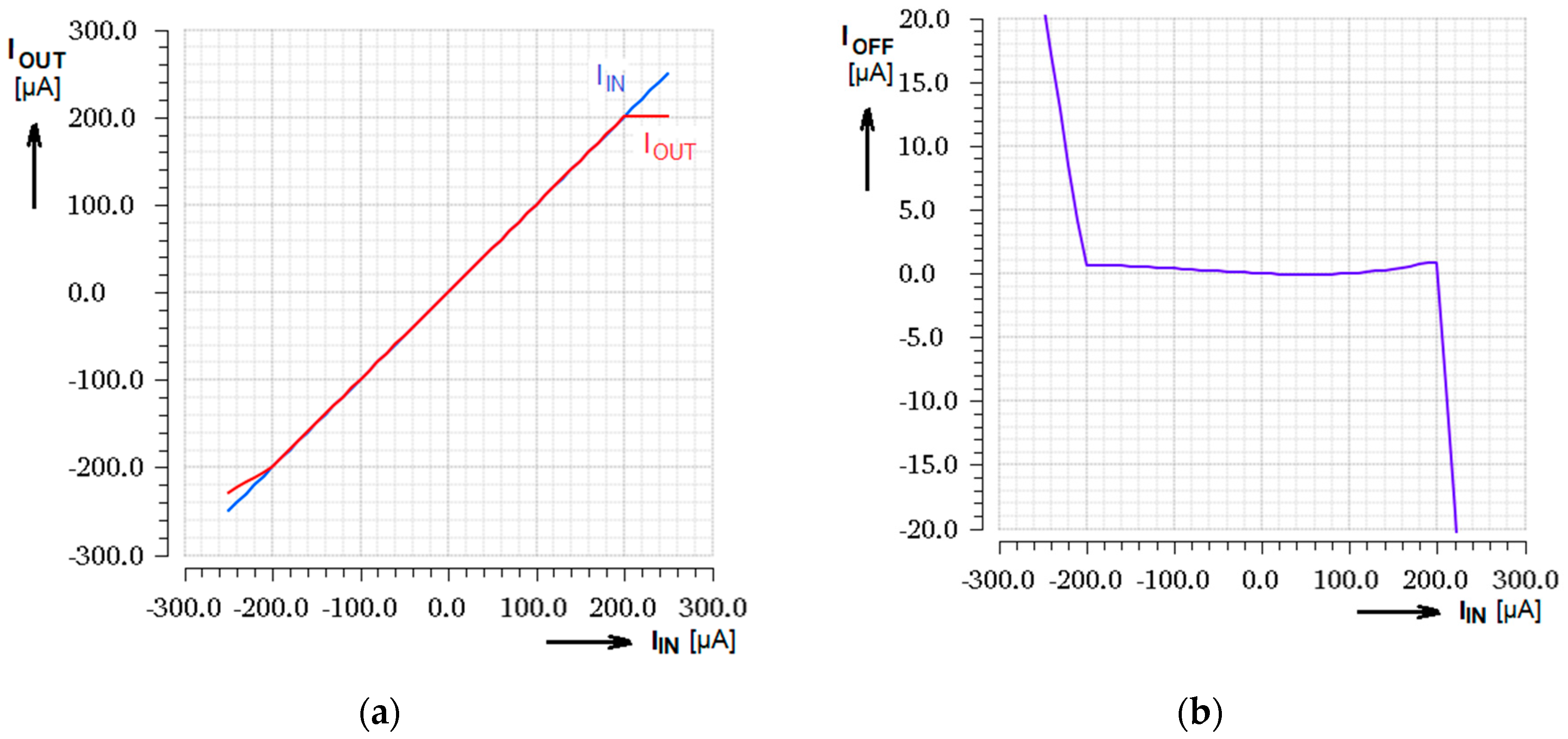

3.1. DC Transfer Characteristics

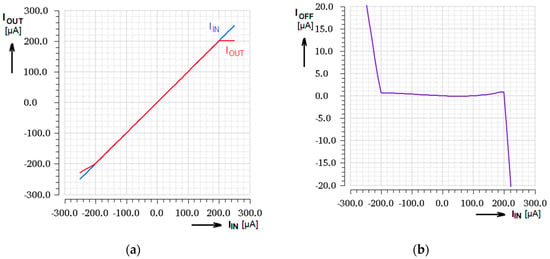

As the basic test of functionality, input range and systematic input offset, the input to output transfer function characteristic together with the input current asymmetry graph can be used conveniently. Figure 6 shows the input and output currents simulated together in one graph for amplifier gain set to 1 and systematic input offset for typical process. There is the limitation of the input current at ±200 µA, due to the differentiator topology, clearly seen. For another process corner the value can be slightly different. The systematic current input asymmetry, when IIN = 0, is typically 5.4 nA.

Figure 6.

Simulated DC transfer response; (a) Input and output currents for amplifier gain B = 1; (b) Current input offset on input current dependence.

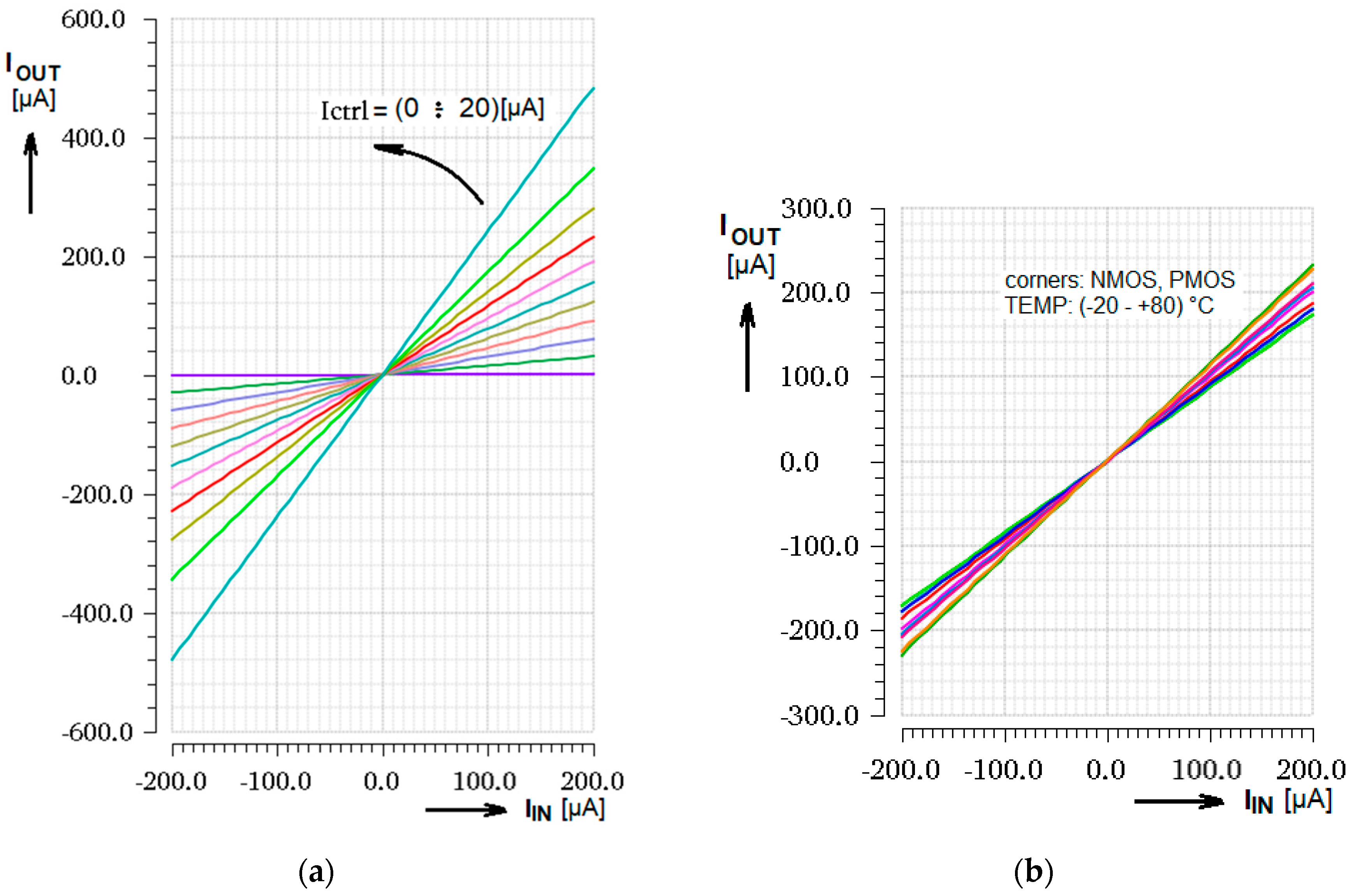

The same response simulated while the gain control current ICTRL is stepped from 0 to 20 µA with step 2 µA, presented in Figure 7a, gives a hint by curves slope that the control of the gain is highly linear up to ICTRL = 12 µA which represents a gain close to 1. Corner analysis across the process and temperature range of (−20 ÷ +80)°C, when current gain is typically set to B = 1, is shown in Figure 7b. The tolerable gain dispersion in range ± 15% is achieved by using the same device type (NMOS) for transimpedance and conductance operation simultaneously.

Figure 7.

DC transfer response; (a) Parametrical simulation for input current range ±200 µA and stepped gain setting current ICTRL from 0 to 20 µA; (b) Corner analysis for typ. current gain B = 1 (ICTRL = 12.5 µA).

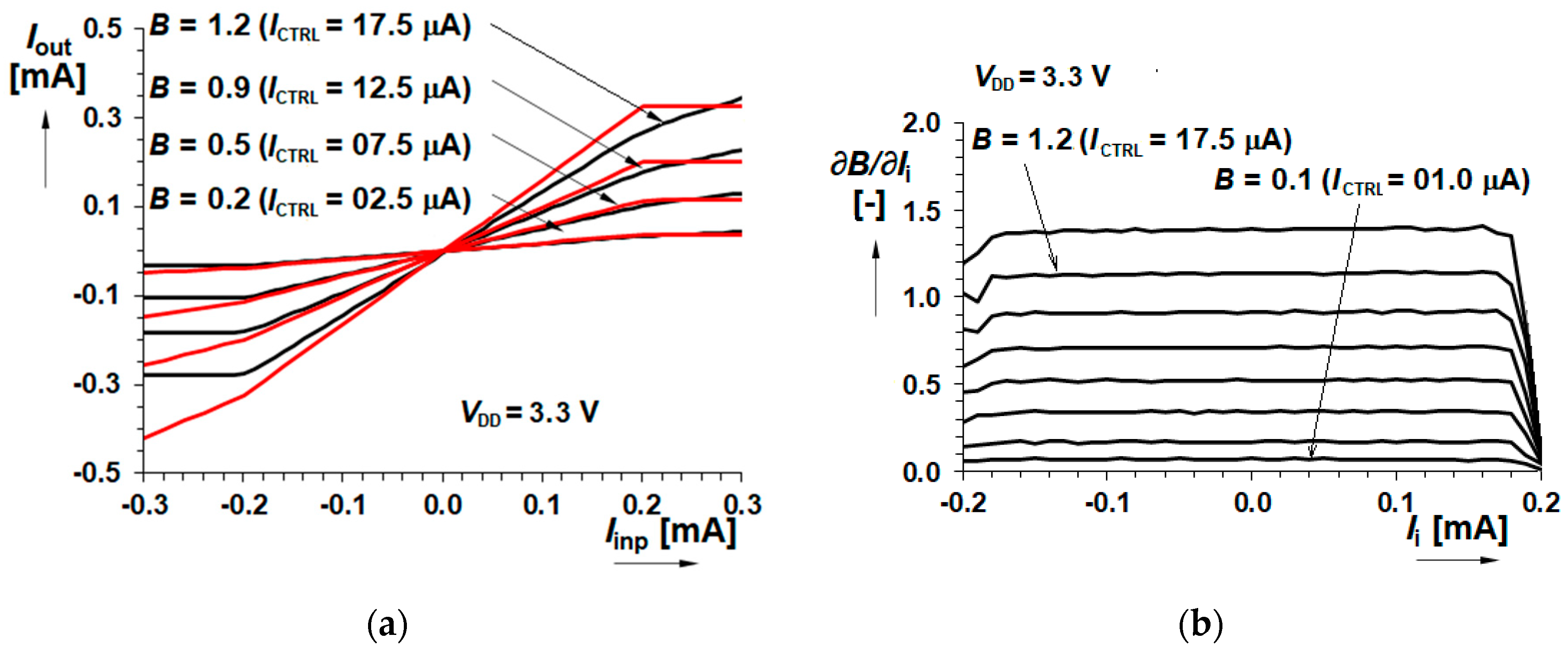

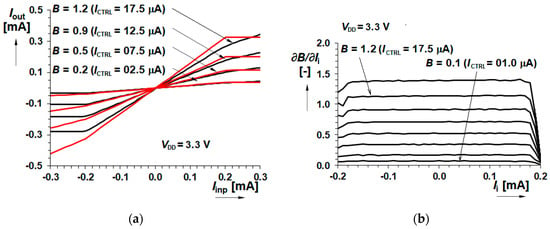

The comparison of the simulated and measured results offers Figure 8. The graph on the left compares DC transfer results of the real tested device with the theoretical characteristics. The right-side graph introduces the gain value at different input currents. This provides information with respect to the input signal linearity if the gain is constant across the input current range and defines the linear input range. From the comparison there is seen that the investigated real device has a slightly smaller gain and input current range against the simulation, but both parameters are in the scope of corners and presumably correspond to the smaller internal bias current.

Figure 8.

Measured DC transfer response (a) Comparison of the simulated (red) and measured (black) curves; (b) Measured gain across the input current range.

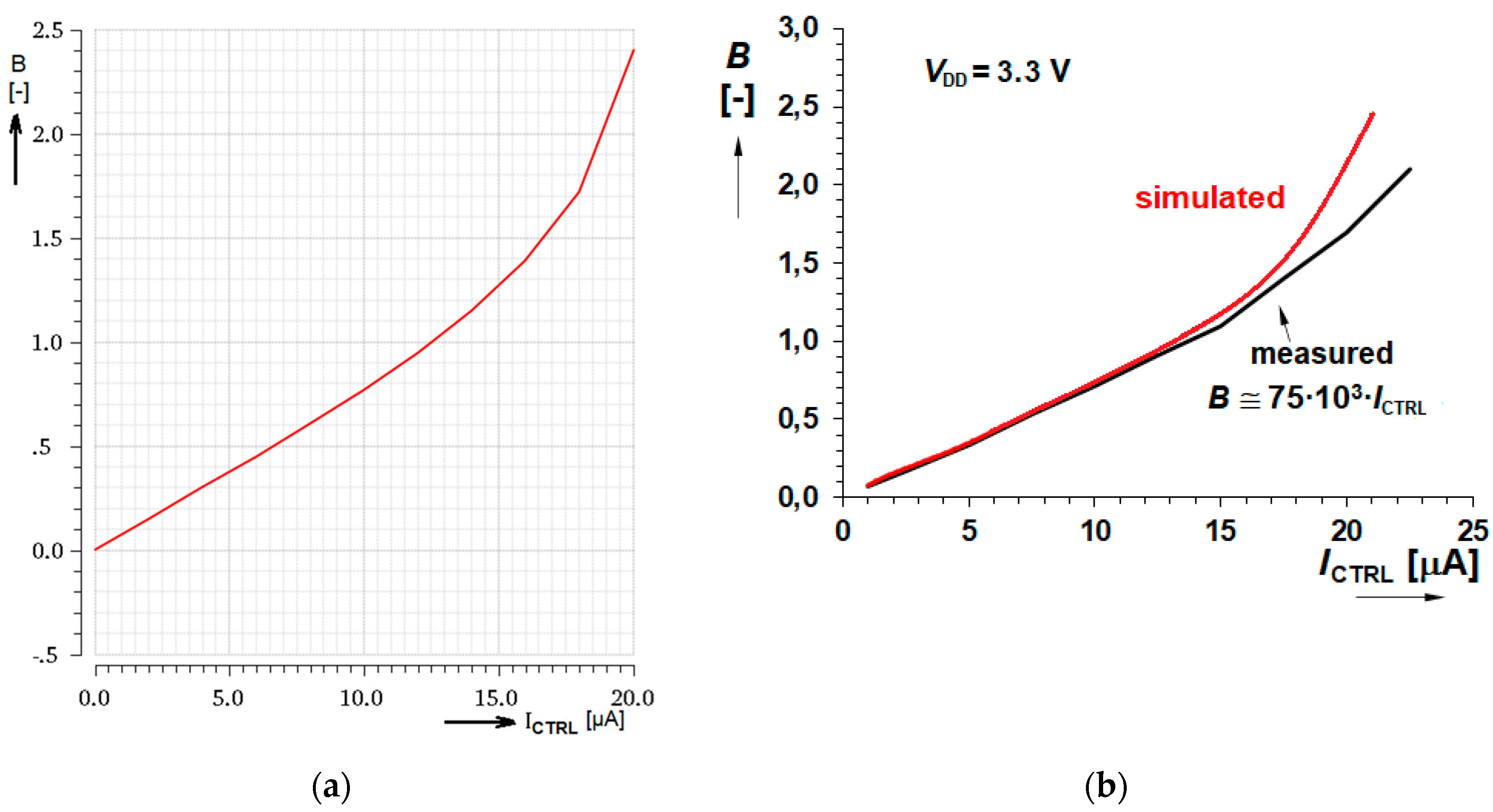

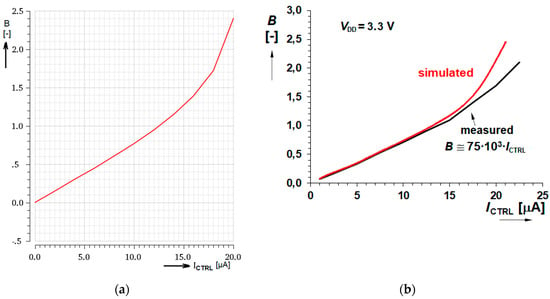

The graph of the gain control by ICTRL is displayed in Figure 9 where both simulated as well as measured curves are given. Let us notice the excellent linearity up to ICTRL = 10 µA and good linearity to ICTRL = 12.5 µA.

Figure 9.

Gain control characteristics (a) Typical Cadence simulation of the gain controlled by current ICTRL; (b) Simulation and measurement comparison.

3.2. Input Signal Linearity and THD

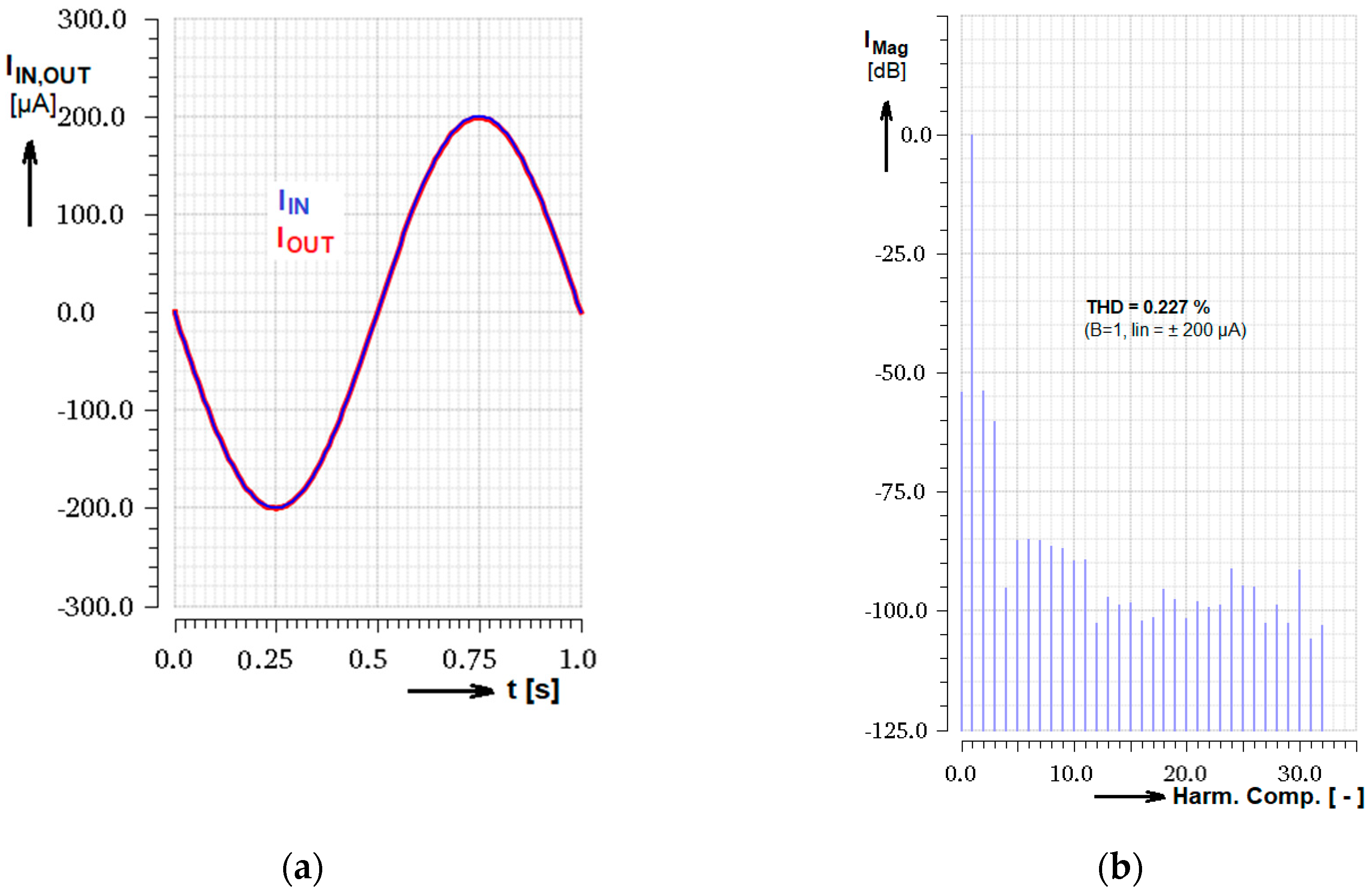

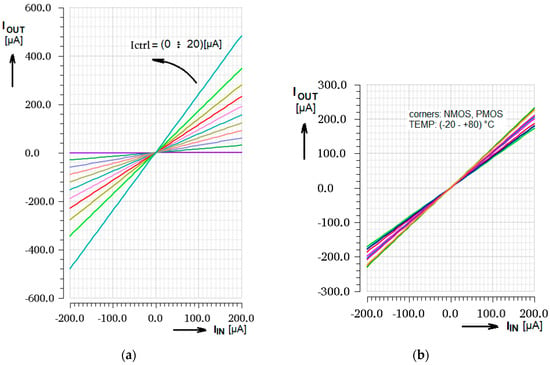

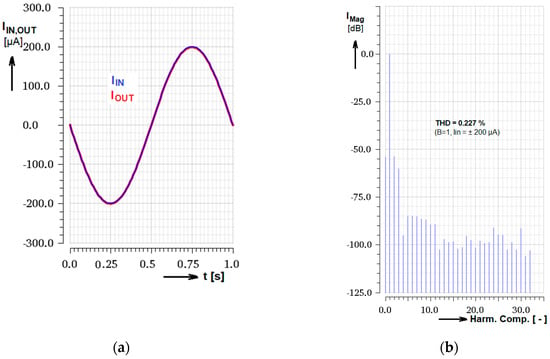

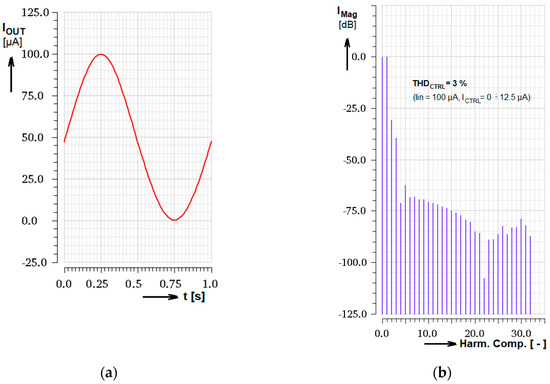

Linearity of the current transfer was the most important parameter considered during design of the amplifier and many other properties, namely frequency bandwidth, were sacrificed to that. The simulated input and output current sinus signal transient as well as the DFT analysis can be seen in Figure 10 for the case of input signal amplitude IIN = ± 200 µA and current gain B = 1. As the result the total harmonic distortion THD = 0.227% was calculated by this simulation. Linearity of the signal transfer taken from the simulated DC transfer characteristics for IIN = ± 200 µA (corresponding to Figure 6) and ICTRL from 10 µA to 20 µA was evaluated in the range of (1.17 ÷ 1.8)%. (As an informative result it can be mentioned that the Cadence simulation values of the transconductor stage itself, as the main tunable part, show the THDgm = approx. 16 m% for the small input signal [mV] and THDgm = approx. 0.25% for large input signals).

Figure 10.

DFT analysis of the output harmonic current; (a) Input and output signal transient simulation for the gain set to B = 1; (b) DFT analysis expressed in dB related to the first harmonic component and appropriate THD result.

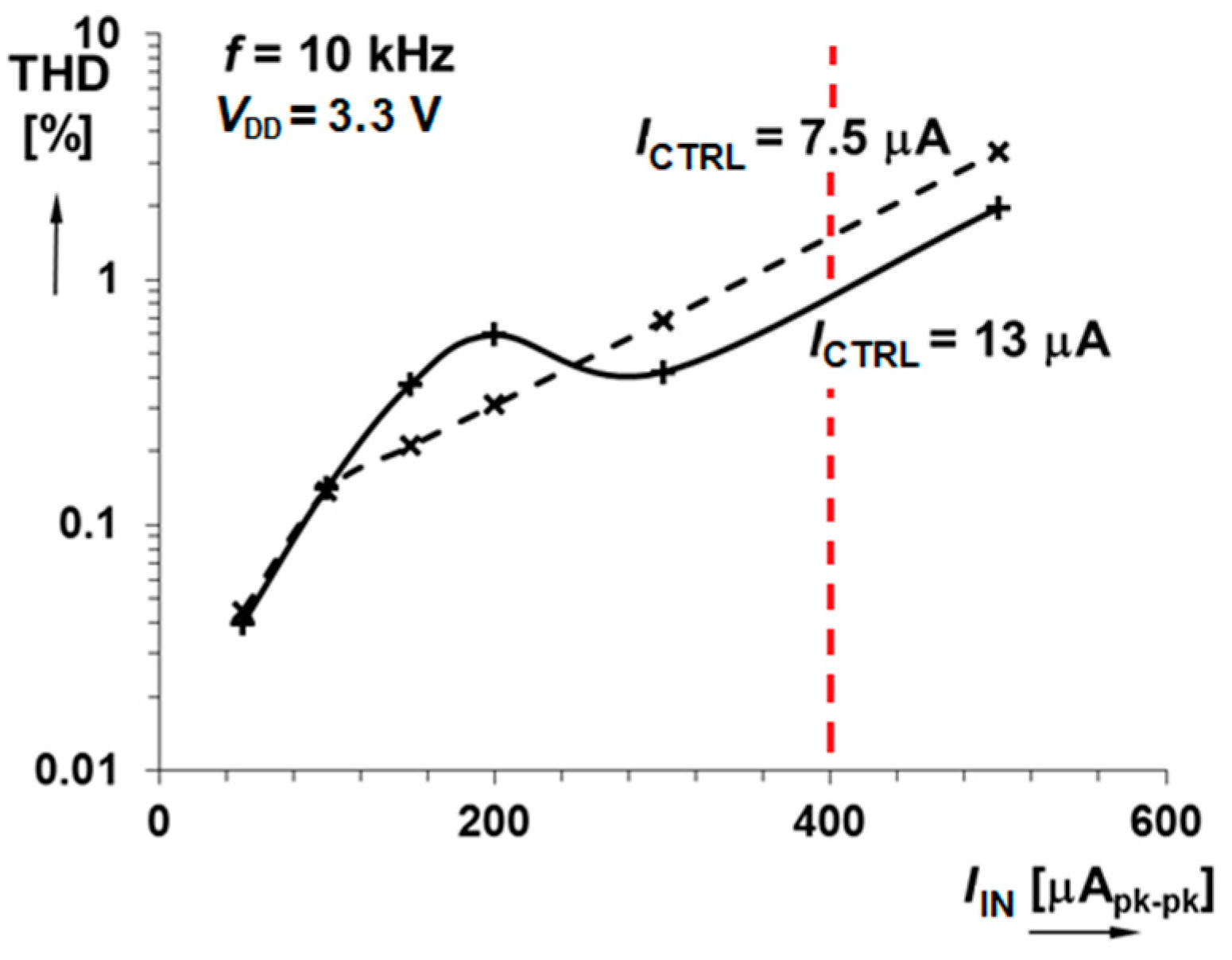

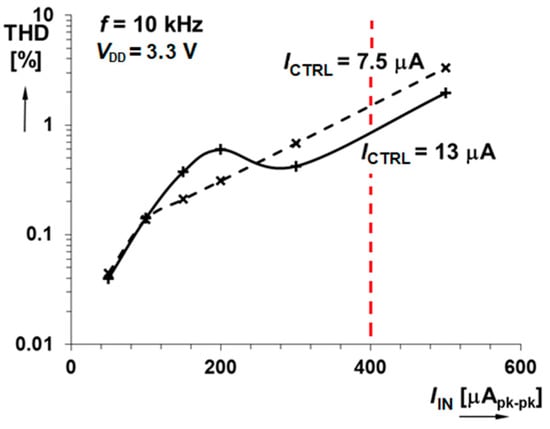

In addition to the simulation, DFT measurement was made to express the parameter in relation to the input signal amplitude for two ICTRL currents (see Figure 11). Let us note that the maximum designed and relevant peak-to-peak input range is IINmax[PK-PK] = 400 µA.

Figure 11.

Measurement of output signal THD dependence on the input signal amplitude for two gain control currents ICTRL. Let us note that the maximum designed input peak-to-peak range is IINmax[PK-PK] = 400 µA.

3.3. Linearity of the Control and Control Input THD

Although, strict linearity is often not necessary for the controlled amplifiers, especially in the case of automatic feedback regulation, in some sensor applications it can be beneficial, for example in amplitude modulation processing or the current multipliers. Exploiting the results from Figure 9 we could define the gain control linearity up to 10% for ICTRLmax = 12.5 µA (B = 1), as the maximum ICTRL value considered during design.

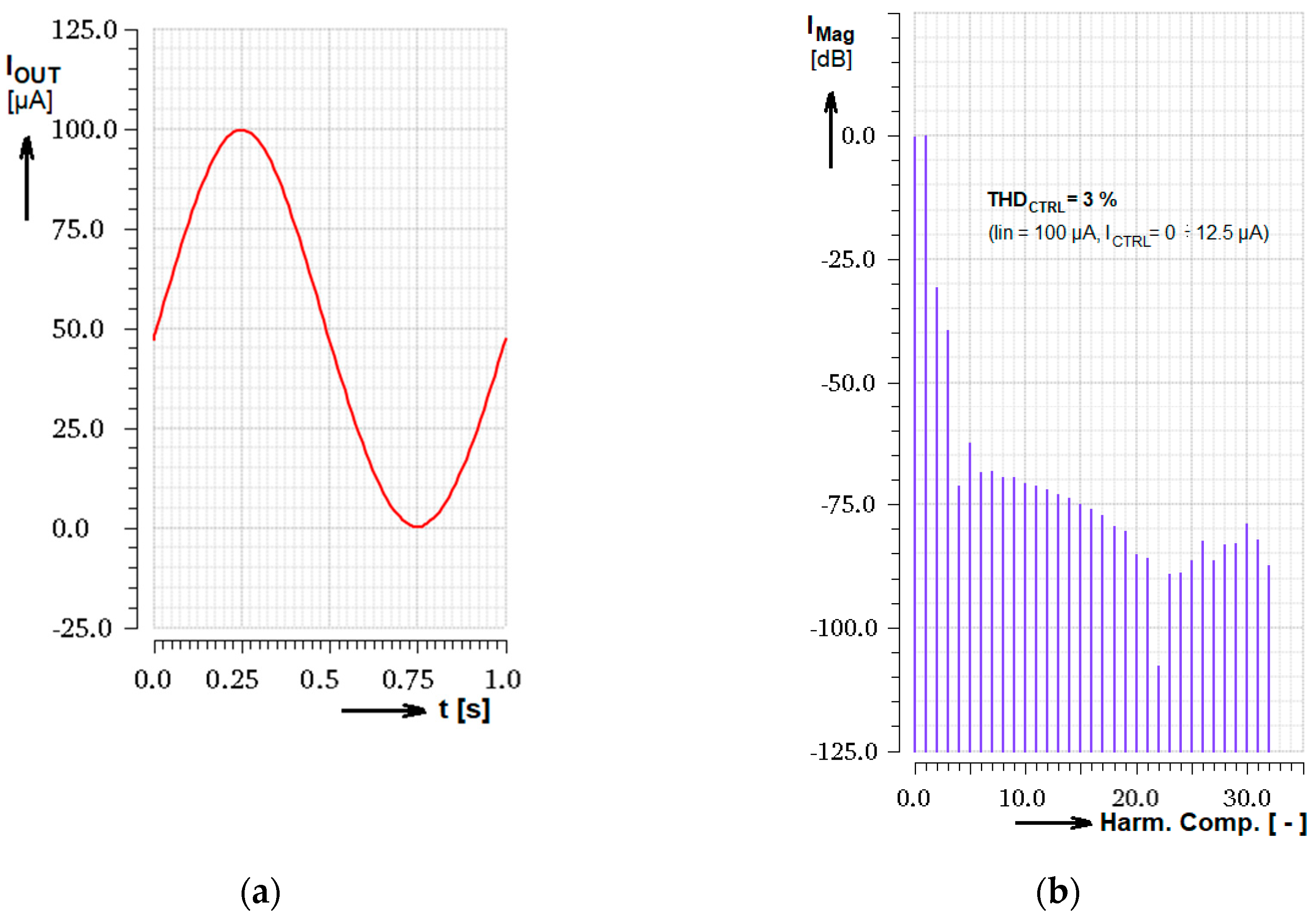

The experimental use of the control current input as the signal input was simulated and obtained results are presented in Figure 12. In this test the main input current was set to constant IIN = 100 µA and control current ICTRL was driven by the harmonic signal from 0 to 12.5 µA (with the DC pre-bias of 6.25 µA). From the transient output response, the DC shift of the output signal can be seen, as well as from the DFT results. Cadence evaluated value of THD = 3%.

Figure 12.

Simulated DFT analysis of the signal transferred from the gain control input; (a) Output current transient for IIN = 100 µA and the gain harmonically modified from 0 to 1; (b) DFT analysis expressed in dB related to the first harmonic component.

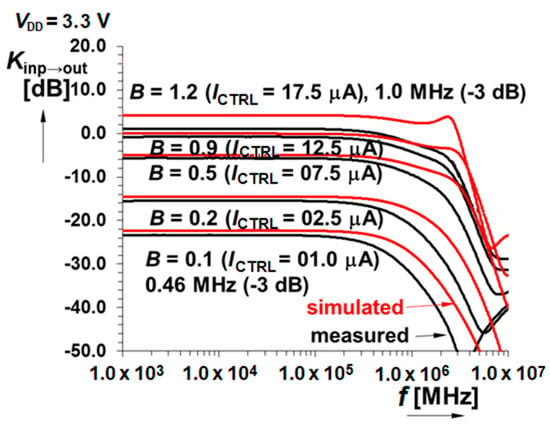

3.4. Frequency Response and Bandwidth

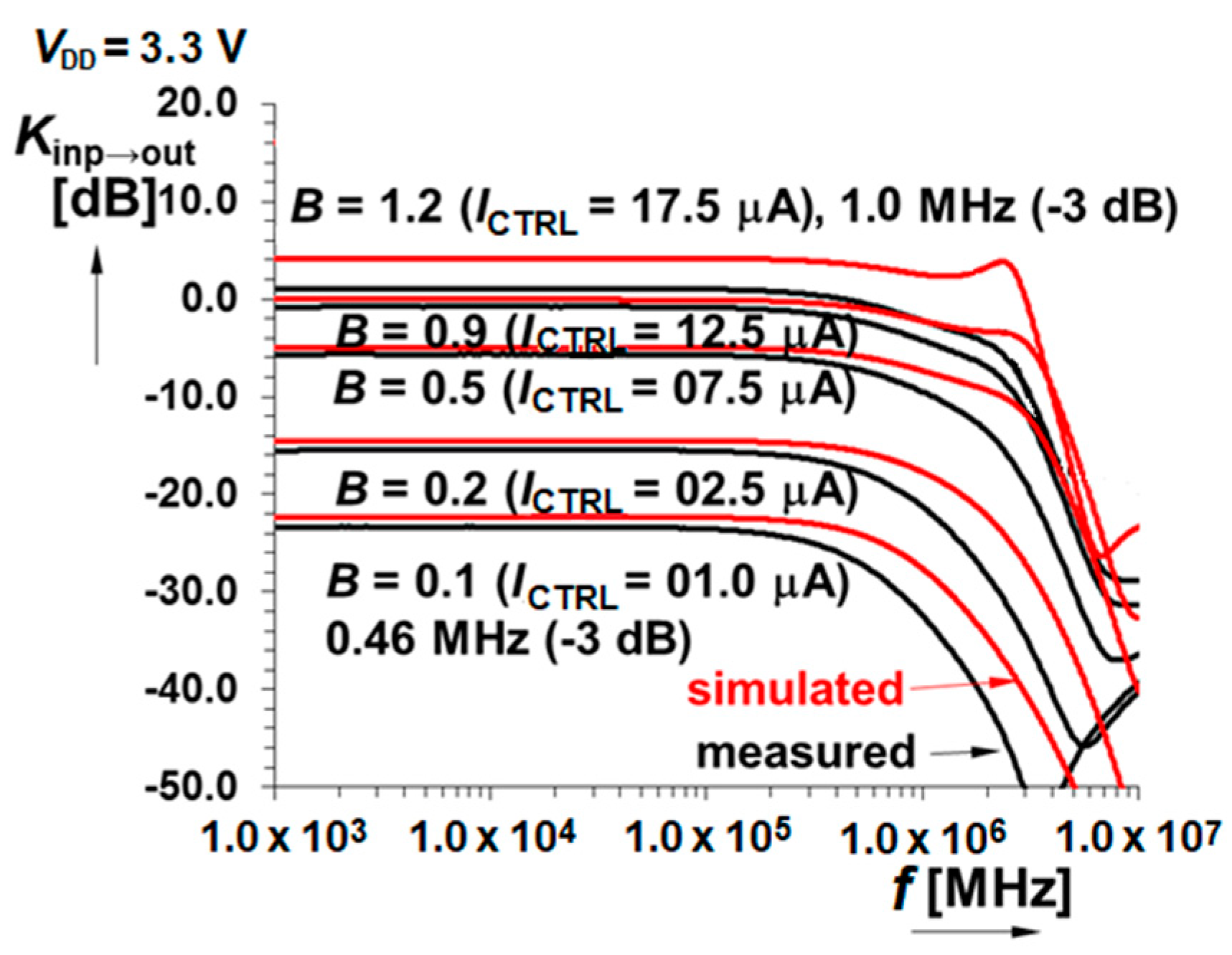

As was already mentioned earlier, the frequency bandwidth was sacrificed to other parameters of the amplifier and the high bandwidth is often not the main request of sensor applications. Despite that, the frequency response of the gain is presented (see Figure 13) comparing simulated and measured results. The values of the frequency bandwidth for different gain will be given in the results overview Table 3.

Figure 13.

Frequency transfer characteristics with measured bandwidth in the scope (0.46 ÷ 1.0) MHz.

Table 3.

Amplifier properties summary.

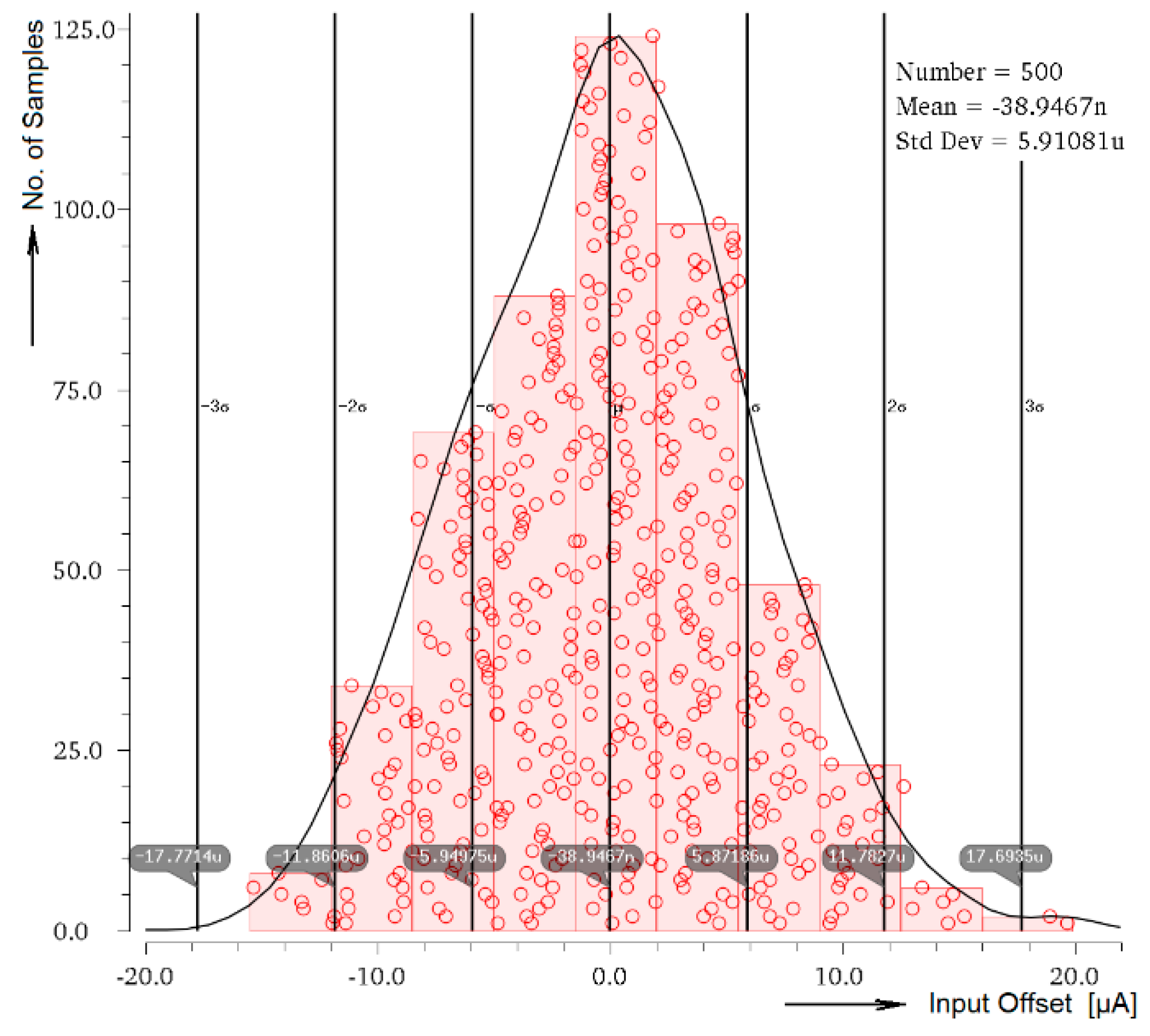

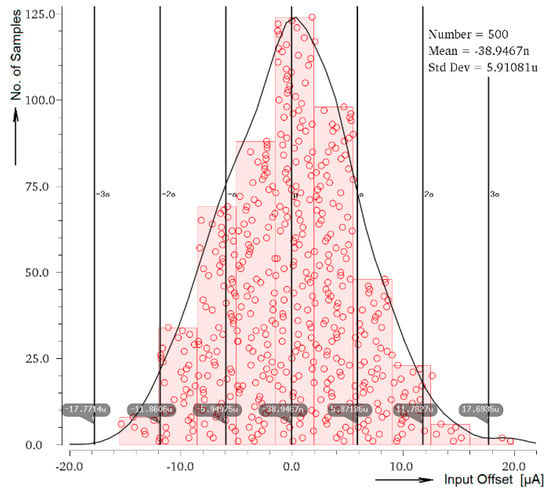

3.5. Input Current Offset

Due to the input offset is one of the important aspects for the circuits used in the measurement applications, dealing with this item must be part of the analysis.

Inspecting the results presented in Figure 6, there can be found out that systematic quiescent input offset (for IIN = 0 A and B = 1) is equal to 5.4 nA, depending on the input signal amplitude it goes typically up to +0.8 µA at the edge of the input current operating range. As usual, even more important error is caused by the random offset, represented by the Monte Carlo matching analysis shown in Figure 14. In the histogram graph there the standard deviation 1σ = 5.9 µA is seen.

Figure 14.

Monte Carlo input offset matching simulation.

Another type of the offset analysis was executed at the level of simulation and measurement too. While input current is kept IIN = 0 A, the ICTRL was stepped in range (1 ÷ 20 µA) and the input current asymmetry observed. Whereas optimistic “systematic” offset simulation gives the offset from 5.4 nA to 60 nA (matching effect should be added), the measured offset acquired by the test is in range (4 ÷ 7) µA.

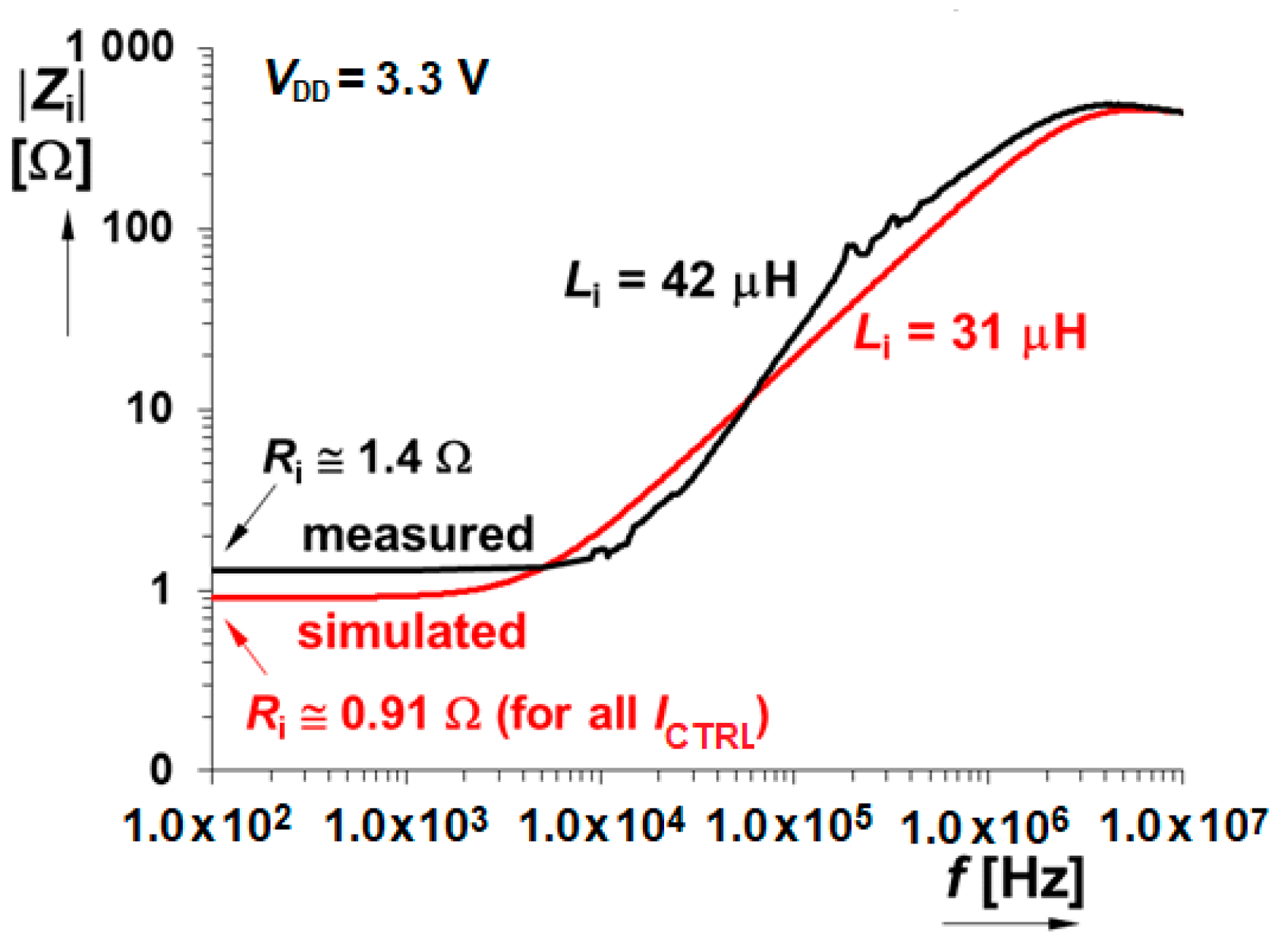

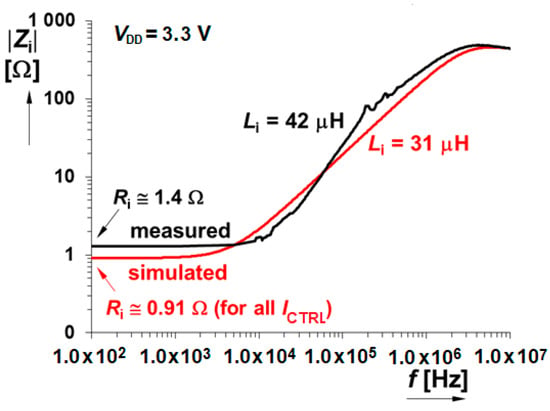

3.6. Input and Output Impedance

Thanks to the used input stage topology the low input impedance represents an important advantage of this cell. It significantly helps to build current mode application circuits without additional errors or signal distortions. The compared simulation and measurement frequency responses of the input impedance are provided in Figure 15. The input impedance is very low (~1 Ω) at low frequencies. It started to increase above 10 kHz with still nice 18 Ω at 100 kHz. The also mentioned value of the serial inductance Li (the model of the input impedance includes the resistive and inductive parts in series with parallel connection of the input capacitance) gives us the information about the complex frequency response of the input impedance. The cut-off frequency defines the frequency where the input impedance starts to increase significantly with inductive character. For the referred values of the Ri, Li it can be calculated about 5 kHz as it is proved in Figure 15. The parallel capacitance causes the input impedance decrease at high frequencies but above the bandwidth of the presented circuit.

Figure 15.

Input impedance frequency response.

Also, the output impedance was determined with acceptable simulation to measurement difference. The simulated ROUT = 8.8 MΩ for IOUT = 0 A (4 MΩ in measurement) with 3dB decline at about 5 kHz. The DC output impedance is ROUT = 7.5 MΩ when 100 µA is sourced/sinked from the output.

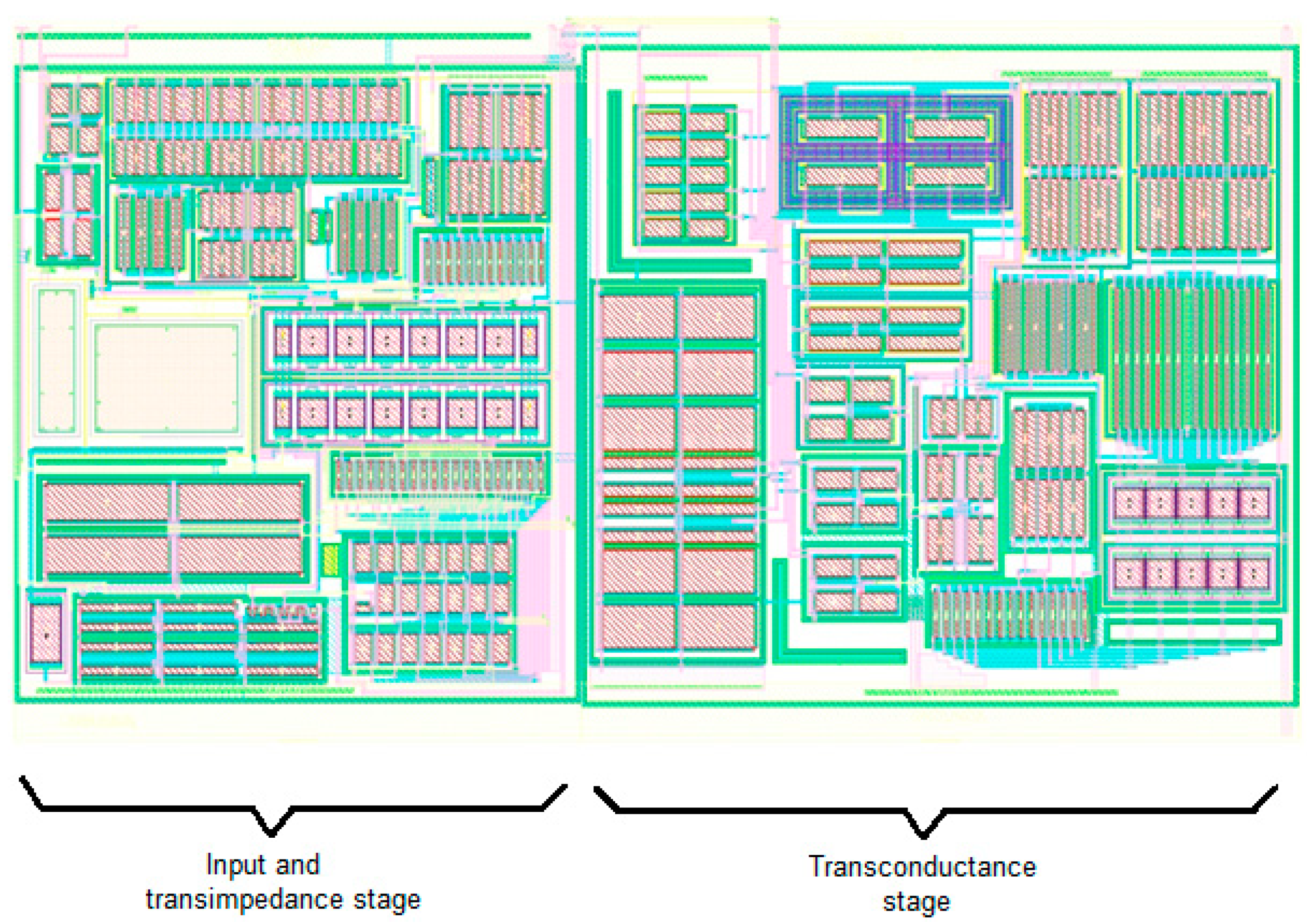

3.7. Result Overview

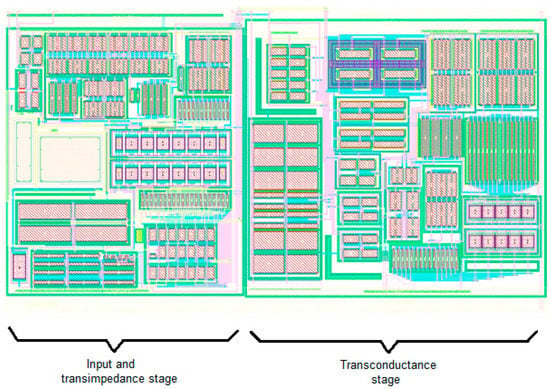

The number of simulated and measured results confirms functionality of the designed circuit with assumed parameters. The tolerable differences between simulation and measurement are in the scope of the factory corner, given possibly by the uncertainty of the MOS transistor KP transconductance parameter or, due to the nature of deviation, probably by the lower internal bias currents. Summary of the experimented circuit properties are published in Table 3. The illustrative Cadence layout is presented in Figure 16.

Figure 16.

Layout of the presented amplifier.

4. Discussion

The careful circuit analysis confirms that the newly developed modular topology of the designed tunable amplifier, working internally on the not very common fully linear principle, can be used with very interesting results. The good accordance between simulation results and measurement speaks about robustness of the introduced topology and of the whole design, as well. Acceptable deviations of measurements from simulations (decreasing gain and input range slightly but always in technology defined corners) are most likely caused by smaller internal bias against the ideal one. Moreover, the experimental measurement is influenced by increasing terminal and nodal parasitic capacities of ESD structures and PCB (approximately 10 pF), especially concerning the frequency response.

By observing the comparison Table 1, we can state that the presented circuit is almost the best one between the referred adjustable amplifiers in the maximum THD parameter. Only [14] reports lower harmonic distortion together with low power consumption, but with the digitally controlled topology, undefined input current range and even with purely theoretical results. Although the THD parameter is usually not the most important one for the amplifiers, it is reported only in limited number of publications. It can be seen that the discussed circuit is very good in the input/output impedance values and is at least well-comparable with other CMOS amplifiers regarding the input current range. In contrast, the BJT solutions are invincible in the input range and frequency bandwidth. However, their input/output impedances make them often unusable in the current mode signal processing chain for the precise measurement and their power consumption is not specified in the referred papers.

As could be expected in Table 2 comparing the current multipliers, much more references can be found stating the value of harmonic distortion. From this group only two circuits report slightly lower THD parameter than the presented one. The CMOS circuit from [65] also boasts the slightly better bandwidth and power consumption but its input current range is significantly lower. Furthermore, the terminal impedances are not reported. As the second one, the bipolar solution from [39] simultaneously shows significantly higher input range and bandwidth. This bipolar circuit was not realized and its impedances are not reported in the paper.

Even though the analyzed input offset is not really stunning, the presented circuit could be one of the better ones between current mode circuits with respect to precision. Unfortunately, there is no relevant comparison because most publications do not address this parameter. Furthermore, using an ADC in the modern sensor applications allows to easily subtract the DC offset from the signal. In that case the precise linearity is probably the most important parameter.

Despite the fact that this presented prototype was optimized especially for good linearity and accuracy properties, with the modified design it can be conveniently used in a wide range of applications from filters, precise generators to any signal processing where the signal multiplication is demanded. Specially in comparison with usual quadratic or exponential multiplier topologies it is able to report very good ratio of linear input range and power consumption.

The authors expect that the presented circuit is going to be beneficial in the field of sensor measurement and it could bring a little bit different approach to design of the precise adjustable circuits.

Author Contributions

Conceptualization and methodology, R.P.; state of the art, R.S.; circuit design and simulation R.P.; layout and GDS preparation, V.K.; prototype validation, R.S. and V.K.; writing—original draft preparation, R.P. and R.S.; writing—review and editing, R.P. and R.S.; project administration, R.S. All authors have read and agreed to the published version of the manuscript.

Funding

Research described in the paper was supported by Czech Science Foundation project under No. 19-22248S. For the research, infrastructure of the SIX Center was used.

Acknowledgments

Cadence software was used with support through the Cadence Academic Network. The prototype has been fabricated in ON I3T25 thanks to EUROPRACTICE service.

Conflicts of Interest

The authors declare no conflict of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, or in the decision to publish the results.

References

- Biolek, D.; Senani, R.; Biolkova, V.; Kolka, Z. Active elements for analog signal processing: Classification, Review, and New Proposals. Radioengineering 2008, 17, 15–32. [Google Scholar]

- Senani, R.; Bhaskar, D.R.; Singh, A.K. Current Conveyors: Variants, Applications and Hardware Implementations; Springer: Berlin, Germany, 2015. [Google Scholar]

- Surakampontorn, W.; Thitimajshima, W. Integrable electronically tunable current conveyors. IEE Proc. G 1988, 135, 71–77. [Google Scholar] [CrossRef]

- Fabre, A.; Mimeche, N. Class A/AB Second-generation Current Conveyor with Controlled Current Gain. Electron. Lett. 1994, 30, 1267–1268. [Google Scholar] [CrossRef]

- El-Adawy, A.; Soliman, A.M.; Elwan, H.O. Low Voltage Digitally Controlled CMOS Current Conveyor. AEU Int. J. Electron. Commun. 2002, 56, 137–144. [Google Scholar] [CrossRef]

- Minaei, S.; Sayin, O.K.; Kuntman, H. A new CMOS electronically tunable current conveyor and its application to current-mode filters. IEEE Trans. Circuits Syst. I 2006, 53, 1448–1457. [Google Scholar] [CrossRef]

- Tangsrirat, W. Electronically Tunable Multi-Terminal Floating Nullor and its Applications. Radioengineering 2008, 17, 3–7. [Google Scholar]

- Marcellis, A.; Ferri, G.; Guerrini, N.C.; Scotti, G.; Stornelli, V.; Trifiletti, A. The VGC-CCII: A novel building block and its application to capacitance multiplication. Analog Integr. Circuits Signal Process. 2009, 58, 55–59. [Google Scholar] [CrossRef]

- Biolek, D.; Bajer, J.; Biolkova, V.; Kolka, Z.; Kubicek, M. Z Copy-Controlled Gain-Current Differencing Buffered Amplifier and its applications. Int. J. Circuit Theory Appl. 2010, 39, 257–274. [Google Scholar] [CrossRef]

- Kumngern, M.; Chanwutium, J.; Dejhan, K. Electronically tunable multiphase sinusoidal oscillator using translinear current conveyors. Analog Integr. Circuits Signal Process. 2010, 65, 327–334. [Google Scholar] [CrossRef]

- Herencsar, N.; Lahiri, A.; Vrba, K.; Koton, J. An electronically tunable current-mode quadrature oscillator using PCAs. Int. J. Electron. 2012, 99, 609–621. [Google Scholar] [CrossRef]

- Sotner, R.; Kartci, A.; Jerabek, J.; Herencsar, N.; Dostal, T.; Vrba, K. An Additional Approach to Model Current Followers and Amplifiers with Electronically Controllable Parameters from Commercially Available ICs. Meas. Sci. Rev. 2012, 12, 255–265. [Google Scholar] [CrossRef]

- Sotner, R.; Jerabek, J.; Herencsar, N.; Dostal, T.; Vrba, K. Electronically Adjustable Modification of CFA: Double Current Controlled CFA (DCC-CFA). In Proceedings of the 35th International Conference on Telecommunications and Signal Processing (TSP), Prague, Czech Republic, 3–4 July 2012; pp. 401–405. [Google Scholar]

- Alzaher, H.; Tasadduq, N.; Al-Ees, O.; Al-Ammari, F. A complementary metal–oxide semiconductor digitally programmable current conveyor. Int. J. Circuit Theory Appl. 2013, 41, 69–81. [Google Scholar] [CrossRef]

- Jerabek, J.; Koton, J.; Sotner, R.; Vrba, K. Adjustable band-pass filter with current active elements: Two fully-differential and single-ended solutions. Analog Integr. Circuits Signal Process. 2013, 74, 129–139. [Google Scholar] [CrossRef]

- Langhammer, L.; Jeřábek, J.; Polák, J.; Pánek, D. A Single-Ended and Fully-Differential Universal Current-Mode Frequency Filter with MO-CF and DACA Elements. Adv. Electr. Comput. Eng. 2016, 16, 43–48. [Google Scholar] [CrossRef]

- Dual Wide-Bandwidth Digitally Adjustable Current Amplifier (DACA). Available online: http://www.utko.feec.vutbr.cz/~jerabekj/daca.pdf (accessed on 15 June 2020).

- Šotner, R.; Herencsár, N.; Jeřábek, J.; Koton, J.; Dostál, T.; Vrba, K. Electronically controlled oscillator with linear frequency adjusting for four-phase or differential quadrature output signal generation. Int. J. Circuit Theory Appl. 2013, 42, 1264–1289. [Google Scholar] [CrossRef]

- Sotner, R.; Herencsar, R.; Jerabek, J.; Langhammer, L.; Polak, J. On practical construction of electronically controllable compact current amplifier based on commercially available elements and its application. AEU Int. J. Electron. Commun. 2017, 81, 56–66. [Google Scholar] [CrossRef]

- Sotner, R.; Langhammer, L.; Petržela, J.; Domanský, O.; Dostál, T. Applications of Novel Behavioral Implementation of a Controllable Generalized Current Conveyor. In Proceedings of the 28th International Conference Radioelektronika 2018, Prague, Czech Republic, 19–20 April 2018. [Google Scholar]

- Esparza-Alfaro, F.; Lopez-Martin, A.J.; Palumbo, G.; Permisi, S. CMOS Class-AB Tunable Voltage-Feedback Current Operational Amplifier. In Proceedings of the 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), Marseille, France, 7–10 December 2014; pp. 140–143. [Google Scholar]

- Esparza-Alfaro, F.; Permisi, S.; Palumbo, G.; Lopez-Martin, A.J. Low-Power Class-AB CMOS Voltage Feedback Current Operational Amplifier with Tunable Gain and Bandwidth. IEEE Trans. Circuits Syst. II 2014, 61, 574–578. [Google Scholar] [CrossRef]

- Safari, L.; Minaei, S. New ECCII-Based Electronically Controllable Current-Mode Instrumentation Amplifier with High Frequency Performance. In Proceedings of the 2017 European Conference on Circuit Theory and Design (ECCTD), Catania, Italy, 4–6 September 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Agrawal, D.; Maheshwari, S. Low Voltage Current Mode Instrumentation Amplifier. In Proceedings of the 2019 International Conference on Computing, Communication, and Intelligent Systems (ICCCIS), Greater Noida, India, 19–20 February 2019; pp. 20–23. [Google Scholar] [CrossRef]

- Altuner, M.S.; Momen, H.G.; Yazgi, M.; Toker, A.; Zeki, A. A Linear-in-dB-Control Variable Gain Amplifier Using a New Approach. In Proceedings of the 2017 10th International Conference on Electrical and Electronics Engineering (ELECO), Bursa, Turkey, 30 November–2 December 2017; pp. 1207–1211. [Google Scholar]

- Di Cataldo, G.; Mita, R.; Pennisi, S. High-Speed CMOS Unity-Gain Current Amplifier. Microelectron. J. 2006, 37, 1086–1091. [Google Scholar] [CrossRef]

- Alzaher, H. Current follower based reconfigurable integrator/differentiator circuits with passive and active components׳ reuse. Microelectron. J. 2015, 46, 135–142. [Google Scholar] [CrossRef]

- Tanno, K.; Ishizuka, O.; Tang, Z. Four-quadrant CMOS current-mode multiplier independent of device parameters. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 2000, 47, 473–477. [Google Scholar] [CrossRef]

- Wasaki, H.; Horio, Y.; Nakamura, S. Current multiplier/divider circuit. Electron. Lett. 1991, 27, 504–506. [Google Scholar] [CrossRef]

- Naderi, A.; Mojarrad, H.; Ghasemzadeh, H.; Khoei, A.; Hadidi, K. Four-Quadrant CMOS Analog Multiplier Based on New Current Squarer Circuit with High-Speed. In Proceedings of the IEEE Eurocon 2009, St.-Petersburg, Russia, 21 July 2009; pp. 282–287. [Google Scholar]

- Narksarp, W.; Pawarangkoon, P.; Kiranon, W.; Wadkien, P. A Four-Quadrant Current-Mode Multiplier/Divider Building Block. In Proceedings of the 6th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology, Pattaya, Thailand, 18–21 July 2009; pp. 574–577. [Google Scholar]

- Festila, L.; Cirlugea, M.; Szolga, L.; Groza, R. Current-Mode Multiplier Models Based on FF−1 Functions. In Proceedings of the 15th International Conference on Mixed Design of Integrated Circuits and Systems, Poznan, Poland, 19–21 June 2008; pp. 401–406. [Google Scholar]

- Yuce, E. Design of a Simple Current-Mode Multiplier Topology Using a Single CCCII+. IEEE Trans. Instrum. Meas. 2008, 57, 631–637. [Google Scholar] [CrossRef]

- Jaikla, W.; Siripruchyanun, M. A Novel Current-Mode Multiplier/Divider Employing only Single Dual-Output Current Controlled CDTA. In Proceedings of the International Symposium on Communications and Information Technologies, Sydney, Australia, 17–19 October 2007; pp. 106–109. [Google Scholar]

- Prommee, P.; Somdunyakanok, M.; Kumngern, M.; Dejhan, K. Single Low-Supply Current-mode CMOS Analog Multiplier Circuit. In Proceedings of the International Symposium on Communications and Information Technologies, Bangkok, Thailand, 18 October–20 September 2006; pp. 1101–1104. [Google Scholar]

- Gravati, M.; Valle, M.; Ferri, G.; Guerrini, N.; Reyes, N. A Novel Current-Mode very Low Power Analog CMOS Four Quadrant Multiplier. In Proceedings of the 31st European Solid-State Circuits Conference, ESSCIRC 2005, Grenoble, France, 12–16 September 2005; pp. 495–498. [Google Scholar]

- Hashiesh, M.A.; Mahmoud, S.A.; Soliman, A.M. New Current-Mode and Voltage-Mode CMOS Analog Multipliers. In Proceedings of the International Conference on Electrical, Electronic and Computer Engineering, ICEEC ’04, Cairo, Egypt, 5–7 September 2004; pp. 435–438. [Google Scholar] [CrossRef]

- Vlassis, S.; Siskos, S. Design of voltage-mode and current-mode computational circuits using floating-gate MOS transistors. IEEE Trans. Circuits Syst. I 2004, 51, 329–341. [Google Scholar] [CrossRef]

- Kaewdang, K.; Fongsamut, C.; Surakampontorn, W. A Wide-Band Current-Mode OTA-Based Analog Multiplier-Divider. In Proceedings of the 2003 International Symposium on Circuits and Systems, ISCAS ’03, Bangkok, Thailand, 25–28 May 2003; pp. 349–352. [Google Scholar] [CrossRef]

- El-Atta, M.A.; El-Ela, M.A.; El Said, M.K. Four-Quadrant Current Multiplier and its Application as a Phase-Detector. In Proceedings of the Nineteenth National Radio Science Conference, Alexandria, Egypt, 19–21 March 2002; pp. 502–508. [Google Scholar] [CrossRef]

- Chang, C.-C.; Lin, M.-L.; Liu, S.-I. CMOS current-mode exponential-control variable-gain amplifier. Electron. Lett. 2001, 37, 868–869. [Google Scholar] [CrossRef]

- Ravindran, A.; Ramarao, K.; Vidal, E.; Ismail, M. Compact low voltage four quadrant CMOS current multiplier. Electron. Lett. 2001, 37, 1428–1429. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Carlosena, A. Geometric-Mean Based Current-Mode CMOS Multiplier/Divider. In Proceedings of the 1999 IEEE International Symposium on Circuits and Systems (ISCAS), Orlando, FL, USA, 30 May–2 June 1999; Volume 1, pp. 342–345. [Google Scholar] [CrossRef]

- Kongpoon, M. Ultra-Low-Power, Modular, Class-AB Current Multiplier. In Proceedings of the 5th International Conference on Engineering, Applied Sciences and Technology (ICEAST), 2019, Luang Prabang, Laos, 2–5 July 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Vlassis, S.; Souliotis, G.; Plessas, F. Ultra Low-Voltage Current Squaring and Multiplier. In Proceedings of the 8th 2019 International Conference on Modern Circuits and Systems Technologies (MOCAST), Thessaloniki, Greece, 13–15 May 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Danesh, M.; Jayaraj, A.; Chandrasekaran, S.T.; Sanyal, A. Ultra-Low Power Analog Multiplier Based on Translinear Principle. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Parveen, T. Electronically Tunable Current Mode Temperature Insensitive Active Only Analog Multiplier/Divider. In Proceedings of the 3rd International Conference and Workshops on Recent Advances and Innovations in Engineering (ICRAIE), Jaipur, India, 22–25 November 2018; pp. 1–7. [Google Scholar] [CrossRef]

- Aloui, I.; Hassen, N.; Besbes, K. ±0.75V Four Quadrant Analog Multiplier in Current Mode. In Proceedings of the 15th International Multi-Conference on Systems, Signals & Devices (SSD), Hammamet, Tunisia, 19–22 March 2018; pp. 1045–1050. [Google Scholar] [CrossRef]

- Aloui, I.; Hassen, N.; Besbes, K. Low-Voltage Low-Power Four-Quadrant Analog Multiplier in Current-Mode. In Proceedings of the 18th International Conference on Sciences and Techniques of Automatic Control and Computer Engineering (STA), Monastir, Tunisia, 21–23 December 2017; pp. 163–167. [Google Scholar] [CrossRef]

- Tijare, A.; Dakhole, P. CMOS Current Mode Analog Multiplier. In Proceedings of the International Conference on Signal and Information Processing (IConSIP), Nanded, Maharashtra, 6–8 October 2016; pp. 1–5. [Google Scholar] [CrossRef]

- Renge, A.; Tijare, A.; Dakhole, P. CMOS Current-Mode Analog Multiplier. In Proceedings of the International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, India, 6–8 April 2016; pp. 823–826. [Google Scholar] [CrossRef]

- Baharmast, A.; Azhari, S.J.; Mowlavi, S. A New Current Mode High Speed Four Quadrant CMOS Analog Multiplier. In Proceedings of the 24th Iranian Conference on Electrical Engineering (ICEE), Shiraz, Iran, 10–12 May 2016; pp. 1371–1376. [Google Scholar] [CrossRef]

- Tangjit, J.; Tangsrirat, W.; Satansup, J.; Surakampontorn, W. Simple Design Technique for Realizing Low-Voltage Low-Power CMOS Current Multiplier. In Proceedings of the 7th International Conference on Information Technology and Electrical Engineering (ICITEE), Chiang Mai, Thailand, 29–30 October 2015; pp. 110–113. [Google Scholar] [CrossRef]

- Borkar, B.D.; Tijare, A.D. VLSI Implementation of Current Mode Analog Multiplier. In Proceedings of the International Conference on Communications and Signal Processing (ICCSP), Melmaruvathur, India, 2–4 April 2015; pp. 531–534. [Google Scholar] [CrossRef]

- Saatlo, A.N.; Ozoguz, S.; Minaei, S. Applications of a CMOS Current Squaring Circuit in Analog Signal Processing. In Proceedings of the 38th International Conference on Telecommunications and Signal Processing (TSP), Prague, Czech Republic, 9–11 July 2015; pp. 339–343. [Google Scholar] [CrossRef]

- Dos Santos, R.B.; Rizol, P.M.S.R.; Mesquita, L. Design of CMOS Current-Mode Multiplier-Divider Circuit for Type-2 FLC Applications. In Proceedings of the IEEE 6th Latin American Symposium on Circuits & Systems (LASCAS), Montevideo, Uruguay, 24–27 February 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Kumngern, M.; Chanwutitum, J. 0.75-V Four-Quadrant Current Multiplier Using Floating Gate-MOS Transistors. In Proceedings of the International Electrical Engineering Congress (iEECON), Chonburi, Thailand, 19–21 March 2014; pp. 1–4. [Google Scholar] [CrossRef]

- Popa, C. Improved Accuracy Current-Mode Analog Function Synthesizer. In Proceedings of the 37th International Convention on Information and Communication Technology, Electronics and Microelectronics (MIPRO), Opatija, Croatia, 26–30 May 2014; pp. 64–67. [Google Scholar] [CrossRef]

- Popa, C. Improved Accuracy Current-Mode Multiplier Circuits with Applications in Analog Signal Processing. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2013, 22, 443–447. [Google Scholar] [CrossRef]

- Kumngern, M.; Junnapiya, S. A CMOS Four-Quadrant Current Multiplier Using Electronically Tunable CCII. In Proceedings of the International Conference on Advanced Technologies for Communications (ATC 2013), Ho Chi Minh City, Vietnam, 16–18 October 2013; pp. 366–369. [Google Scholar] [CrossRef]

- Kumngern, M.; Torteanchai, U. A CMOS Current-Mode Multiplier/Divider Using a Current Amplifier. In Proceedings of the IEEE 7th International Power Engineering and Optimization Conference (PEOCO), Langkawi, Malaysia, 3–4 June 2013; pp. 742–745. [Google Scholar] [CrossRef]

- Kaedi, S.; Farshidi, E. A New Low Voltage Four-Quadrant Current Mode Multiplier. In Proceedings of the 20th Iranian Conference on Electrical Engineering (ICEE2012), Tehran, Iran, 15–17 May 2012; pp. 160–164. [Google Scholar] [CrossRef]

- Al-Absi, M.A.; Hussein, A.; Abuelma’atti, M.Y. A Novel Current-Mode Ultra Low Power Analog CMOS Four Quadrant Multiplier. In Proceedings of the International Conference on Computer and Communication Engineering (ICCCE), Kuala Lumpur, Malaysia, 3–5 July 2012; pp. 13–17. [Google Scholar] [CrossRef]

- Mongkolwai, P.; Tangsrirat, W. CFTA-Based Current Multiplier/Divider Circuit. In Proceedings of the International Symposium on Intelligent Signal Processing and Communications Systems (ISPACS), Chiang Mai, Thailand, 7–9 December 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Algueta Miguel, J.M.A.; De La Cruz Blas, C.A.; Lopez-Martin, A.J. Fully Differential Current-Mode CMOS Triode Translinear Multiplier. IEEE Trans. Circuits Syst. II Express Briefs 2010, 58, 21–25. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; De La Cruz Blas, C.A.; Ramirez-Angulo, J.; Carvajal, R.G. Compact Low-Voltage CMOS Current-Mode Multiplier/Divider. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010; pp. 1583–1586. [Google Scholar] [CrossRef]

- Petchakit, W.; Kiranon, W.; Wardkien, P.; Petchakit, S. A Current-Mode CCCII-Based Analog Multiplier/Divider. In Proceedings of the ECTI-CON2010–The 2010 ECTI International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology, Chiang Mai, Thailand, 19–21 May 2010; pp. 221–224. [Google Scholar]

- Pisutthipong, N.; Siripruchyanun, M. A Novel Simple Current-Mode Multiplier/Divider Employing Only Single Multiple-Output Current Controlled CTTA. In Proceedings of the TENCON 2009—2009 IEEE Region 10 Conference, Singapore, 23-26 November 2009; pp. 1–4. [Google Scholar] [CrossRef]

- Datta, D.; Chaudhuri, A.; Bhanja, M.; Ray, B.; Banerjee, A. Series Realization of Non-Linear Analog Functions using Current Mode Device. In Proceedings of the 4th International Conference on Information Systems and Computer Networks (ISCON), Mathura, India, 21–22 November 2019; pp. 694–699. [Google Scholar] [CrossRef]

- Fujcik, L.; Vrba, R.; Prokop, R. CMOS Auto-Tunable Low-Pass Filter for Harmonic Signal Generator. In Proceedings of the 33rd International Conference on Telecommunications and Signal Processing (TSP 2010), Budapest, Hungary, 17–20 August 2010; pp. 31–34. [Google Scholar]

- Gatti, U.; Maloberti, F.; Torelli, G. A Novel CMOS Linear Transconductance Cell for Continuous-Time Filters. In Proceedings of the 1990 IEEE International Symposium on Circuits and Systems (ISCAS), New Orleans, LA, USA, 1–3 May 1990; pp. 1173–1176. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).