Multi-Channel Neural Recording Implants: A Review

Abstract

:1. Introduction

2. Neural Signals

3. Neural Recording Architectures

4. Neural-Signal Amplifiers

4.1. Neural-Signal Amplifier Topologies

4.1.1. AC-Coupled Neural Amplifiers

4.1.2. DC-Coupled Neural Amplifiers

4.2. Multistage Amplifiers

4.3. Noise Reduction Techniques

4.3.1. Circuit Techniques

4.3.2. Systematic Technique

4.4. Advanced Neural-signal Amplifiers

5. Analog to Digital Converters

6. Data Compression

7. Conclusions

Funding

Acknowledgments

Conflicts of Interest

References

- Hochberg, L.R.; Bacher, D.; Jarosiewicz, B.; Masse, N.Y.; Simeral, J.D.; Vogel, J.; Haddadin, S.; Liu, J.; Cash, S.S.; Van Der Smagt, P.; et al. Reach and grasp by people with tetraplegia using a neurally controlled robotic arm. Nature 2012, 485, 372. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Collinger, J.L.; Wodlinger, B.; Downey, J.E.; Wang, W.; Tyler-Kabara, E.C.; Weber, D.J.; McMorland, A.J.; Velliste, M.; Boninger, M.L.; Schwartz, A.B. High-performance neuroprosthetic control by an individual with tetraplegia. Lancet 2013, 381, 557–564. [Google Scholar] [CrossRef] [Green Version]

- Anumanchipalli, G.K.; Chartier, J.; Chang, E.F. Speech synthesis from neural decoding of spoken sentences. Nature 2019, 568, 493. [Google Scholar] [CrossRef] [PubMed]

- Hochberg, L.R.; Serruya, M.D.; Friehs, G.M.; Mukand, J.A.; Saleh, M.; Caplan, A.H.; Branner, A.; Chen, D.; Penn, R.D.; Donoghue, J.P. Neuronal ensemble control of prosthetic devices by a human with tetraplegia. Nature 2006, 442, 164. [Google Scholar] [CrossRef]

- Wang, W.; Collinger, J.L.; Degenhart, A.D.; Tyler-Kabara, E.C.; Schwartz, A.B.; Moran, D.W.; Weber, D.J.; Wodlinger, B.; Vinjamuri, R.K.; Ashmore, R.C.; et al. An electrocorticographic brain interface in an individual with tetraplegia. PLoS ONE 2013, 8, e55344. [Google Scholar] [CrossRef] [Green Version]

- Aflalo, T.; Kellis, S.; Klaes, C.; Lee, B.; Shi, Y.; Pejsa, K.; Shanfield, K.; Hayes-Jackson, S.; Aisen, M.; Heck, C.; et al. Decoding motor imagery from the posterior parietal cortex of a tetraplegic human. Science 2015, 348, 906–910. [Google Scholar] [CrossRef] [Green Version]

- Yuste, R. From the neuron doctrine to neural networks. Nat. Rev. Neurosci. 2015, 16, 487–497. [Google Scholar] [CrossRef]

- Yazicioglu, R.F.; Merken, P.; Puers, R.; Van Hoof, C. A 200 μW Eight-Channel EEG Acquisition ASIC for Ambulatory EEG Systems. IEEE J. Solid-State Circuits 2008, 43, 3025–3038. [Google Scholar] [CrossRef]

- Buzsáki, G.; Anastassiou, C.A.; Koch, C. The origin of extracellular fields and currents—EEG, ECoG, LFP and spikes. Nat. Rev. Neurosci. 2012, 13, 407. [Google Scholar] [CrossRef]

- Pesaran, B.; Vinck, M.; Einevoll, G.T.; Sirota, A.; Fries, P.; Siegel, M.; Truccolo, W.; Schroeder, C.E.; Srinivasan, R. Investigating large-scale brain dynamics using field potential recordings: Analysis and interpretation. Nat. Neurosci. 2018, 21, 903–919. [Google Scholar] [CrossRef]

- Kaiju, T.; Yokota, M.; Watanabe, K.; Inoue, M.; Ando, H.; Takahashi, K.; Yoshida, F.; Hirata, M.; Suzuki, T.; Doi, K. High spatiotemporal resolution ECoG recording of somatosensory evoked potentials with flexible micro-electrode arrays. Front. Neural Circuits 2017, 11, 20. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Obaid, A.M.; Hanna, M.E.S.; Wu, Y.W.; Kollo, M.; Racz, R.R.; Angle, M.R.; Muller, J.; Brackbill, N.; Wray, W.; Franke, F.; et al. Massively parallel microwire arrays integrated with CMOS chips for neural recording. bioRxiv 2019, 573295. [Google Scholar] [CrossRef] [Green Version]

- Musk, E. An integrated brain-machine interface platform with thousands of channels. J. Med. Internet Res. 2019, 21, e16194. [Google Scholar] [CrossRef] [PubMed]

- Gosselin, B. Recent advances in neural recording microsystems. Sensors 2011, 11, 4572–4597. [Google Scholar] [CrossRef] [Green Version]

- Bagheri, A.; Salam, M.T.; Velazquez, J.L.P.; Genov, R. Low-frequency noise and offset rejection in DC-coupled neural amplifiers: A review and digitally-assisted design tutorial. IEEE Trans. Biomed. Circuits Syst. 2016, 11, 161–176. [Google Scholar] [CrossRef]

- Ruiz-Amaya, J.; Rodriguez-Perez, A.; Delgado-Restituto, M. A low noise amplifier for neural spike recording interfaces. Sensors 2015, 15, 25313–25335. [Google Scholar] [CrossRef] [Green Version]

- Clark, J.W.; Neuman, M.R.; Olson, W.H.; Peura, R.; Primiano, F.; Siedband, M.; Webster, J.; Wheeler, L. Medical Instrumentation: Application and Design; John Wiley & Sons: Hoboken, NJ, USA, 1998. [Google Scholar]

- Nurmikko, A.V.; Donoghue, J.P.; Hochberg, L.R.; Patterson, W.R.; Song, Y.K.; Bull, C.W.; Borton, D.A.; Laiwalla, F.; Park, S.; Ming, Y.; et al. Listening to brain microcircuits for interfacing with external world—Progress in wireless implantable microelectronic neuroengineering devices. Proc. IEEE 2010, 98, 375–388. [Google Scholar] [CrossRef]

- Hubel, D.H. Tungsten microelectrode for recording from single units. Science 1957, 125, 549–550. [Google Scholar] [CrossRef]

- Mollazadeh, M.; Murari, K.; Cauwenberghs, G.; Thakor, N. Wireless micropower instrumentation for multimodal acquisition of electrical and chemical neural activity. IEEE Trans. Biomed. Circuits Syst. 2009, 3, 388–397. [Google Scholar] [CrossRef]

- Quiroga, R.Q.; Panzeri, S. Extracting information from neuronal populations: Information theory and decoding approaches. Nat. Rev. Neurosci. 2009, 10, 173. [Google Scholar] [CrossRef]

- Patil, P.G.; Turner, D.A. The development of brain-machine interface neuroprosthetic devices. Neurotherapeutics 2008, 5, 137–146. [Google Scholar] [CrossRef] [Green Version]

- White, J.R.; Levy, T.; Bishop, W.; Beaty, J.D. Real-time decision fusion for multimodal neural prosthetic devices. PLoS ONE 2010, 5, e9493. [Google Scholar] [CrossRef] [Green Version]

- Buzsáki, G. Large-scale recording of neuronal ensembles. Nat. Neurosci. 2004, 7, 446. [Google Scholar] [CrossRef]

- Gerstein, G.; Clark, W. Simultaneous studies of firing patterns in several neurons. Science 1964, 143, 1325–1327. [Google Scholar] [CrossRef]

- Kandel, E.R.; Schwartz, J.H.; Jessell, T.M.; of Biochemistry, D.; Jessell, M.B.T.; Siegelbaum, S.; Hudspeth, A. Principles of Neural Science; McGraw-Hill: New York, NY, USA, 2000; Volume 4. [Google Scholar]

- Sodagar, A.M.; Wise, K.D.; Najafi, K. A wireless implantable microsystem for multichannel neural recording. IEEE Trans. Microw. Theory Tech. 2009, 57, 2565–2573. [Google Scholar] [CrossRef]

- Gosselin, B.; Ayoub, A.E.; Roy, J.F.; Sawan, M.; Lepore, F.; Chaudhuri, A.; Guitton, D. A mixed-signal multichip neural recording interface with bandwidth reduction. IEEE Trans. Biomed. Circuits Syst. 2009, 3, 129–141. [Google Scholar] [CrossRef]

- Lee, S.B.; Lee, H.M.; Kiani, M.; Jow, U.M.; Ghovanloo, M. An inductively powered scalable 32-channel wireless neural recording system-on-a-chip for neuroscience applications. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 360–371. [Google Scholar]

- Gosselin, B.; Sawan, M.; Kerherve, E. Linear-phase delay filters for ultra-low-power signal processing in neural recording implants. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 171–180. [Google Scholar] [CrossRef]

- Donoho, D.L. Compressed sensing. IEEE Trans. Inf. Theory 2006, 52, 1289–1306. [Google Scholar] [CrossRef]

- Candès, E.J.; Wakin, M.B. An introduction to compressive sampling [a sensing/sampling paradigm that goes against the common knowledge in data acquisition]. IEEE Signal Process. Mag. 2008, 25, 21–30. [Google Scholar]

- Candes, E.; Romberg, J. Sparsity and incoherence in compressive sampling. Inverse Probl. 2007, 23, 969. [Google Scholar] [CrossRef] [Green Version]

- Harrison, R.R.; Charles, C. A low-power low-noise CMOS amplifier for neural recording applications. IEEE J. Solid-State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Wattanapanitch, W.; Fee, M.; Sarpeshkar, R. An energy-efficient micropower neural recording amplifier. IEEE Trans. Biomed. Circuits Syst. 2007, 1, 136–147. [Google Scholar] [CrossRef]

- Azin, M.; Guggenmos, D.J.; Barbay, S.; Nudo, R.J.; Mohseni, P. A battery-powered activity-dependent intracortical microstimulation IC for brain-machine-brain interface. IEEE J. Solid-State Circuits 2011, 46, 731–745. [Google Scholar] [CrossRef]

- Zou, X.; Xu, X.; Yao, L.; Lian, Y. A 1-V 450-nW fully integrated programmable biomedical sensor interface chip. IEEE J. Solid-State Circuits 2009, 44, 1067–1077. [Google Scholar] [CrossRef]

- Harrison, R.; Watkins, P.; Kier, R.; Lovejoy, R.; Black, D.; Normann, R.; Solzbacher, F. A low-power integrated circuit for a wireless 100-electrode neural recording system. In Proceedings of the 2006 IEEE International Solid State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 6–9 February 2006; pp. 2258–2267. [Google Scholar]

- Lee, J.; Rhew, H.G.; Kipke, D.R.; Flynn, M.P. A 64 channel programmable closed-loop neurostimulator with 8 channel neural amplifier and logarithmic ADC. IEEE J. Solid-State Circuits 2010, 45, 1935–1945. [Google Scholar] [CrossRef]

- Ng, K.A.; Xu, Y.P. A compact, low input capacitance neural recording amplifier with C in/gain of 20fF.V/V. In Proceedings of the IEEE 2012 IEEE Biomedical Circuits and Systems Conference (BioCAS), Hsinchu, Taiwan, 28–30 November 2012; pp. 328–331. [Google Scholar]

- Mohseni, P.; Najafi, K. A fully integrated neural recording amplifier with DC input stabilization. IEEE Trans. Biomed. Eng. 2004, 51, 832–837. [Google Scholar] [CrossRef]

- Obeid, I.; Nicolelis, M.A.; Wolf, P.D. A low power multichannel analog front end for portable neural signal recordings. J. Neurosci. Methods 2004, 133, 27–32. [Google Scholar] [CrossRef]

- Chaturvedi, V.; Amrutur, B. An area-efficient noise-adaptive neural amplifier in 130 nm CMOS technology. IEEE J. Emerg. Sel. Top. Circuits Syst. 2011, 1, 536–545. [Google Scholar] [CrossRef]

- Zhao, W.; Li, H.; Zhang, Y. A low-noise integrated bioamplifier with active DC offset suppression. In Proceedings of the IEEE Biomedical Circuits and Systems Conference, Beijing, China, 26–28 November 2009; pp. 5–8. [Google Scholar]

- Liew, W.S.; Zou, X.; Yao, L.; Lian, Y. A 1-V 60-μW 16-channel interface chip for implantable neural recording. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 13–16 September 2009; pp. 507–510. [Google Scholar]

- Zou, X.; Liew, W.S.; Yao, L.; Lian, Y. A 1V 22 μW 32-channel implantable EEG recording IC. In Proceedings of the IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 7–11 Faburary 2010; pp. 126–127. [Google Scholar]

- Zhang, F.; Holleman, J.; Otis, B.P. Design of ultra-low power biopotential amplifiers for biosignal acquisition applications. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 344–355. [Google Scholar] [CrossRef]

- Gosselin, B.; Sawan, M.; Chapman, C.A. A low-power integrated bioamplifier with active low-frequency suppression. IEEE Trans. Biomed. Circuits Syst. 2007, 1, 184–192. [Google Scholar] [CrossRef] [PubMed]

- Ng, K.A.; Chan, P.K. A CMOS analog front-end IC for portable EEG/ECG monitoring applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 2335–2347. [Google Scholar] [CrossRef]

- Yazicioglu, R.F.; Merken, P.; Puers, R.; Van Hoof, C. A 60 μW 60 nV/√Hz Readout Front-End for Portable Biopotential Acquisition Systems. IEEE J. Solid-State Circuits 2007, 42, 1100–1110. [Google Scholar] [CrossRef]

- Muller, R.; Gambini, S.; Rabaey, J.M. A 0.013 mm2, 5 μW, DC-Coupled Neural Signal Acquisition IC With 0.5 V Supply. IEEE J. Solid-State Circuits 2011, 47, 232–243. [Google Scholar] [CrossRef]

- Biederman, W.; Yeager, D.J.; Narevsky, N.; Koralek, A.C.; Carmena, J.M.; Alon, E.; Rabaey, J.M. A Fully-Integrated, Miniaturized (0.125 mm2) 10.5 μW Wireless Neural Sensor. IEEE J. Solid-State Circuits 2013, 48, 960–970. [Google Scholar] [CrossRef]

- Harrison, R.R. The design of integrated circuits to observe brain activity. Proc. IEEE 2008, 96, 1203–1216. [Google Scholar] [CrossRef]

- Olsson, R.H.; Buhl, D.L.; Sirota, A.M.; Buzsáki, G.; Wise, K.D. Band-tunable and multiplexed integrated circuits for simultaneous recording and stimulation with microelectrode arrays. IEEE Trans. Biomed. Eng. 2005, 52, 1303–1311. [Google Scholar] [CrossRef]

- Yuan, S.; Johnson, L.G.; Liu, C.C.; Hutchens, C.; Rennaker, R.L. Current biased pseudo-resistor for implantable neural signal recording applications. In Proceedings of the IEEE Midwest Symposium on Circuits and Systems, Knoxville, TN, USA, 10–13 August 2008; pp. 658–661. [Google Scholar]

- Yin, M.; Ghovanloo, M. A low-noise preamplifier with adjustable gain and bandwidth for biopotential recording applications. In Proceedings of the IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007; pp. 321–324. [Google Scholar]

- Sodagar, A.M.; Perlin, G.E.; Yao, Y.; Najafi, K.; Wise, K.D. An implantable 64-channel wireless microsystem for single-unit neural recording. IEEE J. Solid-State Circuits 2009, 44, 2591–2604. [Google Scholar] [CrossRef]

- Chae, M.S.; Liu, W.; Sivaprakasam, M. Design optimization for integrated neural recording systems. IEEE J. Solid-State Circuits 2008, 43, 1931–1939. [Google Scholar] [CrossRef]

- Rodríguez-Pérez, A.; Ruiz-Amaya, J.; Delgado-Restituto, M.; Rodríguez-Vázquez, Á. An auto-calibrated neural spike recording channel with feature extraction capabilities. In Bioelectronics, Biomedical, and Bioinspired Systems V; and Nanotechnology V. International Society for Optics and Photonics; SPIE: Washington, CA, USA, 2011; Volume 8068, p. 80680N. [Google Scholar]

- Denison, T.; Consoer, K.; Santa, W.; Avestruz, A.T.; Cooley, J.; Kelly, A. A 2.2 μW 94nV/Hz Chopper-Stabilized Instrumentation Amplifier for Chronic Measurement of Neural Field Potentials. IEEE J. Solid-State Circuits 2007, 42, 2934–2945. [Google Scholar] [CrossRef]

- Biederman, W.; Yeager, D.J.; Narevsky, N.; Leverett, J.; Neely, R.; Carmena, J.M.; Alon, E.; Rabaey, J.M. A 4.78 mm 2 fully-integrated neuromodulation SoC combining 64 acquisition channels with digital compression and simultaneous dual stimulation. IEEE J. Solid-State Circuits 2015, 50, 1038–1047. [Google Scholar] [CrossRef]

- Ng, K.A.; Xu, Y.P. A low-power, high CMRR neural amplifier system employing CMOS inverter-based OTAs with CMFB through supply rails. IEEE J. Solid-State Circuits 2016, 51, 724–737. [Google Scholar]

- Rezaee-Dehsorkh, H.; Ravanshad, N.; Lotfi, R.; Mafinezhad, K.; Sodagar, A.M. Analysis and design of tunable amplifiers for implantable neural recording applications. IEEE J. Emerg. Sel. Top. Circuits Syst. 2011, 1, 546–556. [Google Scholar] [CrossRef]

- Abdelhalim, K.; Genov, R. Compact chopper-stabilized neural amplifier with low-distortion high-pass filter in 013 μm CMOS. Proceeding of the IEEE International Symposium on Circuits and Systems, Seoul, Korea, 20–23 May 2012; pp. 1075–1078. [Google Scholar]

- Abdelhalim, K.; Kokarovtseva, L.; Velazquez, J.L.P.; Genov, R. 915-MHz FSK/OOK wireless neural recording SoC with 64 mixed-signal FIR filters. IEEE J. Solid-State Circuits 2013, 48, 2478–2493. [Google Scholar] [CrossRef]

- Kassiri, H.; Abdelhalim, K.; Genov, R. Low-distortion super-GOhm subthreshold-MOS resistors for CMOS neural amplifiers. In Proceedings of the IEEE Biomedical Circuits and Systems Conference (BioCAS), Rotterdam, The Netherlands, 31 October–2 November 2013; pp. 270–273. [Google Scholar]

- Abdelhalim, K.; Jafari, H.M.; Kokarovtseva, L.; Velazquez, J.L.P.; Genov, R. 64-channel UWB wireless neural vector analyzer SOC with a closed-loop phase synchrony-triggered neurostimulator. IEEE J. Solid-State Circuits 2013, 48, 2494–2510. [Google Scholar] [CrossRef]

- Qian, C.; Parramon, J.; Sanchez-Sinencio, E. A micropower low-noise neural recording front-end circuit for epileptic seizure detection. IEEE J. Solid-State Circuits 2011, 46, 1392–1405. [Google Scholar] [CrossRef]

- Carusone, T.C.; Johns, D.A.; Martin, K.W. Integrated-Circuit Devices and Modeling. In Analog Integrated Circuit Design, 2nd ed.; John Wiley & Sons: Hoboken, NJ, USA, 2012; pp. 42–44. [Google Scholar]

- Steyaert, M.S.; Sansen, W.M. A micropower low-noise monolithic instrumentation amplifier for medical purposes. IEEE J. Solid-State Circuits 1987, 22, 1163–1168. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw-Hill Series: New York, NY, USA, 2005. [Google Scholar]

- Shoaran, M.; Kamal, M.H.; Pollo, C.; Vandergheynst, P.; Schmid, A. Compact low-power cortical recording architecture for compressive multichannel data acquisition. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 857–870. [Google Scholar] [CrossRef]

- Enz, C.C.; Temes, G.C. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef] [Green Version]

- Makinwa, K. Dynamic-offset Cancellation Techniques in CMOS. IEEE ISSCC Tutor. Sess. 2007. [Google Scholar]

- Xu, J.; Yazicioglu, R.F.; Grundlehner, B.; Harpe, P.; Makinwa, K.A.; Van Hoof, C. A 160 μW 8 Channel Active Electrode System for EEG Monitoring. IEEE Trans. Biomed. Circuits Syst. 2011, 5, 555–567. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Verma, N.; Shoeb, A.; Bohorquez, J.; Dawson, J.; Guttag, J.; Chandrakasan, A.P. A Micro-Power EEG Acquisition SoC with Integrated Feature Extraction Processor for a Chronic Seizure Detection System. IEEE J. Solid-State Circuits 2010, 45, 804–816. [Google Scholar] [CrossRef]

- Jochum, T.; Denison, T.; Wolf, P. Integrated circuit amplifiers for multi-electrode intracortical recording. J. Neural Eng. 2009, 6, 012001. [Google Scholar] [CrossRef] [PubMed]

- Wu, R.; Makinwa, K.A.; Huijsing, J.H. A chopper current-feedback instrumentation amplifier with a 1 mHz 1/f noise corner and an AC-coupled ripple reduction loop. IEEE J. Solid-State Circuits 2009, 44, 3232–3243. [Google Scholar] [CrossRef] [Green Version]

- Witte, F.; Makinwa, K.; Huijsing, J. Dynamic Offset Compensated CMOS Amplifiers; Springer Science & Business Media: Berlin, Germany, 2009. [Google Scholar]

- Bakker, A.; Thiele, K.; Huijsing, J. A CMOS nested chopper instrumentation amplifier with 100 nV offset. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 9 February 2000; pp. 156–157. [Google Scholar]

- Van Der Meer, J.C.; Riedijk, F.R.; van Kampen, E.; Makinwa, K.A.; Huijsing, J.H. A fully integrated CMOS Hall sensor with a 365 μT 3σ offset for compass applications. In Proceedings of the IEEE International Solid State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 10 February 2005; pp. 246–247. [Google Scholar]

- Pertijs, M.A.; Makinwa, K.A.; Huijsing, J.H. A CMOS smart temperature sensor with a 3σ inaccuracy of ±0.1 °C from −55 °C to 125 °C. IEEE J. Solid-State Circuits 2005, 40, 2805–2815. [Google Scholar] [CrossRef]

- Makinwa, K.A.; Snoeij, M.F. A CMOS Temperature-to-Frequency Converter With an Inaccuracy of Less Than ±0.5 °C (3σ) From −40 °C to −105 °C. IEEE J. Solid-State Circuits 2006, 41, 2992–2997. [Google Scholar] [CrossRef]

- Enz, C.C. High Precision CMOS Micropower Amplifiers; Technical Report; EPFL: Lausanne, Switzerland, 1989. [Google Scholar]

- Enz, C.C.; Vittoz, E.A.; Krummenacher, F. A CMOS chopper amplifier. IEEE J. Solid-State Circuits 1987, 22, 335–342. [Google Scholar] [CrossRef]

- Menolfi, C.; Huang, Q. A fully integrated, untrimmed CMOS instrumentation amplifier with submicrovolt offset. IEEE J. Solid-State Circuits 1999, 34, 415–420. [Google Scholar] [CrossRef]

- Menolfi, C.; Huang, Q. A chopper modulated instrumentation amplifier with first order low-pass filter and delayed modulation scheme. In Proceedings of the IEEE Solid-State Circuits Conference, San Francisco, CA, USA, 15–17 February 1999; pp. 54–57. [Google Scholar]

- Bilotti, A.; Monreal, G. Chopper-stabilized amplifiers with a track-and-hold signal demodulator. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1999, 46, 490–495. [Google Scholar] [CrossRef]

- Huang, Q.; Menolfi, C. A 200 nV offset 65 nV/Hz noise PSD 5.6 kHz chopper instrumentation amplifier in 1 μm digital CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 7 February 2001; pp. 362–363. [Google Scholar]

- Denison, T.; Consoer, K.; Kelly, A.; Hachenburg, A.; Santa, W. A 22 μW 94 nV/Hz, Chopper-Stabilized Instrumentation Amplifier for EEG Detection in Chronic Implants. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2007; pp. 162–594. [Google Scholar]

- Fan, Q.; Sebastiano, F.; Huijsing, J.H.; Makinwa, K.A. A 1.8 μW 60 nV/Hz Capacitively-Coupled Chopper Instrumentation Amplifier in 65 nm CMOS for Wireless Sensor Nodes. IEEE J. Solid-State Circuits 2011, 46, 1534–1543. [Google Scholar] [CrossRef]

- Khazaei, Y.; Sodagar, A.M. Multi-Channel ADC with Improved Bit Rate and Power Consumption for ElectroCorticoGraphy Systems. In Proceedings of the IEEE Biomedical Circuits and Systems Conference (BioCAS), Nara, Japan, 17–19 October 2019; pp. 1–4. [Google Scholar]

- Nasserian, M.; Peiravi, A.; Moradi, F. An adaptive-resolution signal-specific ADC for sensor-interface applications. Analog Integr. Circuits Signal Process. 2019, 98, 125–135. [Google Scholar] [CrossRef]

- Pareschi, F.; Albertini, P.; Frattini, G.; Mangia, M.; Rovatti, R.; Setti, G. Hardware-algorithms co-design and implementation of an analog-to-information converter for biosignals based on compressed sensing. IEEE Trans. Biomed. Circuits Syst. 2015, 10, 149–162. [Google Scholar] [CrossRef] [PubMed]

- Robert, P.Y.; Gosselin, B.; Ayoub, A.E.; Sawan, M. An ultra-low-power successive-approximation-based ADC for implantable sensing devices. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, San Juan, Puerto Rico, 6–9 August 2006; Volume 1, pp. 7–11. [Google Scholar]

- Shulyzki, R.; Abdelhalim, K.; Bagheri, A.; Florez, C.M.; Carlen, P.L.; Genov, R. 256-site active neural probe and 64-channel responsive cortical stimulator. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 19–21 September 2011; pp. 1–4. [Google Scholar]

- Wang, J.; Hua, Y.; Zhu, Z. A 10-bit reconfigurable ADC with SAR/SS mode for neural recording. Analog Integr. Circuits Signal Process. 2019, 101, 297–305. [Google Scholar] [CrossRef]

- Barati, S.; Yavari, M. An adaptive continuous-time incremental ΣΔ ADC for neural recording implants. Int. J. Circuit Theory Appl. 2019, 47, 187–203. [Google Scholar] [CrossRef]

- Qian, C.; Shi, J.; Parramon, J.; Sánchez-Sinencio, E. A low-power configurable neural recording system for epileptic seizure detection. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 499–512. [Google Scholar] [CrossRef] [PubMed]

- Miaou, S.G.; Chao, S.N. Wavelet-based lossy-to-lossless ECG compression in a unified vector quantization framework. IEEE Trans. Biomed. Eng. 2005, 52, 539–543. [Google Scholar] [CrossRef]

- Aviyente, S. Compressed sensing framework for EEG compression. In Proceedings of the 2007 IEEE/SP 14th Workshop on Statistical Signal Processing, Madison, WI, USA, 26-29 August 2007; pp. 181–184. [Google Scholar]

- Candes, E.J.; Tao, T. Near-optimal signal recovery from random projections: Universal encoding strategies? IEEE Trans. Inf. Theory 2006, 52, 5406–5425. [Google Scholar] [CrossRef] [Green Version]

- Laska, J.N.; Kirolos, S.; Duarte, M.F.; Ragheb, T.S.; Baraniuk, R.G.; Massoud, Y. Theory and implementation of an analog-to-information converter using random demodulation. In Proceedings of the IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007; pp. 1959–1962. [Google Scholar]

- Chen, X.; Yu, Z.; Hoyos, S.; Sadler, B.M.; Silva-Martinez, J. A sub-Nyquist rate sampling receiver exploiting compressive sensing. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 58, 507–520. [Google Scholar] [CrossRef]

- Shoaran, M.; Lopez, M.M.; Pasupureddi, V.S.R.; Leblebici, Y.; Schmid, A. A low-power area-efficient compressive sensing approach for multi-channel neural recording. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS2013), Beijing, China, 19–23 May 2013; pp. 2191–2194. [Google Scholar]

- Kamal, M.H.; Shoaran, M.; Leblebici, Y.; Schmid, A.; Vandergheynst, P. Compressive multichannel cortical signal recording. In Proceedings of the IEEE International Conference on Acoustics, Speech and Signal Processing, Vancouver, BC, Canada, 26–31 May 2013; pp. 4305–4309. [Google Scholar]

- Chen, F.; Chandrakasan, A.P.; Stojanovic, V.M. Design and analysis of a hardware-efficient compressed sensing architecture for data compression in wireless sensors. IEEE J. Solid-State Circuits 2012, 47, 744–756. [Google Scholar] [CrossRef] [Green Version]

- Suo, Y.; Zhang, J.; Xiong, T.; Chin, P.S.; Etienne-Cummings, R.; Tran, T.D. Energy-efficient multi-mode compressed sensing system for implantable neural recordings. IEEE Trans. Biomed. Circuits Syst. 2014, 8. [Google Scholar] [CrossRef]

- Liu, X.; Zhu, H.; Zhang, M.; Richardson, A.G.; Lucas, T.H.; Van der Spiegel, J. Design of a low-noise, high power efficiency neural recording front-end with an integrated real-time compressed sensing unit. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 2996–2999. [Google Scholar]

- Zhang, J.; Mitra, S.; Suo, Y.; Cheng, A.; Xiong, T.; Michon, F.; Welkenhuysen, M.; Kloosterman, F.; Chin, P.S.; Hsiao, S.; et al. A closed-loop compressive-sensing-based neural recording system. J. Neural Eng. 2015, 12, 036005. [Google Scholar] [CrossRef]

- Chen, F.; Chandrakasan, A.P.; Stojanović, V. A signal-agnostic compressed sensing acquisition system for wireless and implantable sensors. In Proceedings of the IEEE Custom Integrated Circuits Conference 2010, San Jose, CA, USA, 19–22 September 2010; pp. 1–4. [Google Scholar]

- Liu, X.; Zhang, M.; Xiong, T.; Richardson, A.G.; Lucas, T.H.; Chin, P.S.; Etienne-Cummings, R.; Tran, T.D.; Van der Spiegel, J. A fully integrated wireless compressed sensing neural signal acquisition system for chronic recording and brain machine interface. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 874–883. [Google Scholar] [CrossRef]

- Lewicki, M.S. A review of methods for spike sorting: The detection and classification of neural action potentials. Netw. Comput. Neural Syst. 1998, 9, R53–R78. [Google Scholar] [CrossRef]

- Eftekhar, A.; Sivylla, E.P.; Timothy, G.C. Towards a next generation neural interface: Optimizing power, bandwidth and data quality. In Proceedings of the IEEE Biomedical Circuits and Systems Conference (BioCAS), Paphos, Cyprus, 3–5 November 2010; pp. 122–125. [Google Scholar]

- Harrison, R.R. A low-power integrated circuit for adaptive detection of action potentials in noisy signals. In Proceedings of the 25th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (IEEE Cat. No.03CH37439), Cancun, Mexico, 17–21 September 2003; Volume 4, pp. 3325–3328. [Google Scholar]

- Perelman, Y.; Ginosar, R. An integrated system for multichannel neuronal recording with spike/LFP separation, integrated A/D conversion and threshold detection. IEEE Trans. Biomed. Eng. 2006, 54, 130–137. [Google Scholar] [CrossRef] [PubMed]

- Obeid, I.; Wolf, P.D. Evaluation of spike-detection algorithms for a brain-machine interface application. IEEE Trans. Biomed. Eng. 2004, 51, 905–911. [Google Scholar] [CrossRef] [PubMed]

- Bonfanti, A.; Ceravolo, M.; Zambra, G.; Gusmeroli, R.; Spinelli, A.; Lacaita, A.L.; Angotzi, G.; Baranauskas, G.; Fadiga, L. A multi-channel low-power system-on-chip for single-unit recording and narrowband wireless transmission of neural signal. In Proceedings of the IEEE Engineering in Medicine and Biology, Buenos Aires, Argentina, 31 August–4 September 2010; pp. 1555–1560. [Google Scholar]

- Rizk, M.; Obeid, I.; Callender, S.H.; Wolf, P.D. A single-chip signal processing and telemetry engine for an implantable 96-channel neural data acquisition system. J. Neural Eng. 2007, 4, 309. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Sodagar, A.M.; Wise, K.D.; Najafi, K. A fully integrated mixed-signal neural processor for implantable multichannel cortical recording. IEEE Trans. Biomed. Eng. 2007, 54, 1075–1088. [Google Scholar] [CrossRef]

- Haas, A.M.; Cohen, M.H.; Abshires, P.A. Real-time variance based template matching spike sorting system. In Proceedings of the IEEE/NIH Life Science Systems and Applications Workshop, Bethesda, MD, USA, 8–9 November 2007; pp. 104–107. [Google Scholar]

- Gosselin, B.; Sawan, M. An ultra low-power CMOS automatic action potential detector. IEEE Trans. Neural Syst. Rehabil. Eng. 2009, 17, 346–353. [Google Scholar] [CrossRef] [PubMed]

- Rogers, C.L.; Harris, J.G. A low-power analog spike detector for extracellular neural recordings. In Proceedings of the IEEE International Conference on Electronics, Circuits and Systems (ICECS 2004), Tel Aviv, Israel, 13–15 December 2004; pp. 290–293. [Google Scholar]

- Peng, C.C.; Sabharwal, P.; Bashirullah, R. An adaptive neural spike detector with threshold-lock loop. In Proceedings of the IEEE International Symposium on Circuits and Systems, Taipei, Taiwan, 24–17 May 2009; pp. 2133–2136. [Google Scholar]

- Watkins, P.T.; Santhanam, G.; Shenoy, K.V.; Harrison, R.R. Validation of adaptive threshold spike detector for neural recording. In Proceedings of the IEEE Engineering in Medicine and Biology Society, San Francisco, CA, USA, 1–5 September 2004; Volume 2, pp. 4079–4082. [Google Scholar]

- Kamboh, A.M.; Raetz, M.; Oweiss, K.G.; Mason, A. Area-power efficient VLSI implementation of multichannel DWT for data compression in implantable neuroprosthetics. IEEE Trans. Biomed. Circuits Syst. 2007, 1, 128–135. [Google Scholar] [CrossRef] [PubMed]

- Gosselin, B.; Hosseini Khayat, S.S.; Quotb, A.; Sawan, M. Hardware implementation of wavelet transforms for real-time detection and compression of biopotentials in neural implants. Curr. Dev. Theory Appl. Wavelets 2011, 5, 1–34. [Google Scholar]

- Peng, C.C.; Xiao, Z.; Bashirullah, R. Toward energy efficient neural interfaces. IEEE Trans. Biomed. Eng. 2009, 56, 2697–2700. [Google Scholar] [CrossRef] [PubMed]

- Aziz, J.N.; Abdelhalim, K.; Shulyzki, R.; Genov, R.; Bardakjian, B.L.; Derchansky, M.; Serletis, D.; Carlen, P.L. 256-channel neural recording and delta compression microsystem with 3D electrodes. IEEE J. Solid-State Circuits 2009, 44, 995–1005. [Google Scholar] [CrossRef]

| Signal Type | Amplitude | Bandwidth |

|---|---|---|

| Extracellular action potential | 50–500 Vpp | 100 Hz–10 kHz |

| Intracellular action potential | 10–70 mVpp | 100 Hz–10 kHz |

| Local field potentials | 0.5–5 mVpp | 1 mHz–200 Hz |

| Electroencephalogram | 10–400 Vpp | 1 mHz–200 Hz |

| Electrocorticography | 10–1000 Vpp | 1 mHz–200 Hz |

| Amplifier Topology | Figure | Ref. | Pros | Cons |

|---|---|---|---|---|

| CFN | 3a | [34] | Accurate gain, suitable for multistage amplifier | Large cap. area to obtain high gain |

| CFN with T-network | 3b | [40] | Input and total cap. reduction | Low-cutoff frequency increase |

| Electrode cap. and resistive feedback | 3c | [41] | No need to input cap. | Inaccurate and not adjustable high pass pole |

| OLN | 3d | [43] | Small input cap. area | Inaccurate gain |

| CAFN | 3e | [16,44] | Smaller total cap. area compared to CFN | Higher power consumption and noise compared to CFN |

| MCCFN | 3f | [45,46] | Higher swing as a single stage high gain amplifier compared to CFN | Higher power consumption compared to CFN, Higher area consumption compared to multistage CFN |

| Analog Integrator | 4a | [48] | Elimination of input cap. | Inaccurate gain and Low-cutoff frequency, Large power consumption |

| Differential difference amplifier | 4b | [49] | Elimination of input cap. | Inaccurate gain and Low-cutoff frequency, large off-chip passive components |

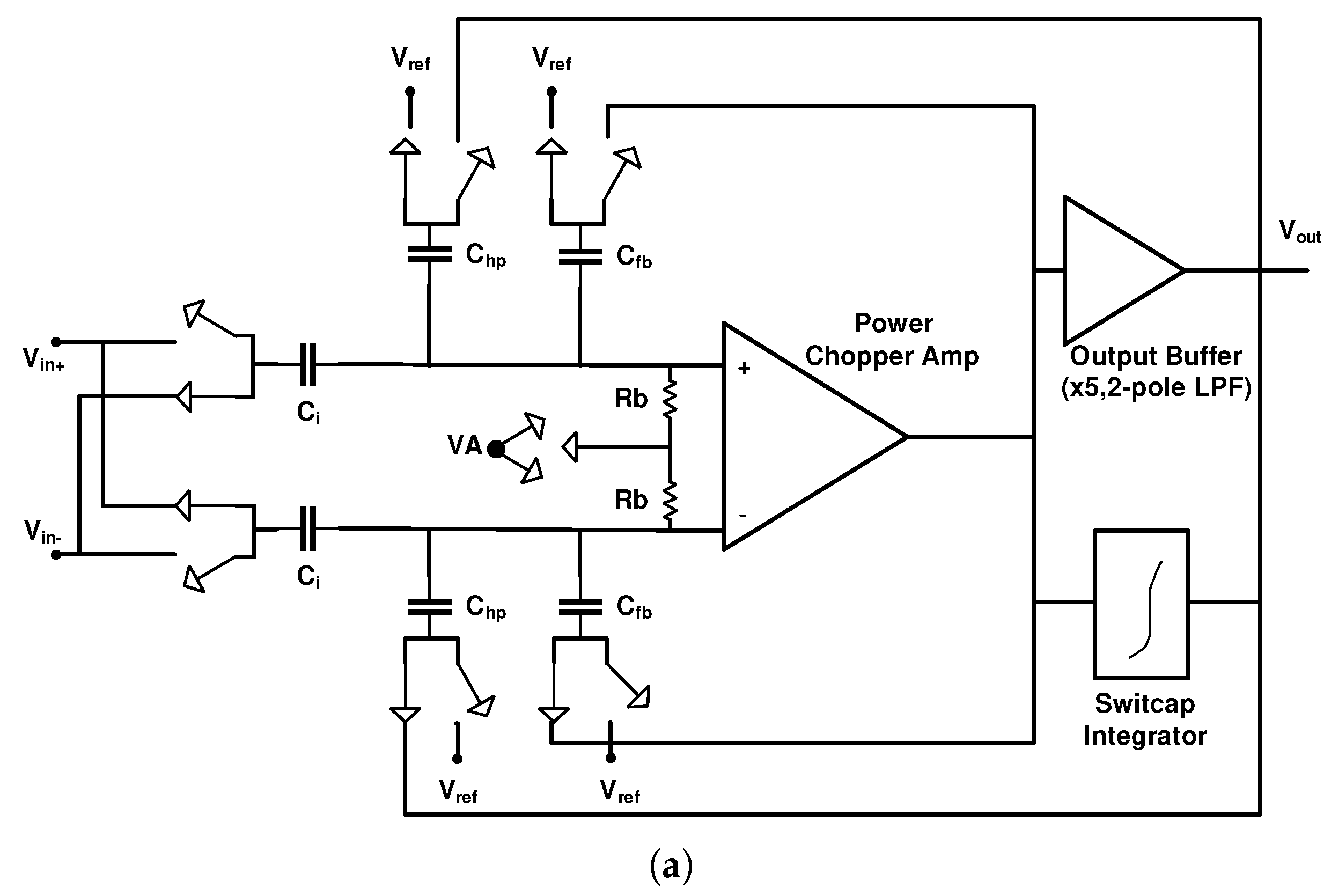

| Analog & digital DSL | 4c | [8,50] | Relax analog DSL requirement due to digital DSL | Large area and power consumption |

| Differential pair width modulation | 4d | [51,52] | Fully-digital DC offset rejection | IRN and CMRR variation with input offset variation, complexity overhead |

| Fully-digital DSL | 11 | [15] | Fully-digital DC offset rejection | Inaccurate gain, high power consumption and NEF |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hashemi Noshahr, F.; Nabavi, M.; Sawan, M. Multi-Channel Neural Recording Implants: A Review. Sensors 2020, 20, 904. https://doi.org/10.3390/s20030904

Hashemi Noshahr F, Nabavi M, Sawan M. Multi-Channel Neural Recording Implants: A Review. Sensors. 2020; 20(3):904. https://doi.org/10.3390/s20030904

Chicago/Turabian StyleHashemi Noshahr, Fereidoon, Morteza Nabavi, and Mohamad Sawan. 2020. "Multi-Channel Neural Recording Implants: A Review" Sensors 20, no. 3: 904. https://doi.org/10.3390/s20030904