A 0.3 V PNN Based 10T SRAM with Pulse Control Based Read-Assist and Write Data-Aware Schemes for Low Power Applications

Abstract

:1. Introduction

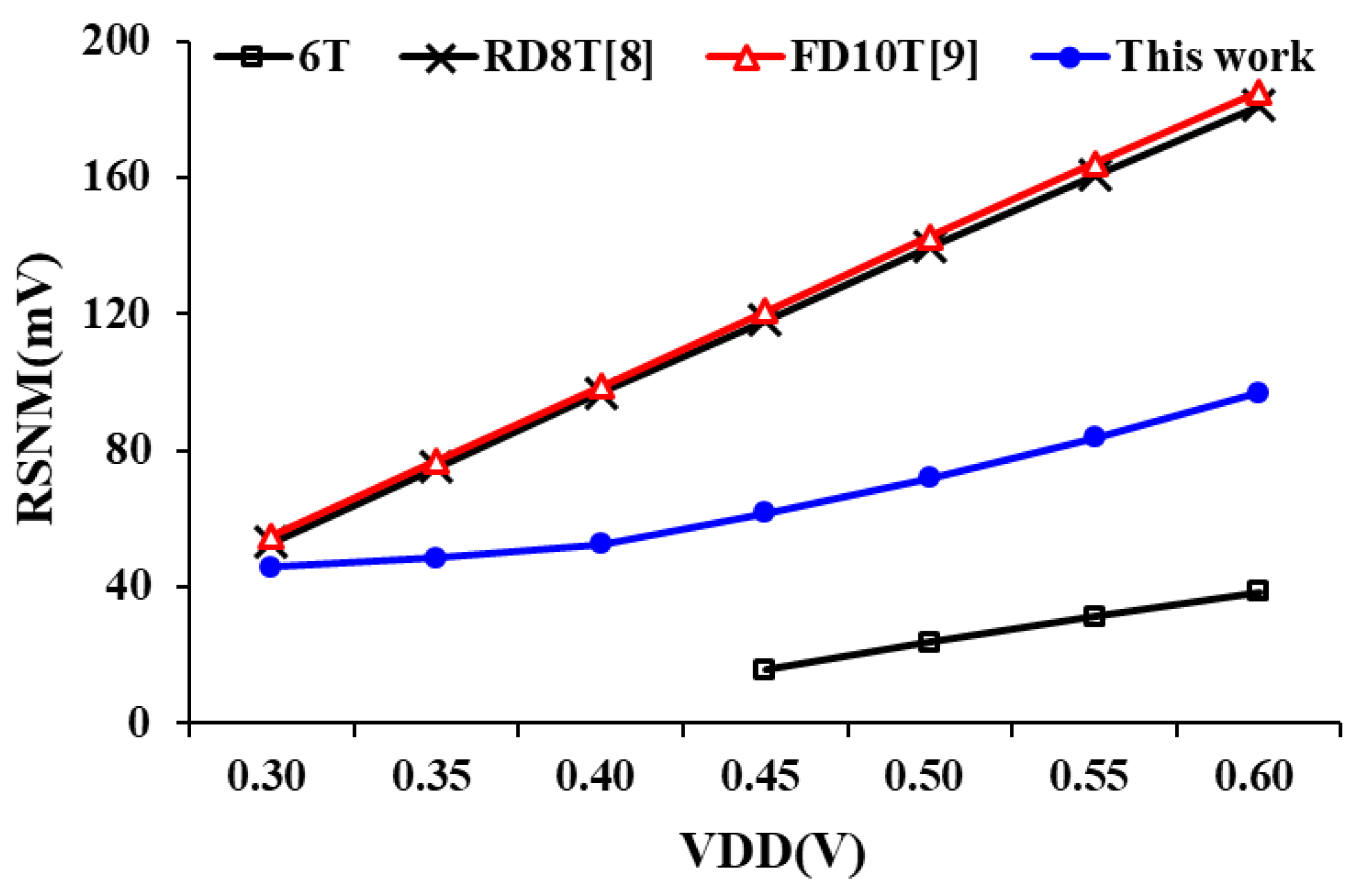

- ❖

- The proposed 10T SRAM design solves the half-selected problems;

- ❖

- The read decoupling technique increase the read static noise margin;

- ❖

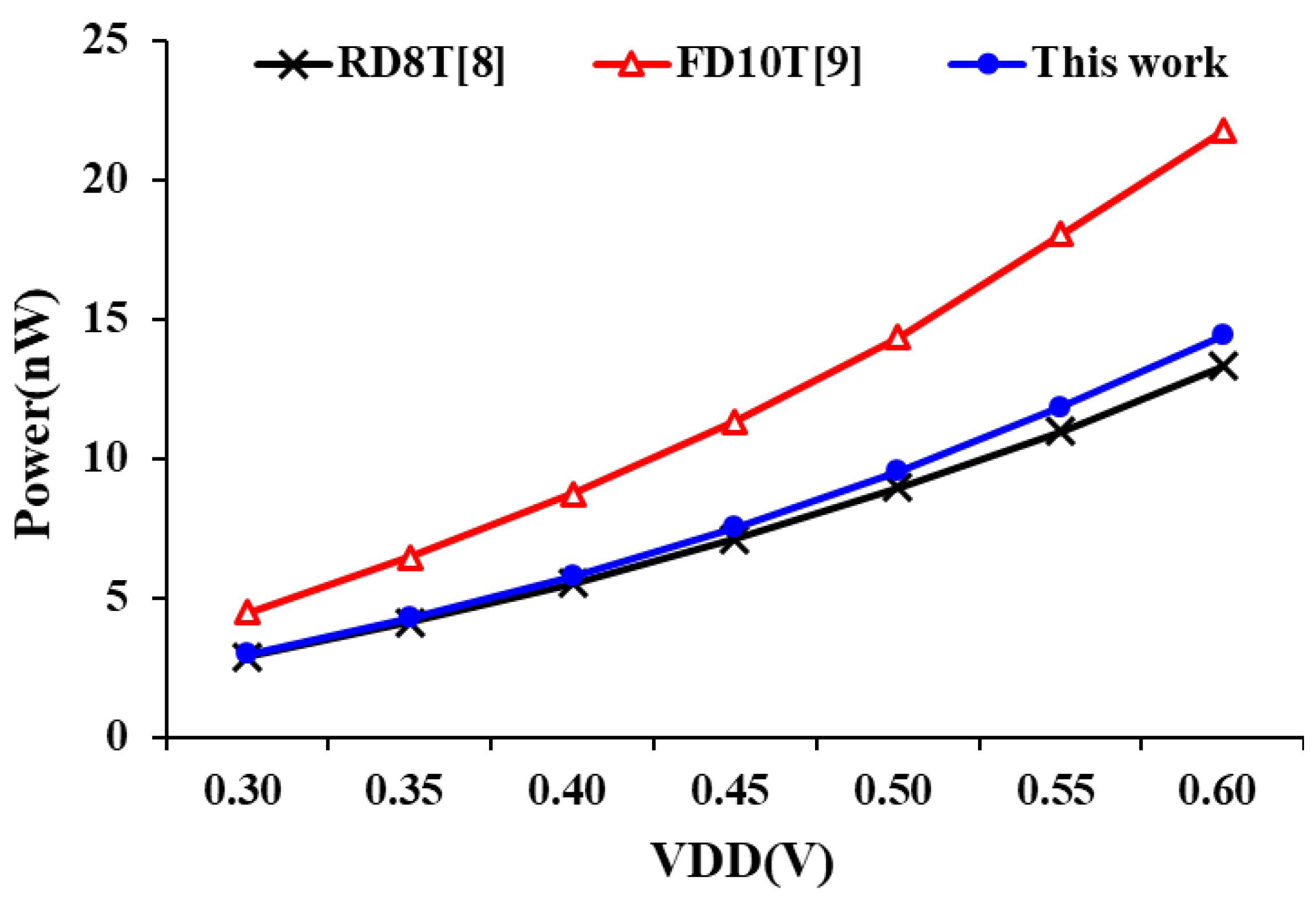

- The write data-aware techniques cut off the pull-down path and achieved low leakage power.

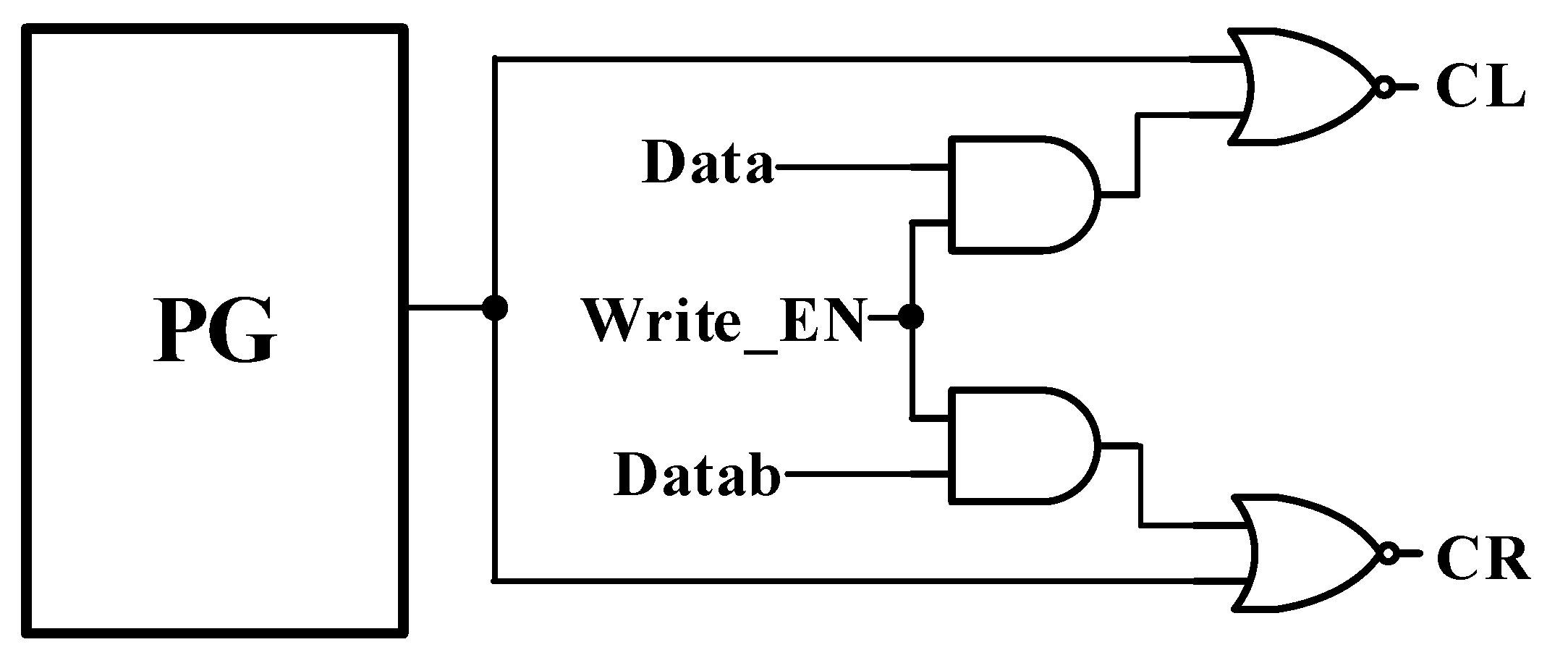

2. Proposed 10T SRAM Architecture

2.1. Memory Cell Design with 10T

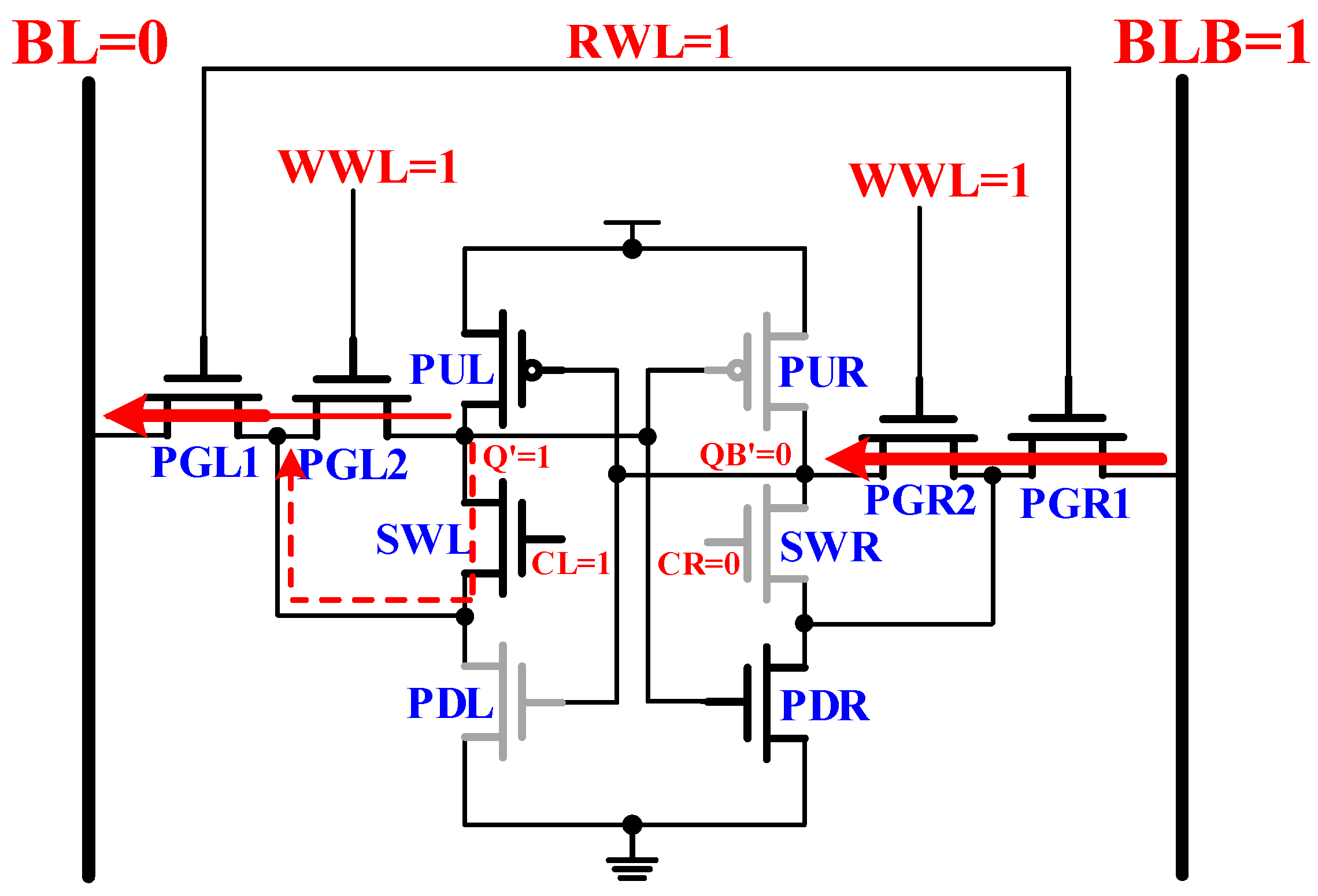

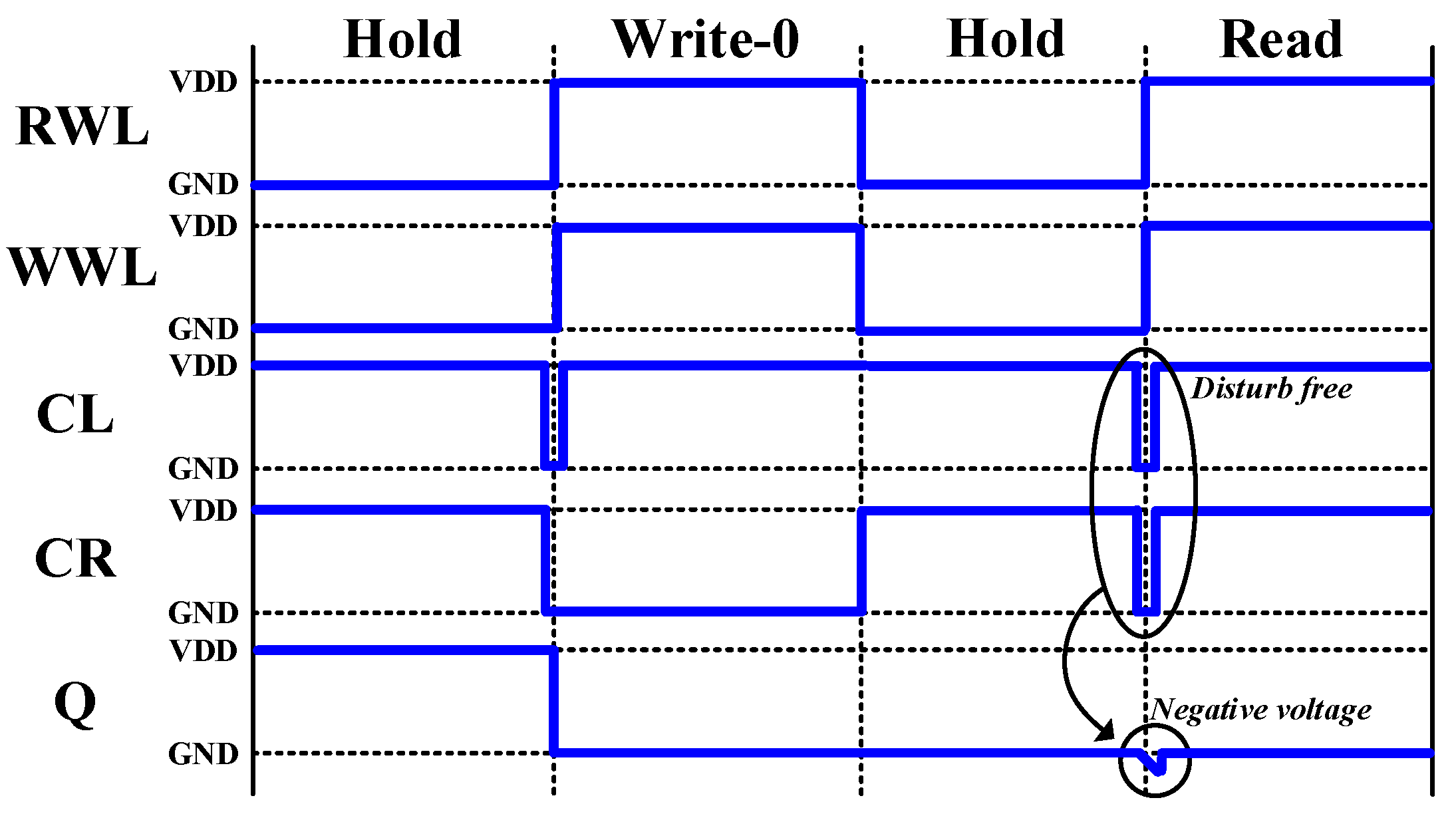

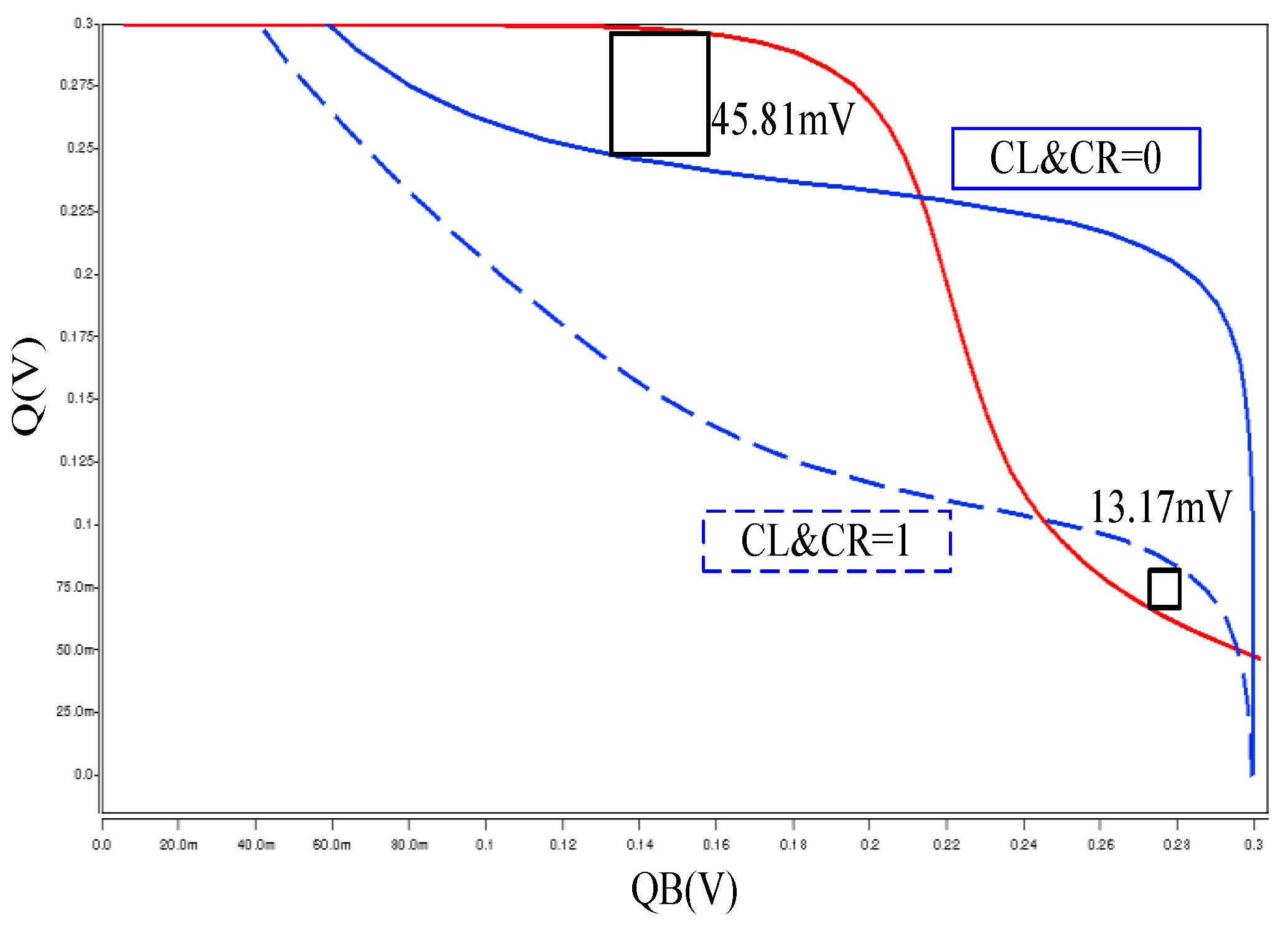

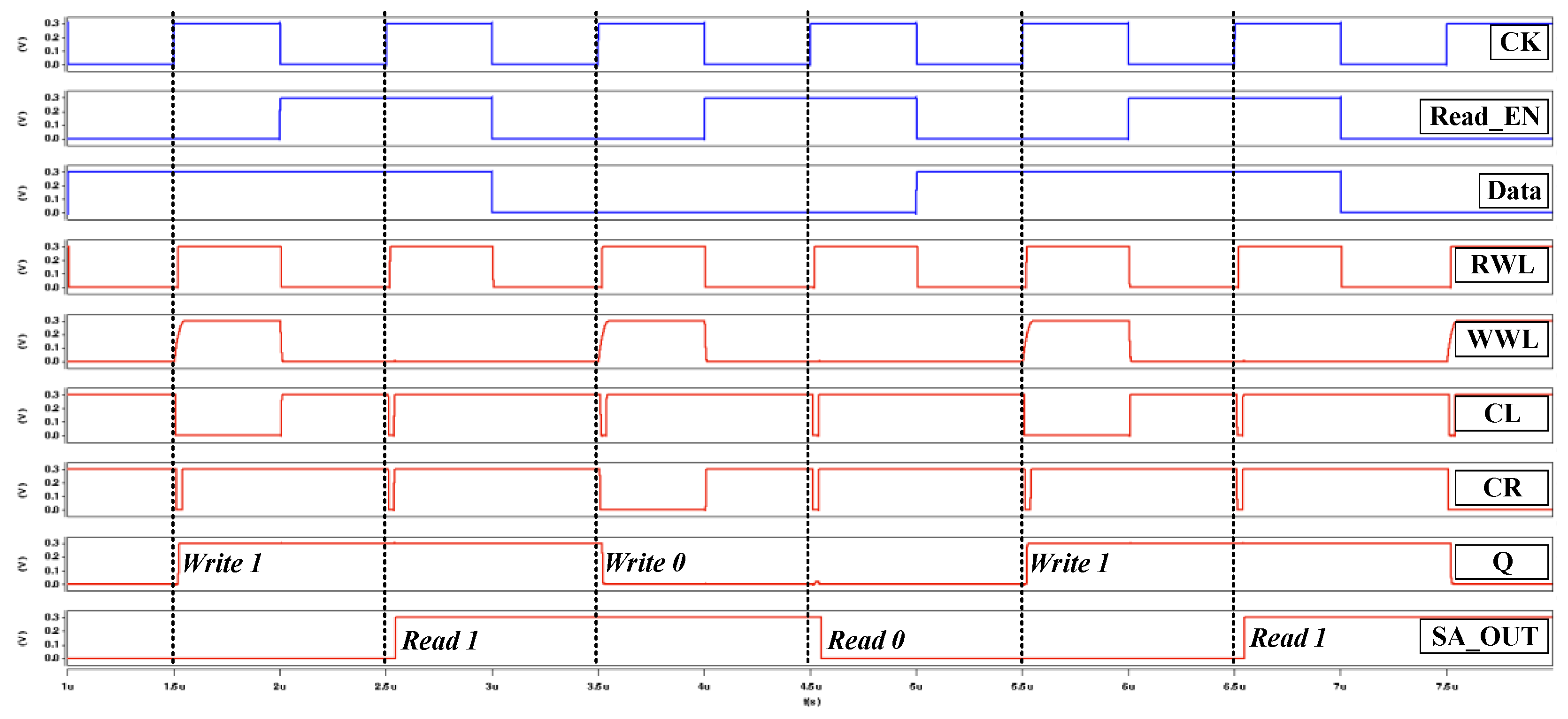

2.2. Write Mode Operatio

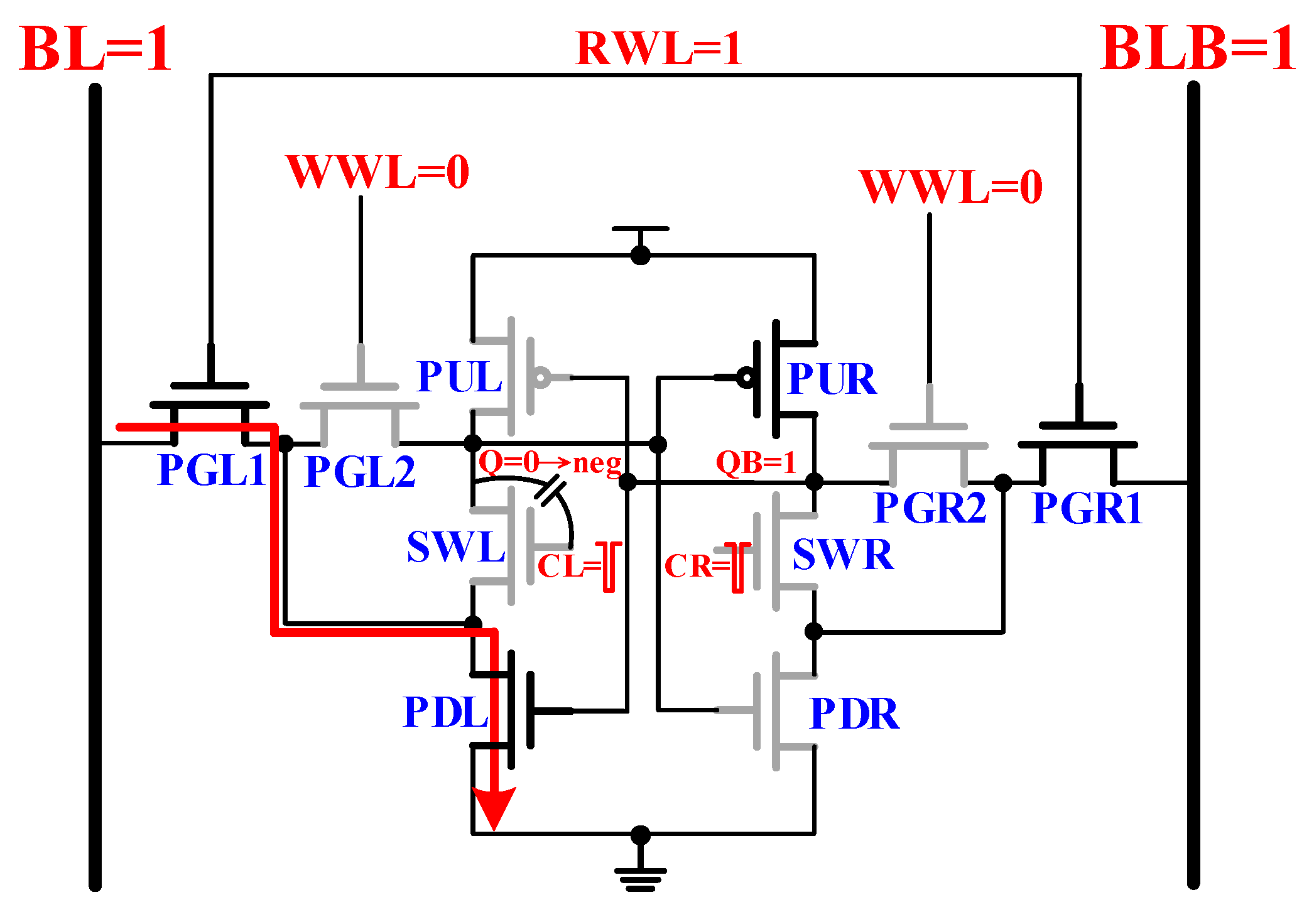

2.3. Read Mode Operation

2.4. Write Half-Selected

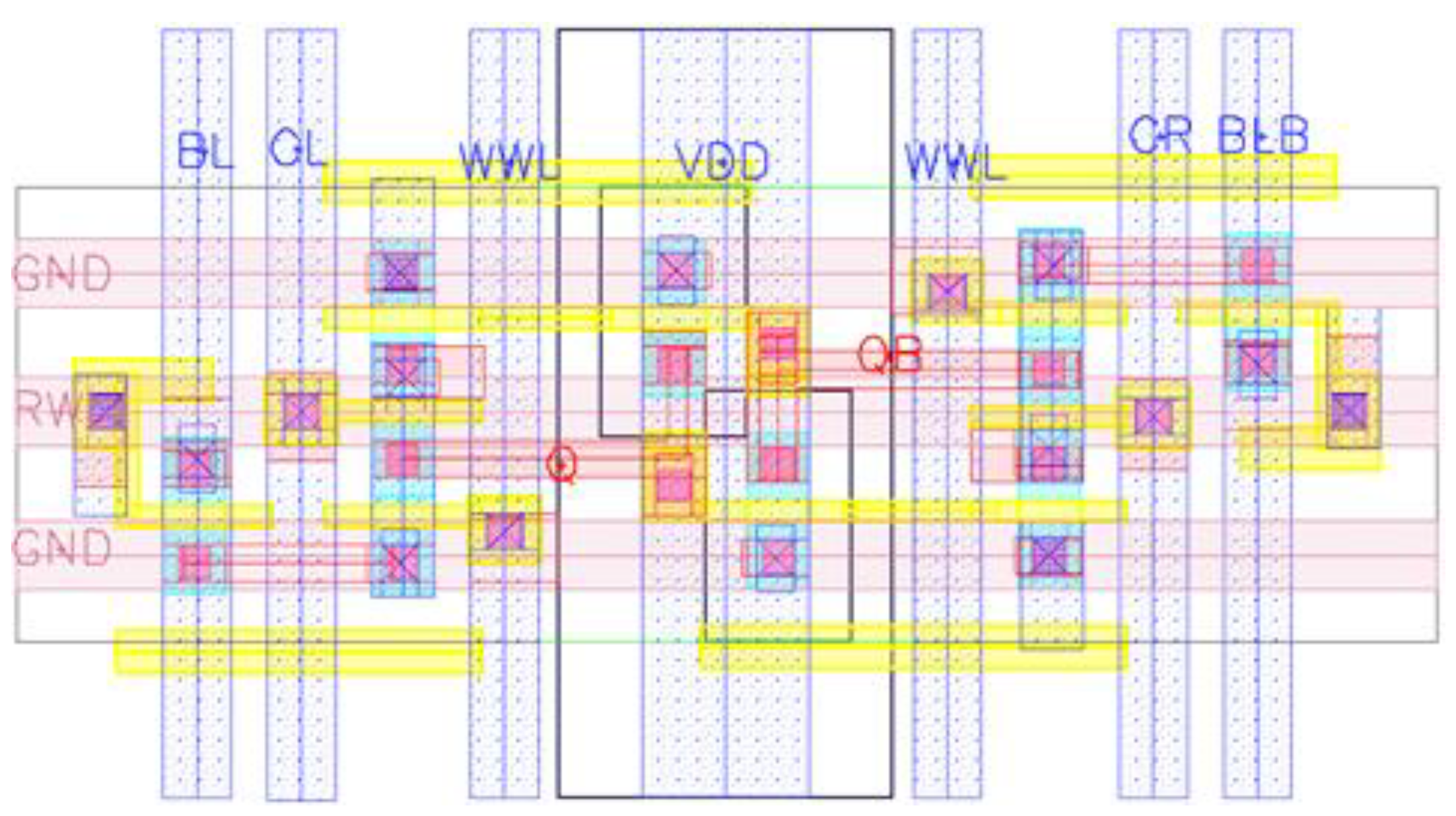

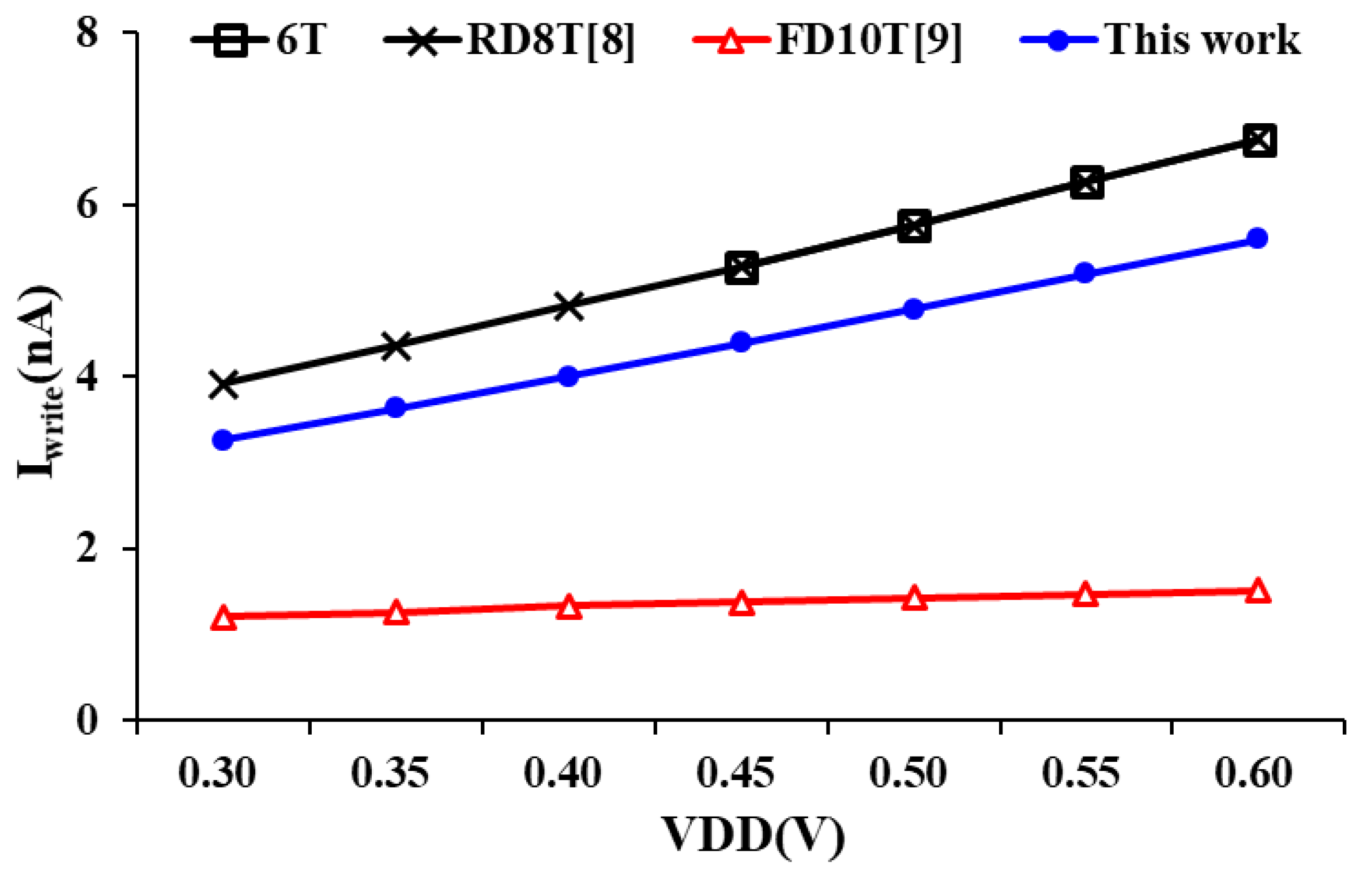

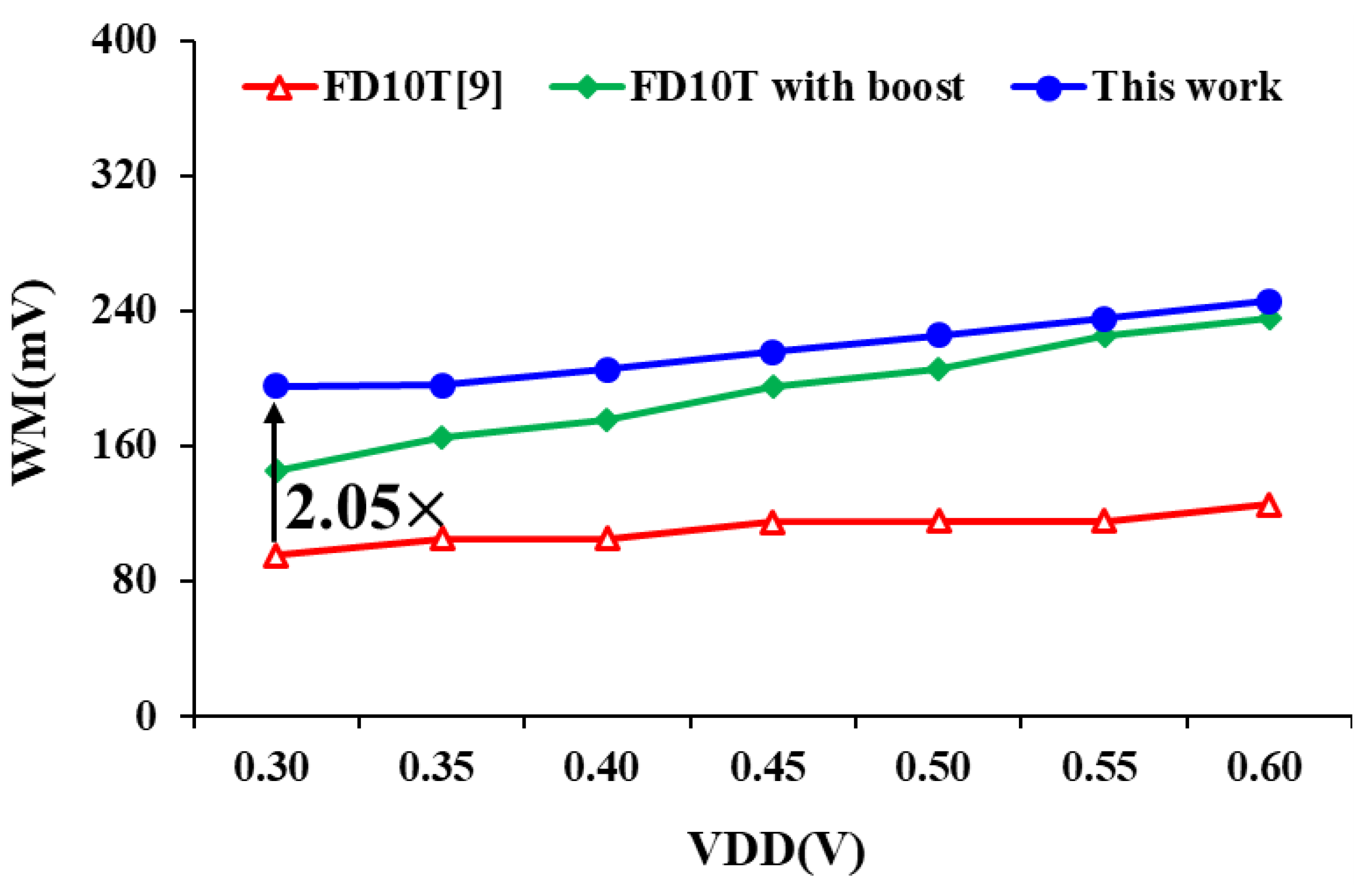

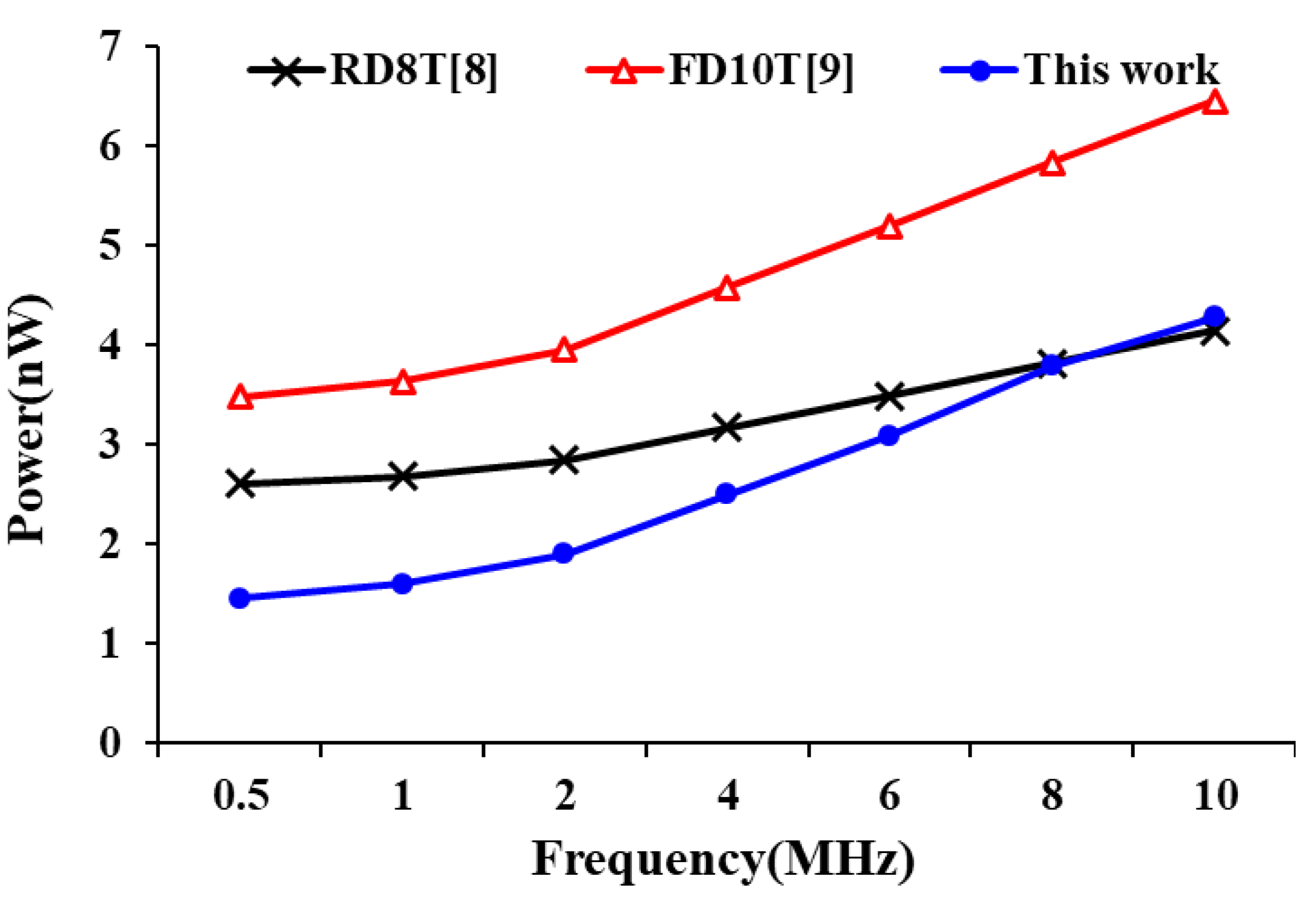

3. Layout Design and Simulation Results

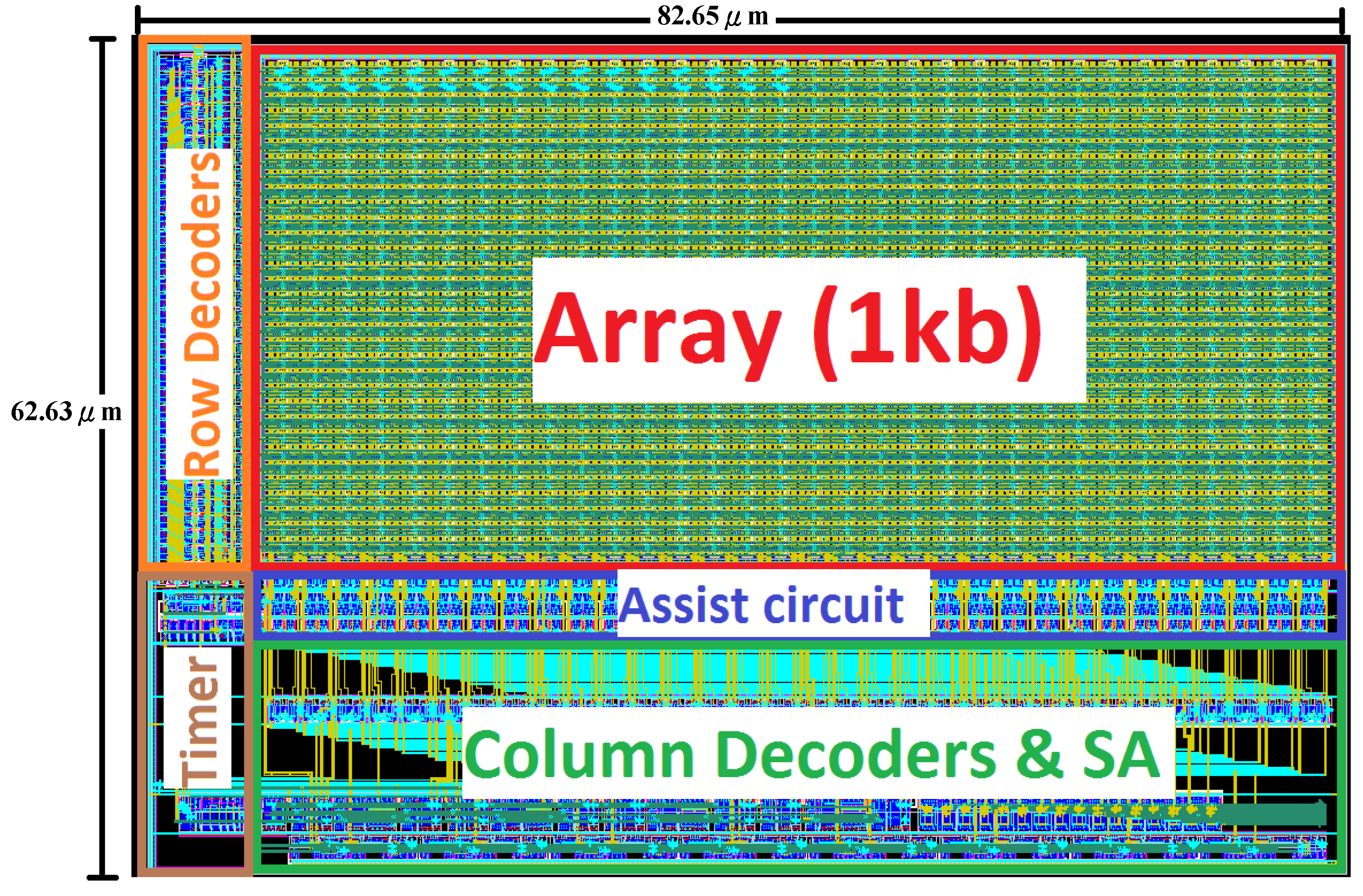

4. Chip Implementation

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Ahmad, S.; Gupta, M.K.; Alam, N.; Hasan, M. Single-Ended Schmitt-Trigger-Based Robust Low-Power SRAM Cell. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2634–2642. [Google Scholar] [CrossRef]

- Yadav, N.; Shah, A.P.; Vishvakarma, S.K. Stable, Reliable, and Bit-Interleaving 12T SRAM for Space Applications: A Device Circuit Co-Design. IEEE Trans. Semiconduct. Manuf. 2017, 30, 276–284. [Google Scholar] [CrossRef]

- Choi, W.; Park, J. A charge-recycling assist technique for reliable and low power SRAM design. IEEE Trans. Circuits Syst. I Regul. Papers 2016, 63, 1164–1175. [Google Scholar] [CrossRef]

- Zhang, K.; Bhattacharya, U.; Chen, Z.; Hamzaoglu, F.; Murray, D.; Vallepalli, N.; Wang, Y.; Zheng, B.; Bohr, M. A 3-GHz 70-Mb SRAM in 65-nm CMOS technology with integrated column-based dynamic power supply. IEEE J. Solid-State Circuits 2006, 41, 146–151. [Google Scholar] [CrossRef]

- Kushwah, C.B.; Vishvakarma, S.K. A Single-Ended with Dynamic Feedback Control 8T Subthreshold SRAM Cell. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 373–377. [Google Scholar] [CrossRef]

- Chuang, C.T.; Mukhopadhyay, S.; Kim, J.-J.; Kim, K.; Rao, R. High-performance SRAM in nanoscale CMOS: Design challenges and techniques. In Proceedings of the 2007 IEEE International Workshop on Memory Technology, Design and Testing, Taipei, Taiwan, 3–5 December 2007; pp. 4–12. [Google Scholar]

- Sheu, M.H.; Morsalin, S.M.S.; Tsai, C.M.; Yang, C.J.; Hsia, S.C.; Hsueh, Y.H.; Lin, J.F.; Chang, C.Y. Stable Local Bit-Line 6 T SRAM Architecture Design for Low-Voltage Operation and Access Enhancement. Electronics 2021, 10, 685. [Google Scholar] [CrossRef]

- Chang, L.; Montoye, R.K.; Nakamura, Y.; Batson, K.A.; Eickemeyer, R.J.; Dennard, R.H.; Haensch, W.; Jamsek, D. An 8T-SRAM for variability tolerance and low-voltage operation in high-performance caches. IEEE J. Solid-State Circuits 2008, 43, 956–963. [Google Scholar] [CrossRef]

- Chang, I.J.; Kim, J.J.; Park, S.P.; Roy, K. A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. IEEE J. Solid-State Circuits 2009, 44, 650–658. [Google Scholar] [CrossRef] [Green Version]

- Chiu, Y.W.; Hu, Y.H. 40 nm bit-interleaving 12T subthreshold SRAM with data-aware write-assist. IEEE Trans. Circuits Syst. I Regul. Papers 2014, 61, 2578–2585. [Google Scholar] [CrossRef]

- Chien, Y.C.; Wang, J.S. A 0.2 V 32-Kb 10T SRAM with 41 nW Standby Power for IoT Applications. IEEE Trans. Circuits Syst. I Regul. Papers 2018, 65, 2443–2454. [Google Scholar] [CrossRef]

- Pal, S.; Bose, S.; Ki, W.; Islam, A. Half-Select-Free Low-Power Dynamic Loop-Cutting Write Assist SRAM Cell for Space Applications. IEEE Trans. Electron. Dev. 2020, 67, 80–89. [Google Scholar] [CrossRef]

- Chang, M.H.; Chiu, Y.T.; Hwang, W. Design and Iso-Area Vmin Analysis of 9T Subthreshold SRAM With Bit-Interleaving Scheme in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Br. 2012, 59, 429–433. [Google Scholar] [CrossRef] [Green Version]

- Tu, M.H.; Lin, J.-Y.; Tsai, M.-C.; Lu, C.-Y.; Lin, Y.-J.; Wang, M.-H.; Huang, H.-S.; Lee, K.-D.; Shih, W.-C.; Jou, S.-J.; et al. A single-ended disturb-free 9T subthreshold SRAM with cross-point data-aware write word-line structure, negative bit-line, and adaptive read operation timing tracing. IEEE J. Solid-State Circuits 2012, 47, 1469–1482. [Google Scholar] [CrossRef] [Green Version]

- Pal, S.; Bose, S.; Ki, W.H. A highly stable reliable SRAM cell design for low power applications. Microelectron. Reliab. 2020, 105, 113503. [Google Scholar] [CrossRef]

- Song, T.; Jung, J.; Rim, W.; Kim, H.; Kim, Y.; Park, C.; Do, J.; Park, S.; Cho, S.; Jung, H.; et al. A 7nm FinFET SRAM using EUV lithography with dual write-driver-assist circuitry for low-voltage applications. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 198–200. [Google Scholar]

- Chang, T.Y.J.; Chen, Y.-H.; Chan, W.-M.; Cheng, H.; Wang, P.-S.; Lin, Y.; Fujiwara, H.; Lee, R.; Liao, H.-J.; Wang, P.-W.; et al. A 5-nm 135-Mb SRAM in EUV and High-Mobility Channel FinFET Technology With Metal Coupling and Charge-Sharing Write-Assist Circuitry Schemes for High-Density and Low-V MIN Applications. IEEE J. Solid-State Circuits 2020, 56, 179–187. [Google Scholar] [CrossRef]

- Guo, Z.; Wiedemer, J.; Kim, Y.; Ramamoorthy, P.S.; Sathyaprasad, P.B.; Shridharan, S.; Kim, D.; Karl, E. 10nm SRAM Design using Gate-Modulated Self-Collapse Write Assist Enabling 175mV VMIN Reduction with Negligible Active Power Overhead. IEEE Solid-State Circuits Lett. 2021, 4, 6–9. [Google Scholar] [CrossRef]

- Cho, K.; Park, J.; Oh, T.W.; Jung, S.O. One-Sided Schmitt-Trigger-Based 9T SRAM Cell for Near-Threshold Operation. IEEE Trans. Circuits Syst. I Regul. Papers 2020, 67, 1551–1561. [Google Scholar] [CrossRef]

- Lu, C.Y.; Chuang, C.-T.; Jou, S.-J.; Tu, M.-H.; Wu, Y.-P.; Huang, C.-P.; Kan, P.-S.; Huang, H.-S.; Lee, K.-D.; Kao, Y.-S. A 0.325 V, 600-kHz, 40-nm 72-kb 9T subthreshold SRAM with aligned boosted write wordline and negative write bitline write-assist. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 23, 958–962. [Google Scholar] [CrossRef]

- Sinangil, M.E.; Lin, Y.T.; Liao, H.J.; Chang, J. A 290-mV, 7-nm Ultra-Low-Voltage One-Port SRAM Compiler Design Using a 12T Write Contention and Read Upset Free Bit-Cell. IEEE J. Solid-State Circuits 2019, 54, 1152–1160. [Google Scholar] [CrossRef]

- Sinangil, M.E.; Mair, H.; Chandrakasan, A.P. A 28nm high-density 6T SRAM with optimized peripheral-assist circuits for operation down to 0.6V. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 260–262. [Google Scholar]

| Hold | Read | Write-0 | Write-1 | |

|---|---|---|---|---|

| Write_EN | 0 | 0 | 1 | 1 |

| BL/BLB | 1/1 | 1/1 (floating) | 0/1 | 1/0 |

| RWL | 0 | 1 | 1 | 1 |

| WWL | 0 | 0 | 1 | 1 |

| CL/CR | 1/1 | Pulse | 1/0 | 0/1 |

| Characteristics | 6T [22] | FD10T [9] | DFL10T [11] | PCA12T [10] | Proposed10T |

|---|---|---|---|---|---|

| Process | 28 nm | 90 nm | 28 nm | 40 nmGP | 40 nmGP |

| Assist Scheme | Optimized Peripheral | WordLine boost | No necessary | DAPC | PCR + WDA |

| VDDMIN | 0.6 V | 160 mV | 250 mV | 350 mV | 300 mV |

| Capacity | 128-kb | 32-kb | 32-kb | 4-kb | 1-kb |

| Frequency @VDDMIN | 20 MHz | 500 Hz | 30 kHz | 11.5 MHz | 10 MHz |

| Read Power (μW) | 2800 | 0.123 | 0.088 | 22.0 | 4.15 |

| Write Power (μW) | 0.087 | 3.82 | |||

| Energy/Access (pJ) | 140 | 246 | 2.92 | 1.91 | 0.39 |

| Leakage Power (μW) | N/A | 0.36 @ 6 °C | 0.05 *1 | 17.38 | 3.64 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sheu, M.-H.; Tsai, C.-M.; Tsai, M.-Y.; Hsia, S.-C.; Morsalin, S.M.S.; Lin, J.-F. A 0.3 V PNN Based 10T SRAM with Pulse Control Based Read-Assist and Write Data-Aware Schemes for Low Power Applications. Sensors 2021, 21, 6591. https://doi.org/10.3390/s21196591

Sheu M-H, Tsai C-M, Tsai M-Y, Hsia S-C, Morsalin SMS, Lin J-F. A 0.3 V PNN Based 10T SRAM with Pulse Control Based Read-Assist and Write Data-Aware Schemes for Low Power Applications. Sensors. 2021; 21(19):6591. https://doi.org/10.3390/s21196591

Chicago/Turabian StyleSheu, Ming-Hwa, Chang-Ming Tsai, Ming-Yan Tsai, Shih-Chang Hsia, S. M. Salahuddin Morsalin, and Jin-Fa Lin. 2021. "A 0.3 V PNN Based 10T SRAM with Pulse Control Based Read-Assist and Write Data-Aware Schemes for Low Power Applications" Sensors 21, no. 19: 6591. https://doi.org/10.3390/s21196591

APA StyleSheu, M.-H., Tsai, C.-M., Tsai, M.-Y., Hsia, S.-C., Morsalin, S. M. S., & Lin, J.-F. (2021). A 0.3 V PNN Based 10T SRAM with Pulse Control Based Read-Assist and Write Data-Aware Schemes for Low Power Applications. Sensors, 21(19), 6591. https://doi.org/10.3390/s21196591