A 0.8 V, 5.3–5.9 GHz Sub-Sampling PLL with 196.5 fsrms Integrated Jitter and −251.6 dB FoM

Abstract

:1. Introduction

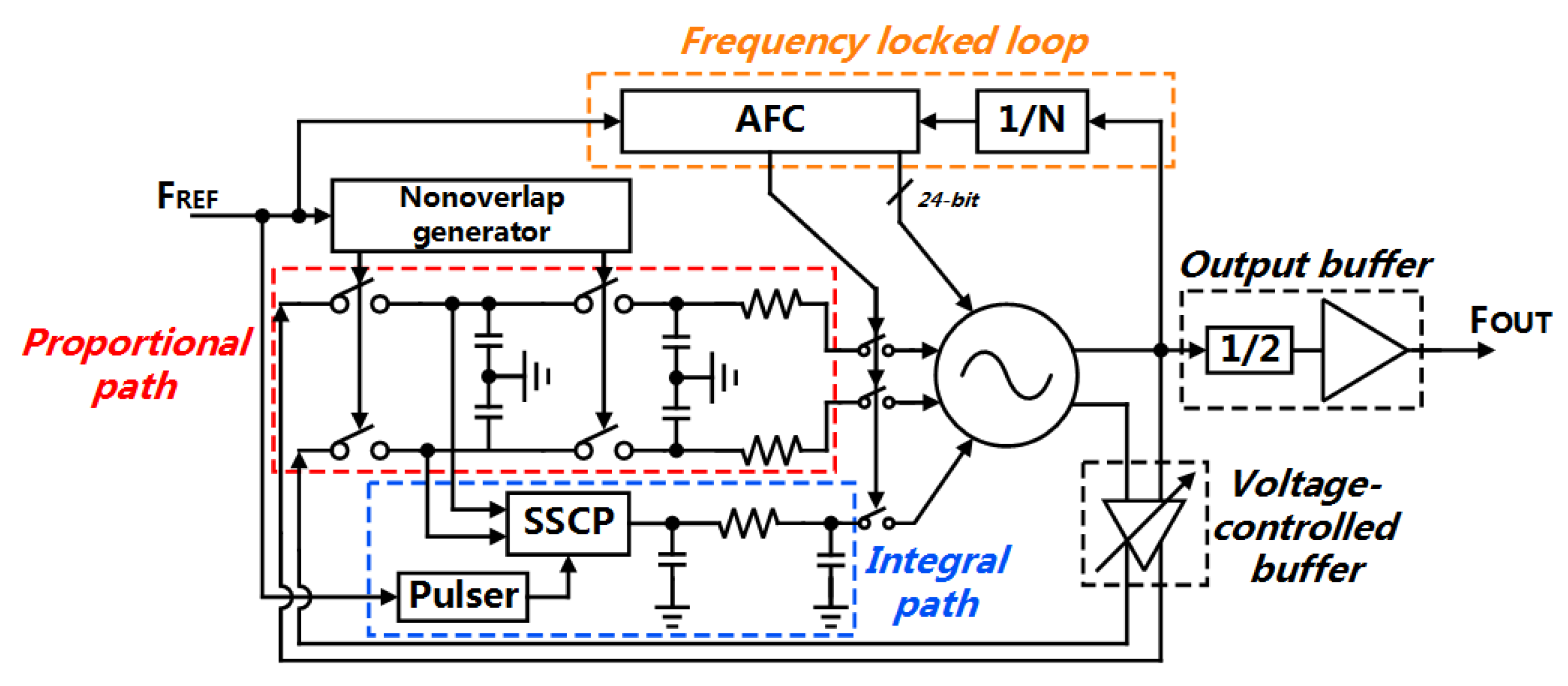

2. Architecture of Proposed SSPLL

2.1. Conceptual Block Diagram

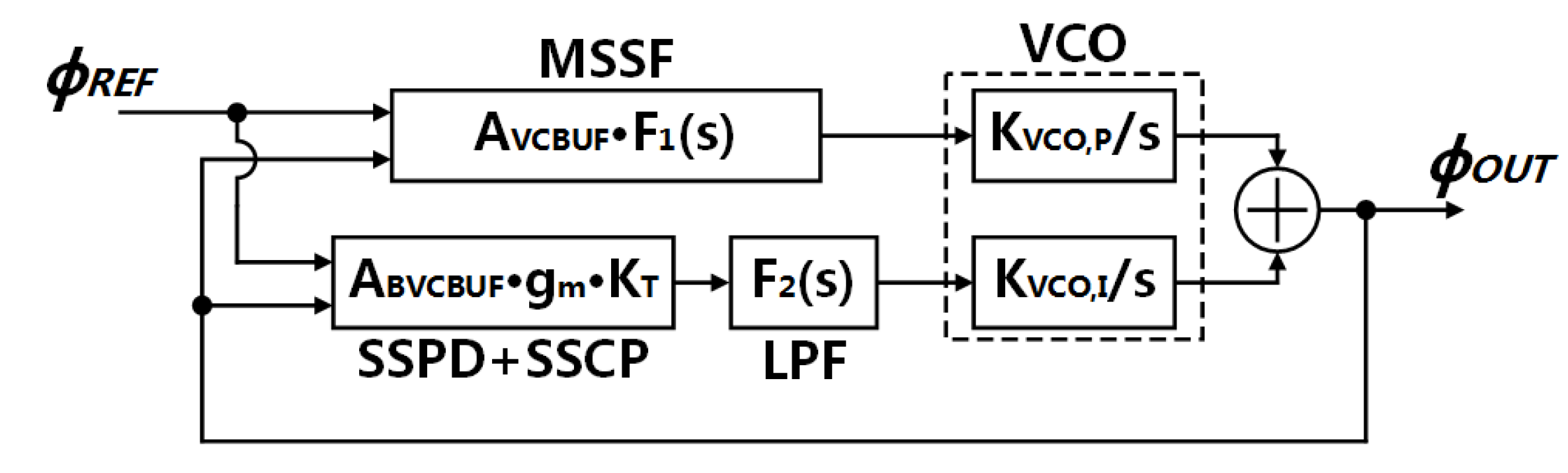

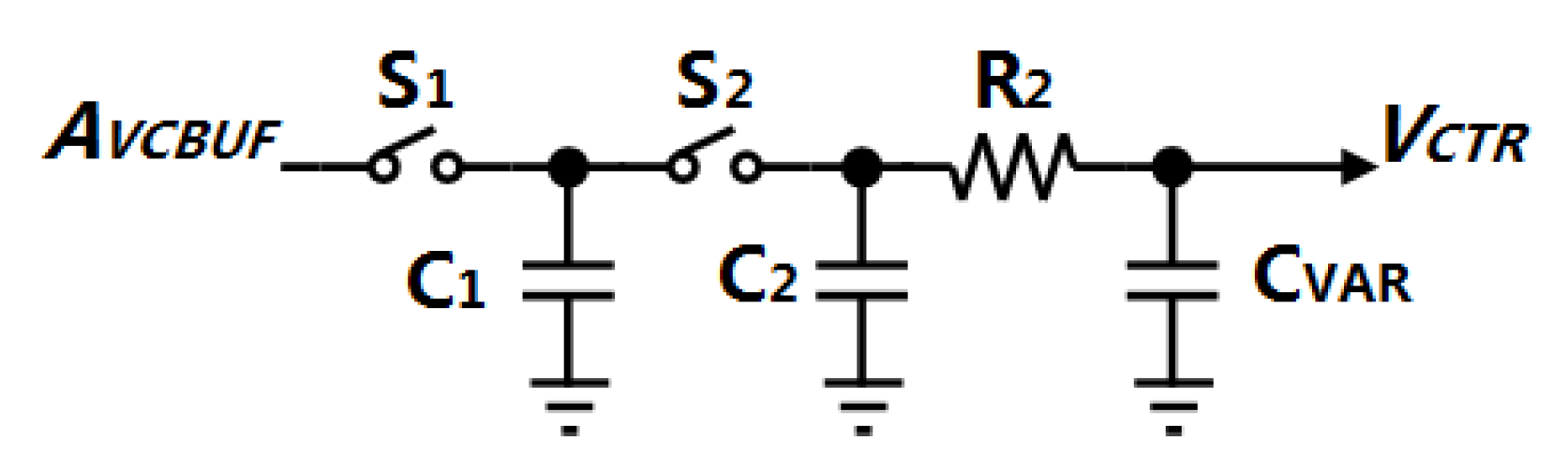

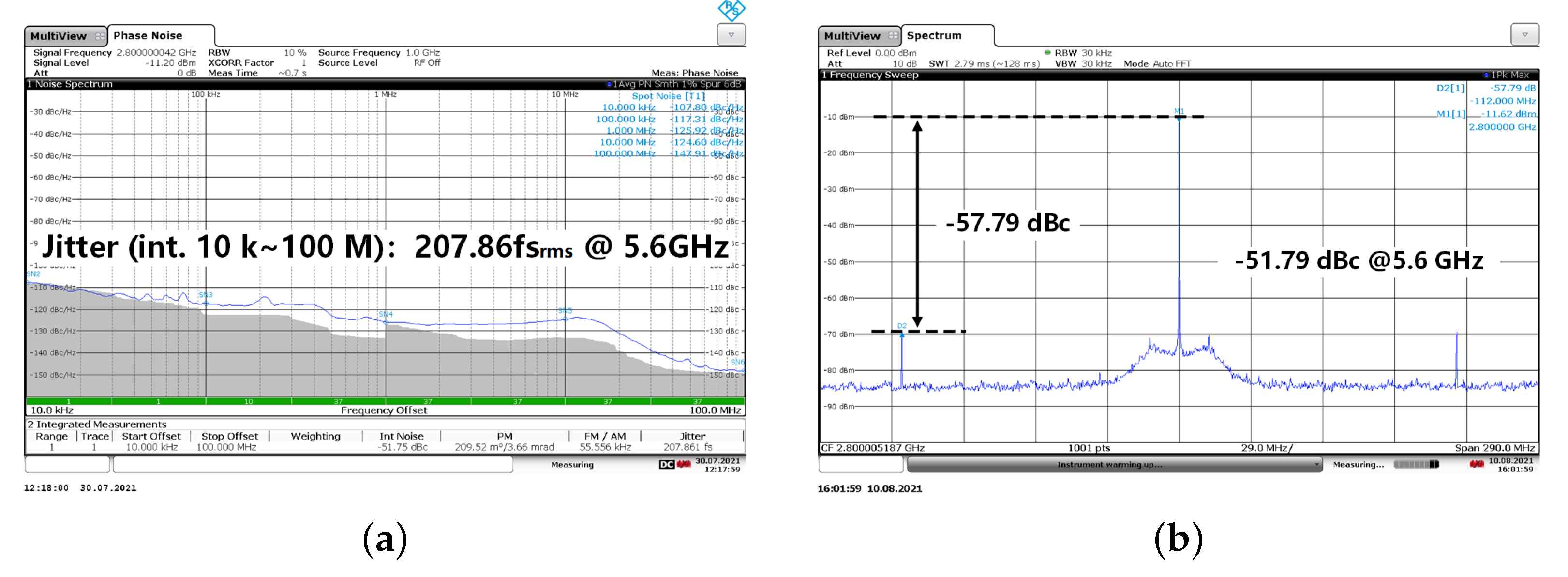

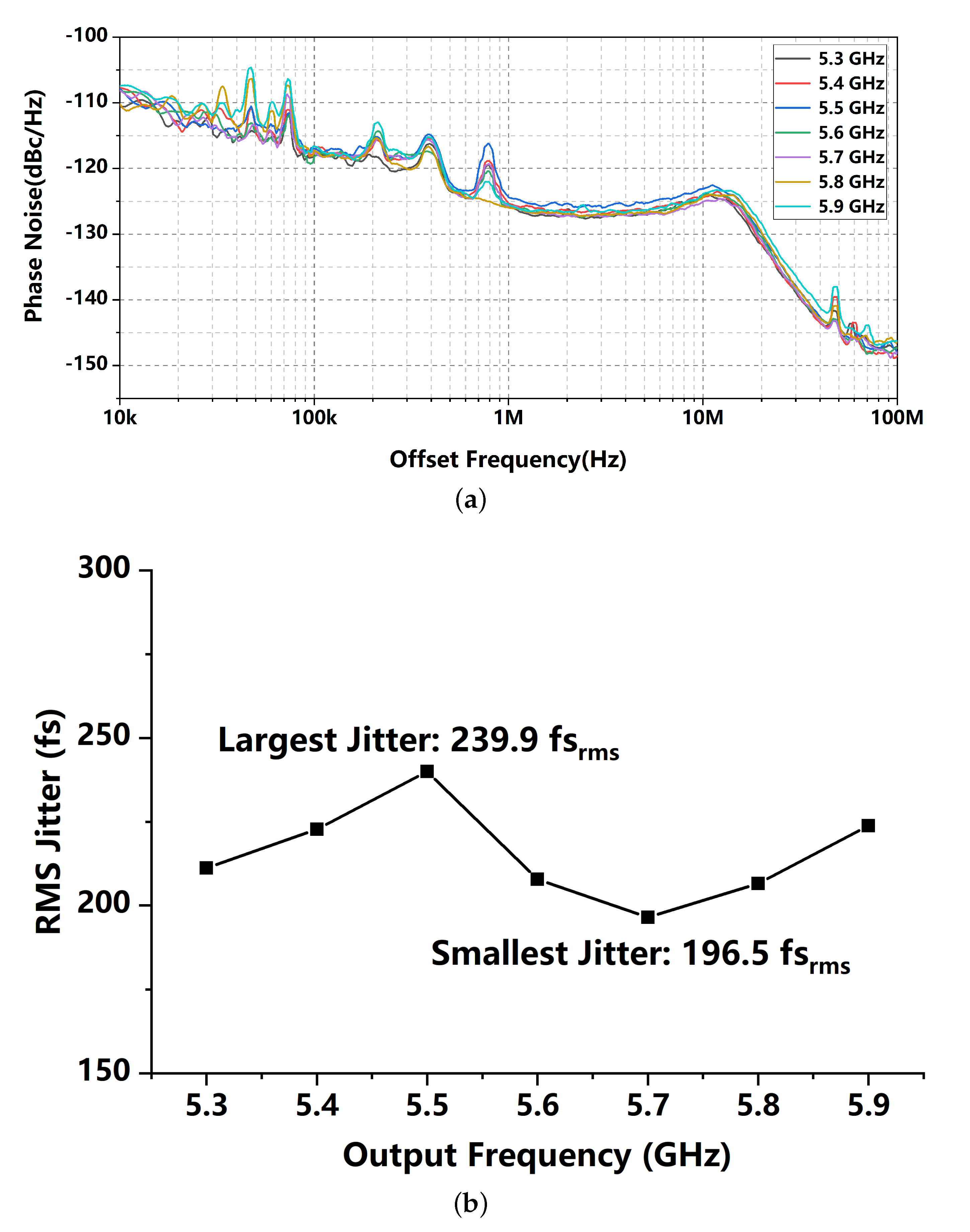

2.2. Loop Analysis

3. Circuit Implementation

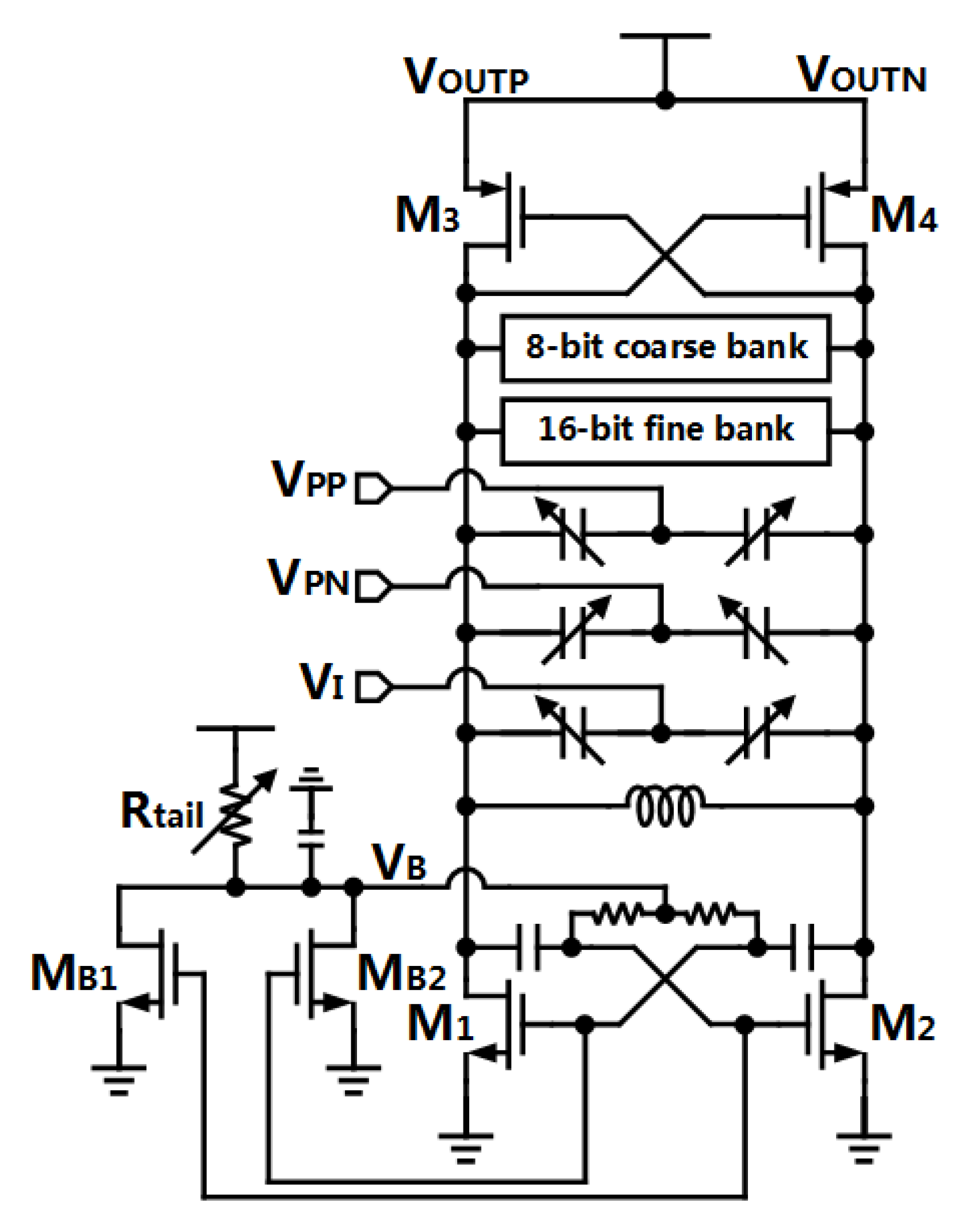

3.1. Class-C VCO with Start-Up Circuit

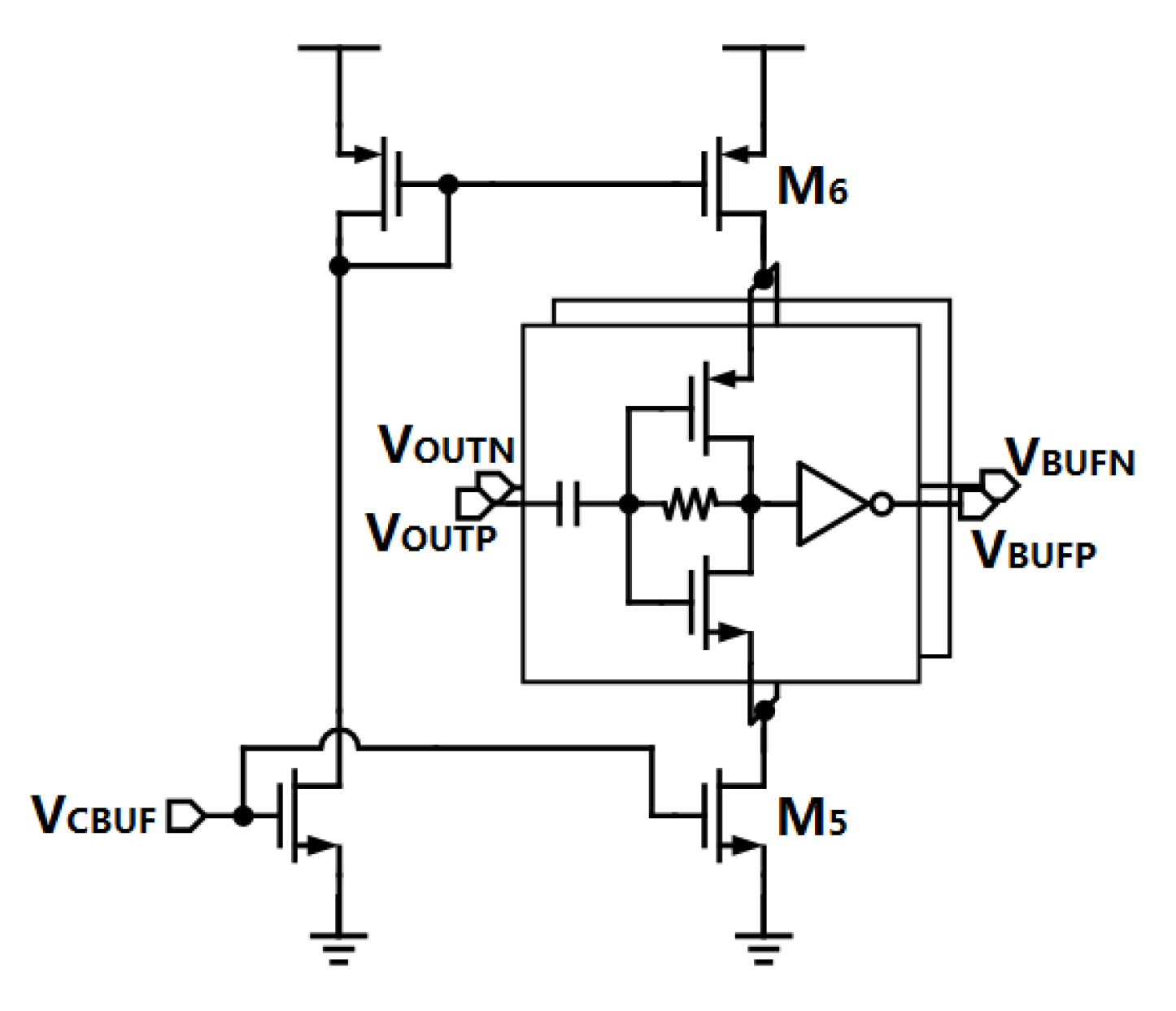

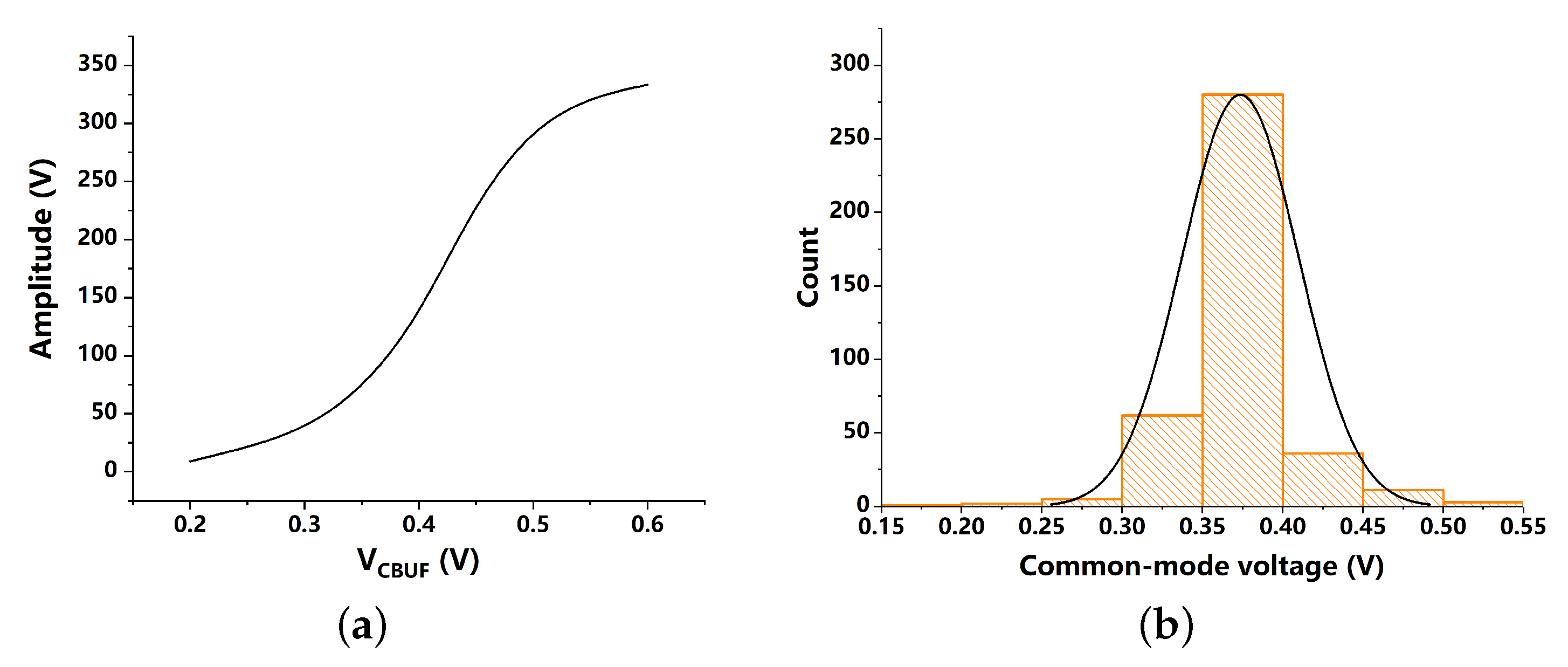

3.2. Voltage-Controlled Buffer

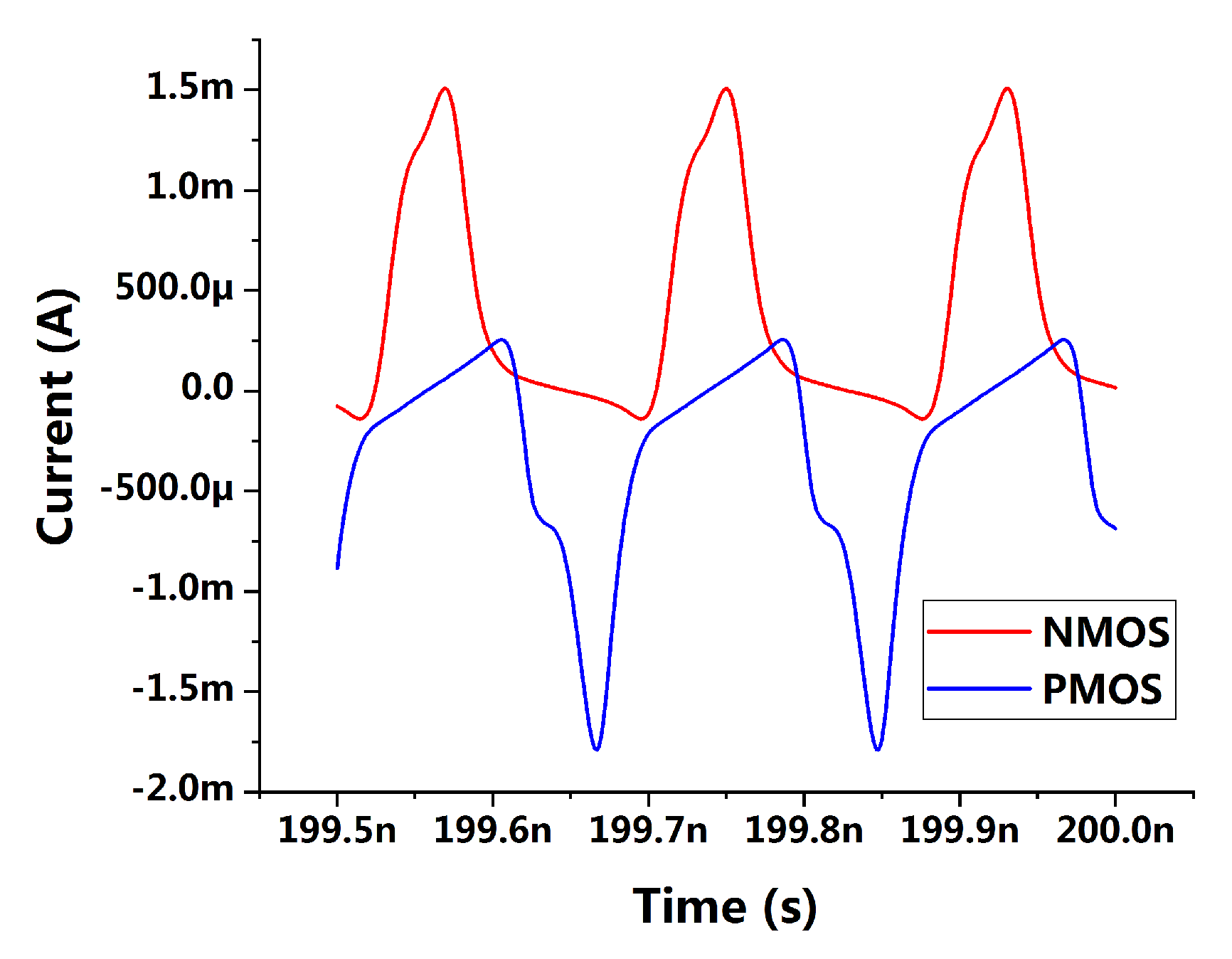

3.3. Rail-to-Rail Sub-Sampling Charge Pump

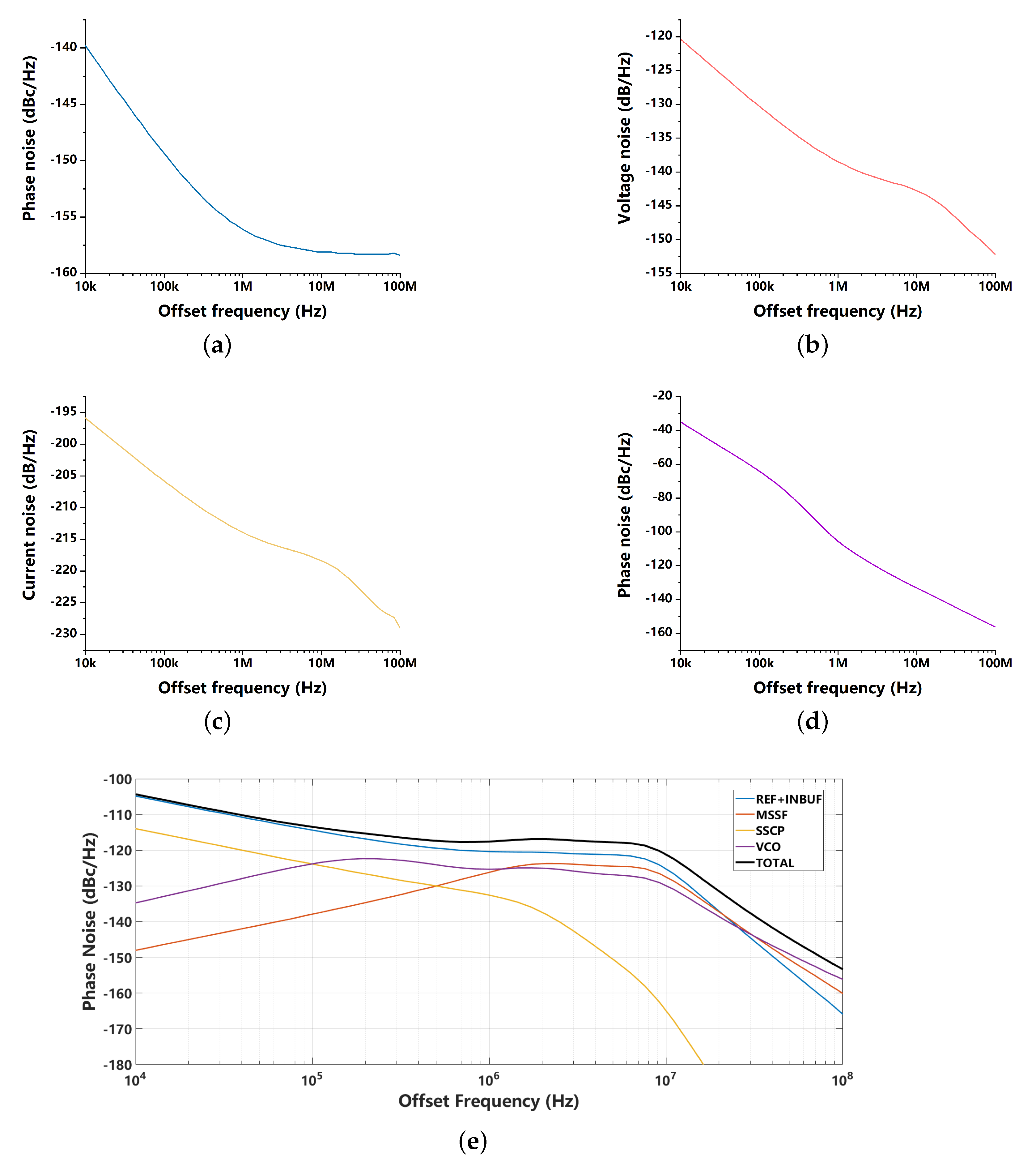

4. Phase Noise Analysis

5. Measurement Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Grebene, A.; Camenzind, H. Phase locking as a new approach for tuned integrated circuits. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, Philadelphia, PA, USA, 19–21 February 1969. [Google Scholar]

- Zhang, Z.; Yang, J.; Liu, L.; Feng, P.; Liu, J.; Wu, N. A 0.9–2.25-GHz Sub-0.2-mW/GHz Compact Low-Voltage Low-Power Hybrid Digital PLL with Loop Bandwidth-Tracking Technique. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 933–944. [Google Scholar] [CrossRef]

- Yin, W.; Inti, R.; Elshazly, A.; Young, B.; Hanumolu, P.K. A 0.7-to-3.5 GHz 0.6-to-2.8 mW Highly Digital Phase-Locked Loop with Bandwidth Tracking. IEEE J. Solid-State Circuits 2011, 46, 1870–1880. [Google Scholar] [CrossRef]

- Sun, Y.; Zhang, Z.; Xu, N.; Wang, M.; Rhee, W.; Oh, T.-Y.; Wang, Z. A 1.75 mW 1.1 GHz Semi-Digital Fractional-N PLL with TDC-Less Hybrid Loop Control. IEEE Microw. Wirel. Components Lett. 2012, 22, 654–656. [Google Scholar] [CrossRef]

- Zhang, Z.; Zhu, G.; Yue, C.P. A 0.65-V 12–16-GHz Sub-Sampling PLL with 56.4-fsrms Integrated Jitter and −256.4-dB FoM. IEEE J. Solid-State Circuits 2020, 55, 1665–1683. [Google Scholar] [CrossRef]

- Elkholy, A.; Talegaonkar, M.; Anand, T.; Hanumolu, P.K. A 6.75-to-8.25 GHz 2.25 mW 190 fsrms integrated-jitter PVT-insensitive injection-locked clock multiplier using all-digital continuous frequency-tracking loop in 65 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015. [Google Scholar]

- Gao, X.; Klumperink, E.; Socci, G.; Bohsali, M.; Nauta, B. A 2.2 GHz sub-sampling PLL with 0.16 psrms jitter and −125 dBc/Hz in-band phase noise at 700 μW loop-components power. In Proceedings of the Symposium on VLSI Circuits, Honolulu, HI, USA, 16–18 June 2010. [Google Scholar]

- Liu, H.; Sun, Z.; Huang, H.; Deng, W.; Siriburanon, T.; Pang, J.; Wang, Y.; Wu, R.; Someya, T.; Shirane, A.; et al. A 265-μW Fractional-N Digital PLL with Seamless Automatic Switching Sub-Sampling/Sampling Feedback Path and Duty-Cycled Frequency-Locked Loop in 65-nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 3478–3492. [Google Scholar] [CrossRef]

- van de Beek, R.C.; Vaucher, C.S.; Leenaerts, D.M.; Klumperink, E.A.; Nauta, B. A 2.5–10-GHz Clock Multiplier Unit with 0.22-ps RMS Jitter in Standard 0.18-μm CMOS. IEEE J. Solid-State Circuits 2004, 39, 1862–1872. [Google Scholar] [CrossRef]

- Nonis, R.; Da Dalt, N.; Palestri, P.; Selmi, L. Modeling, design and characterization of a new low-jitter analog dual tuning LC-VCO PLL architecture. IEEE J. Solid-State Circuits 2005, 40, 1303–1309. [Google Scholar] [CrossRef]

- Gu, R.; Yee, A.-L.; Xie, Y.; Lee, W. A 6.25GHz 1V LC-PLL in 0.13 μm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 6–9 February 2006. [Google Scholar]

- Ding, Y.; Kenneth, K.O. A 21-GHz 8-Modulus prescaler and a 20-GHz phase-locked loop fabricated in 130-nm CMOS. IEEE J. Solid-State Circuits 2007, 42, 1240–1249. [Google Scholar] [CrossRef]

- Turker, D.; Bekele, A.; Upadhyaya, P.; Verbruggen, B.; Cao, Y.; Ma, S.; Erdmann, C.; Farley, B.; Frans, Y.; Chang, K. A 7.4-to-14 GHz PLL with 54 fsrms jitter in 16 nm FinFET for integrated RF-data-converter SoCs. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2018. [Google Scholar]

- Ahmadi, M.R.; Pi, D.; Çatlı, B.; Singh, U.; Zhang, B.; Huang, Z.; Momtaz, A.; Cao, J. A 288 fs RMS jitter versatile 8–12.4 GHz wide-band Fractional-N synthesizer for SONET and SerDes communication standards in 40 nm CMOS. In Proceedings of the Symposium on VLSI Circuits, Kyoto, Japan, 12–14 June 2013. [Google Scholar]

- Song, F.; Zhao, Y.; Wu, B.; Tang, L.; Lin, L.; Razavi, B. A Fractional-N Synthesizer with 110 fsrms Jitter and a Reference Quadrupler for Wideband 802.11ax. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2019. [Google Scholar]

- Andreani, P.; Fard, A. More on the 1/f2 Phase Noise Performance of CMOS Differential-Pair LC-Tank Oscillators. IEEE J. Solid-State Circuits 2006, 41, 2703–2712. [Google Scholar] [CrossRef] [Green Version]

- Ham, D.; Hajimiri, A. Concepts and methods in optimization of integrated LC VCOs. IEEE J. Solid-State Circuits 2001, 36, 896–909. [Google Scholar] [CrossRef] [Green Version]

- Hegazi, E.; Sjöland, H.; Abidi, A.A. A filtering technique to lower LC oscillator phase noise. IEEE J. Solid-State Circuits 2001, 36, 1921–1930. [Google Scholar] [CrossRef] [Green Version]

- Aspemyr, L.; Linten, D. An Ultra Low Voltage, Low Power, Fully Integrated VCO for GPS in 90 nm RF-CMOS. Analog Integr. Circuits Signal Process. 2006, 46, 57–63. [Google Scholar] [CrossRef]

- Hsieh, H.-H.; Lu, L.-H. A High-Performance CMOS Voltage-Controlled Oscillator for Ultra-Low-Voltage Operations. IEEE Trans. Microw. Theory Tech. 2007, 55, 467–473. [Google Scholar] [CrossRef]

- Kwok, K.; Luong, H.C. Ultra-low-Voltage high-performance CMOS VCOs using transformer feedback. IEEE J. Solid-State Circuits 2005, 40, 652–660. [Google Scholar] [CrossRef]

- Gao, X.; Klumperink, E.A.; Bohsali, M.; Nauta, B. A Low Noise Sub-Sampling PLL in Which Divider Noise is Eliminated and PD/CP Noise is Not Multiplied by N2. IEEE J. Solid-State Circuits 2009, 44, 3253–3263. [Google Scholar] [CrossRef] [Green Version]

- Raj, M.; Bekele, A.; Turker, D.; Upadhyaya, P.; Frans, Y.; Chang, K. A 164 fsrms 9-to-18 GHz sampling phase detector based PLL with in-band noise suppression and robust frequency acquisition in 16 nm FinFET. In Proceedings of the Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017. [Google Scholar]

- Liu, M.; Ma, R.; Liu, S.; Ding, Z.; Zhang, P.; Zhu, Z. A 5-GHz Low-Power Low-Noise Integer-N Digital Subsampling PLL with SAR ADC PD. IEEE Trans. Microw. Theory Tech. 2018, 66, 4078–4087. [Google Scholar] [CrossRef]

- Kong, L.; Razavi, B. A 2.4 GHz 4 mW inductorless RF synthesizer. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015. [Google Scholar]

- Gao, X.; Klumperink, E.A.; Geraedts, P.F.; Nauta, B. Jitter Analysis and a Benchmarking Figure-of-Merit for Phase-Locked Loops. IEEE Trans. Circuits Syst. II Express Briefs 2009, 56, 117–121. [Google Scholar]

- Koo, Y.; Huh, H.; Cho, Y.; Lee, J.; Park, J.; Lee, K.; Jeong, D.; Kim, W. A fully integrated CMOS frequency synthesizer with charge-averaging charge pump and dual-path loop filter for PCS- and cellular-CDMA wireless systems. IEEE J. Solid-State Circuits 2002, 37, 536–542. [Google Scholar]

- Gardner, F.M. Charge-Pump Phase-Lock Loops. IEEE Trans. Commun. 1980, 28, 1849–1858. [Google Scholar] [CrossRef]

- Fanori, L.; Andreani, P. A high-swing complementary class-C VCO. In Proceedings of the European Conference on Solid-State Circuits, Bucharest, Romania, 16–20 September 2013. [Google Scholar]

| Tech. (nm) | Supply (V) | Out Freq. (GHz) | Ref. Freq. (MHz) | Ref. Spur (dBc) | RMS Jitter (fs) | Power (mW) | FoM (dB) | |

|---|---|---|---|---|---|---|---|---|

| This work | 40 | 0.8 | 5.6 | 112 | −51.8 | 196.5 (10 k–100 M) | 1.8 | −251.6 |

| [6] | 65 | 0.9 | 6.8 | 106.25 | −40 | 190 (10 k–100 M) | 2.25 | −251 |

| [8] | 65 | 0.45 | 2.4 | 10 | −50.1 | 2800 (1 k–100 M) | 0.265 | −236.8 |

| [15] | 28 | - | 7.77 | 80 | −66.4 | 82 (10 k–10 M) | 14.7 | −250 |

| [23] | 16 | 0.9/1.8 | 18 | 450 | - | 164 (1 k–10 M) | 29.2 | −241 |

| [24] | 65 | 1.2 | 5 | 50 | −77 | 357 (10 k–10 M) | 3.9 | −243 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zuo, S.; Zhao, J.; Zhou, Y. A 0.8 V, 5.3–5.9 GHz Sub-Sampling PLL with 196.5 fsrms Integrated Jitter and −251.6 dB FoM. Sensors 2021, 21, 7648. https://doi.org/10.3390/s21227648

Zuo S, Zhao J, Zhou Y. A 0.8 V, 5.3–5.9 GHz Sub-Sampling PLL with 196.5 fsrms Integrated Jitter and −251.6 dB FoM. Sensors. 2021; 21(22):7648. https://doi.org/10.3390/s21227648

Chicago/Turabian StyleZuo, Shi, Jianzhong Zhao, and Yumei Zhou. 2021. "A 0.8 V, 5.3–5.9 GHz Sub-Sampling PLL with 196.5 fsrms Integrated Jitter and −251.6 dB FoM" Sensors 21, no. 22: 7648. https://doi.org/10.3390/s21227648