Highly Configurable 100 Channel Recording and Stimulating Integrated Circuit for Biomedical Experiments

Abstract

:1. Introduction

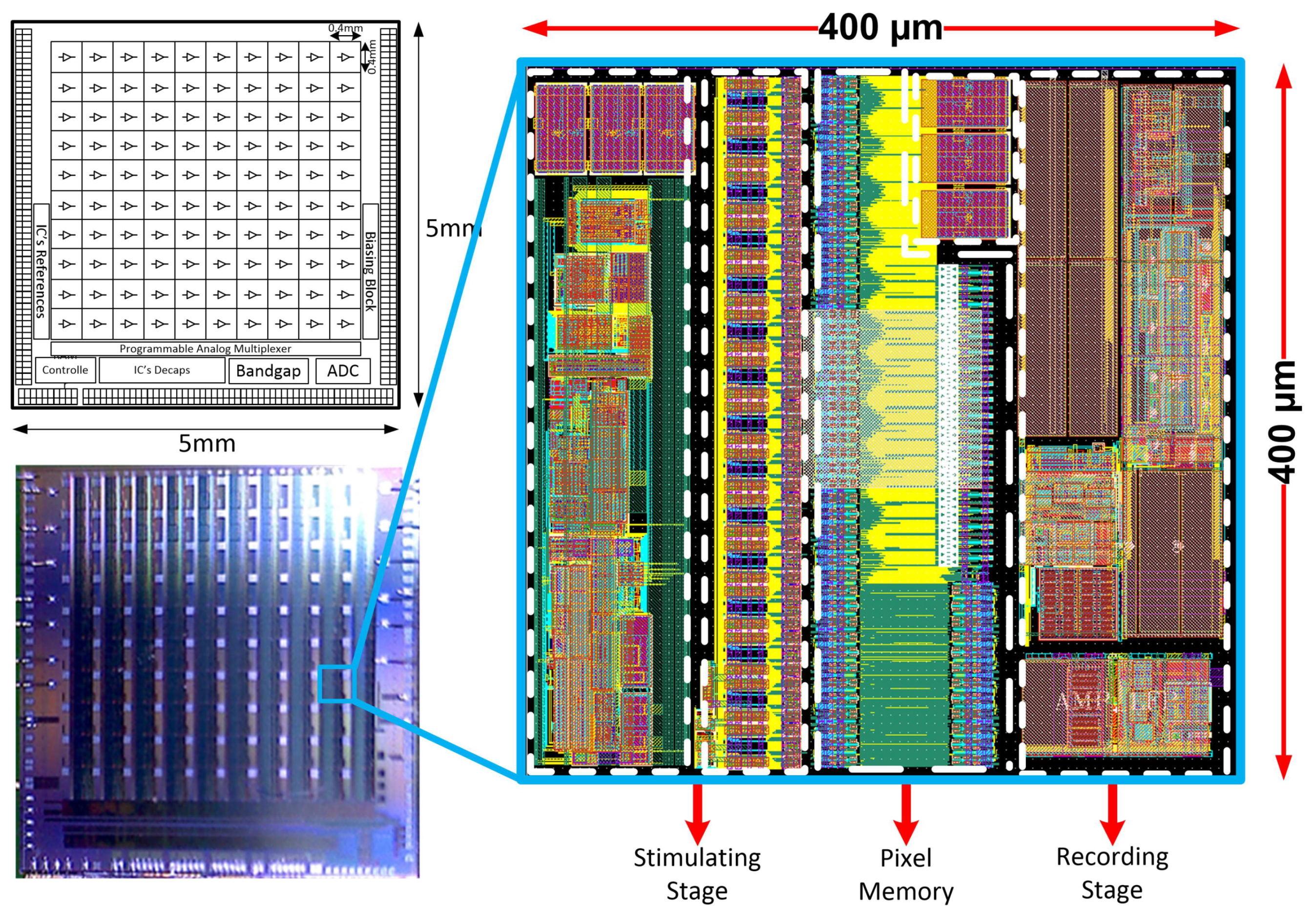

2. IC Architecture

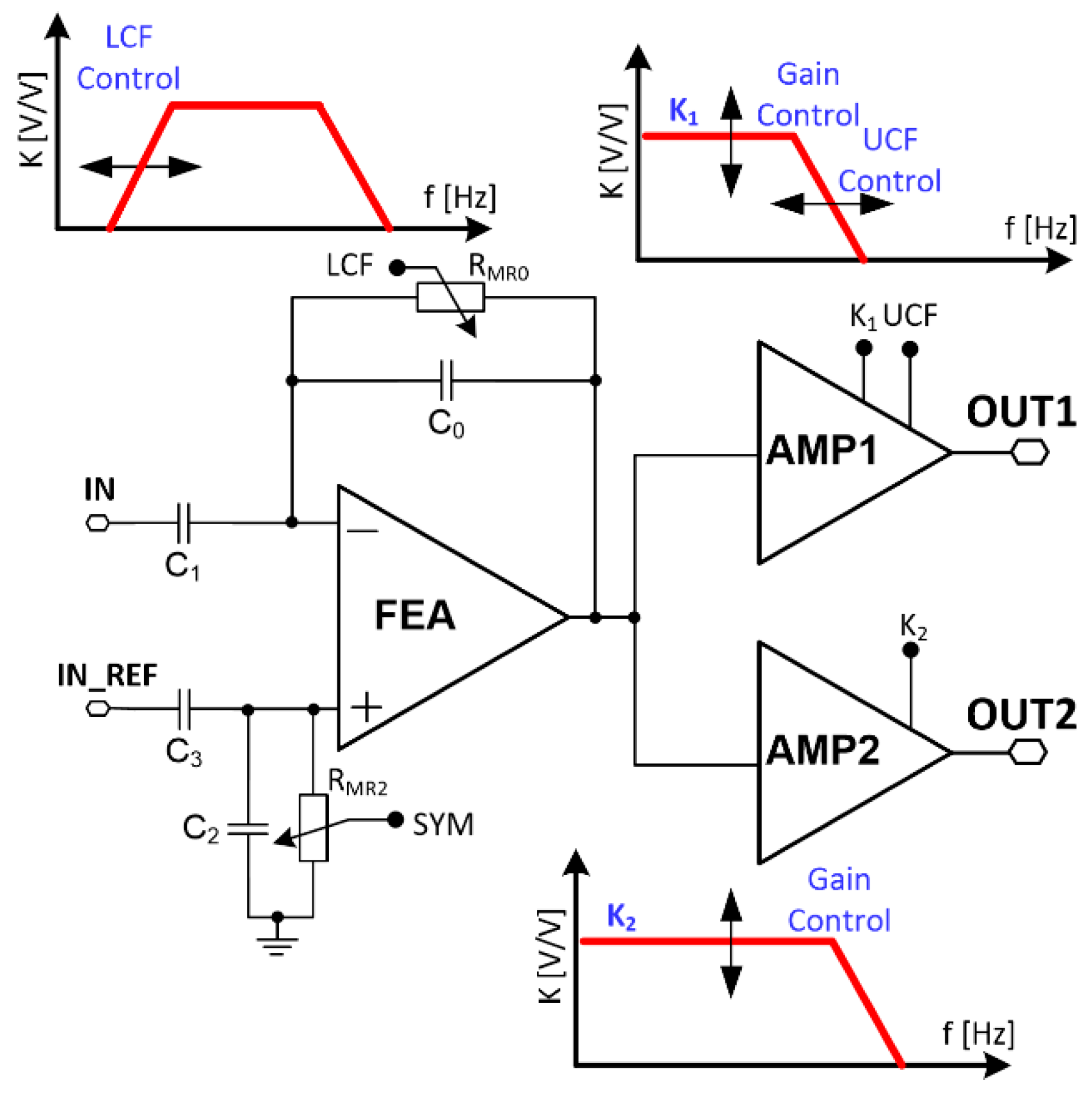

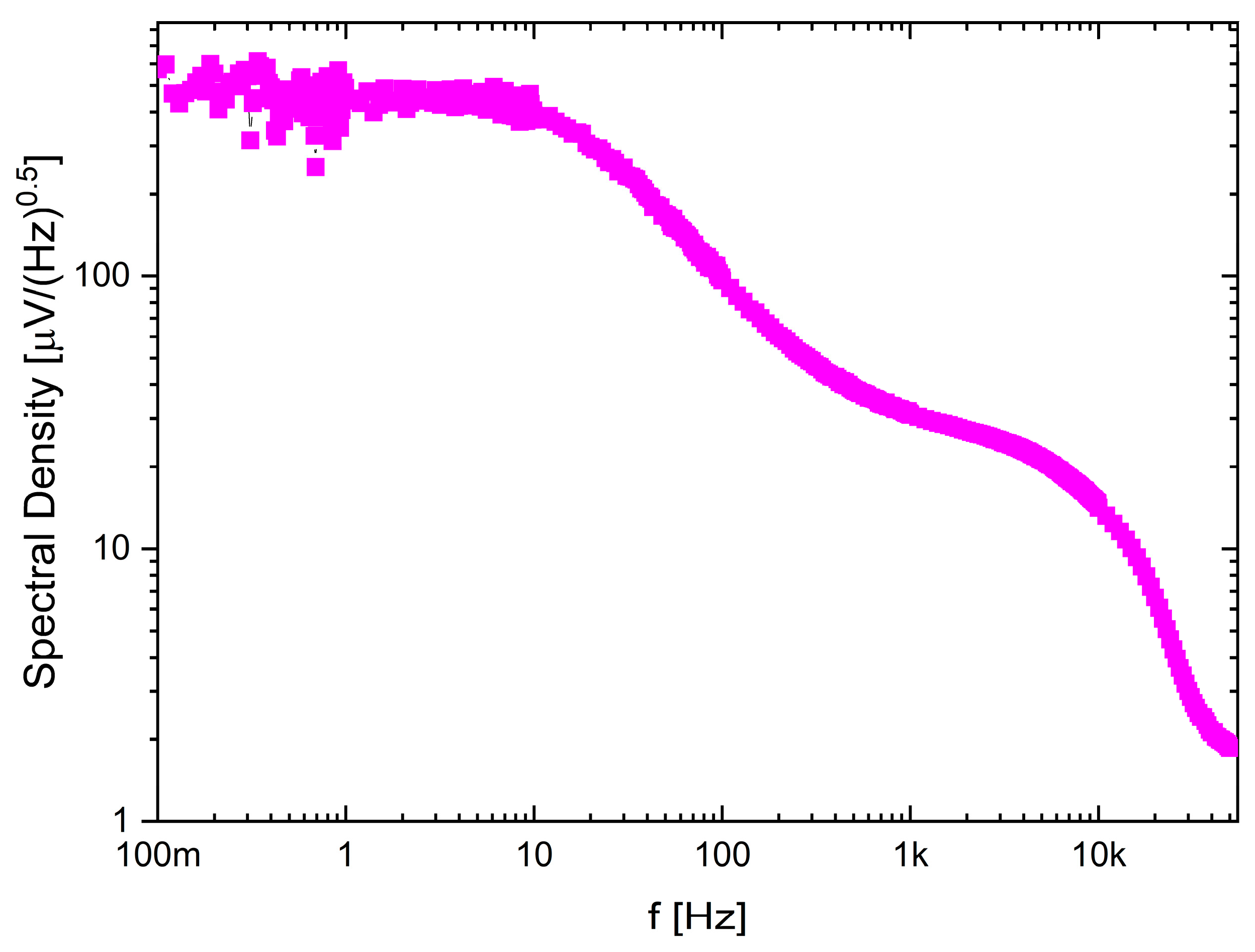

3. Recording Channel

3.1. Voltage Gain

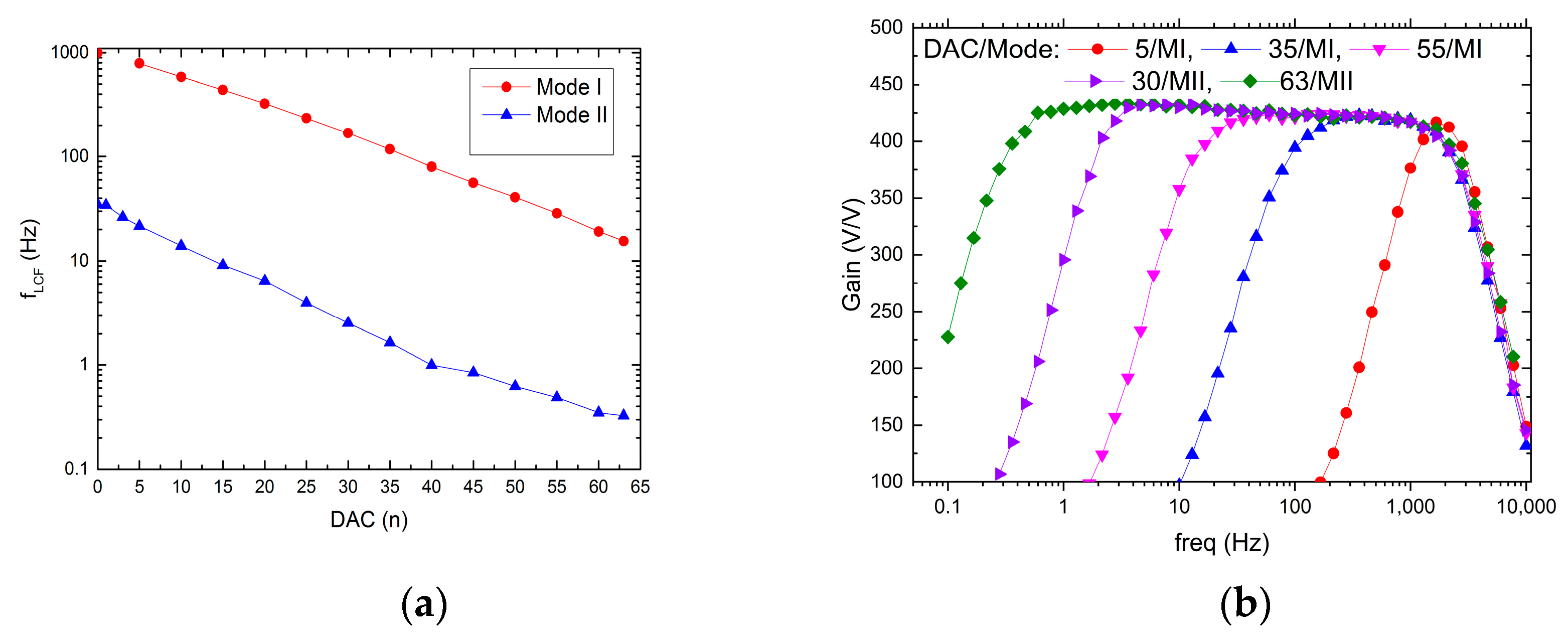

3.2. Lower Corner Frequency

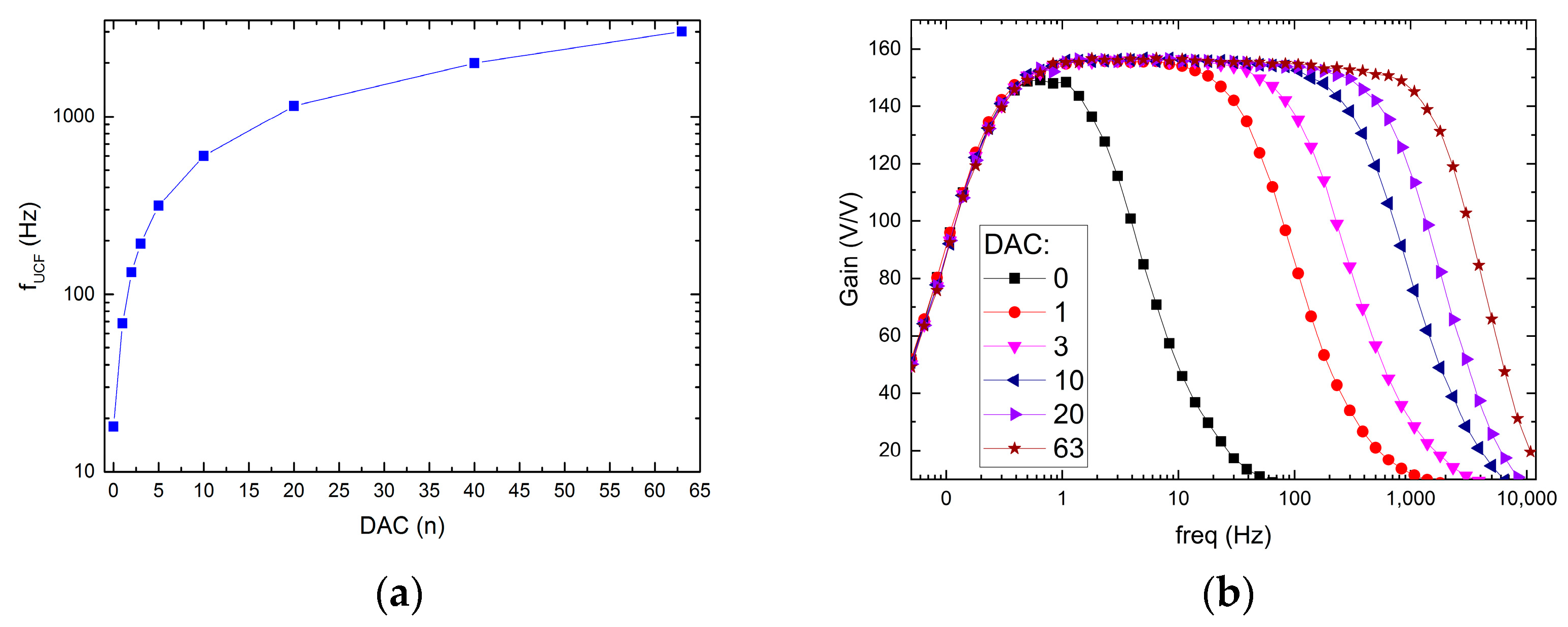

3.3. Upper Corner Frequency

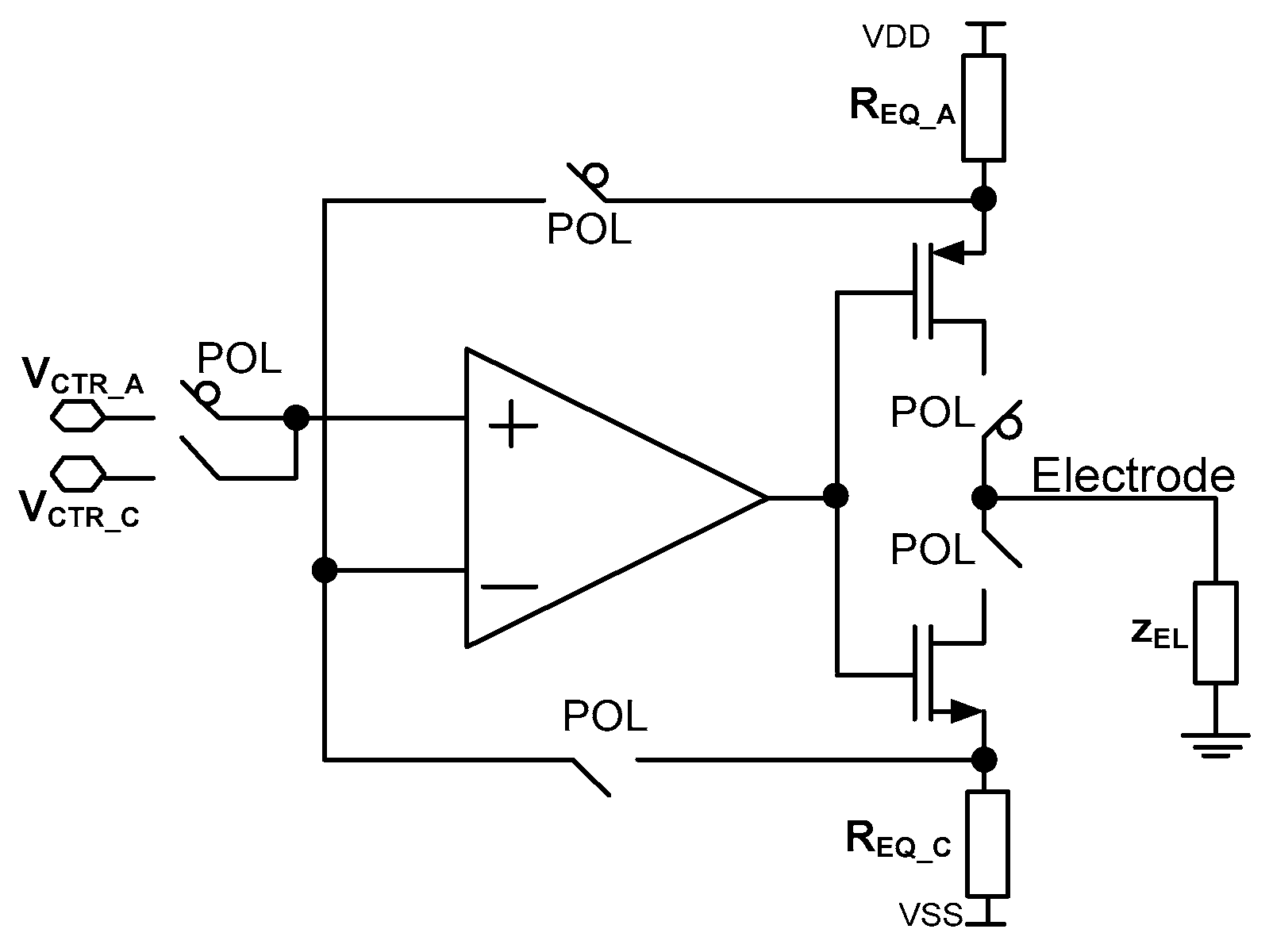

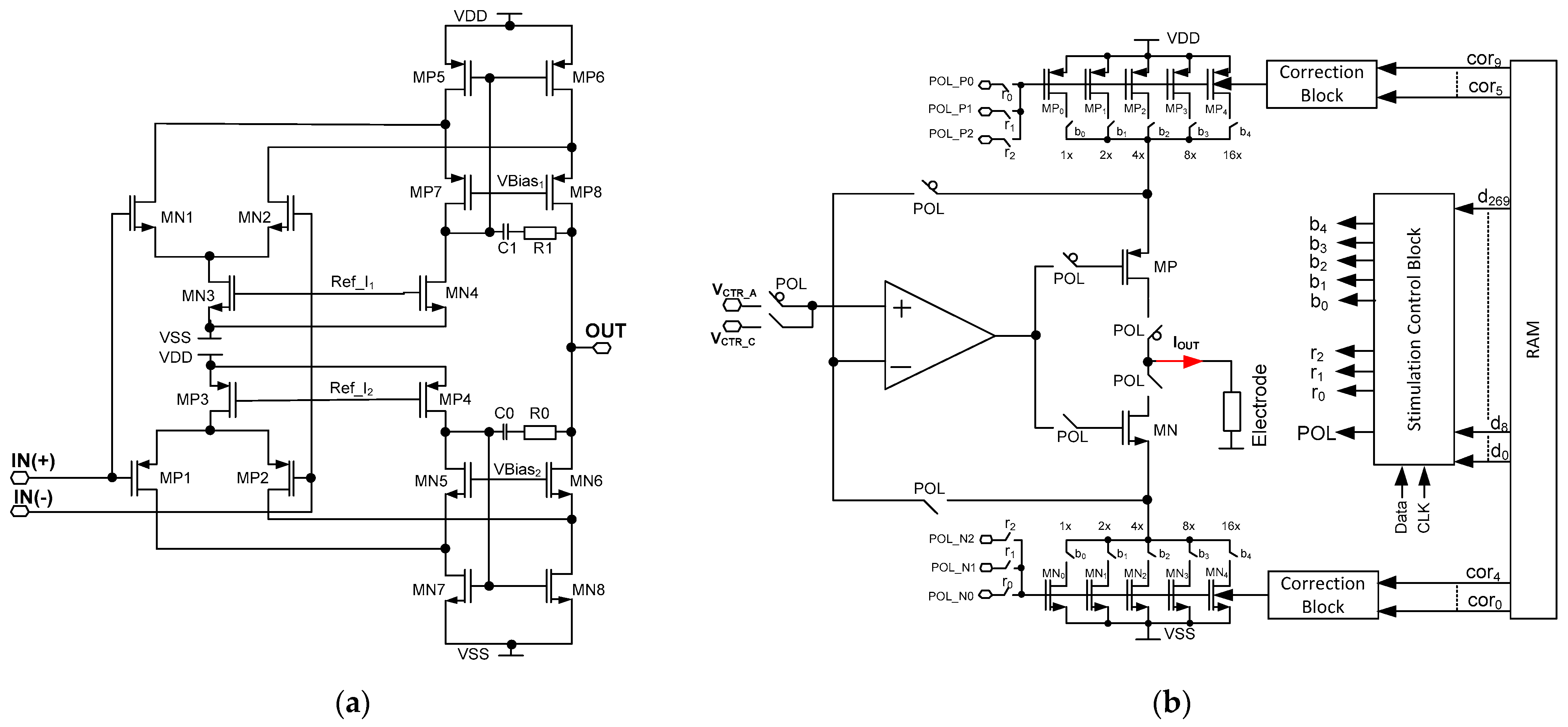

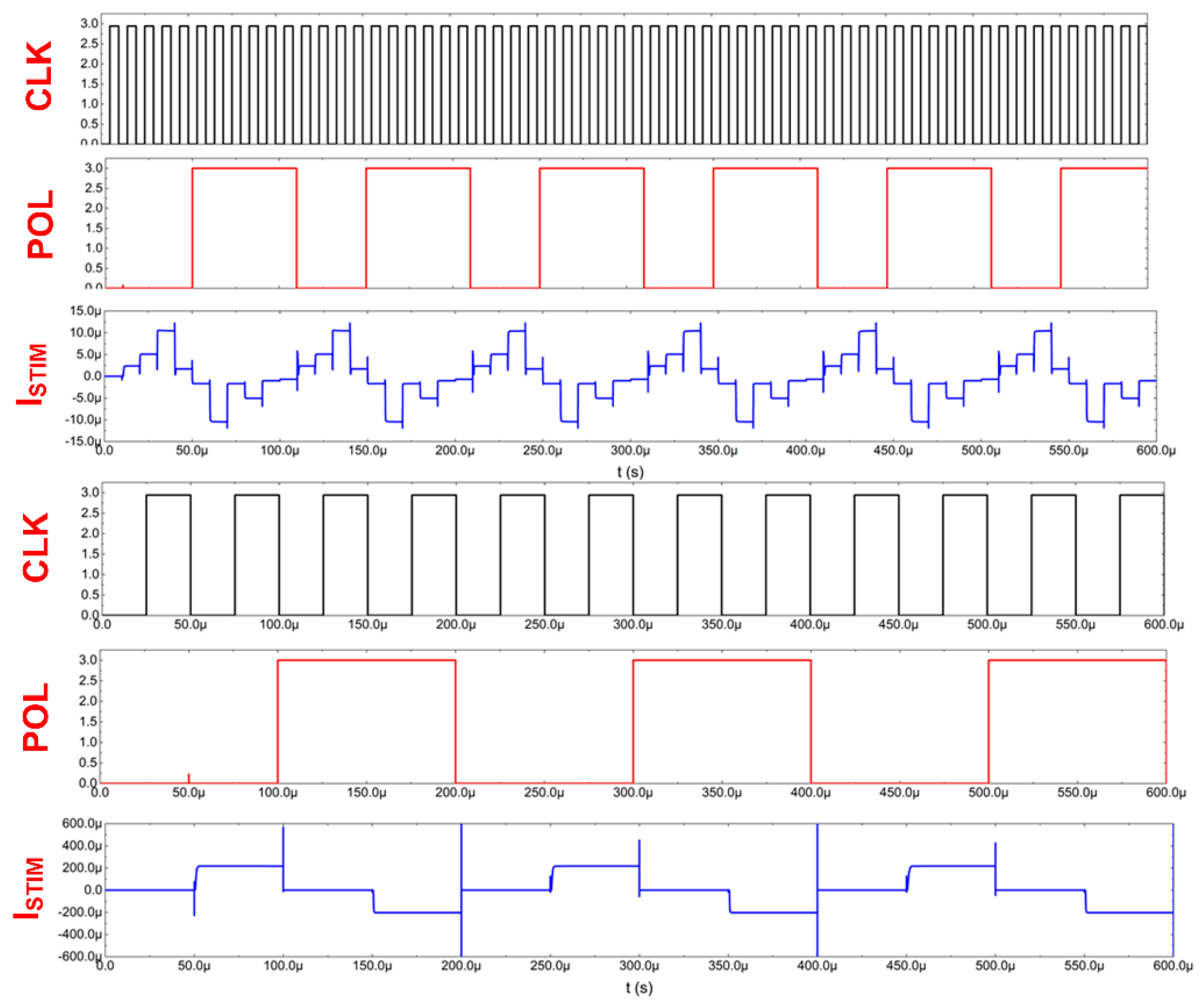

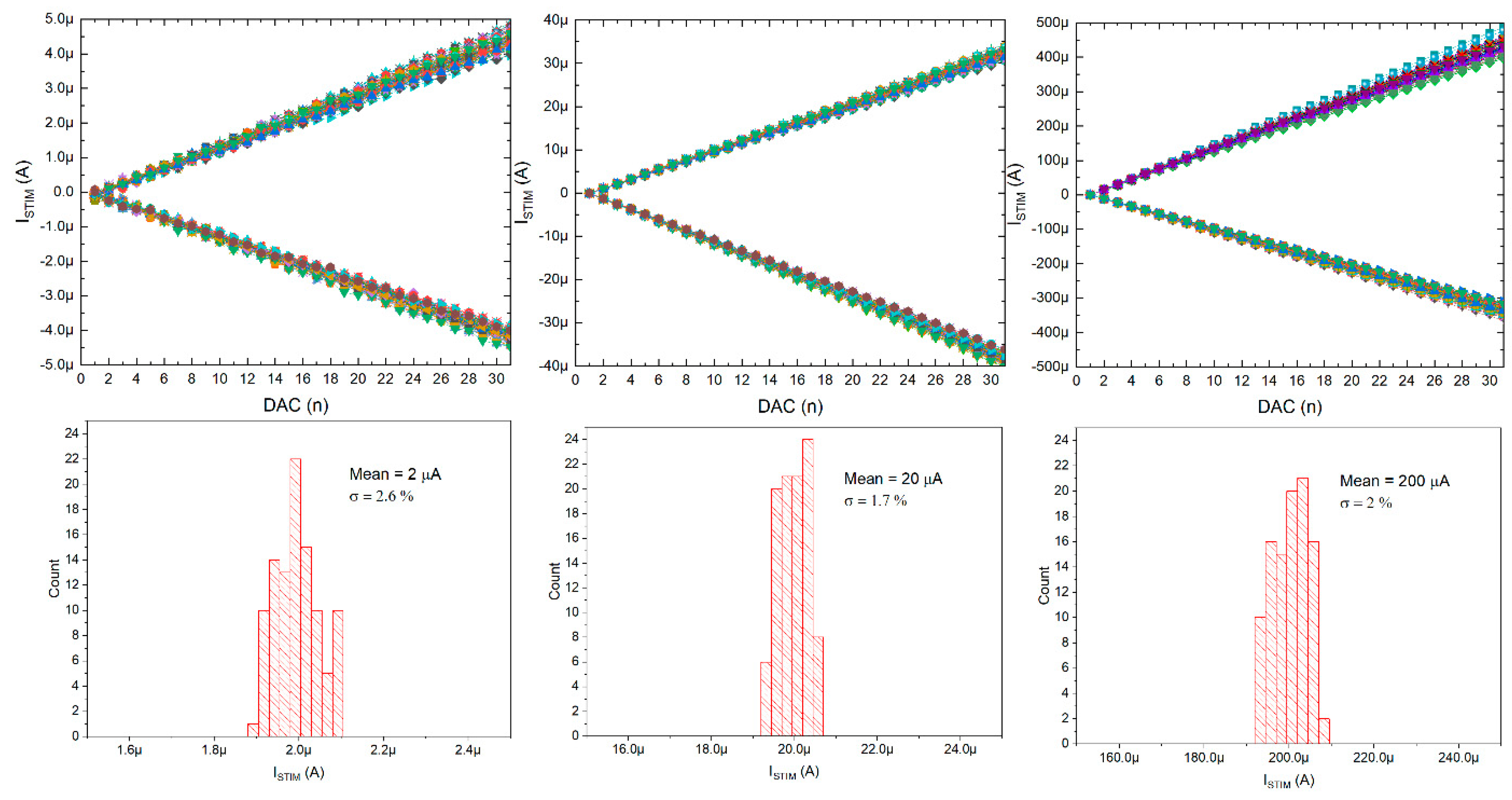

4. Stimulating Channel

- -

- current range (r0, r1, r2 outputs for selecting POL_P/POL_N voltages);

- -

- current polarity (POL output for selecting either cathodic or anodic current);

- -

- current value (b0 ÷ b4 outputs for defining the REQ resistance value).

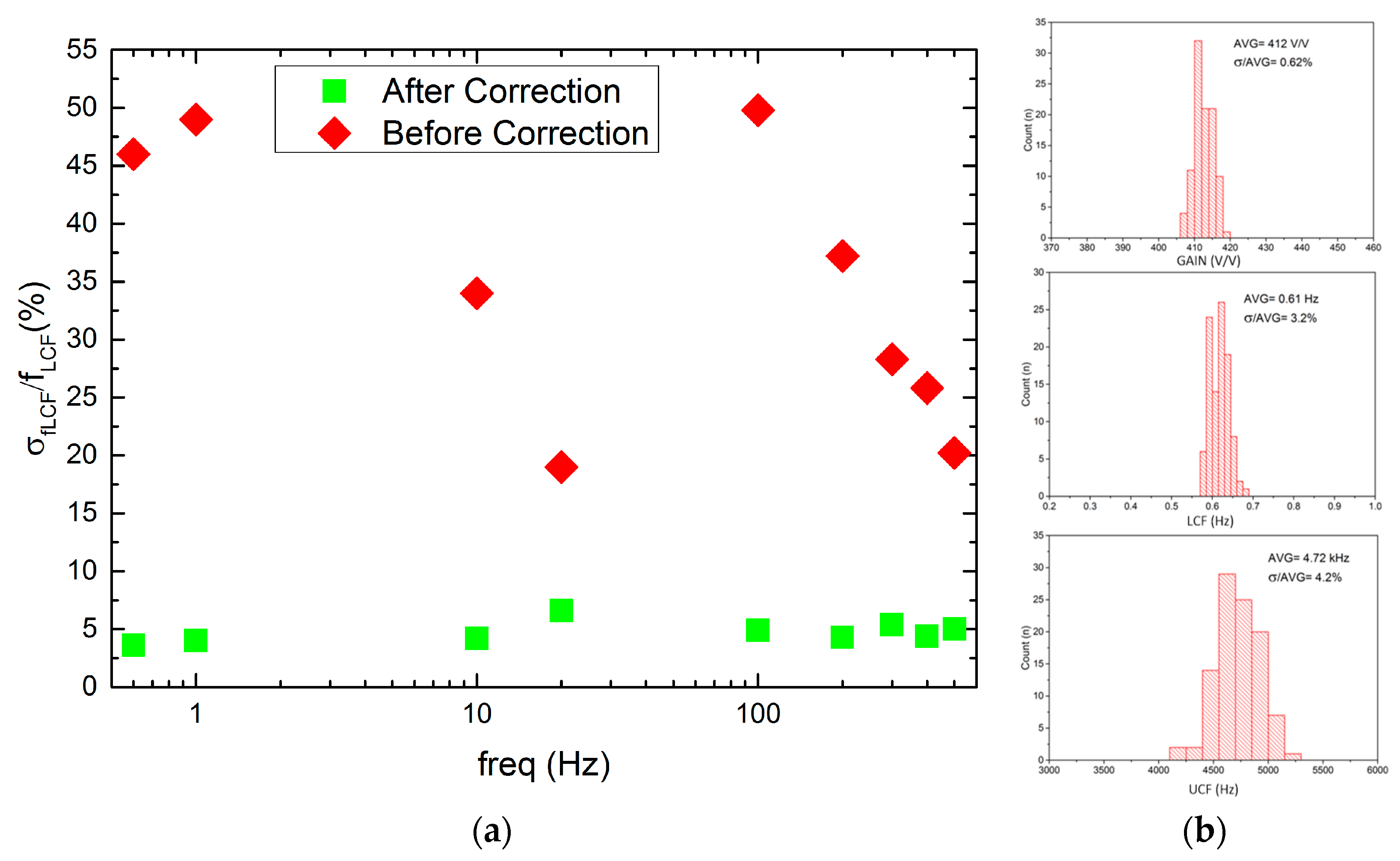

5. Measurement Results

5.1. NRS100 Main Parameters Characterization

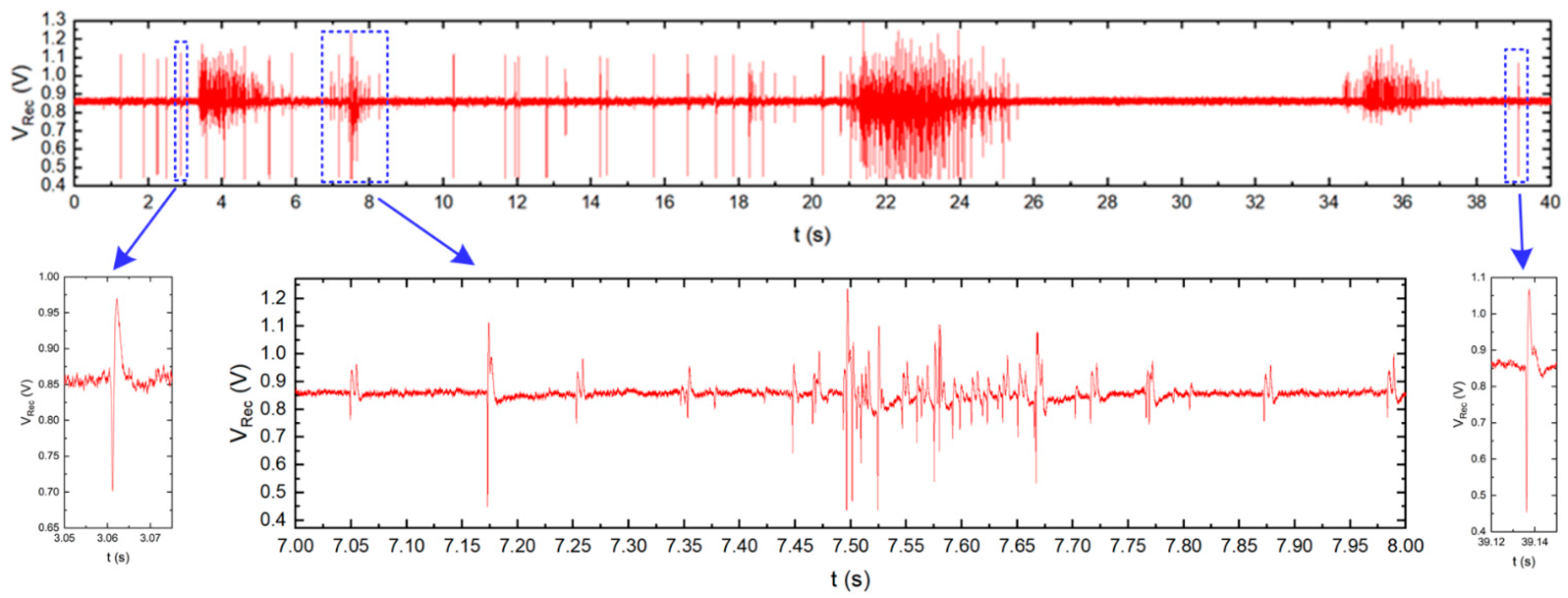

5.2. Neurobiological Experiments

6. Conclusions

- -

- recording channels’ architecture (two followed stages with individual gain and bandwidth control);

- -

- stimulating channels’ architecture (anodic/cathodic single based amplifier current source individually controlled);

- -

- correction circuitry (in-pixel local DACs supported by global DACs located out-of-the pixel matrix, in-pixel RAM).

Funding

Acknowledgments

Conflicts of Interest

References

- Narayan, R. Encyclopedia of Biomedical Engineering; Elsevier: Amsterdam, The Netherlands, September 2018. [Google Scholar]

- Saltzman, W.M. Biomedical Engineering: Bridging Medicine and Technology; Cambridge University Press: Cambridge, UK, 2015. [Google Scholar]

- Fischer, A.C.; Forsberg, F.; Lapisa, M.; Bleiker, S.J.; Stemme, G.; Roxhed, N.; Niklaus, F. Integrating MEMS and ICs. Microsyst. Nanoeng. 2015, 1, 15005. [Google Scholar] [CrossRef] [Green Version]

- Shin, H.; Jeong, S.; Lee, J.H.; Sun, W.; Choi, N.; Cho, I.J. 3D high density microelectrode array with optical stimulation and drug delivery for investigating neural circuits dynamics. Nat. Commun. 2021, 12, 492. [Google Scholar] [CrossRef] [PubMed]

- Hochberg, L.R.; Bacher, D.; Jarosiewicz, B.; Masse, N.Y.; Simeral, J.D.; Vogel, J.; Haddadin, S.; Lieu, J.; Cash, S.S.; Smagt, P.; et al. Reach and grasp by people with tetraplegia using a neurally controlled robotic arm. Nature 2012, 485, 372–375. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Johns Hopkins Applied Physics Laboratory. In a First, Patient Controls Two Prosthetic Arms with His Thoughts. Available online: https://www.jhuapl.edu/PressRelease/191016 (accessed on 25 October 2020).

- Lozano, A.M.; Lipsam, N.; Bergman, H.; Brown, P.; Chabardes, S.; Chang, J.W.; Matthews, K.; Mcintyre, C.C.; Schaepfler, T.E.; Schulder, M.; et al. Deep brain stimulation: Current challenges and future directions. Nat. Rev. Neurol. 2019, 15, 148–160. [Google Scholar] [CrossRef] [PubMed]

- Lenarz, T. Cochlear implant—State of the art. GMS Curr. Top. Otorhinolaryngol. Head Neck Surg. 2018, 16, Doc04. [Google Scholar] [CrossRef] [Green Version]

- Bullmann, T.; Radivojevic, M.; Huber, S.T.; Deligkaris, K.; Hierlemann, A.; Frey, U. Large-scale mapping of axonal arbors using high-density microelectrode arrays. Front. Cell. Neurosci. 2019, 13, 404. [Google Scholar] [CrossRef]

- Lee, T.; Je, M. Multimodal Neural Interface Circuits for Diverse Interaction With Neuronall Cell Population in Human Brain. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 574–580. [Google Scholar] [CrossRef]

- Denison, T.; Morris, M.; Sun, F. Building a bionic nervous system. IEEE Spectr. 2015, 52, 32–39. [Google Scholar] [CrossRef]

- Delyfer, M.-N.; Gaucher, D.; Govare, M.; Cougnard-Gregoire, A.; Korobelnik, J.F.; Ajana, S.; Mohand-Said, S.; Ayello-Scheer, S.; Rozaiguia-Studer, F.; Dollfus, H.; et al. Adapted Surgical Procedure for Argus II Retinal Implantation: Feasibility, Safety, Efficiency, and Postoperative Anatomic Findings. Ophthalamol. Retin. 2018, 2, 276–287. [Google Scholar] [CrossRef]

- Lopez, C.M.; Andrei, A.; Miltra, S.; Welkenhuysen, M.; Eberle, W.; Bartic, C.; Puers, R.; Yazicioglu, R.F. An Implantable 455-Active-Electrode 52-Channel CMOS Neural Probe. IEEE Int. Solid-State Circuits Conf. 2013, 49, 248–261. [Google Scholar] [CrossRef]

- Buzsaki, G.; Stark, E.; Berenyi, A.; Khodholy, D.; Kipke, D.R.; Yoon, E.; Wise, K. Tools for probing local circuits: High-density silicon probes combined with optogenetics. Neuron 2015, 86, 92–105. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Lopez, C.M.; Putzeys, J.; Raducanu, B.C.; Ballini, M.; Wang, S.; Andrei, A.; Rochus, V.; Vadebriel, R.; Severi, S.; van Hoof, C.; et al. A Neural Probe with Up to 966 Electrodes and Up to 384 Configurable Channels in 0.13 µm SOI CMOS. IEEE Trans. Biomed. Circuits Syst. 2017, 11, 510–522. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Ng, K.A.; Greenwald, E.; Xu, Y.P.; Thakor, N.V. Implantable neurotechnologies: A review of integrated circuit amplifiers. Med Biol. Eng. Comput. 2016, 54, 45–62. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Davis, W.R.; Wilson, J.; Mick, S.; Xu, J.; Hua, H.; Mineo, C.; Sule, A.M.; Steer, M.; Franzon, P.D. Demystifying 3D ICs: The pros and cons on going vertical. IEEE Des. Test. Comput. 2005, 22, 498–510. [Google Scholar] [CrossRef]

- Chang, C.W.; Chou, L.C.; Huang, P.T.; Wu, S.L.; Lee, W.W.; Chuang, C.T.; Chen, K.N.; Hwang, W.; Chen, K.H.; Chiu, C.T.; et al. A double-sided, single-chip integration scheme using through-silicon-via for neural sensing applications. Biomed. Microdevices 2015, 17, 11. [Google Scholar] [CrossRef]

- Brown, A.; Ross, J.D.; Blum, R.A.; Nam, Y.; Wheeler, B.C.; DeWeerth, S.P. Stimulus-artifact elimination in a multi-electrode system. IEEE Trans. Biomed. Circuits Syst. 2008, 2, 10–21. [Google Scholar] [CrossRef]

- Bagheri, A.; Salam, M.T.; Velasquez, J.L.P.; Genov, R. Low-Frequency Noise and Offset Rejection in DC-Coupled Neural Amplifiers: A Review and Digitally-Assisted Design Tutorial. IEEE Trans. Biomed. Circuits Syst. 2016, 11, 161–176. [Google Scholar] [CrossRef] [PubMed]

- Kmon, P.; Grybos, P. Energy Efficient Low-Noise Multichannel Neural Amplifier in Submicron CMOS Process. IEEE Trans. Circuits Syst. –I 2013, 60, 1764–1775. [Google Scholar] [CrossRef]

- Kmon, P. Noise Minimization Limits in Multichannel Integrated Circuits Dedicated to Neurobiology Experiments. Microelectron. J. 2016, 51, 67–74. [Google Scholar] [CrossRef]

- Żołądź, M.; Kmon, P.; Rauza, J.; Gryboś, P.; Blasiak, T. Multichannel Neural Recording System Based on Family ASICs Processed in Submicron Technology. Microelectron. J. 2014, 45, 1226–1231. [Google Scholar] [CrossRef]

- Kmon, P.; Gryboś, P.; Zoladz, M.; Lisicka, A. Fast and Effective Method of CMRR Enhancement For Multichannel Integrated Circuits Dedicated to Biomedical Measurements. Electron. Lett. 2015, 51, 1736–1738. [Google Scholar] [CrossRef]

- Deptuch, G.W.; Fahim, F.; Grybos, P.; Hoff, J.; Holm, S.; Maj, P.; Siddons, D.P.; Trimpl, M.; Zimmerman, T. An algorithm of an X-ray hit allocation to a single pixel in a cluster and its test-circuit implementation. IEEE Trans. Circuits Syst. –I 2017, 65, 185–197. [Google Scholar] [CrossRef]

- Kmon, P.; Deptuch, G.; Fahim, F.; Gryboś, P.; Maj, P.; Szczygieł, R.; Zimmerman, T. Active feedback with leakage current compensation for charge sensitive amplifier used in hybrid pixel detector. IEEE Trans. Nucl. Sci. 2019, 66, 664–673. [Google Scholar] [CrossRef]

- Samiei, A.; Hashemi, H. A Bidirectional Neural Interface SoC with Adaptive IIR Stimulation Artifact Cancelers. IEEE J. Solid-State Circuits 2021, 56, 2142–2157. [Google Scholar] [CrossRef]

- Rezaei, M.; Maghsoudloo, E.; Bories, C.; de Koninck, Y.; Gosselin, B. A low-power current-reuse analog front-end for high-density Neural Recording Implants. IEEE Trans. Biomed. Syst. Circuits 2018, 12, 271–280. [Google Scholar] [CrossRef] [PubMed]

- Ballini, M.; Muller, J.; Livi, P.; Chen, Y.; Frey, U.; Stettler, A.; Shadmani, A.; Viswam, V.; Jones, I.L.; Jackel, D.; et al. A 1024-channel CMOS microelectrode array with 26,400 electrodes for recording and stimulation of electrogenic cells in vitro. IEEE J. Solid-State Circuits 2014, 49, 2705–2719. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Chen, W.-M.; Chiueh, H.; Chen, T.-J.; Ho, C.-L.; Jeng, C.; Ker, M.-D.; Lin, C.-Y.; Huang, Y.-C.; Chou, C.-W.; Fan, T.-Y. A fully integrated 8-channel closed-loop neural prosthetic SoC for real-time epileptic seizure control. IEEE J. Solid-State Circuits 2014, 49, 232–247. [Google Scholar] [CrossRef]

- Muller, R.; Gambini, S.; Rabaey, J.M. A 0.013 mm 25 μW DCcoupled neural signal acquisition IC with 0.5 V supply. Proc. IEEE Solid-State Circuits Conf. 2011, 47, 232–243. [Google Scholar] [CrossRef]

- Kassiri, H.; Salam, M.T.; Pazhouhandeh, M.R.; Soltani, N.; Velasquez, J.L.P.; Carlen, P.; Genov, R. Rail-to-Rail-Input Dual-Radio 64-Channel Closed-Loop Neurostimulator. IEEE J. Solid State Circuits 2017, 52, 2793–2810. [Google Scholar] [CrossRef]

- Greenwald, E.; So, E.; Wang, Q.; Mollazadeh, M.; Maier, C.; Etienne-Cummings, R.; Cauwenberghs, G.; Thakor, N. A bidirectional neural interface IC with chopper stabilized BioADC array and charge balanced stimulator. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 990–1002. [Google Scholar] [CrossRef] [PubMed]

- Harrison, R.R.; Charles, C. A low-power low-noise CMOS amplifier for neural recording applications. IEEE J. Solid-State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Tsividis, Y. Operation and Modelling of the MOS Transistor; Oxford University Press: Oxford, UK, 2003. [Google Scholar]

- Simpson, J.; Ghovanloo, M. An Experimental Study of Voltage, Current, and Charge Controlled Stimulation Front-End Circuitry. In Proceedings of the IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007. [Google Scholar]

- Gilja, V.; Chestek, C.A.; Diester, I.; Henderson, J.M.; Deisseroth, K.; Shenoy, K.V. Challenges and opportunities for next-generation intracortically based neural prostheses. IEEE Trans. Biomed. Eng. 2011, 58, 1891–1899. [Google Scholar] [CrossRef] [PubMed]

- Michael, J.F.; Samanta, J.; Moustafa, A.A.; Sherman, S.J. Hold your horses: Impulsivity, deep brain stimulation, and medication in Parkinsonism. Science 2007, 318, 1309–1312. [Google Scholar]

- Luo, Y.H.L.; da Cruz, L. The Argus II Retinal Prosthesis System. Prog. Retin. Eye Res. 2016, 50, 89–107. [Google Scholar] [CrossRef]

- Collinger, J.L.; Wodlinger, B.; Downey, J.E.; Wang, W.; Tyler-Kabara, E.C.; Weber, D.J.; McMorland, A.J.C.; Velliste, M.; Boninger, M.L.; Schwartz, A.B. High-performance neuroprosthetic control by an individual with tetraplegia. Lancet 2013, 381, 557–564. [Google Scholar] [CrossRef] [Green Version]

- Liu, Y.; Urso, A.; da Ponte, R.M.; Costa, T.; Valente, V.; Giagka, V.; Serdijn, W.A.; Constandinou, T.G.; Denison, T. Bidirectional Bioelectronic Interfaces: System Design and Circuit Implications. IEEE Solid State Circuits Mag. 2020, 12, 30–46. [Google Scholar] [CrossRef]

- Stanslaski, S.; Herron, J.; Chouinard, T.; Bourget, D.; Isaacson, B.; Kremen, V.; Opri, E.; Drew, W.; Brinkman, B.H.; Gunduz, A.; et al. A chronically-implanted neural coprocessor for exploring treatments for neurological disorders. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 1230–1245. [Google Scholar] [CrossRef]

- Gnadt, J.W.; Echols, S.D.; Yildrim, A.; Zhang, H.; Paul, K. Spectral cancellation of microstimulation artifact for simultaneous neural recording in situ. IEEE Trans. Biomed. Eng. 2003, 50, 1129–1135. [Google Scholar] [CrossRef] [PubMed]

- Frey, U.; Sedivy, J.; Heer, F.; Pedron, R.; Ballini, M.; Mueller, J.; Bakkum, D.; Hafizovic, S.; Faraci, F.D.; Greve, F.; et al. Switch-matrix-based high-density microelectrode array in CMOS technology. IEEE J. Solid-State Circuits 2010, 45, 467–482. [Google Scholar] [CrossRef]

- Jimbo, Y.; Kasai, N.; Torimitsu, K.; Tateno, T.; Robinson, H.P.C. A system for MEA-based multisite stimulation. IEEE Trans. Biomed. Eng. 2003, 50, 241–248. [Google Scholar] [CrossRef] [PubMed]

- Kadlubowski, L.; Kmon, P. Analysis of circuits for effective stimulation in neurobiological experiments. Electr. Rev. 2016, 11. [Google Scholar] [CrossRef]

- Hottowy, P.; Skoczeń, A.; Gunning, D.E.; Kachiguine, S.; Mathieson, K.; Sher, A.; Wiącek, P.; Litke, A.M.; Dąbrowski, W. Properties and application of a multichannel integrated circuit for low-artifact, patterned electrical stimulation of neural tissue. J. Neural Eng. 2012, 9, 066005. [Google Scholar] [CrossRef] [Green Version]

- Valente, V.; Demosthenous, A.; Bayford, R. A Tripolar Current-Steering Stimulator ASIC for Field Shaping in Deep Brain Stimulation. IEEE Trans. Biomed. Circuits Syst. 2011, 6, 197–207. [Google Scholar] [CrossRef] [PubMed]

- Farahmand, S.; Vahedian, H.; Eslami, M.A. Wearable, Battery-Powered, Wireless, Programmable 8-Channel Neural Stimulator. In Proceedings of the 34th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, San Diego, CA, USA, 28 August–1 September 2012. [Google Scholar]

- Mokwa, W.; Goertz, M.; Koch, C.; Krisch, I.; Trieu, H.; Walter, P. Intraocular Epiretinal Prosthesis to Restore Vision in Blind Humans. In Proceedings of the 30th Annual International IEEE Engineering in Medicine and Biology Society, Vancouver, BC, Canada, 20–25 August 2008. [Google Scholar]

- Wagenaar, D.A.; Pine, J.; Potter, S.M. Effective parameters for stimulation of dissociated cultures using multi-electrode arrays. J. Neurosci. Methods 2004, 138, 27–37. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Laotaveerungrueng, N.; Lahiji, R.R.; Garverick, S.L.; Mehregany, M. A High-Voltage, High-Current CMOS Pulse Generator ASIC for Deep Brain Stimulation. In Proceedings of the 32nd Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Buenos Aires, Argentina, 31 August–4 September 2010. [Google Scholar]

- Chin, C.; Senior, W.; Sung, T.C.; Wu, Y.H.; Hsu, C.H.; Shmilovitz, D. A Reconfigurable 16-channel HV Stimulator ASIC for Spinal Cord Stimulation Systems. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems, Kaohsiung, Taiwan, 2–5 December 2012. [Google Scholar]

- Arfin, S.K.; Sarpeshkar, R. An Energy-Efficient, Adiabatic Electrode Stimulator with Inductive Energy Recycling and Feedback Current Regulation. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 1–14. [Google Scholar] [CrossRef]

- Chun, H.; Tran, N.; Yang, Y.; Kavehei, O.; Bai, S.; Skafidas, S. A Precise Charge Balancing and Compliance Voltage MonitoringStimulator Front-End for 1024-electrodes Retinal Prosthesis. In Proceedings of the 34th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, San Diego, CA, USA, 28 August–1 September 2012. [Google Scholar]

- Sooksood, K.; Noorsal, E.; Bihr, U.; Ortmanns, M. Recent Advances in Power Efficient Output Stage for High Density Implantable Stimulators. In Proceedings of the 34th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, San Diego, CA USA, 28 August–1 September 2012. [Google Scholar]

- Kmon, P. Design of a Reconfigurable Stimulator for Multichannel Integrated Systems Dedicated to Neurobiology Experiments. In Proceedings of the 21st International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), Lublin, Poland, 19–21 June 2014. [Google Scholar]

- NEUROACT: A Collaborative Training Program to Develop Multi-Electrode Array (MEA) Platforms to Understand Synaptic Function and Treat Diseases of the Nervous System. Available online: https://cordis.europa.eu/project/id/286403/ (accessed on 25 May 2018).

- Zoladz, M. A System for 256-Channel In-Vitro Recording of the Electrophysiological Activity of Brain Tissue. Metrol. Meas. Syst. 2013, 20, 371–384. [Google Scholar] [CrossRef] [Green Version]

- Heuschkel, M. Fabrication of Multi-Electrode Array Devices for Electrophysiological Monitoring of In-Vitro Cell/Tissue Cultures. Ph.D. Thesis, EPFL, Lausanne, Switzerland, 2001. [Google Scholar]

- Van de Vijver, S.; Missault, S.; van Soom, J.; van der Veken, P.; Augustyns, K.; Joossens, J.; Dedeurwaerdere, S.; Giugliano, M. The effect of pharmacological inhibition of Serine Proteases on neuronal networks in vitro. PeerJ 2019, 7, e6796. [Google Scholar] [CrossRef] [Green Version]

| Biomedical Signal | Amplitudes | Frequency Band |

|---|---|---|

| Local Field Potentials (LFP) | 10 µV ÷ 5 mV | 1 ÷ 500 Hz |

| Action Potentials (AP) | 10 µV ÷ 500 µV | 300 Hz ÷ 7 kHz |

| EEG | 1 µV ÷ 10 µV | <1 ÷ 100 Hz |

| ECG | 1 mV ÷ 10 mV | 5 ÷ 500 Hz |

| EMG | 100 µV ÷ 10 mV | 20 Hz ÷ 1 kHz |

| Application | Stimulation Current [µA] | Duration [µs] |

|---|---|---|

| Cortex | 400 | 500 |

| Retina | 100 | 27–1500 |

| In vitro neural networks | 1 ÷ 10 | 20 ÷ 1280 |

| Deep Brain Stimulation | 200 ÷ 2000 | 60 ÷ 120 |

| Spinal Cord | 500 | 60 ÷ 1000 |

| Specification | This Work | JSSC’14 [30] | JSSC’17 [32] | JSSC’21 [27] | TBCAS’16 [33] |

|---|---|---|---|---|---|

| Technology (nm) | 180 | 180 | 130 | 180 | 180 |

| Supply (V) | 1.8/3.3 | 1.8 | 1.2/2.5/3.3 | 1/3 | 1.5/5 |

| Neural Recording | |||||

| Area/ch. (mm2) | 0.053 | 0.45 | 0.011 | 0.66 | 0.56 |

| Power/ch. (µW) | 12 | 57.7 | 0.63 | 2.5 | 5.5 |

| Bandwidth (Hz) | (0.3 ÷ 1k)–(20 ÷ 3k) LFP (0.3 ÷ 1k)–4.7k AP | (0.1 ÷ 10) –(0.8 k ÷ 7k) | 0.1–500 | 200–9k | 0.25–250 |

| Voltage Gain (dB) | 43.5/52 | 41–61 | Direct ADC w/o amplifier | 27.6–50 | Direct ADC w/o amplifier |

| Controllability | In-pixel LCF (6–bit), UCF (6–bit), Voltage Gain | Global LCF, UCF, and Voltage Gain | N.A. | Voltage Gain | UCF |

| Noise (µVRMS) | 8.5 (10–4.7k) | 5.23 (0.5–7k) | 1.13 (0.1–500) | 6.2/11 | 1 |

| # of Rec. Channels | 100 | 8 | 64 | 8 | 4 |

| eural Stimulation | |||||

| Current Range (µA) | 0–4.5 0–30 0–400 | 30 | 10–1350 | 1–127 | 250 |

| Controllability | In-pixel 10 bit + 18 bits for chip range control In-pixel RAM for 30 independent current stimulus Global stimulation frequency control | N.A. | 8 bit current DAC | 7 bit current DAC | 8 bit current DAC |

| # of Stim. Channels | 100 | 1 | 64 | 2 | 4 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kmon, P. Highly Configurable 100 Channel Recording and Stimulating Integrated Circuit for Biomedical Experiments. Sensors 2021, 21, 8482. https://doi.org/10.3390/s21248482

Kmon P. Highly Configurable 100 Channel Recording and Stimulating Integrated Circuit for Biomedical Experiments. Sensors. 2021; 21(24):8482. https://doi.org/10.3390/s21248482

Chicago/Turabian StyleKmon, Piotr. 2021. "Highly Configurable 100 Channel Recording and Stimulating Integrated Circuit for Biomedical Experiments" Sensors 21, no. 24: 8482. https://doi.org/10.3390/s21248482

APA StyleKmon, P. (2021). Highly Configurable 100 Channel Recording and Stimulating Integrated Circuit for Biomedical Experiments. Sensors, 21(24), 8482. https://doi.org/10.3390/s21248482