An 8.72 µW Low-Noise and Wide Bandwidth FEE Design for High-Throughput Pixel-Strip (PS) Sensors

Abstract

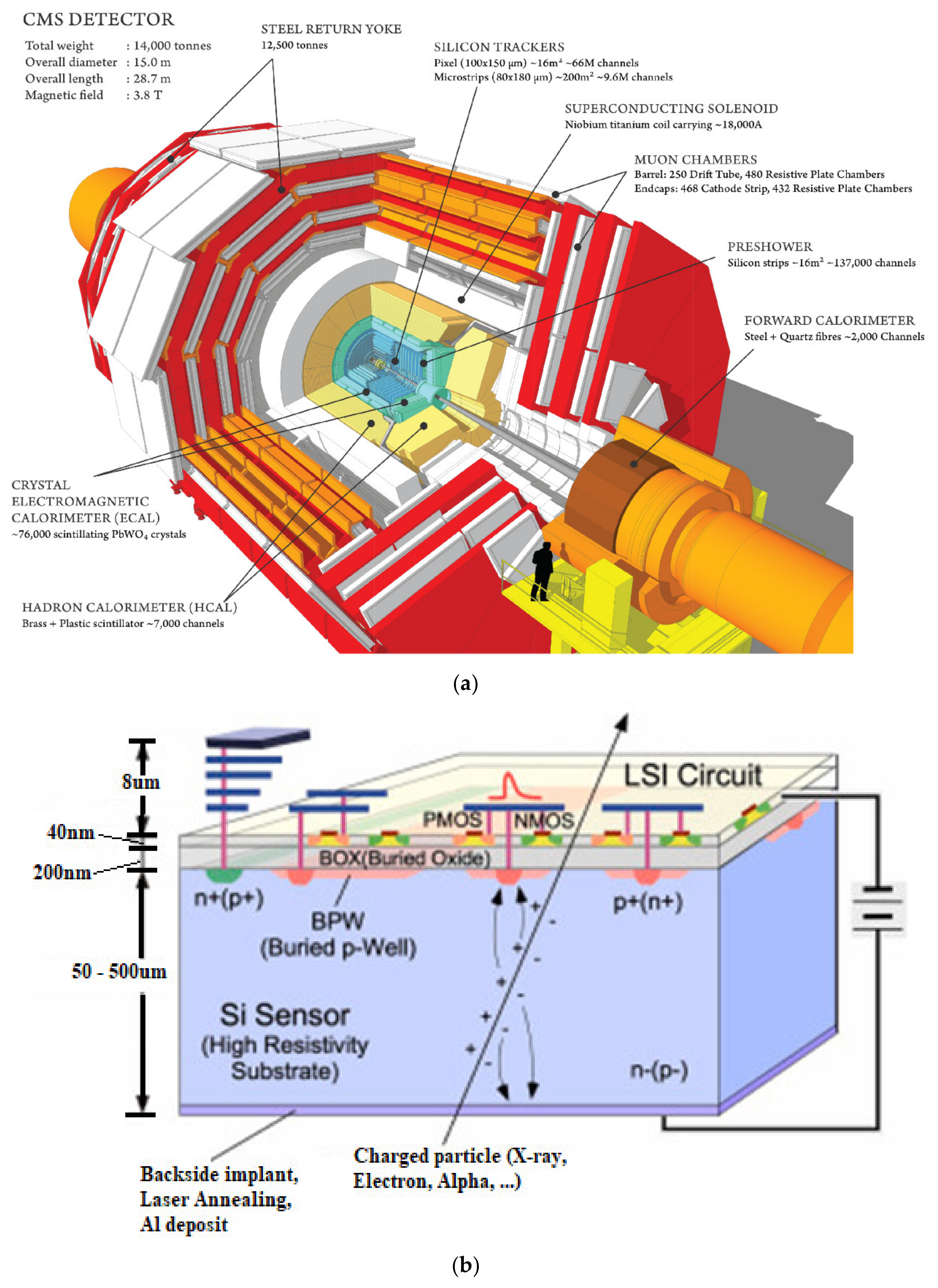

1. Introduction

2. Design Philosophy and Materials

2.1. Design of the CSA Core Amplifier Circuit

2.2. Analysis of the CSA Circuit

2.3. Feedback Lead Network (FLN) Implementation

2.4. Design of the CR-RC1 Pulse Shaper

2.5. Noise Optimization of the FEE Circuit

3. Simulation Outcomes and Discussions

3.1. Simulation and Implementation Framework

3.2. Results and Discussions

3.3. Post Layout Monte Carlo Simulation Results

3.4. Process Variations

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Acknowledgments

Conflicts of Interest

References

- Fahim, F.; Bianconi, S.; Rabinowitz, J.; Joshi, S.; Mohseni, H. Dynamically Reconfigurable Data Readout of Pixel Detectors for Automatic Synchronization with Data Acquisition Systems. Sensors 2020, 20, 2560. [Google Scholar] [CrossRef]

- Ceresa, D.; Kloukinas, K.; Kaplon, J.; Caratelli, A.; Scarfì, S. Readout Architecture for the Pixel-Strip Module of the CMS Outer Tracker Phase-2 Upgrade; Technical Report; SISSA: Trieste, Italy, 2017. [Google Scholar]

- Jung, S.-J.; Hong, S.-K.; Kwon, O.-K. A Readout IC Using Two-Step Fastest Signal Identification for Compact Data Acquisition of PET Systems. Sensors 2016, 16, 1748. [Google Scholar] [CrossRef]

- William, R.L. Techniques for Nuclear and Particle Physics Experiments, a How-To Approach, 2nd ed.; Springer: Berlin/Heidelberg, Germany, 1994; pp. 233–296. [Google Scholar]

- Ghosh, S.S. Highlights from the Compact Muon Solenoid (CMS) Experiment. Universe 2019, 5, 28. [Google Scholar] [CrossRef]

- Jérôme, F.K.; Evariste, W.T.; Bernard, E.Z.; Crespo, M.L.; Cicuttin, A.; Reaz, M.B.I.; Bhuiyan, M.A.S.; Chowdhury, M.E.H. A 0.35 μm low-noise stable charge sensitive amplifier for silicon sensors applications. Inf. MIDEM 2020, 50, 3–13. [Google Scholar]

- Seidel, S. Silicon strip and pixel detectors for particle physics experiments. Phys. Rep. 2019, 828, 1–34. [Google Scholar] [CrossRef]

- Park, K.; Kim, S.M.; Eom, W.-J.; Kim, J.J. A Reconfigurable Readout Integrated Circuit for Heterogeneous Display-Based Multi-Sensor Systems. Sensors 2017, 17, 759. [Google Scholar] [CrossRef] [PubMed]

- Lee, C.; Cho, G.; Unruh, T.; Hur, S.; Kwon, I. Integrated Circuit Design for Radiation-Hardened Charge-Sensitive Amplifier Survived up to 2 Mrad. Sensors 2020, 20, 2765. [Google Scholar] [CrossRef]

- Dmitrii, V.A.; Gennady, G.B.; Vladimir, V.A.; Alexander, A.S. Use of high-field electron injection into dielectrics to enhance functional capabilities of radiation MOS sensors. Sensors 2020, 20, 2382. [Google Scholar]

- Jiang, W.; Chalich, Y.; Deen, M.J. Sensors for Positron Emission Tomography Applications. Sensors 2019, 19, 5019. [Google Scholar] [CrossRef]

- Abbene, L.; Gerardi, G. High Resolution X-ray spectroscopy with compound semiconductor detectors and digital pulse processing systems. Intech Open 2012, 39–64. [Google Scholar]

- Schioppa, E.J.; Idarraga, J.; Beuzekom, M.V.; Visser, J.; Koffeman, E.; Heijne, E.; Engel, K.J.; Uher, J. Study of charge diffusion in a silicon sensor using an energy sensitive pixel readout chip. IEEE Trans. Nucl. Sci. 2015, 62, 2349–2359. [Google Scholar] [CrossRef]

- Peric, I. A novel monolithic pixel sensor implemented in high-voltage CMOS technology. In Proceedings of the IEEE Nuclear Science Symposium Conference Record, Honolulu, HI, USA, 26 October–3 November 2007; pp. 1033–1039. [Google Scholar]

- Orshanky, M.; Nassif, S.; Boning, D. Design for Manufacturability and Statistical Design: A Constructive Approach Integrated Circuits and Systems; Springer: Boston, MA, USA, 2008. [Google Scholar]

- Faccio, F.; Cervelli, G. Radiation-induced edge effects in deep submicron CMOS transistors. IEEE Trans. Nucl. Sci. 2005, 52, 2413–2420. [Google Scholar] [CrossRef]

- Tang, T.; Goh, W.L.; Yao, L.; Cheong, J.H.; Gao, Y. An integrated multichannel neural recording analog front-end ASIC with area-efficient driven right leg circuit. In Proceedings of the 2017 39th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), Jeju, Korea, 11–15 July 2017; pp. 217–220. [Google Scholar]

- Noulis, T.; Siskos, S.; Sarrabayrouse, G. Noise optimized charge-sensitive CMOS amplifier for capacitive radiation sensors. IET Circuits Devices Syst. 2008, 2, 324–334. [Google Scholar] [CrossRef]

- Bhuiyan, M.A.S.; Badal, T.I.; Reaz, M.B.I.; Crespo, M.L.; Cicuttin, A. Design Architectures of the CMOS Power Amplifier for 2.4 GHz ISM Band Applications: An Overview. Electronics 2019, 8, 477. [Google Scholar] [CrossRef]

- Pezzotta., A.; Costantini, A.; Matteis, M.D.; D’Amico, S.; Gorini, G.; Murtas, F.; Baschirotto, A. A low-power CMOS 0.13 µm charge-sensitive preamplifier for GEM sensors. In Proceedings of the 2013 International Conference on IC Design & Technology, Pavia, Italy, 29–31 May 2013; pp. 147–150. [Google Scholar]

- Cheng, Q.; Li, W.; Tang, X.; Guo, J. Design and analysis of three-stage amplifier for driving pF-to-nF capacitive load based on local Q-factor control and cascode miller compensation techniques. Electronics 2019, 8, 572. [Google Scholar] [CrossRef]

- Wang, H.; Britton, C.; Quaiyum, F.; Pullano, S.A.; Taylor, L.; Fiorillo, A.S.; Islam, S.K. A Charge Sensitive Pre-Amplifier for Smart Point-of-Care Devices Employing Polymer-Based Lab-on-a-Chip. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 984–988. [Google Scholar] [CrossRef]

- Song, H.; Park, Y.; Kim, H.; Ko, H. Fully Integrated Biopotential Acquisition Analog Front-End IC. Sensors 2015, 15, 25139–25156. [Google Scholar] [CrossRef]

- Baschirotto, A.; Cocciolo, G.; De Matteis, M.; Giachero, A.; Gotti, C.; Maino, M.; Pessina, G. A fast and low noise charge sensitive preamplifier in 90 nm CMOS technology. J. Instrum. 2012, 7, C01003. [Google Scholar] [CrossRef]

- Gordon, R.G. Practical Gamma-Ray Spectrometry, 2nd ed.; John Wiley & Sons: Hoboken, NJ, USA, 2008; pp. 61–99, 279–293. [Google Scholar]

- Zubrzycka, W.; Kasinski, K. All-programmable low noise readout ASIC for silicon strip sensors in tracking detectors. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2021, 988, 164892. [Google Scholar] [CrossRef]

- Andreou, C.M.; González-Castaño, D.M.; Gerardin, S.; Bagatin, M.; Rodriguez, F.G.; Paccagnella, A.; Prokofiev, A.V.; Javanainen, A.; Virtanen, A.; Liberali, V.; et al. Low-Power, Subthreshold Reference Circuits for the Space Environment: Evaluated with γ-rays, X-rays, Protons and Heavy Ions. Electronics 2019, 8, 562. [Google Scholar] [CrossRef]

- Pude, M.; Mukund, P.; Singh, P.; Paradis, K.; Burleson, J. Amplifier gain enhancement with positive feedback. In Proceedings of the 2010 53rd IEEE International Midwest Symposium on Circuits and Systems, Seattle, WA, USA, 1–4 August 2010; pp. 981–984. [Google Scholar] [CrossRef]

- Dadashi, A.; Sadrafshari, S.; Hadidi, K.; Khoei, A. An enhanced folded cascode Op-Amp using positive feedback and bulk amplification in 0.35 μm CMOS process. Analog. Integr. Circuits Signal Process. 2010, 67, 213–222. [Google Scholar] [CrossRef]

- Dadashi, A.; Sadraf Shari, S.; Hadidi, K.; Khoei, A. Fast-settling CMOS op-amp with improved DC-gain. Analog Integr. Circuits Signal Process. 2012, 70, 283–292. [Google Scholar] [CrossRef]

- Safarian, M.R.; Moradi, G.; Toos, S.I. Gain and bandwidth enhancement in CMOS low voltage low-power operational amplifiers. Int. J. Comput. Appl. 2019, 177, 8–14. [Google Scholar]

- Millman, J.; Grabel, A. Microelectronics, 2nd ed.; Electronics Engineering Series; Mc Graw-Hill International: Singapore, 1987; pp. 564–602, 662–668. [Google Scholar]

- O’Connor, P.; De Geronimo, G. Prospects for charge sensitive amplifiers in scaled CMOS. In Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment; Elsevier: New York, NY, USA, 2002; Volume 480, pp. 713–725. [Google Scholar] [CrossRef]

- Chakraborty, S.; Pandey, A.; Nath, V. Ultra high gain CMOS Op-Amp design using self-cascoding and positive feedback. Microsyst. Technol. 2016, 23, 541–552. [Google Scholar] [CrossRef]

- Inaba, Y.; Nakamura, M.; Zuguchi, M.; Chida, K. Development of Novel Real-Time Radiation Systems Using 4-Channel Sensors. Sensors 2020, 20, 2741. [Google Scholar] [CrossRef] [PubMed]

- Valente, V.; Demosthenous, A. Wideband Fully-Programmable Dual-Mode CMOS Analogue Front-End for Electrical Impedance Spectroscopy. Sensors 2016, 16, 1159. [Google Scholar] [CrossRef]

- Rogalski, A.; Bielecki, Z.; Mikolajczyk, J. Detection of optical radiation. In Handbook of Optoelectronics; CRC Press: Warsaw, Poland, 2017; Volume 52, pp. 65–124. [Google Scholar]

- Kmon, P. Low-power low-area techniques for multichannel recording circuits dedicated to biomedical experiments. Bull. Pol. Acad. Sci. Tech. Sci. 2016, 64, 615–624. [Google Scholar] [CrossRef]

- McGregor, D.S. IMR-MIP: High-Detection-Efficiency and High-Spatial Resolution Thermal Neutron Imaging System for the Spallation Neutron Source Using Pixelated Semiconductor Neutron Sensors. NSF Grant Proposal Number 0412208, 31 August 2008. [Google Scholar]

- Geronimo, G.D.; Li, S. Shaper design in CMOS for high dynamic range. IEEE Trans. Nucl. Sci. 2011, 58, 2382–2390. [Google Scholar] [CrossRef]

- Re, V.; Manghisoni, M.; Ratti, L.; Speziali, V.; Traversi, G. Survey of noise performances and scaling effects in deep submicron CMOS devices from different foundries. In Proceedings of the IEEE Symposium Conference Record Nuclear Science 2004, Rome, Italy, 16–22 October 2004; Volume 13, pp. 68–72. [Google Scholar]

- Streel, G.D.; Bol, D. Study of back biasing schemes for ULV logic from the gate level to the IP level. J. Low Power Electron. Appl. 2014, 4, 168–187. [Google Scholar] [CrossRef]

- Ro, D.; Min, C.; Kang, M.; Chang, I.J.; Lee, H.-M. A Radiation-Hardened SAR ADC with Delay-Based Dual Feedback Flip-Flops for Sensor Readout Systems. Sensors 2019, 20, 171. [Google Scholar] [CrossRef]

- Jendernalik, W.; Jakusz, J.; Blakiewicz, G.; Piotrowski, R.; Szczepański, S. CMOS realisation of analogue processor for early vision processing. Bull. Pol. Acad. Sci. Tech. Sci. 2011, 59, 141–147. [Google Scholar] [CrossRef][Green Version]

- Zhao, H.; Liu, X. Modeling of a standard 0.35 µm CMOS technology Operating from 77K to 300K. Cryogenics 2014, 59, 49–59. [Google Scholar] [CrossRef]

- Bertuccio, G.; Caccia, S. Progress in ultra-low-noise ASICs for radiation sensors. Nucl. Instrum. Methods Phys. Res. Sect. A 2007, 579, 243–246. [Google Scholar] [CrossRef]

- Dao, N.C.; El Kass, A.; Azghadi, M.R.; Jin, C.T.; Scott, J.B.; Leong, P.H. An enhanced MOSFET threshold voltage model for the 6–300K temperature range. Microelectron. Reliab. 2017, 69, 36–39. [Google Scholar] [CrossRef]

- Seljak, A.; Cumming, H.S.; Varner, G.; Vallerga, J.; Raffanti, R.; Virta, V. A fast, low power and low noise charge sensitive amplifier ASIC for a UV imaging single photon sensor. J. Instrum. 2017, 7, C01003. [Google Scholar]

- Kawamura, T.; Orita, T.; Takeda, S.; Watanabe, S.; Ikeda, H.; Takahashi, T. Development of a low-noise front-end ASIC for CdTe detectors. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2020, 982, 164575. [Google Scholar] [CrossRef]

- Ciciriello, F.; Corsi, F.; Robertis, G.D.; Felici, G.; Loddo, F.; Marzocca, C.; Matarrese, G.; Ranieri, A. A new front-end asic for GEM sensors with time and charge measurement capabilities. Nucl. Instrum. Methods Phys. Res. Sect. A 2016, 824, 265–267. [Google Scholar] [CrossRef]

- Baur, R.; Ernst, P.; Gramegna, G.; Richter, M. Frond-electronics for the CERES TPC-sensor. Nucl. Instrum. Methods Phys. Res. Sect. A 1998, 409, 278–285. [Google Scholar] [CrossRef]

- Pichler, B.; Pimpl, W.; Büttler, W.; Kotoulas, L.; Böning, G.; Rafecas, M.; Lorenz, E.; Ziegler, S. Integrated low-noise low-power fast charge-sensitive preamplifier for avalanche photodiodes in JFET-CMOS technology. IEEE Trans. Nucl. Sci. 2001, 48, 2370–2374. [Google Scholar] [CrossRef]

- Chawla, T.; Marchal, S.A.; Amara, A.; Vladimirescu, A. Local mismatch in 45 nm digital clock networks. In Proceedings of the 12th International Symposium on Integrated Circuits, Singapore, 14–16 December 2009; pp. 466–469. [Google Scholar]

- Llopart, X.; Alozy, J.; Ballabriga, R.; Campbell, M.; Egidos, N.; Fernandez, J.M.; Heijne, E.; Kremastiotis, I.; Santin, E.; Tlustos, L.; et al. Study of low power front-ends for hybrid pixel sensors with sub-ns time tagging. J. Instrum. 2019, 14, C01024. [Google Scholar] [CrossRef]

- Pullia, A.; Capra, S. Experimental performance of a highly innovative low-noise charge-sensitive preamplifier with integrated range-boosted. J. Instrum. 2018, 13, C12004. [Google Scholar] [CrossRef]

- Folla, J.K.; Crespo, M.L.; Wembe, E.T.; Bhuiyan, M.A.S.; Cicuttin, A.; Essimbi, B.Z.; Reaz, M.B.I. A low-offset low-power and high-speed dynamic latch comparator with a preamplifier-enhanced stage. IET Circuits Devices Syst. 2021, 15, 65–77. [Google Scholar] [CrossRef]

- Qi, M.; Guo, A.-Q.; Qiao, D.-H. A High-Temperature, Low-Noise Readout ASIC for MEMS-Based Accelerometers. Sensors 2019, 20, 241. [Google Scholar] [CrossRef] [PubMed]

- Prayer, P.; Blagojevic, B.; Haendler, M.; Valentian, S.; Amara, A.; Flatresse, P. Performance analysis of multi-VT design solutions in 28 nm UTBB FD-SOI technology. In Proceedings of the 2013 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Monterey, CA, USA, 7–10 October 2013; pp. 1–2. [Google Scholar]

- Karel, A.; Comte, M.; Galliere, J.-M.; Azais, F.; Renovell, M. Impact of VT and Body-Biasing on Resistive Short Detection in 28 nm UTBB FDSOI—LVT and RVT Configurations. In Proceedings of the 2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Pittsburgh, PA, USA, 11–13 July 2016; pp. 164–169. [Google Scholar] [CrossRef]

- Sharrouh, S.M. Design of CMOS inverter-based amplifier: A quantitative approach. Int. J. Circuit Theory Appl. 2019, 47, 1006–1036. [Google Scholar] [CrossRef]

| Vendor Parameters | Hamamatsu (H4083) | AMPTEK (A250) |

|---|---|---|

| Power consumption | 50 mW@12 V | 14 m W@6 V |

| Count rate | 2.6 MHz | 2.5 MHz |

| Sensor capacitance | 0–25 pF | 0–250 pF |

| ENC (Cin = 5 pF) | 240 e− | 6 e− |

| Noise slope | 4 e−/pF | 11.5 e−/pF |

| Sensitivity | 22 mV/MeV (Si) | 176 mV/MeV (Si) |

| DC gain | 94 dB | 76 dB |

| Transistor W/L(µm/µm) | gmk Value (µS) | Capacitance/λ |

|---|---|---|

| M1—62.5/10.5 | gm1—61.4 | CL = 1 pF |

| M2—0.84/0.35 M3—18/0.35 M4,5,6—12/0.35 | gm2—12.28 gm3—50 gm4,5,6—20 | Cm = 50 fF CF = 100 fF C1 = 0.74 fF |

| M7—9/0.35 | gm7—200 | C2 = 1.82 fF |

| M8,9—10/0.35 MF—3/36 MP—2.772/0.7 Md—2/23.6 | gm8,9—12 gmF—13.13 gmF—704.2 gmd—2.88 | Cd = 534 fF Ci = 200 fF CL2 = 1 pF |

| Mi—10/41 | gmi—3.27 | λ = 0.0746 |

| M1sh—3/20 M2sh—0.63/59.25 | gmish—4.67 gm2sh—0.467 g03,08—0.1865 |

| Parameters | This Work | [26] | [49] | [45] | [17] | [22] |

|---|---|---|---|---|---|---|

| CMOS Technology | 0.35 µm | 0.18 µm | 0.35 µm | 0.13 µm | 0.35 µm | 0.18 µm |

| Power Supply | 3.3 V | 1.8 V | ±1.65 V | 1.2 V | 3.3 V | 1.8 V |

| Power Consumption | 8.72 µW | 8.7 mW | 2.1 mW | 4.8 mW | -- | 2.1 µW |

| Input Parasitic Capacitance | 0.2–2 pF | 0.1 pF | 17 pF | 5 pF | 10 pF | - |

| Gain/Operating Bandwidth | 88 dB/1 GHz | --/9.1 GHz | --- | - | 60 dB/5.1 kHz | - |

| ENC | 37.6 e− + 16.32 e− /pF | 278.2 e− + 26.6 e−/pF | 58.4 e− + 12.7 e−/pF | 600 e− + 100 e−/pF | 650 e− | - |

| Amplifier Gain (mV/MeV) | 546.56/920.66 | 513.67/1740.2 | 9366.45 | 550.96 | 826.45 | 0.044 |

| Active area (mm2) | 0.0205 | 0.093 | 47.64 | 0.7225 | 0.75 | 0.038 |

| Input Dynamic Peaking time | 0–280 fC 214 ns | 0–15 fC 40 ns/250 ns | 6 fC 500 ns/2 us | 0–60 fC 100 ns | 80 fC --- | 450 pC --- |

| Figure of merit (FOM) (MHz/µW) | 116.82 | 1.05 | -- | 0.002 | - | 14.29 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jérôme, F.K.; Evariste, W.T.; Bernard, E.Z.; Crespo, M.L.; Cicuttin, A.; Reaz, M.B.I.; Bhuiyan, M.A.S. An 8.72 µW Low-Noise and Wide Bandwidth FEE Design for High-Throughput Pixel-Strip (PS) Sensors. Sensors 2021, 21, 1760. https://doi.org/10.3390/s21051760

Jérôme FK, Evariste WT, Bernard EZ, Crespo ML, Cicuttin A, Reaz MBI, Bhuiyan MAS. An 8.72 µW Low-Noise and Wide Bandwidth FEE Design for High-Throughput Pixel-Strip (PS) Sensors. Sensors. 2021; 21(5):1760. https://doi.org/10.3390/s21051760

Chicago/Turabian StyleJérôme, Folla Kamdem, Wembe Tafo Evariste, Essimbi Zobo Bernard, Maria Liz Crespo, Andres Cicuttin, Mamun Bin Ibne Reaz, and Mohammad Arif Sobhan Bhuiyan. 2021. "An 8.72 µW Low-Noise and Wide Bandwidth FEE Design for High-Throughput Pixel-Strip (PS) Sensors" Sensors 21, no. 5: 1760. https://doi.org/10.3390/s21051760

APA StyleJérôme, F. K., Evariste, W. T., Bernard, E. Z., Crespo, M. L., Cicuttin, A., Reaz, M. B. I., & Bhuiyan, M. A. S. (2021). An 8.72 µW Low-Noise and Wide Bandwidth FEE Design for High-Throughput Pixel-Strip (PS) Sensors. Sensors, 21(5), 1760. https://doi.org/10.3390/s21051760