An 18.8–33.9 GHz, 2.26 mW Current-Reuse Injection-Locked Frequency Divider for Radar Sensor Applications

Abstract

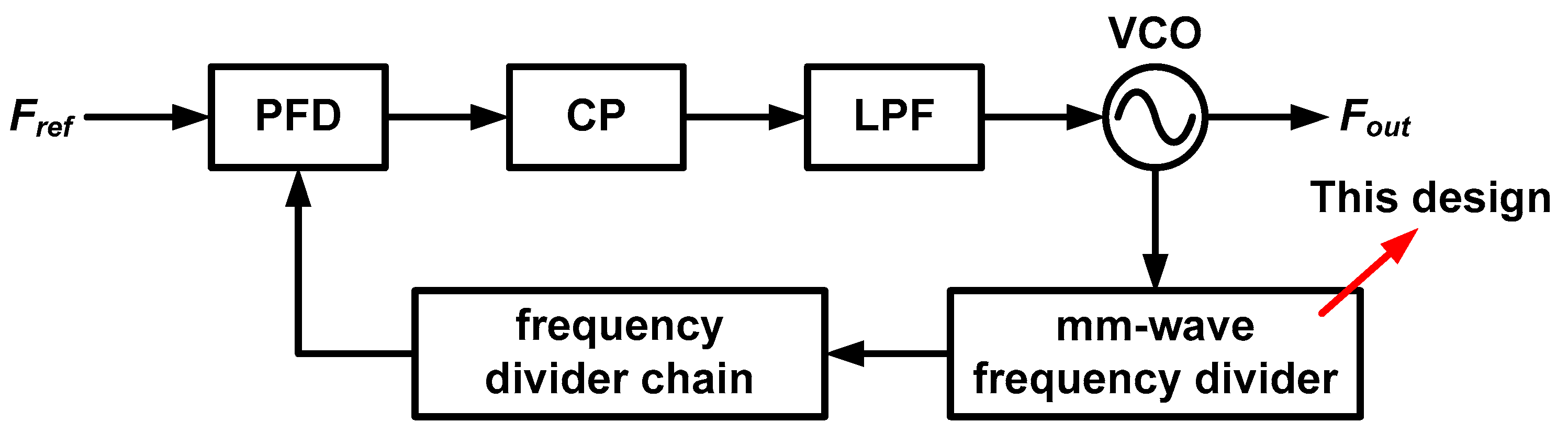

1. Introduction

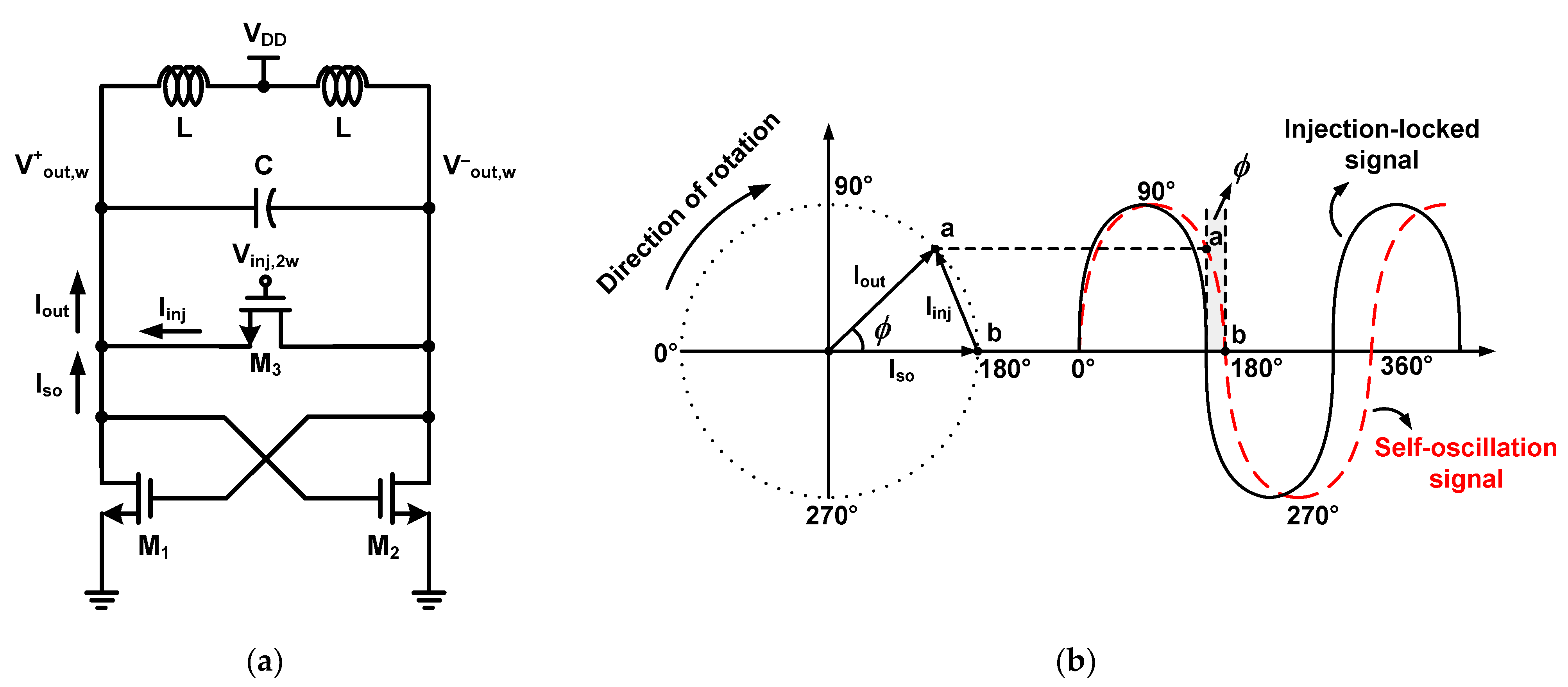

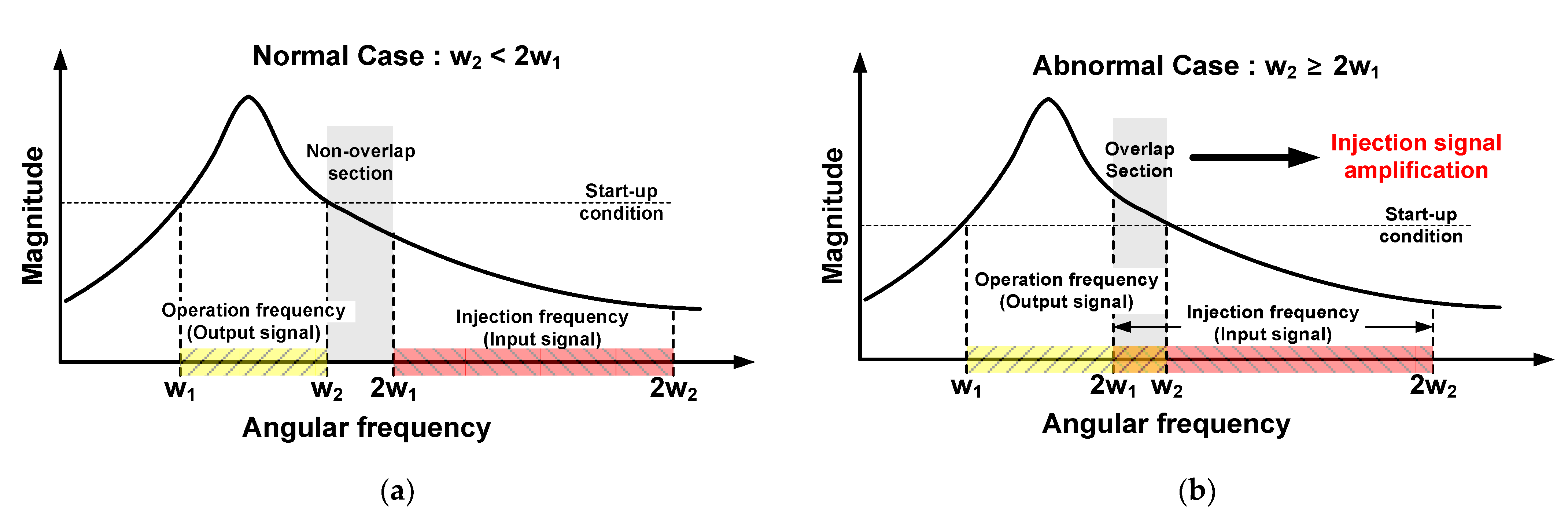

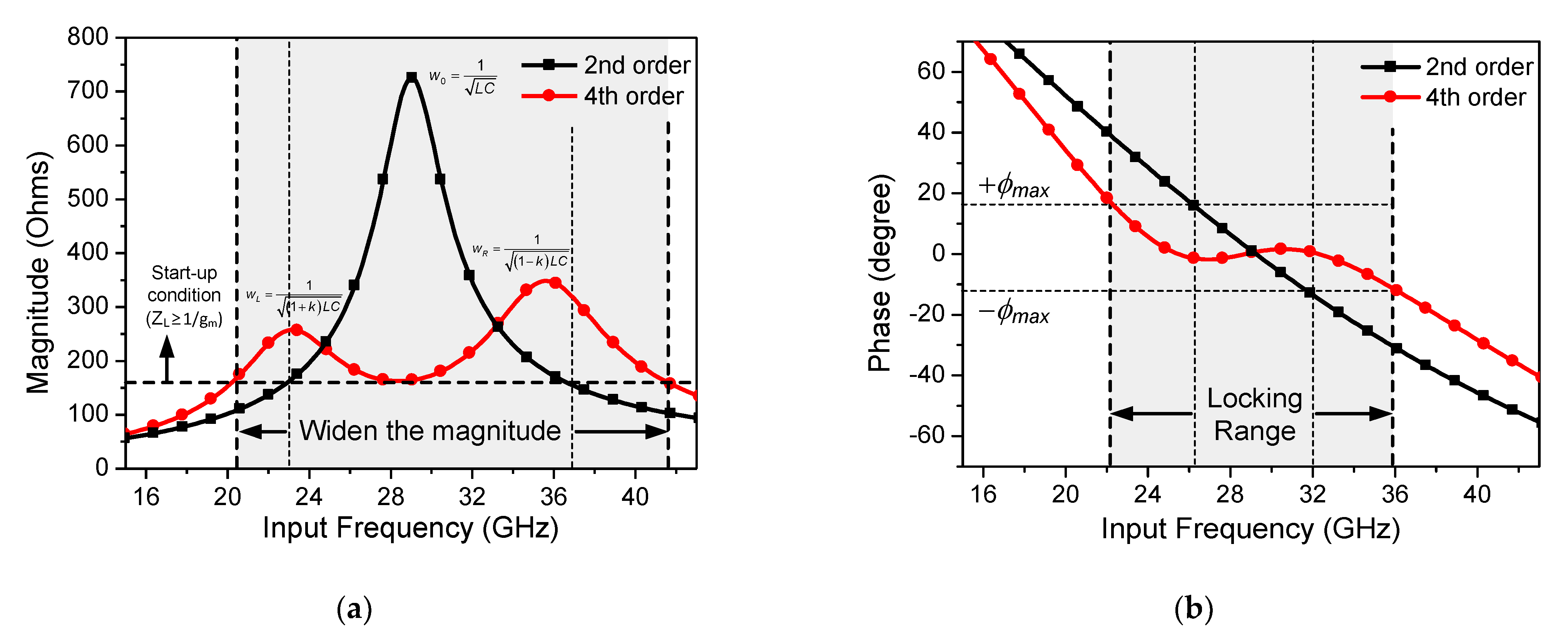

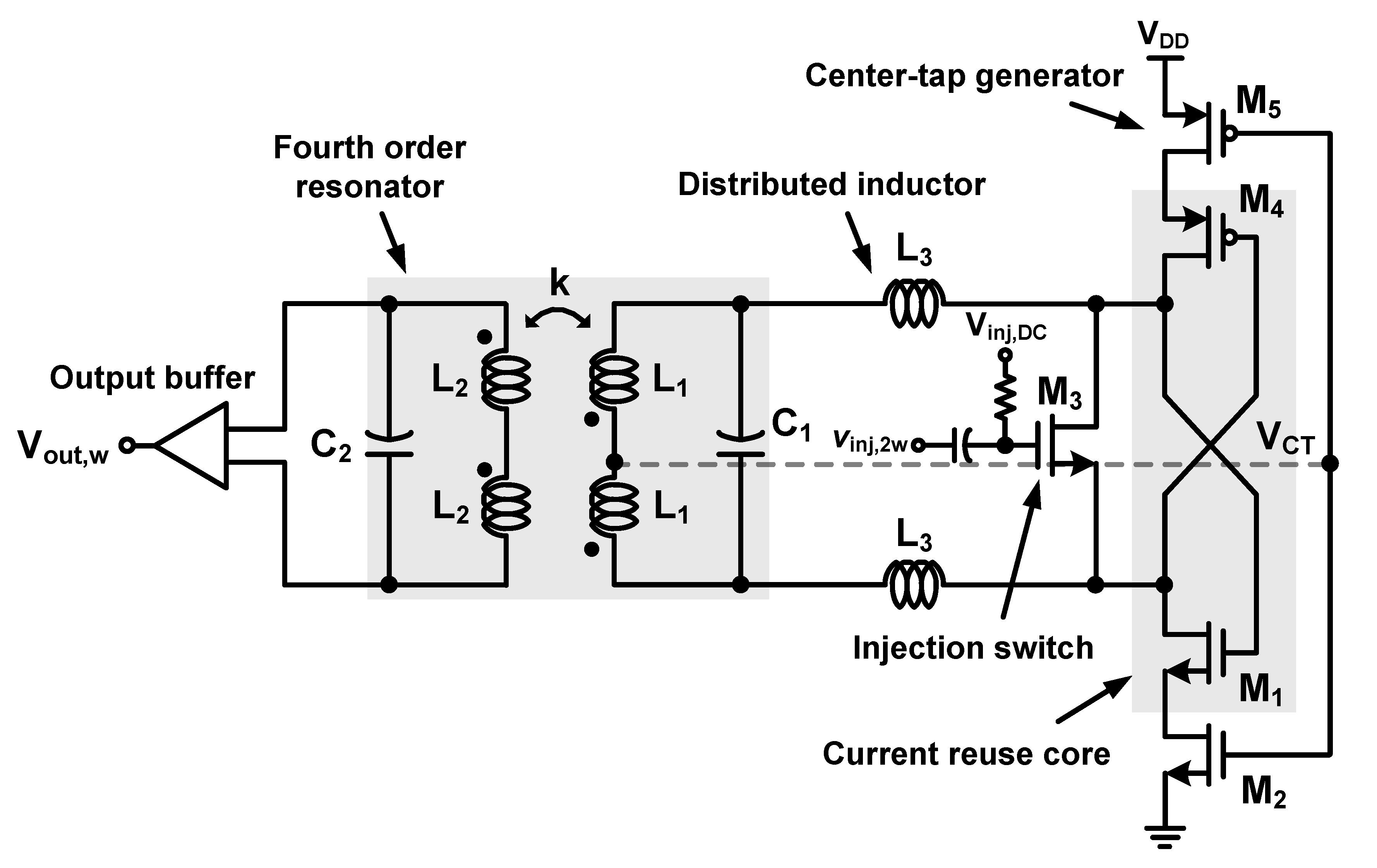

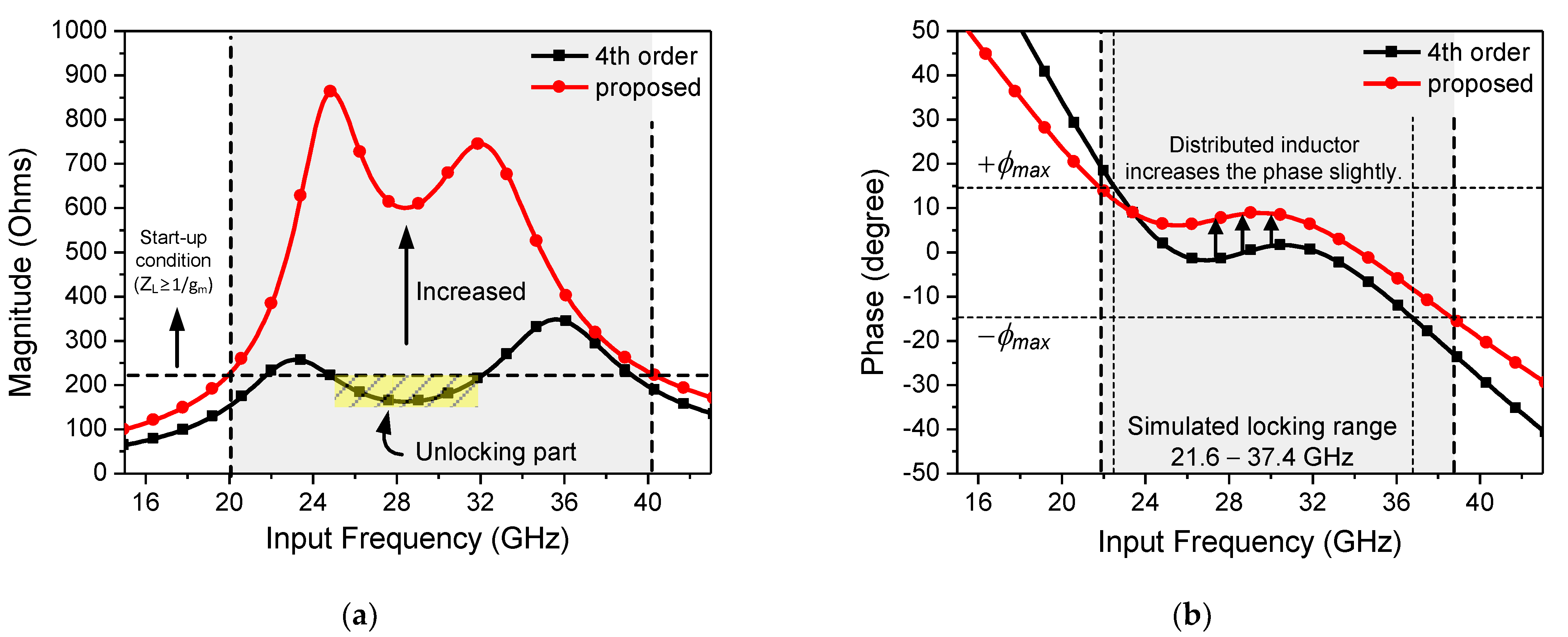

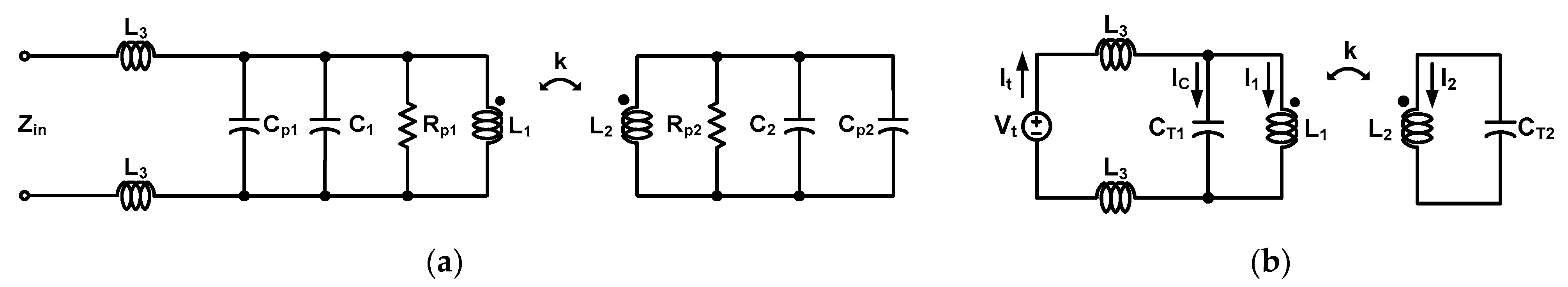

2. Locking Range Analysis of ILFD

3. Circuit Design of Proposed CR-ILFD

3.1. Fourth-Order Resonator and CR Core

3.2. Proposed CR-ILFD

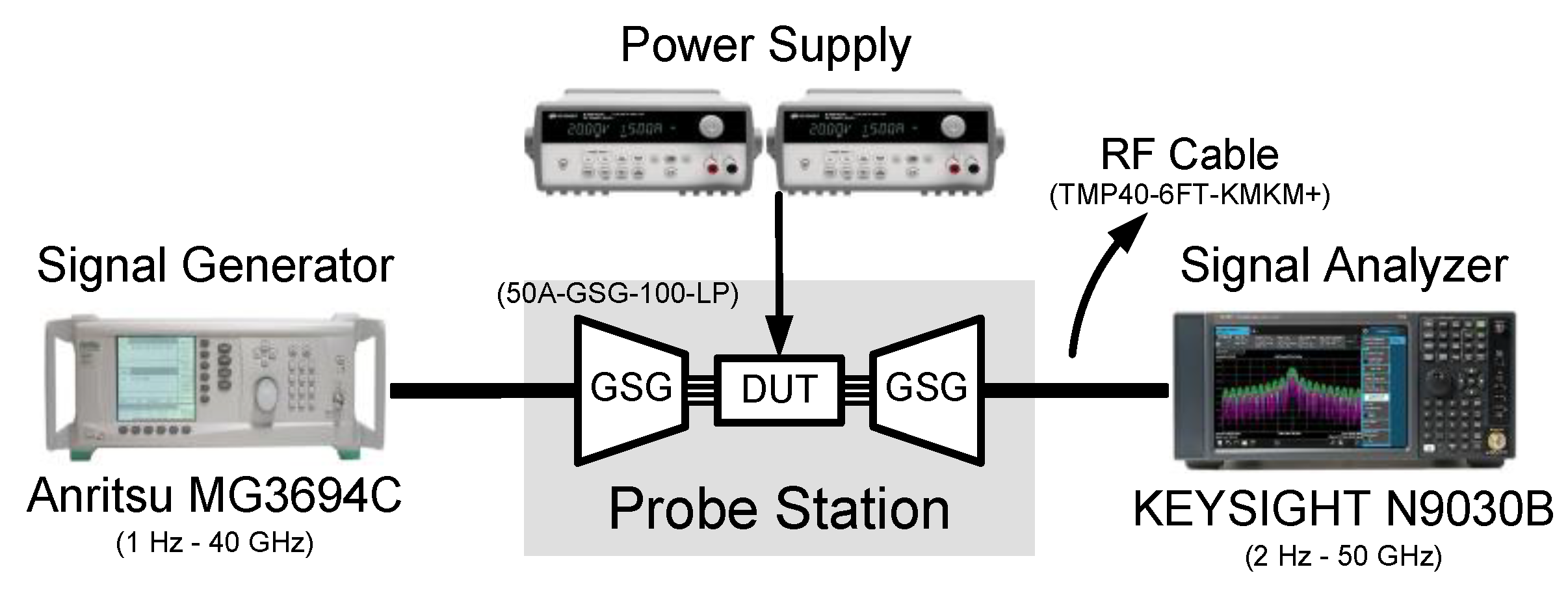

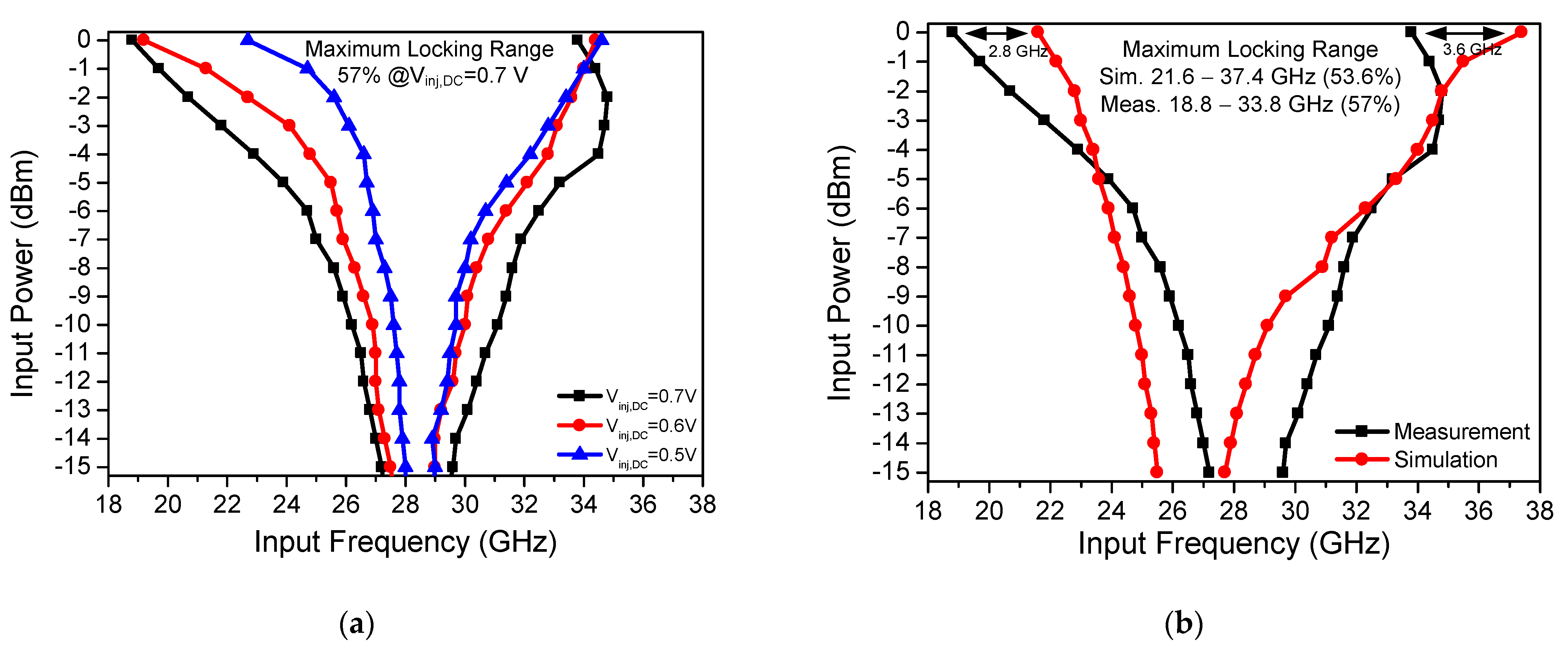

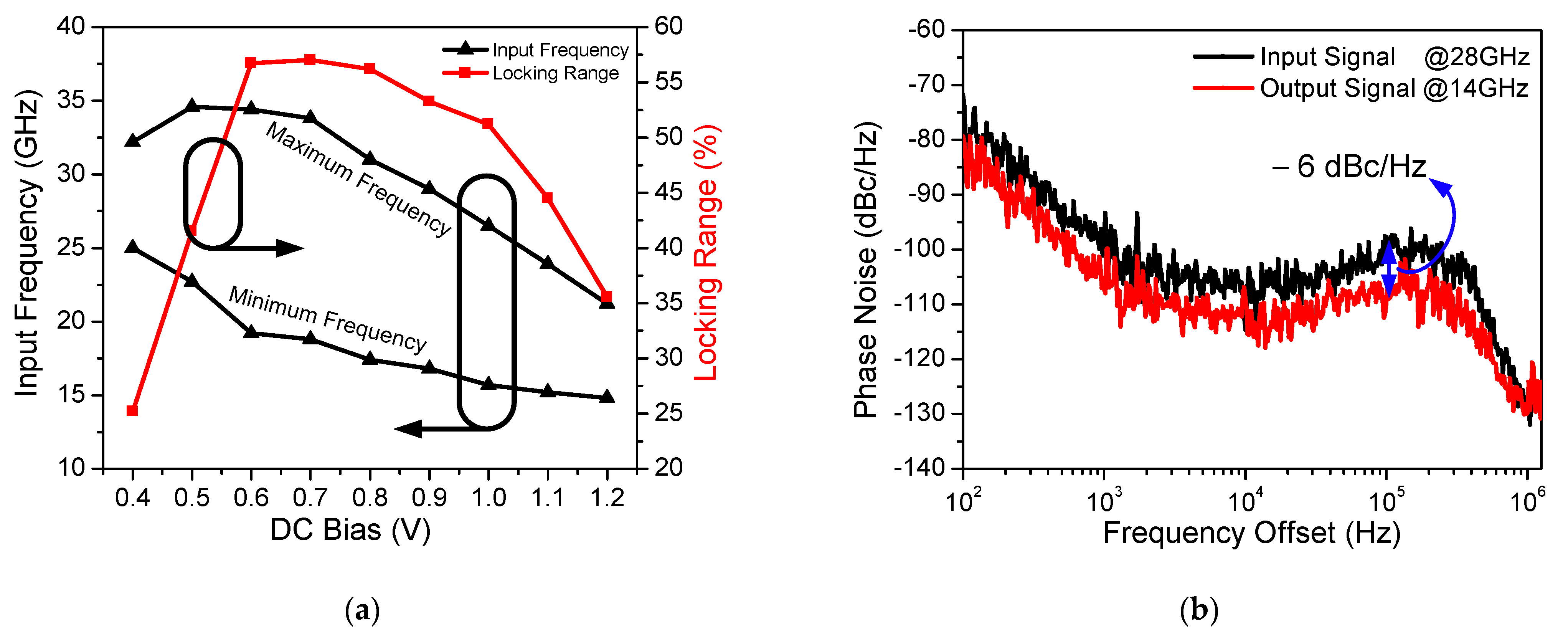

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kim, K.-R.; Kim, J.-H. Wideband Waveform Generation Using MDDS and Phase Compensation for X-Band SAR. Sensors 2020, 12, 1431. [Google Scholar] [CrossRef]

- Song, J.-H.; Lee, K.-W.; Lee, W.-K.; Jung, C.-H. High Resolution Full-Aperture ISAR Processing through Modified Doppler History Based Motion Compensation. Sensors 2017, 12, 1234. [Google Scholar] [CrossRef] [PubMed]

- Park, J.; Ryu, H.; Ha, K.-W.; Kim, J.-G.; Baek, D. 76–81-GHz CMOS Transmitter with a Phase-Locked-Loop-Based Multichirp Modulator for Automotive Radar. IEEE Trans. Microw. Theory Tech. 2015, 63, 1399–1408. [Google Scholar] [CrossRef]

- Ek, S.; Pahlsson, T.; Elgaard, C.; Carlsson, A.; Axholt, A.; Stenman, A.K.; Sundstrom, L.; Sjoland, H. A 28-nm FD-SOI 115-fs Jitter PLL-Based LO System for 24-30-GHz Sliding-IF 5G Transceivers. IEEE J. Solid-State Circuits 2018, 53, 1988–2000. [Google Scholar] [CrossRef]

- Wang, H.-N.; Huang, Y.-W.; Chung, S.-J. Spatial Diversity 24-GHz FMCW Radar with Ground Effect Compensation for Automotive Applications. IEEE Trans. Veh. Technol. 2017, 66, 965–973. [Google Scholar] [CrossRef]

- Lee, J.-Y.; Kim, G.S.; Ko, G.-H.; Oh, K.-I.; Park, J.G.; Baek, D. Low Phase Noise and Wide-Range Class-C VCO Using Auto-Adaptive Bias Technique. Electronics 2020, 9, 1290. [Google Scholar] [CrossRef]

- Kang, C.-W.; Moon, H.; Yang, J.-R. Switched-Biasing Techniques for CMOS Voltage-Controlled Oscillator. Sensors 2021, 21, 316. [Google Scholar] [CrossRef] [PubMed]

- Oh, K.-I.; Kim, G.S.; Park, J.-G.; Ko, G.-H.; Baek, D. Fourth-order Resonator based Current Reuse Injection-Locking Frequency Divider with Peaking Inductor. In Proceedings of the 2019 Asia-Pacific Microwave Conference (APMC), Singapore, 10–13 December 2019; pp. 1421–1423. [Google Scholar]

- Zhao, X.; Chen, Y.; Mak, P.-I.; Martins, R. A 0.0018-mm2 153% Locking-Range CML-Based Divider-by-2 With Tunable Self-Resonant Frequency Using an Auxiliary Negative-gm Cell. IEEE Trans. Circuits Syst. I Reg. Pap. 2019, 66, 3330–3339. [Google Scholar] [CrossRef]

- Chen, Y.; Yang, Z.; Zhao, X.; Huang, Y.; Mak, P.-I.; Martins, R.P. A 6.5 × 7 μm2 0.98-to-1.5 mW Nonself-Oscillation-Mode Frequency Divider-by-2 Achieving a Single-Band Untuned Locking Range of 166.6% (4–44 GHz). IEEE J. Solid-State Circuits Lett. 2019, 2, 37–40. [Google Scholar] [CrossRef]

- Ghilioni, A.; Mazzanti, A.; Svelto, F. Analysis and design of mm-Wave frequency dividers based on dynamic latches with load modulation. IEEE J. Solid-State Circuits 2013, 48, 1842–1850. [Google Scholar] [CrossRef]

- Hussein, A.I.; Paramesh, J. Design and Self-Calibration Techniques for Inductor-Less Millimeter-Wave Frequency Dividers. IEEE J. Solid-State Circuits 2017, 52, 1521–1541. [Google Scholar] [CrossRef]

- Lin, Y.-H.; Wang, H. A 35.7-64.2 GHz low power Miller Divider with Weak Inversion Mixer in 65 nm CMOS. IEEE Microw. Wireless Compon. Lett. 2016, 26, 948–950. [Google Scholar] [CrossRef]

- Lin, Y.-S.; Huang, W.-H.; Lu, C.-L.; Wang, Y.-H. Wide-Locking-Range Multi-Phase-Outputs Regenerative Frequency Dividers Using Even-Harmonic Mixers and CML Loop Dividers. IEEE Trans. Microw. Theory Tech. 2014, 62, 3065–3075. [Google Scholar] [CrossRef]

- Kuo, Y.-H.; Tsai, J.-H.; Huang, T.-W.; Wang, H. Design and Analysis of Digital-Assisted Bandwidth-Enhanced Miller Divider in 0.18- m CMOS Process. IEEE Trans. Microw. Theory Tech. 2012, 60, 3769–3777. [Google Scholar] [CrossRef]

- Chen, Y.-T.; Li, S.-W.; Huang, T.-H.; Chuang, H.-R. V-Band CMOS Direct Injection-Locked Frequency Divider Using Forward Body Bias Technology. IEEE Microw. Wireless Compon. Lett. 2010, 20, 396–398. [Google Scholar] [CrossRef]

- Cheng, Y.-H.; Tsai, J.-H.; Huang, T.-H. Design of a 90.9% Locking Range Injection-Locked Frequency Divider with Device Ratio Optimization in 90-nm CMOS. IEEE Trans. Microw. Theory Tech. 2017, 65, 187–197. [Google Scholar] [CrossRef]

- Jang, S.-L.; Lai, W.-C.; Ciou, Y.-L.; Hou, J.C. Divide-by-2 Injection-Locked Frequency Dividers Using the Electric-Field Coupling Dual-Resonance Resonator. IEEE Trans. Microw. Theory Tech. 2020, 68, 844–853. [Google Scholar] [CrossRef]

- Zou, Q.; Ma, K.; Yeo, K.S. A V-Band Wide Locking Range Divide-by-4 Injection-Locked Frequency Divider. IEEE Microw. Wireless Compon. Lett. 2018, 28, 1020–1022. [Google Scholar] [CrossRef]

- Kim, J.; Lee, S.; Choi, D.-H. Injection-Locked Frequency Divider Topology and Design Techniques for Wide Locking-Range and High-Order Division. IEEE Access 2016, 5, 4410–4417. [Google Scholar] [CrossRef]

- Zhang, J.; Cheng, Y.; Zhao, C.; Wu, Y.; Kang, K. Analysis and Design of Ultra-Wideband mm-Wave Injection-Locked Frequency Dividers Using Transformer-Based High-Order Resonators. IEEE J. Solid-State Circuits 2018, 53, 2177–2189. [Google Scholar] [CrossRef]

- Chao, Y.; Luong, H. Analysis and Design of Wide-Band Millimeter-Wave Transformer-Based VCO and ILFDs. IEEE Trans. Circuits Syst. I Reg. Pap. 2016, 63, 1416–1425. [Google Scholar] [CrossRef]

- Ha, K.-W.; Ryu, H.; Lee, J.-H.; K, J.-G.; Baek, D. Gm-Boosted Complementary Current-Reuse Colpitts VCO With Low Power and Low Phase Noise. IEEE Microw. Wireless Compon. Lett. 2014, 24, 418–420. [Google Scholar] [CrossRef]

- Ha, K.-W.; Ryu, H.; Park, J.; K, J.-G.; Baek, D. Transformer-Based Current-Reuse Armstrong and Armstrong-Colpitts VCOs. IEEE Trans. Circuits Syst. II Exp. Briefs 2014, 61, 676–680. [Google Scholar] [CrossRef]

- Ryu, H.; Ha, K.W.; Baek, D. Low-power quadrature voltage-controlled oscillator using current-reuse and transformer-based Armstrong topologies. Electron. Lett. 2016, 52, 462–464. [Google Scholar] [CrossRef]

- Yun, S.J.; Shin, S.-B.; Choi, H.-C.; Lee, S.-G. A 1mW Current-Reuse CMOS Differential LC-VCO with Low Phase Noise. In Proceedings of the 2005 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2005; pp. 540–541. [Google Scholar]

- Ha, K.-W.; Sung, E.-T.; Baek, D. Low-power transformer-based current-reuse injection-locked frequency divider. Electron. Lett. 2015, 51, 161–162. [Google Scholar] [CrossRef]

- Lee, I.-T.; Tsai, K.-H.; Liu, S.-I. A 104- to 112.8-GHz CMOS Injection-Locked Frequency Divider. IEEE Trans. Circuits Syst. II Exp. Briefs 2009, 56, 555–559. [Google Scholar]

- Lin, B.-Y.; Liu, S.-I. Analysis and Design of D-Band Injection-Locked Frequency Dividers. IEEE J. Solid-State Circuits 2011, 46, 1250–1264. [Google Scholar] [CrossRef]

- Chine, K.-H.; Chen, J.-Y.; Chiou, H.-K. Designs of K-Band Divide-by-2 and Divide-by-3 Injection-Locked Frequency Divider with Darlington Topology. IEEE Trans. Microw. Theory Tech. 2015, 63, 2877–2888. [Google Scholar] [CrossRef]

- Jang, S.-L.; Luo, J.-C.; Chang, C.-W.; Lee, C.-F.; Huang, J.-F. LC-Tank Colpitts Injection-Locked Frequency Divider with Even and Odd Modulo. IEEE Microw. Wireless Compon. Lett. 2009, 19, 113–115. [Google Scholar] [CrossRef]

- Jang, S.-L.; Huang, S.-H.; Lee, C.-F.; Juang, M.-H. LC-Tank Colpitts Injection-Locked Frequency Divider with Record Locking Range. IEEE Microw. Wireless Compon. Lett. 2008, 18, 560–562. [Google Scholar] [CrossRef]

- Mahalingam, N.; Ma, K.; Yeo, K.-S.; Lim, W.-M. Coupled Dual LC Tanks Based ILFD With Low Injection Power and Compact Size. IEEE Microw. Wireless Compon. Lett. 2014, 24, 105–107. [Google Scholar] [CrossRef]

- Wu, J.-W.; Tu, C.-H.; Chen, S.-W.; Chen, C.-C.; Hsiao, H.-F.; Chang, D.C. Low Power Consumption and Wide Locking Range Triple-Injection-Locked Frequency Divider by Two. In Proceedings of the 2015 Asia-Pacific Microwave Conference (APMC), Nanjing, China, 6–9 December 2015; pp. 1–3. [Google Scholar]

- Jang, S.-L.; Jina, S.-J.; Hsue, C.-W. Wideband Divide-by-4 Injection-Locked Frequency Divider Using Harmonic Mixer. IEEE Microw. Wireless Compon. Lett. 2017, 27, 924–926. [Google Scholar] [CrossRef]

- Mahalingam, N.; Ma, K.; Yeo, K.S.; Lim, W.M. Modified Inductive Peaking Direct Injection ILFD With Multi-Coupled Coils. IEEE Microw. Wireless Compon. Lett. 2015, 25, 379–381. [Google Scholar] [CrossRef]

- Wu, L.; Luong, H. Analysis and Design of a 0.6 V 2.2 mW 58.5-to-72.9 GHz Divide-by-4 Injection-Locked Frequency Divider with Harmonic Boosting. IEEE Trans. Circuits Syst. I Reg. Pap. 2013, 60, 2001–2008. [Google Scholar] [CrossRef]

- Kuo, Y.-H.; Tsai, J.-H.; Chang, H.-Y.; Tsai, T.-W. Design and Analysis of a 77.3% Locking-Range Divide-by-4 Frequency Divider. IEEE Trans. Microw. Theory Tech. 2011, 59, 2477–2485. [Google Scholar] [CrossRef]

- Imani, A.; Hashemi, H. Distributed Injection-Locked Frequency Dividers. IEEE J. Solid-State Circuits 2017, 52, 2083–2093. [Google Scholar] [CrossRef]

- Chen, H.-K.; Chen, H.H.; Chang, D.-C.; Juang, Y.-Z.; Yang, Y.-C.; Lu, S.-S. A mm-Wave CMOS Multimode Frequency Divider. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 280–282. [Google Scholar]

- Chang, H.-Y.; Chen, W.-C.; Yeh, H.-N.; Shen, I.Y.-E. A V-Band CMOS Low-DC-Power Wide-Locking-Range Divide-by-6 Injection-Locked Frequency Divider Using Transformer Coupling. IEEE Microw. Wireless Compon. Lett. 2020, 30, 593–596. [Google Scholar] [CrossRef]

| Design Parameter | Value |

|---|---|

| M1, M2, M4, M5 (unit W/L) | 2 μm/0.06 μm |

| M3 (unit W/L) | 1 μm/0.06 μm |

| Finger of M1, M3, M4 | 20 |

| Finger of M2, M5 | 50 |

| L1 | 230 pH |

| L2 | 265 pH |

| L3 | 433 pH |

| k | 0.51 |

| C1 | 144 fF |

| C2 | 240 fF |

| This Work | [30] 15′MTT | [31] 09′MWCL | [32] 08′MWCL | [33] 14′MWCL | [34] 15′APMC | [35] 17′MWCL | |

|---|---|---|---|---|---|---|---|

| Technology | 65-nm CMOS | 0.18-μm CMOS | 0.18-μm CMOS | 0.18-μm CMOS | 0.18-μm SiGe BiCMOS | 0.18-μm CMOS | 0.18-μm CMOS |

| Core topology | Current reuse | Darlington | Armstrong | Colpitts + Current reuse | Complementary cross-coupled pair | NMOS cross-coupled pair | NMOS cross-coupled pair |

| Self-oscillation frequency (GHz) | 14.08 | N/A | 4.77–5.08 (w/varactor) | 5.85–6.17 (w/varactor) | N/A | N/A | 2.97–4.66 (w/varactor) |

| Input signal power (dBm) | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Division ratio | 2 | 2 | 2 | 2 | 2 | 2 | 4 |

| Input frequency range (GHz) | 18.8–33.8 | 20.5–22.9 | 7.7–11.5 | 7.3–14.4 | 20.1–25.9 | 10.2–15.5 | 13–19 |

| Locking range (%) | 57 | 11 | 39.6 | 65.4 | 25.1 | 41.4 | 37.5 * |

| Supply voltage (V) | 1 | 1.2 | 1.4 | 1.5 | 1.8 | 1.2 | 0.8 |

| Power consumption of core (mW) | 2.26 | 1.73 | 9.02 | 7.65 | 4.8 | 2.71 | 7.09 |

| Phase noise (dBc/Hz @1 MHz) | −129.81 (14 GHz) | −138.3 (N/A) | −134.942 (4.9 GHz) | −134.8 (6 GHz) | −124 (12.5 GHz) | −120.53 (5.495 GHz) @ 100 kHz | −133.26 (4 GHz) |

| FOM1 (GHz/mW) | 6.64 | 1.38 | 0.42 | 0.93 | 1.21 | 1.96 | 0.85 |

| FOM2 (GHz/mW) | 13.28 | 2.76 | 0.84 | 1.86 | 2.42 | 3.92 | 3.4 |

| Chip size (mm2) | 0.75 × 0.45 | 0.8 × 0.75 | 0.55 × 0.74 | 0.46 × 0.52 | 0.75 × 0.78 | 0.57 × 0.68 | 1.01 × 1.18 |

| This Work | [36] 15′MWCL | [37] 13′TCAS1 | [38] 11′MTT | [39] 17′JSSC | [40] 09′ISSCC | [41] 20′MWCL | |

|---|---|---|---|---|---|---|---|

| Technology | 65-nm CMOS | 65-nm CMOS | 65-nm CMOS | 0.13-μm CMOS | 0.13-μm CMOS | 0.13-μm CMOS | 90-nm CMOS |

| Self-oscillation frequency (GHz) | 14.08 | 17.5 | N/A | 5.9 | 25.9 | N/A | 9.7 |

| Input signal power (dBm) | 0 | 0 | 0 | 0 | 0 | 0 | −5 |

| Division ratio | 2 | 2 | 4 | 4 | 2 | 2 | 6 |

| Input frequency range (GHz) | 18.8–33.8 | 31.7–39.3 | 58.5–72.9 | 13.5–30.5 | 35–4441–59.5 | 35.6–39.3 | 54.5–60.1 |

| Locking range (%) | 57 | 21.4 | 21.9 | 77.3 | 53 * | 9.9 | 9.8 |

| Supply Voltage (V) | 1 | 1 | 0.6 | 1.4 | 1.15 | 1 | N/A |

| Power consumption of core (mW) | 2.26 | 2.5 | 2.2 | 7.3 | 3.8 | 3.12 | 5.6 |

| Phase noise (dBc/Hz @1 MHz) | –129.81 (14 GHz) | –102 (N/A) | –126.74 (N/A) | –137.4 (6 GHz) | –124 (24 GHz) | –133.7 (N/A) | –140 (9.7 GHz) |

| FOM1 (GHz/mW) | 6.64 | 3.04 | 6.54 | 2.33 | 6.45 | 1.19 | 1 |

| FOM2 (GHz/mW) | 13.28 | 6.08 | 26.16 | 9.32 | 12.9 | 2.38 | 6 |

| Chip size (mm2) | 0.75 × 0.45 | 0.6 × 0.75 | 0.16 × 0.26 | 0.52 × 0.64 | 1 × 0.9 | 0.13 × 0.18 ** | 0.83 × 0.61 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Oh, K.-I.; Ko, G.-H.; Kim, J.-G.; Baek, D. An 18.8–33.9 GHz, 2.26 mW Current-Reuse Injection-Locked Frequency Divider for Radar Sensor Applications. Sensors 2021, 21, 2551. https://doi.org/10.3390/s21072551

Oh K-I, Ko G-H, Kim J-G, Baek D. An 18.8–33.9 GHz, 2.26 mW Current-Reuse Injection-Locked Frequency Divider for Radar Sensor Applications. Sensors. 2021; 21(7):2551. https://doi.org/10.3390/s21072551

Chicago/Turabian StyleOh, Kwang-Il, Goo-Han Ko, Jeong-Geun Kim, and Donghyun Baek. 2021. "An 18.8–33.9 GHz, 2.26 mW Current-Reuse Injection-Locked Frequency Divider for Radar Sensor Applications" Sensors 21, no. 7: 2551. https://doi.org/10.3390/s21072551

APA StyleOh, K.-I., Ko, G.-H., Kim, J.-G., & Baek, D. (2021). An 18.8–33.9 GHz, 2.26 mW Current-Reuse Injection-Locked Frequency Divider for Radar Sensor Applications. Sensors, 21(7), 2551. https://doi.org/10.3390/s21072551