An Analysis of Noise in Multi-Bit ΣΔ Modulators with Low-Frequency Input Signals

Abstract

:1. Introduction

2. Materials and Methods

2.1. Related Work

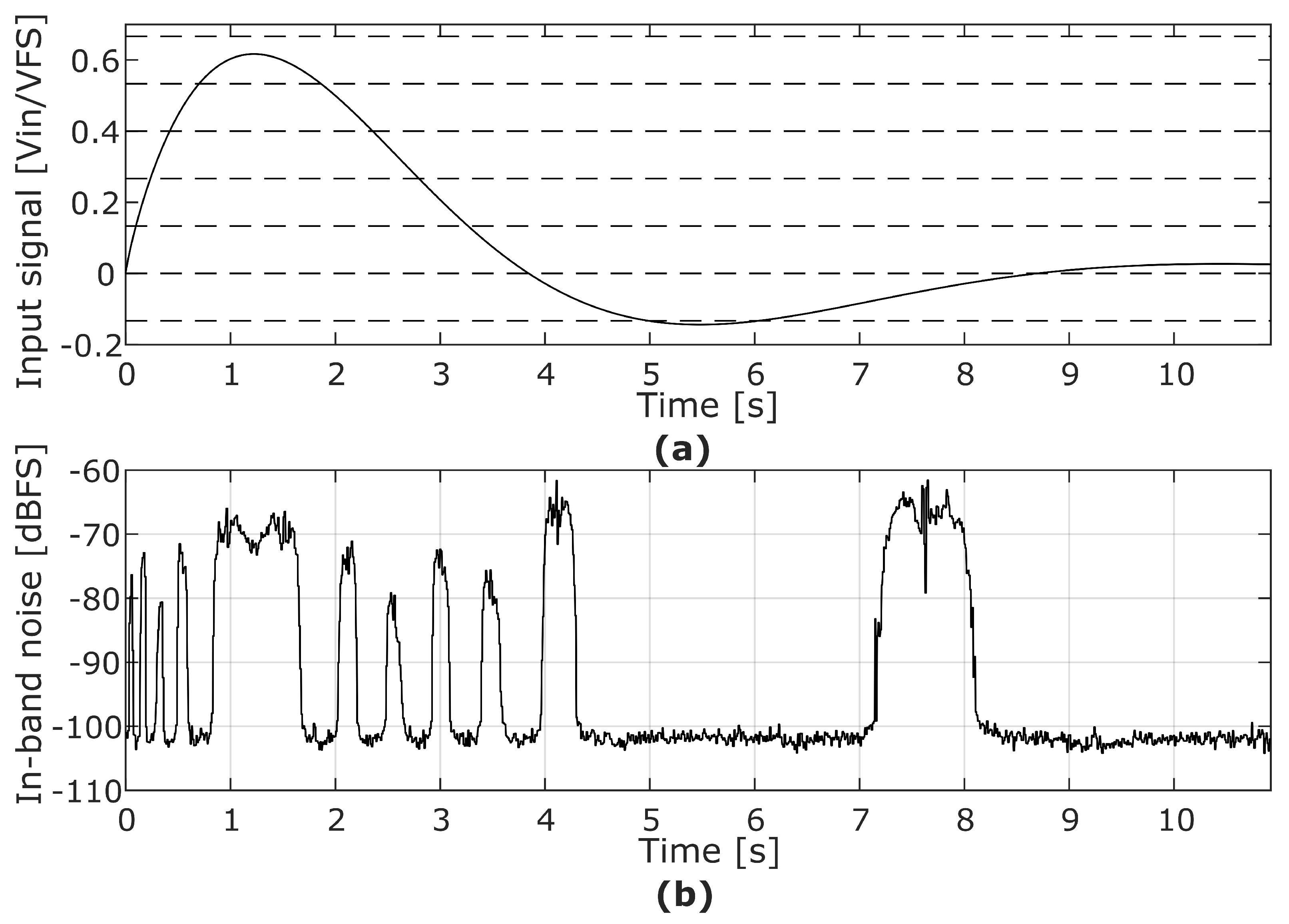

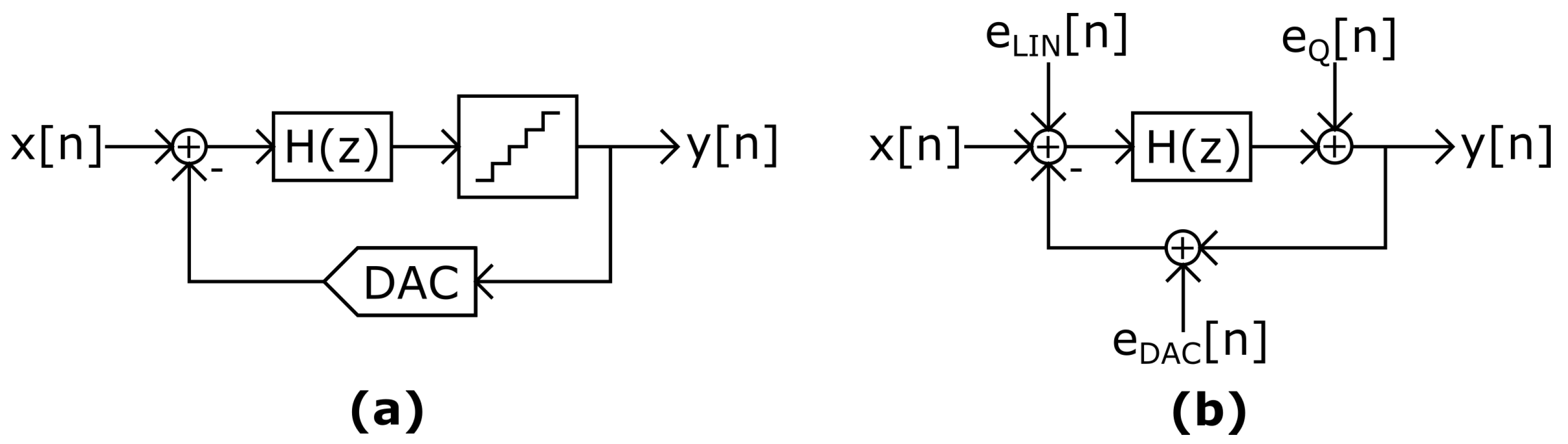

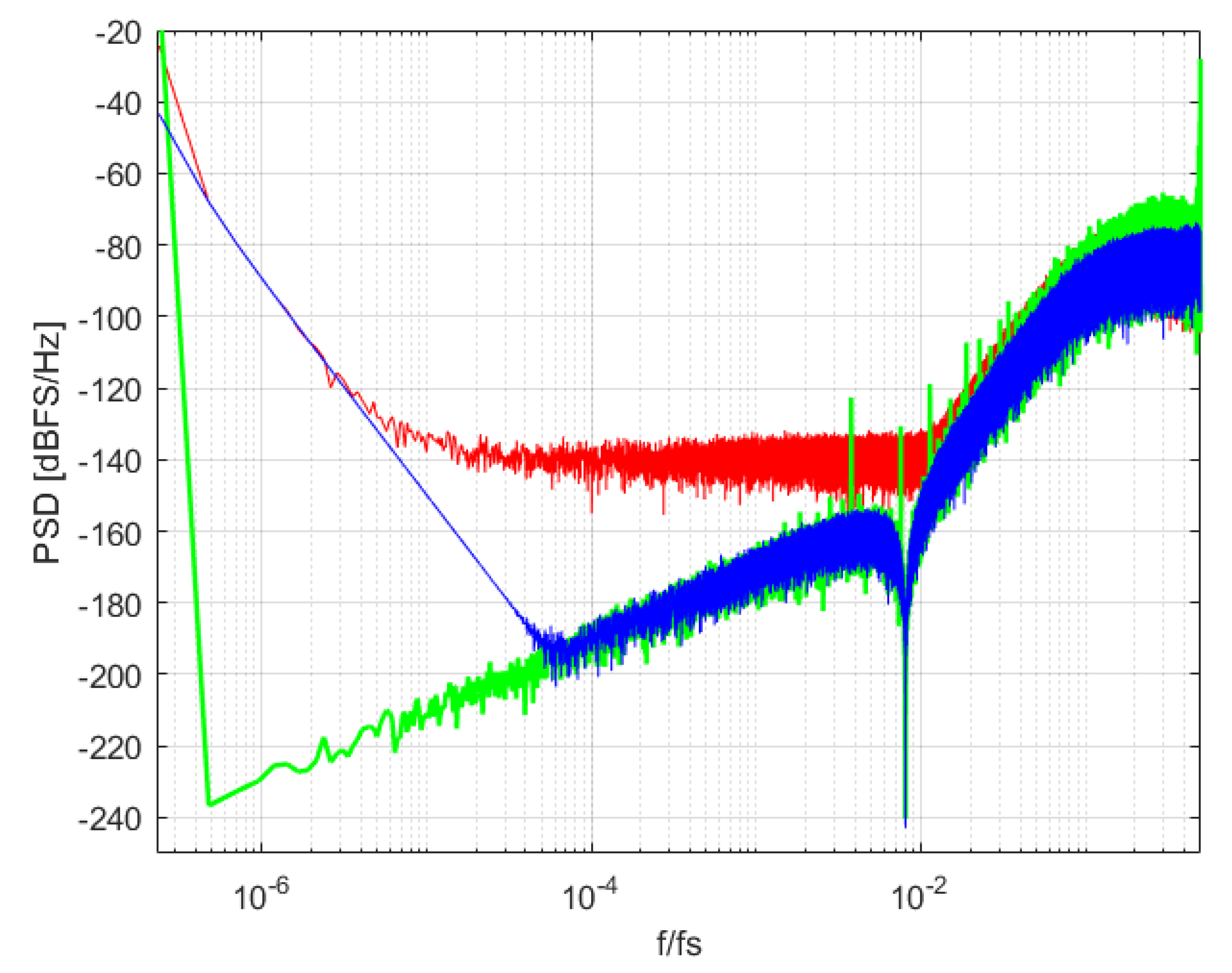

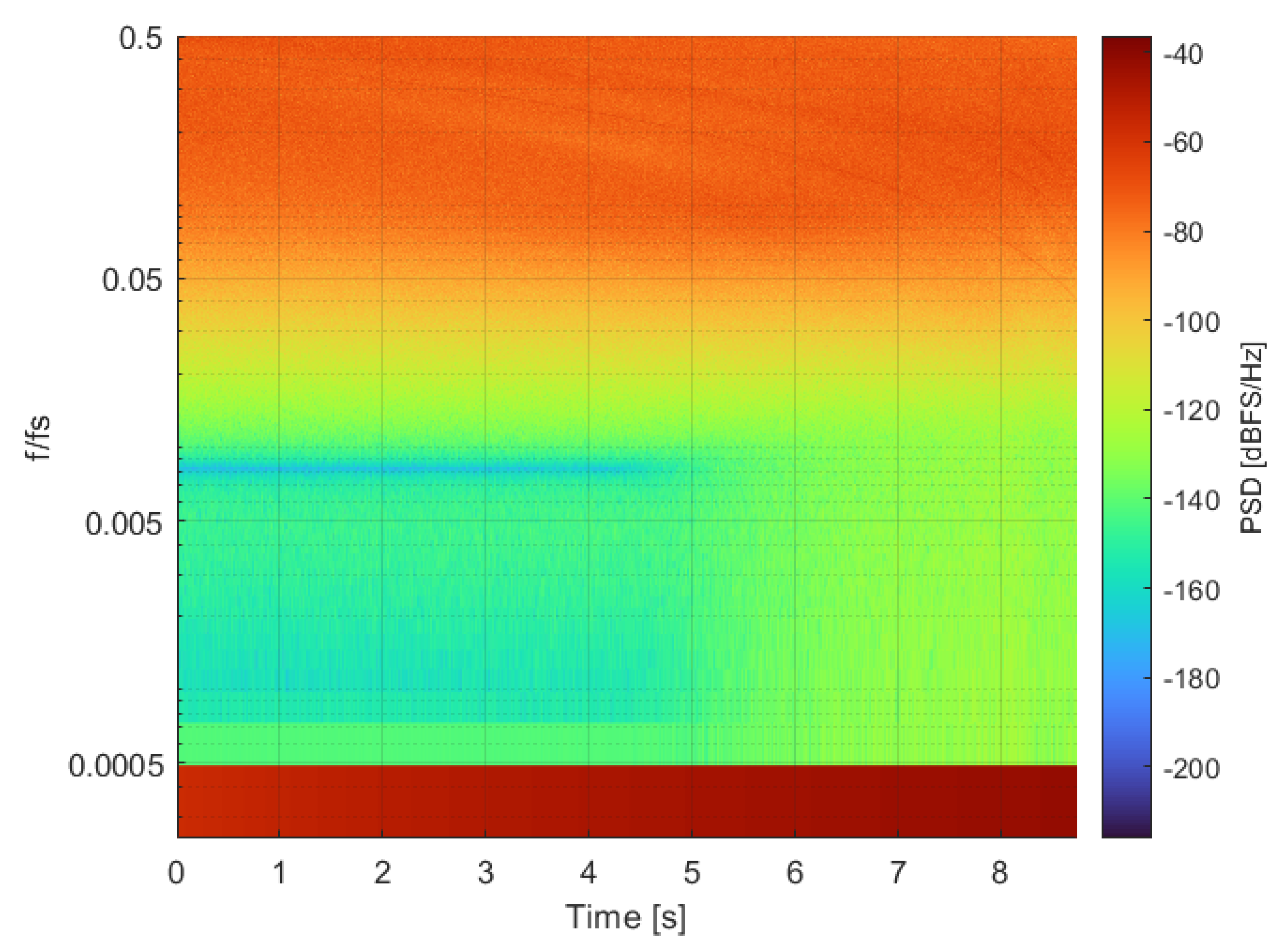

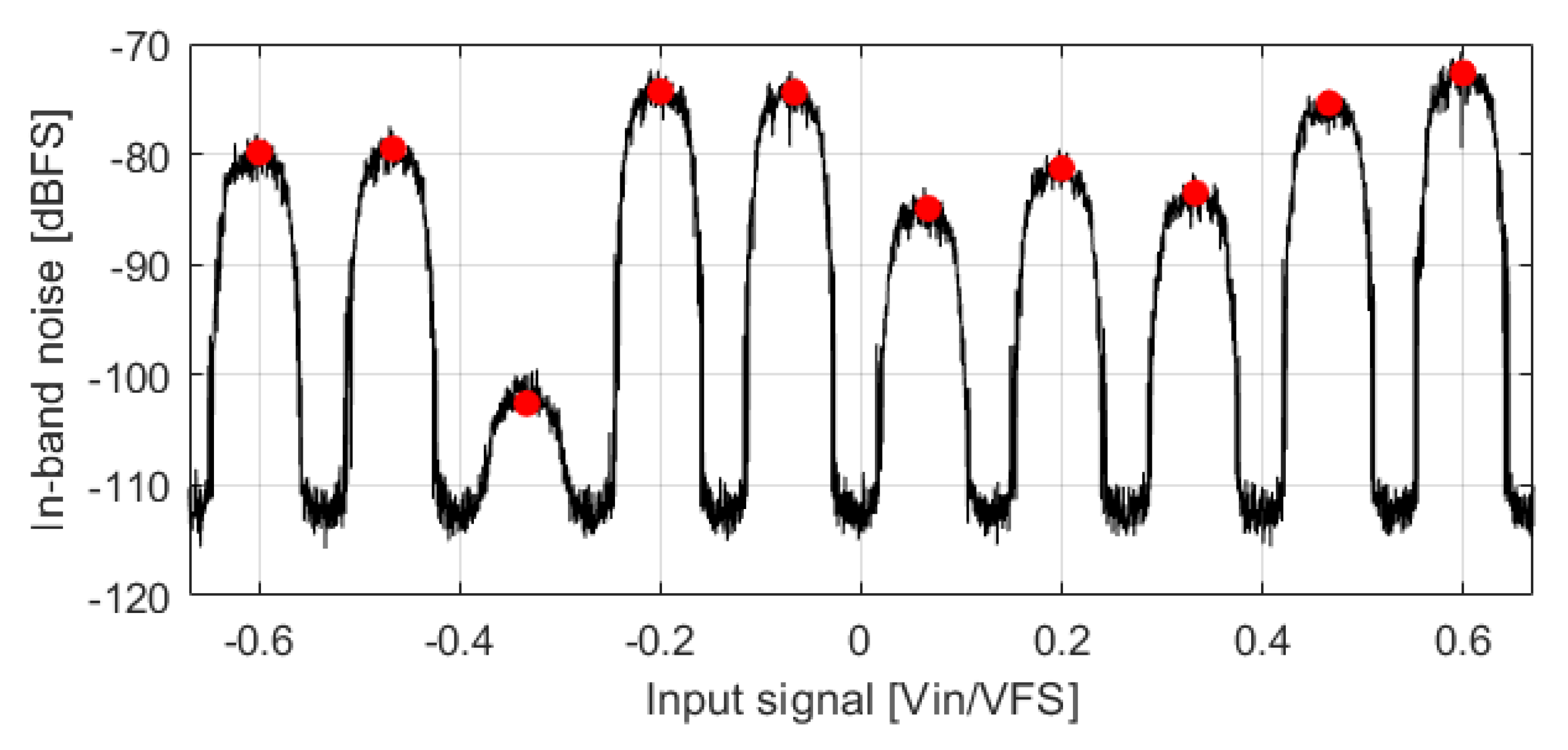

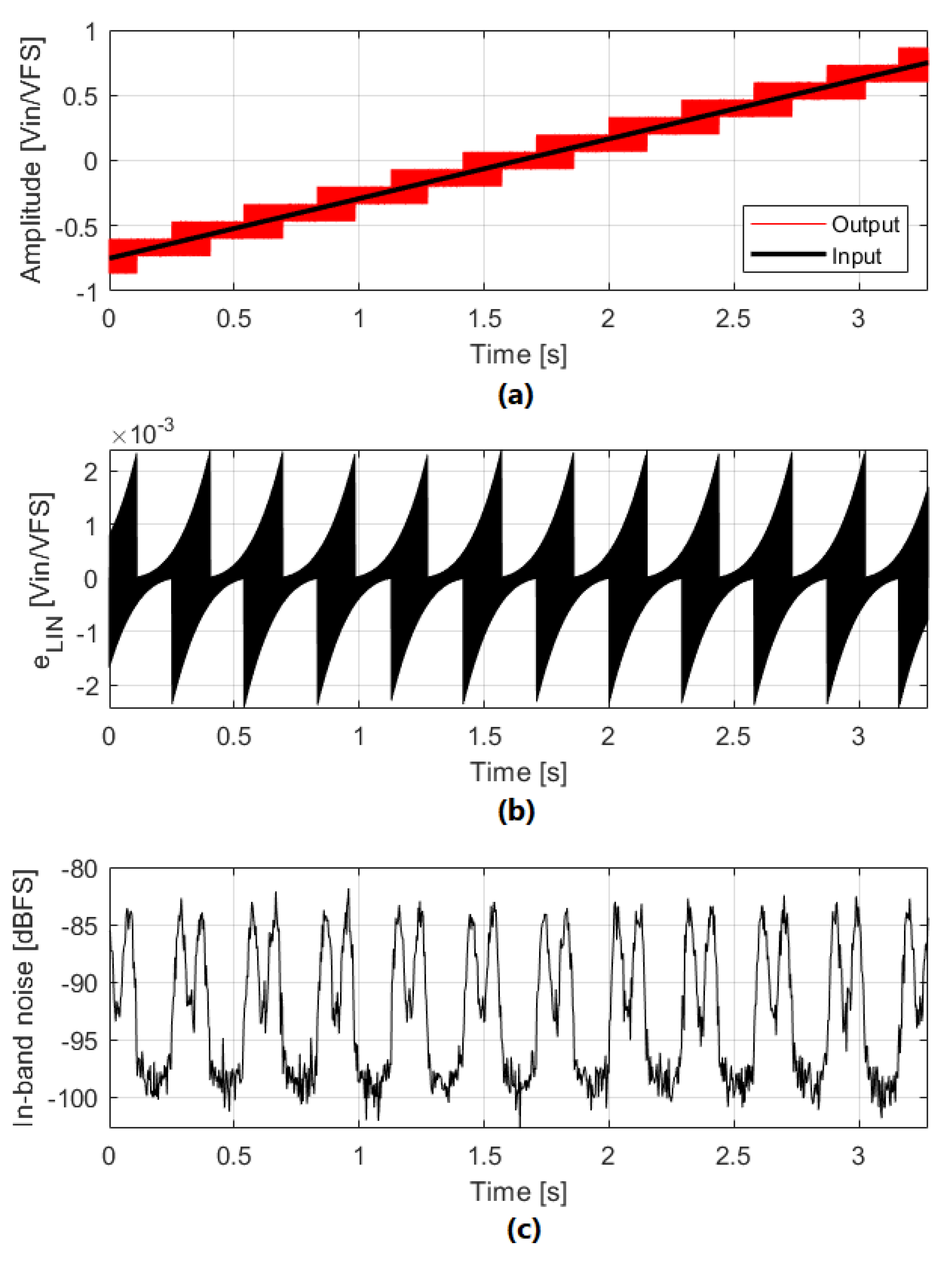

2.2. Origin of Increased Noise Power in the Presence of Slow Input Signals

Influence of Dither

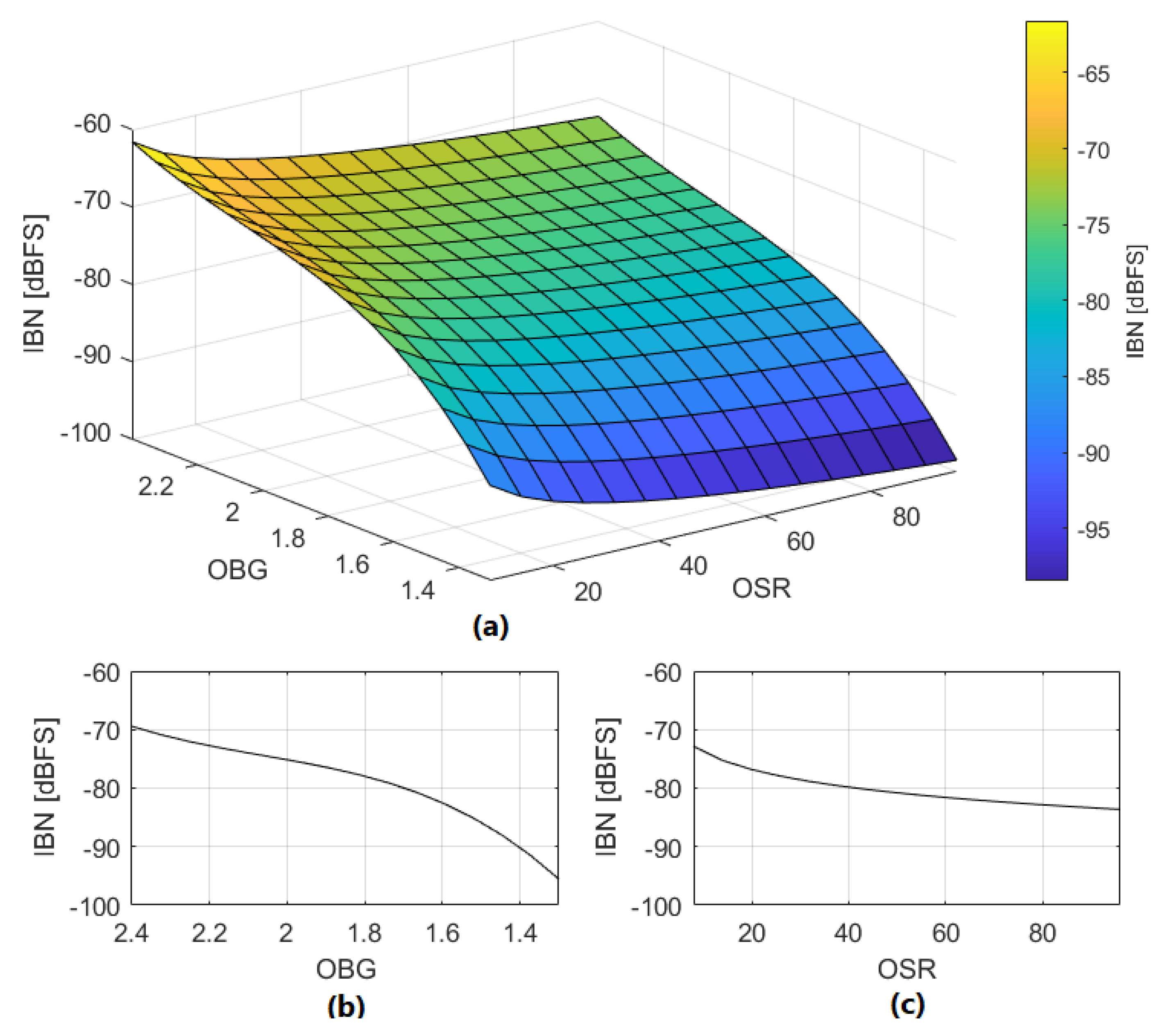

3. Evaluation of Noise Increase

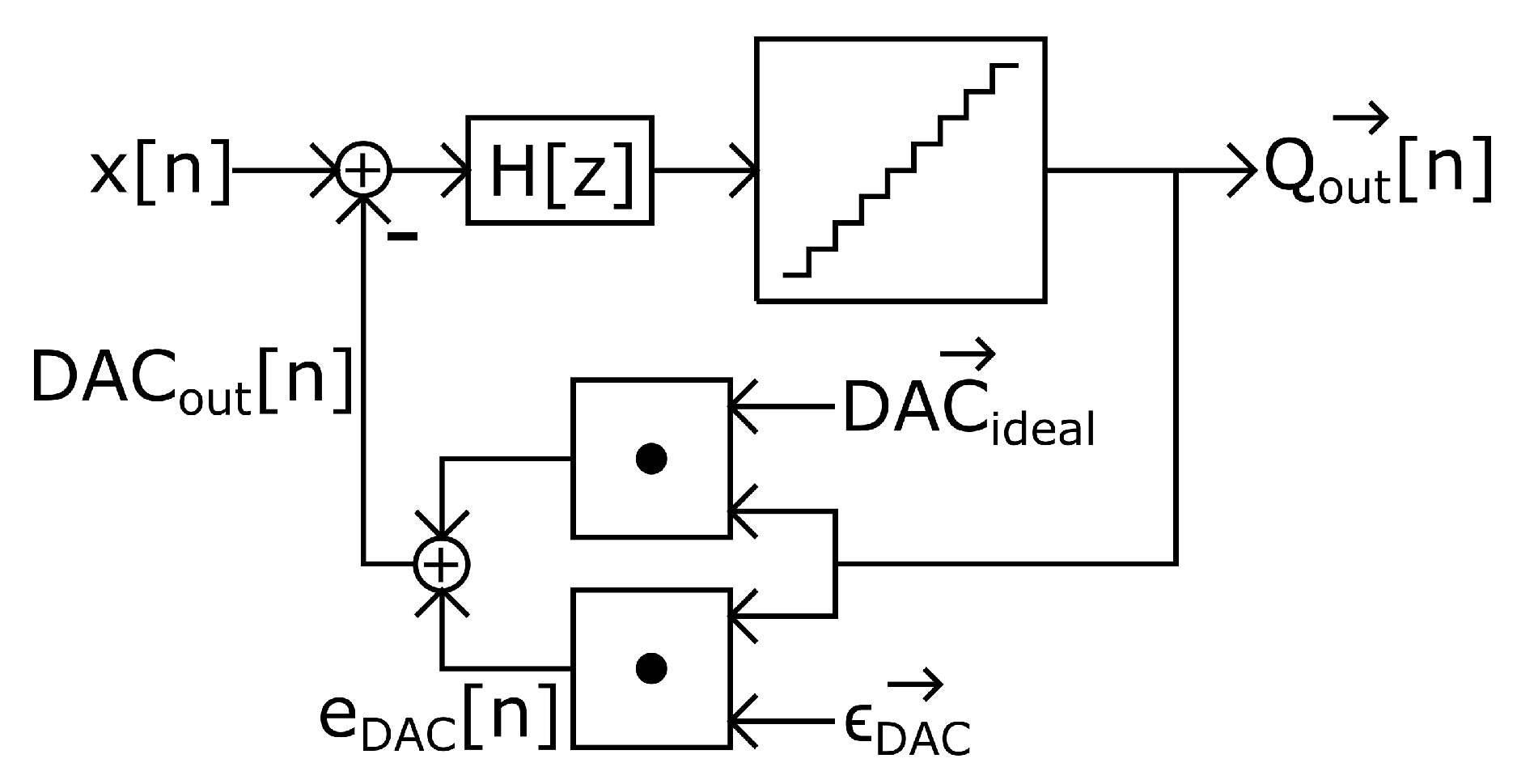

3.1. The Effect of DAC Mismatch on IBN Power Increase

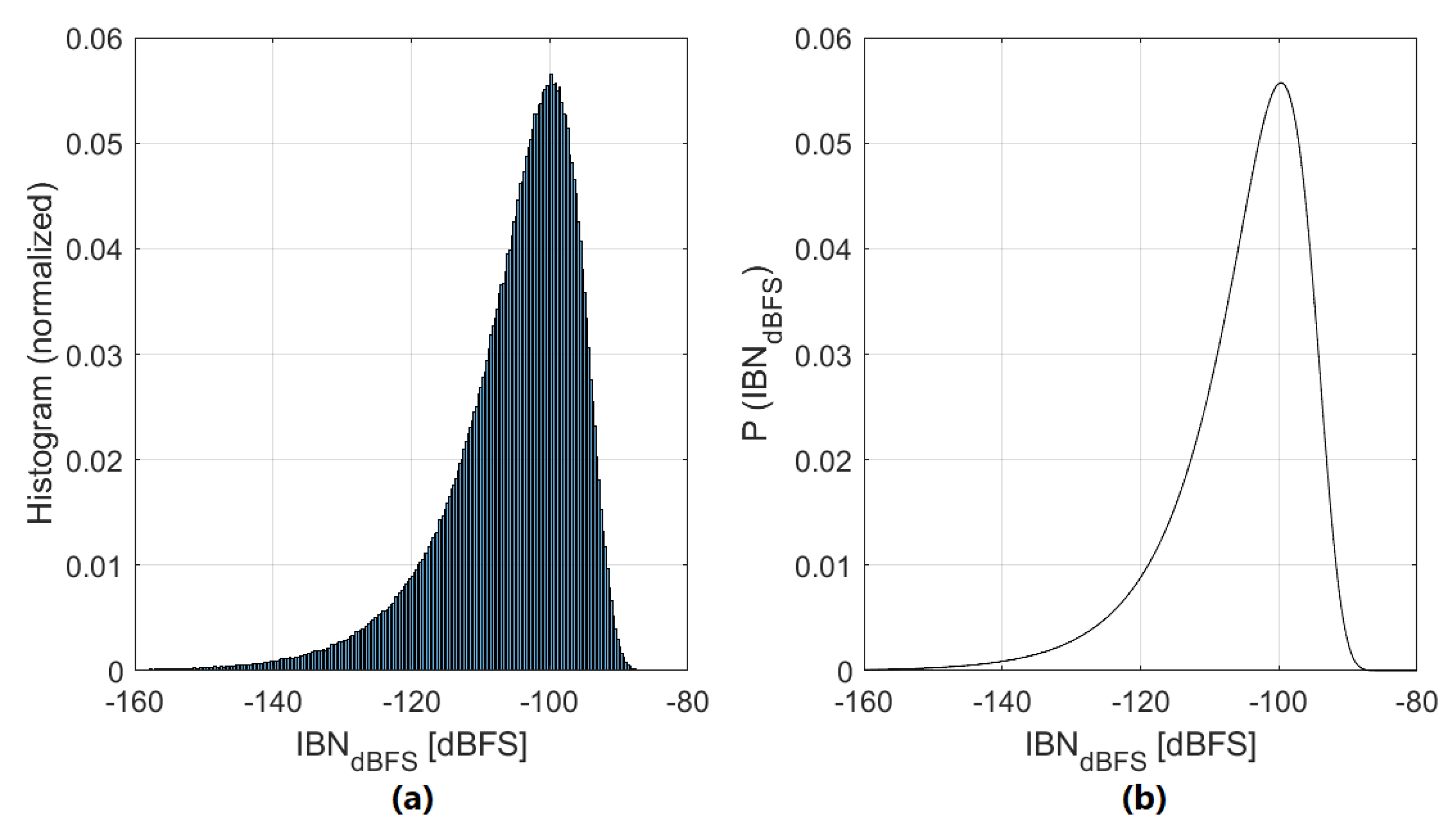

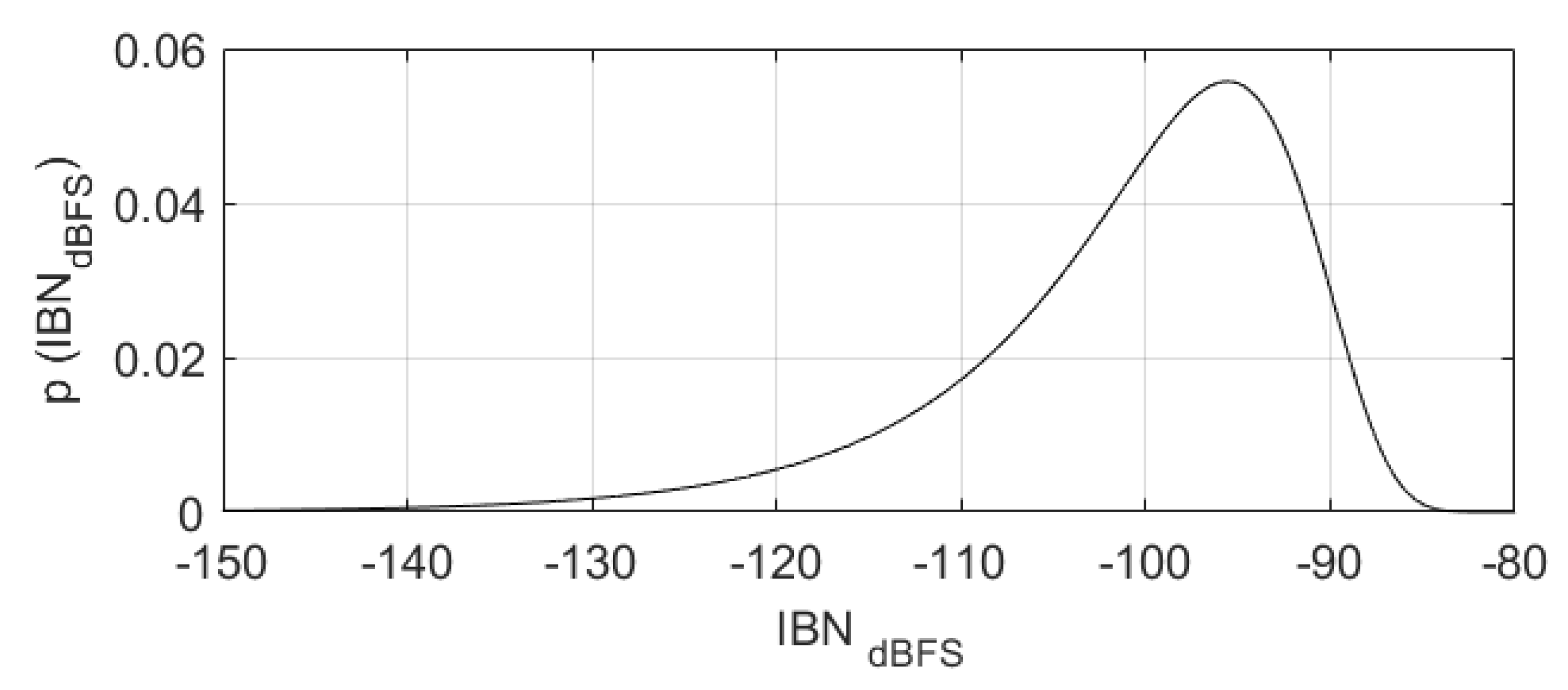

3.1.1. IBN Power Estimation Due to DAC Mismatch

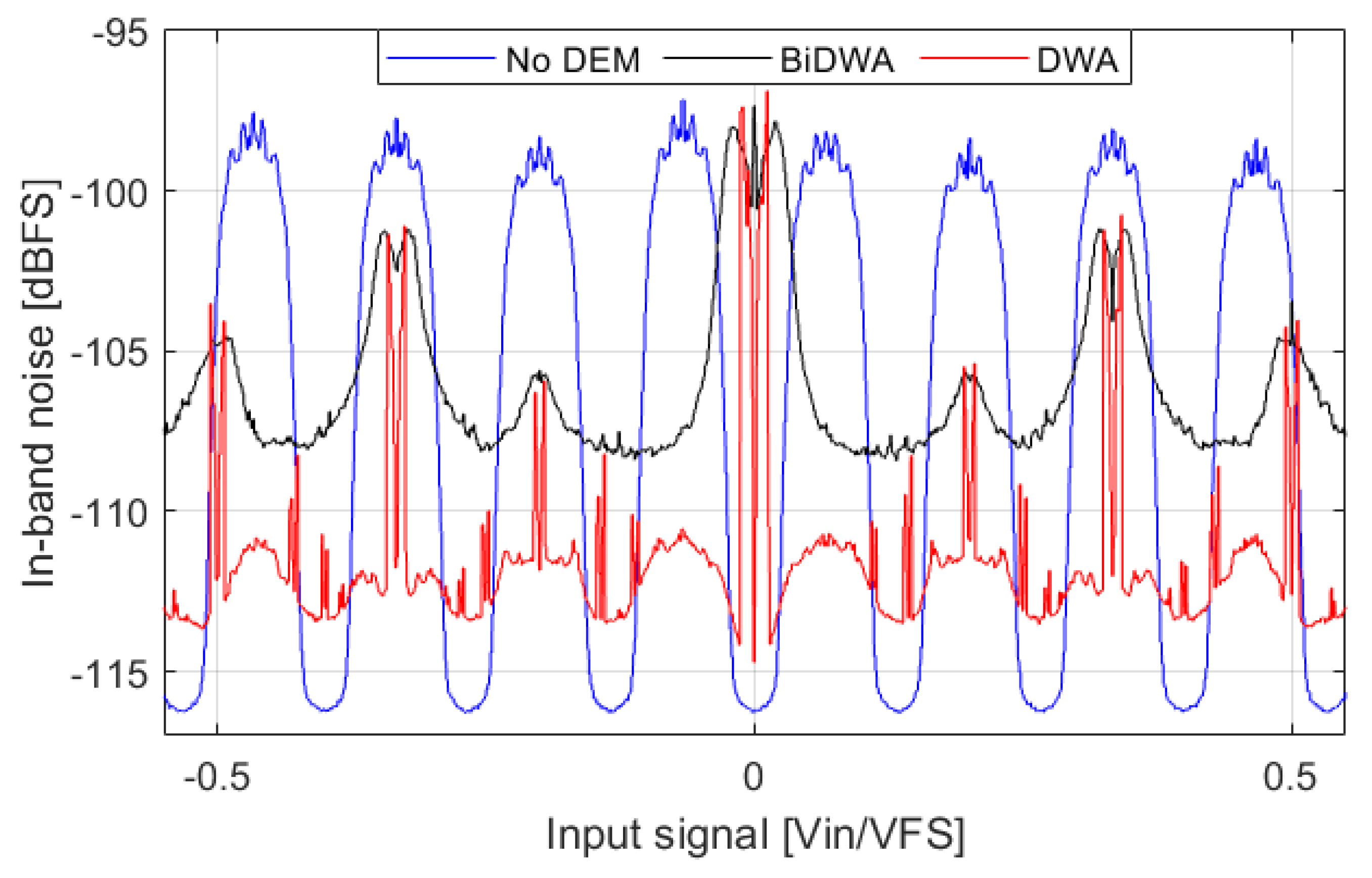

3.1.2. Dynamic Element Matching

3.2. The Effect of Loop Filter Linearity Error on IBN Power Increase

IBN Power Estimation Due to Loop Filter Linearity Error

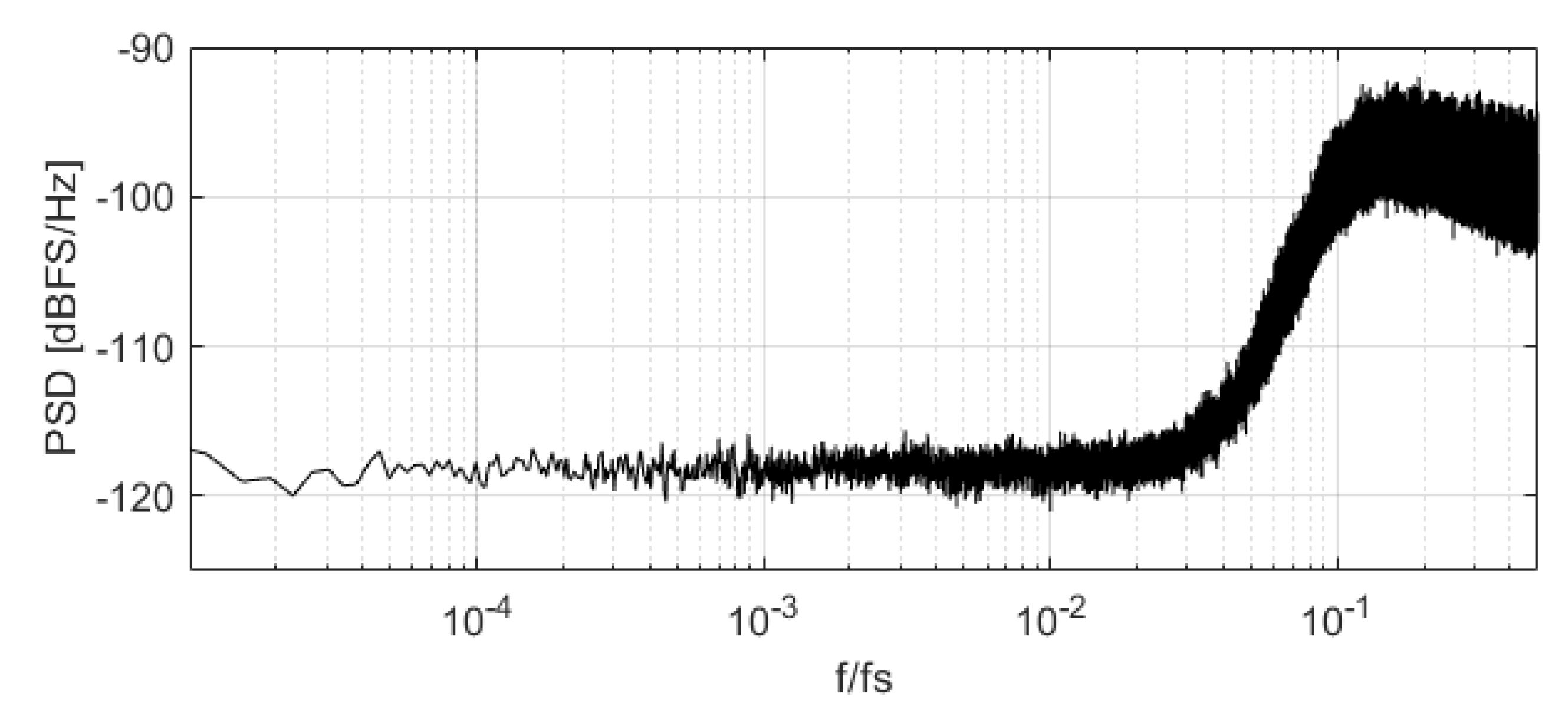

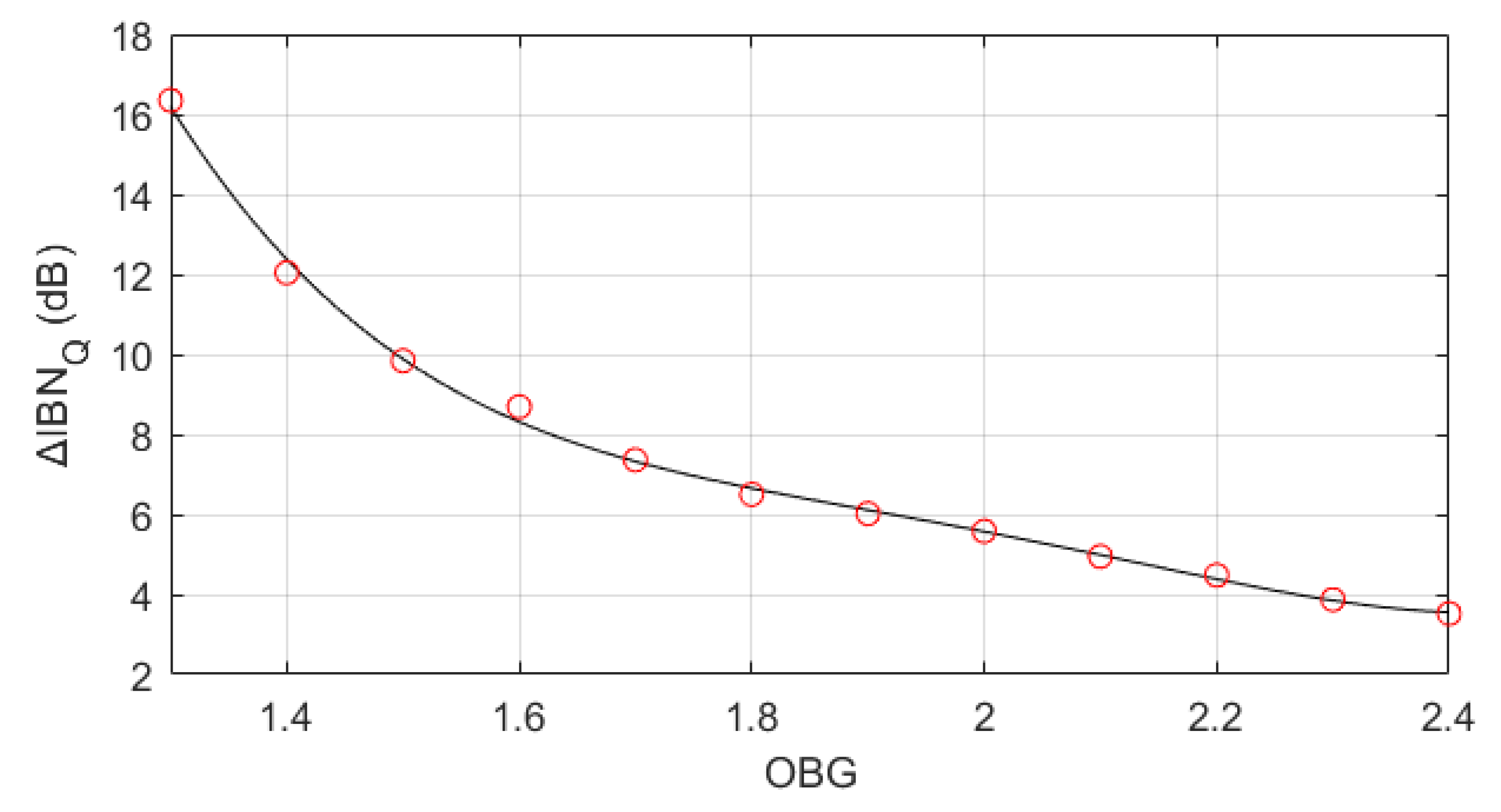

3.3. The Effect of Quantization Error on IBN Power Increase

IBN Power Estimation Due to Quantization Error

4. Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Pavan, S.; Schreier, R.; Temes, G. Understanding Delta-Sigma Converters; Wiley-IEEE Press: Piscataway, NJ, USA, 2017. [Google Scholar]

- Bach, E.; Gaggl, R.; Sant, L.; Buffa, C.; Stojanovic, S.; Straeussnigg, D.; Wiesbauer, A. 9.5 A 1.8 V true-differential 140 dB SPL full-scale standard CMOS MEMS digital microphone exhibiting 67 dB SNR. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 166–167. [Google Scholar] [CrossRef]

- Han, J.H.; Cho, K.I.; Kim, H.J.; Boo, J.H.; Kim, J.S.; Ahn, G.C. A 96 dB Dynamic Range 2 kHz Bandwidth 2nd Order Delta-Sigma Modulator Using Modified Feed-Forward Architecture With Delayed Feedback. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 1645–1649. [Google Scholar] [CrossRef]

- Sant, L.; Füldner, M.; Bach, E.; Conzatti, F.; Caspani, A.; Gaggl, R.; Baschirotto, A.; Wiesbauer, A. A 130 dB SPL 72 dB SNR MEMS Microphone Using a Sealed-Dual Membrane Transducer and a Power-Scaling Read-Out ASIC. IEEE Sens. J. 2022, 22, 7825–7833. [Google Scholar] [CrossRef]

- Candy, J.; Benjamin, O. The Structure of Quantization Noise from Sigma-Delta Modulation. IEEE Trans. Commun. 1981, 29, 1316–1323. [Google Scholar] [CrossRef]

- Ardalan, S.; Paulos, J. An analysis of nonlinear behavior in Delta-Sigma Modulators. IEEE Trans. Circuits Syst. 1987, 34, 593–603. [Google Scholar] [CrossRef]

- Fraser, N.; Nowrouzian, B. A novel technique to estimate the statistical properties of Sigma-Delta A/D converters for the investigation of DC stability. In Proceedings of the 2002 IEEE International Symposium on Circuits and Systems (ISCAS), Phoenix-Scottsdale, AZ, USA, 26–29 May 2002; Volume 3, pp. 289–293. [Google Scholar] [CrossRef]

- He, N.; Kuhlmann, F.; Buzo, A. Double-loop sigma-delta modulation with DC input. IEEE Trans. Commun. 1990, 38, 487–495. [Google Scholar] [CrossRef]

- de la Rosa, J.; del Rio, R. CMOS Sigma-Delta Converters: Practical Design Guide; John Wiley & Sons, Ltd.: Chichester, UK, 2013. [Google Scholar]

- Schreier, R. Delta Sigma Toolbox, MATLAB Central File Exchange. Available online: https://www.mathworks.com/matlabcentral/fileexchange/19-delta-sigma-toolbox (accessed on 27 August 2021).

- Hyun, D.; Fischer, G. Limit cycles and pattern noise in single-stage single-bit delta-sigma modulators. IEEE Trans. Circuits Syst. Fundam. Theory Appl. 2002, 49, 646–656. [Google Scholar] [CrossRef]

- Dunn, C.; Sandler, M. Linearising sigma-delta modulators using dither and chaos. In Proceedings of the 1995 IEEE International Symposium on Circuits and Systems (ISCAS), Seattle, WA, USA, 30 April–3 May 1995; Volume 1, pp. 625–628. [Google Scholar] [CrossRef]

- Tan, Z.; Maurino, R.; Adams, R.; Nguyen, K. Subtractive dithering technique for delta-sigma modulator. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Magrath, A.; Sandler, M. Non-linear deterministic dithering of sigma-delta modulators. In Proceedings of the IEEE Colloquium on Oversampling and Sigma-Delta Strategies for DSP, London, UK, 23 November 1995; pp. 2/1–2/6. [Google Scholar] [CrossRef]

- Baird, R.; Fiez, T. Improved Delta Sigma DAC linearity using data weighted averaging. In Proceedings of the International Symposium on Circuits and Systems (ISCAS’95), Seattle, WA, USA, 30 April–3 May 1995; Volume 1, pp. 13–16. [Google Scholar] [CrossRef]

- Fujimori, I.; Longo, L.; Hairapetian, A.; Seiyama, K.; Kosic, S.; Cao, J.; Chan, S.L. A 90-dB SNR 2.5-MHz output-rate ADC using cascaded multibit Delta-Sigma modulation at 8x oversampling ratio. IEEE J.-Solid Circuits 2000, 35, 1820–1828. [Google Scholar] [CrossRef]

- Gray, R.; Neuhoff, D. Quantization. IEEE Trans. Inf. Theory 1998, 44, 2325–2383. [Google Scholar] [CrossRef]

| M Order | NTF OBG | OSR | Nbits | (% of ) | Simulated IBN Power (dBFS) | Predicted IBN Power (dBFS) |

|---|---|---|---|---|---|---|

| 2 | 1.8 | 64 | 4 | 4.44 | −75.03 | −73.21 |

| 2 | 2 | 48 | 5 | 0.20 | −104.52 | −102.04 |

| 2 | 2.2 | 72 | 4 | 2.66 | −75.24 | −72.95 |

| 2 | 2.3 | 32 | 5 | 0.20 | −99.23 | −96.43 |

| 3 | 1.3 | 58 | 3 | 1.22 | −93.57 | −94.97 |

| 3 | 1.5 | 56 | 4 | 0.53 | −99.30 | −96.43 |

| 3 | 1.8 | 38 | 4 | 0.44 | −91.44 | −91.02 |

| 3 | 2.4 | 12 | 5 | 0.20 | −91.98 | −90.66 |

| 4 | 1.3 | 38 | 3 | 2.15 | −86.59 | −88.21 |

| 4 | 1.8 | 16 | 3 | 1.63 | −69.08 | −68.54 |

| 4 | 2.1 | 32 | 4 | 0.53 | −82.78 | −84.69 |

| 4 | 2.25 | 12 | 4 | 0.26 | −82.42 | −84.48 |

| M Order | NTF OBG | OSR | Nbits | IBN Power Outside of NP Regions (dBFS) | IBN Power in NP Regions (dBFS) | (dB) |

|---|---|---|---|---|---|---|

| 3 | 1.8 | 32 | 4 | −99.23 | −92.73 | 6.50 |

| 2 | 1.8 | 32 | 4 | −85.51 | −79.12 | 6.39 |

| 4 | 1.8 | 32 | 4 | −113.51 | −106.26 | 7.25 |

| 3 | 1.5 | 32 | 4 | −93.65 | −83.81 | 9.84 |

| 3 | 2.1 | 32 | 4 | −101.62 | −96.67 | 4.95 |

| 3 | 1.8 | 16 | 4 | −79.07 | −71.92 | 7.15 |

| 3 | 1.8 | 64 | 4 | −117.57 | −111.18 | 6.39 |

| 3 | 1.8 | 32 | 3 | −92.38 | −85.71 | 6.67 |

| 3 | 1.8 | 32 | 5 | −106.25 | −99.15 | 7.10 |

| Dominant Noise Source | Suggested Changes |

|---|---|

| DAC mismatch error | Increase OSR |

| Decrease OBG | |

| Decrease | |

| Increase | |

| Loop filter linearity error | Increase OSR |

| Decrease OBG | |

| Decrease | |

| Increase | |

| Quantization error | Increase OBG |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Vera, P.; Wiesbauer, A.; Paton, S. An Analysis of Noise in Multi-Bit ΣΔ Modulators with Low-Frequency Input Signals. Sensors 2022, 22, 7458. https://doi.org/10.3390/s22197458

Vera P, Wiesbauer A, Paton S. An Analysis of Noise in Multi-Bit ΣΔ Modulators with Low-Frequency Input Signals. Sensors. 2022; 22(19):7458. https://doi.org/10.3390/s22197458

Chicago/Turabian StyleVera, Pablo, Andreas Wiesbauer, and Susana Paton. 2022. "An Analysis of Noise in Multi-Bit ΣΔ Modulators with Low-Frequency Input Signals" Sensors 22, no. 19: 7458. https://doi.org/10.3390/s22197458

APA StyleVera, P., Wiesbauer, A., & Paton, S. (2022). An Analysis of Noise in Multi-Bit ΣΔ Modulators with Low-Frequency Input Signals. Sensors, 22(19), 7458. https://doi.org/10.3390/s22197458