Concurrent-Mode CMOS Detector IC for Sub-Terahertz Imaging System

Abstract

:1. Introduction

2. Proposed Detector Circuit

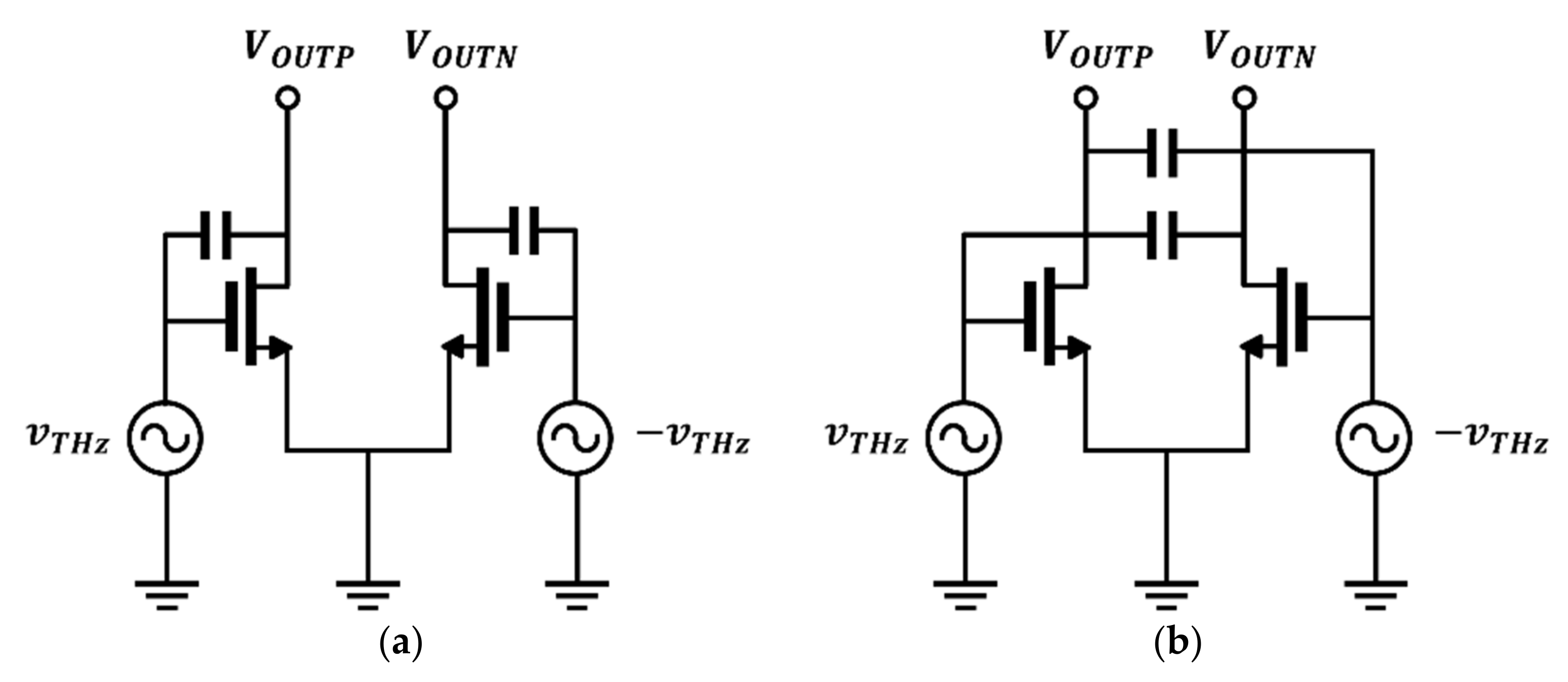

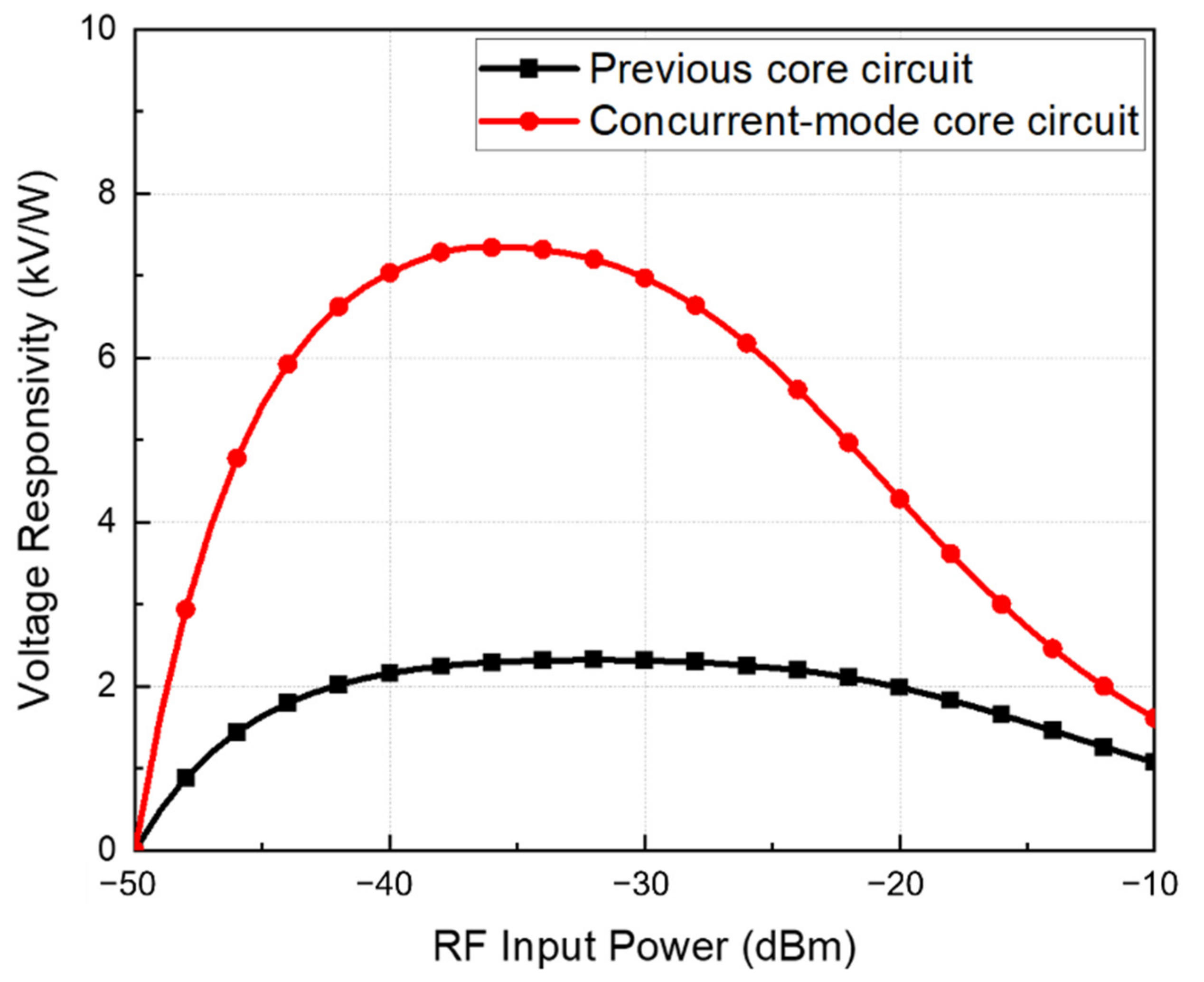

2.1. Proposed Detector Core Configuration

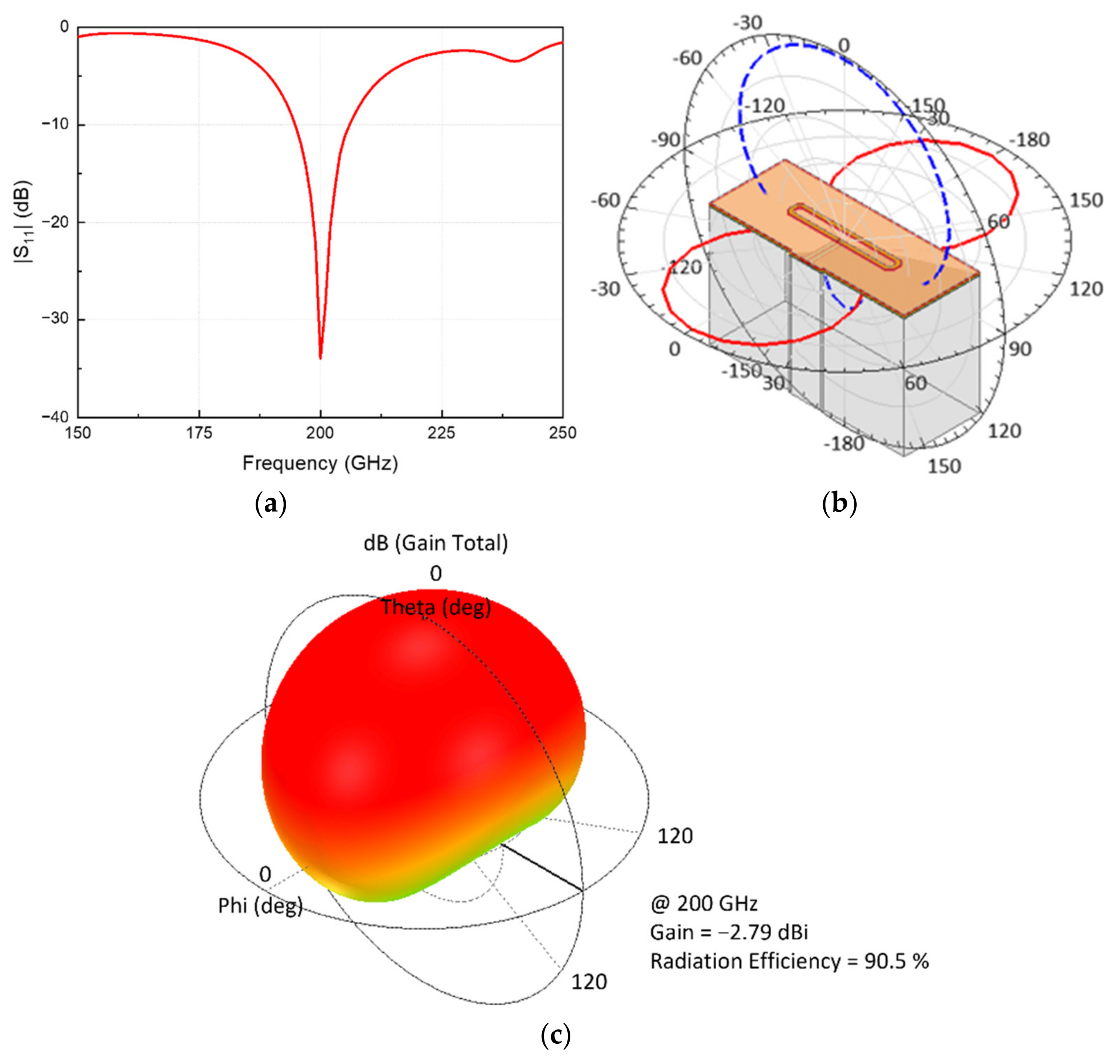

2.2. Folded Dipole Antenna

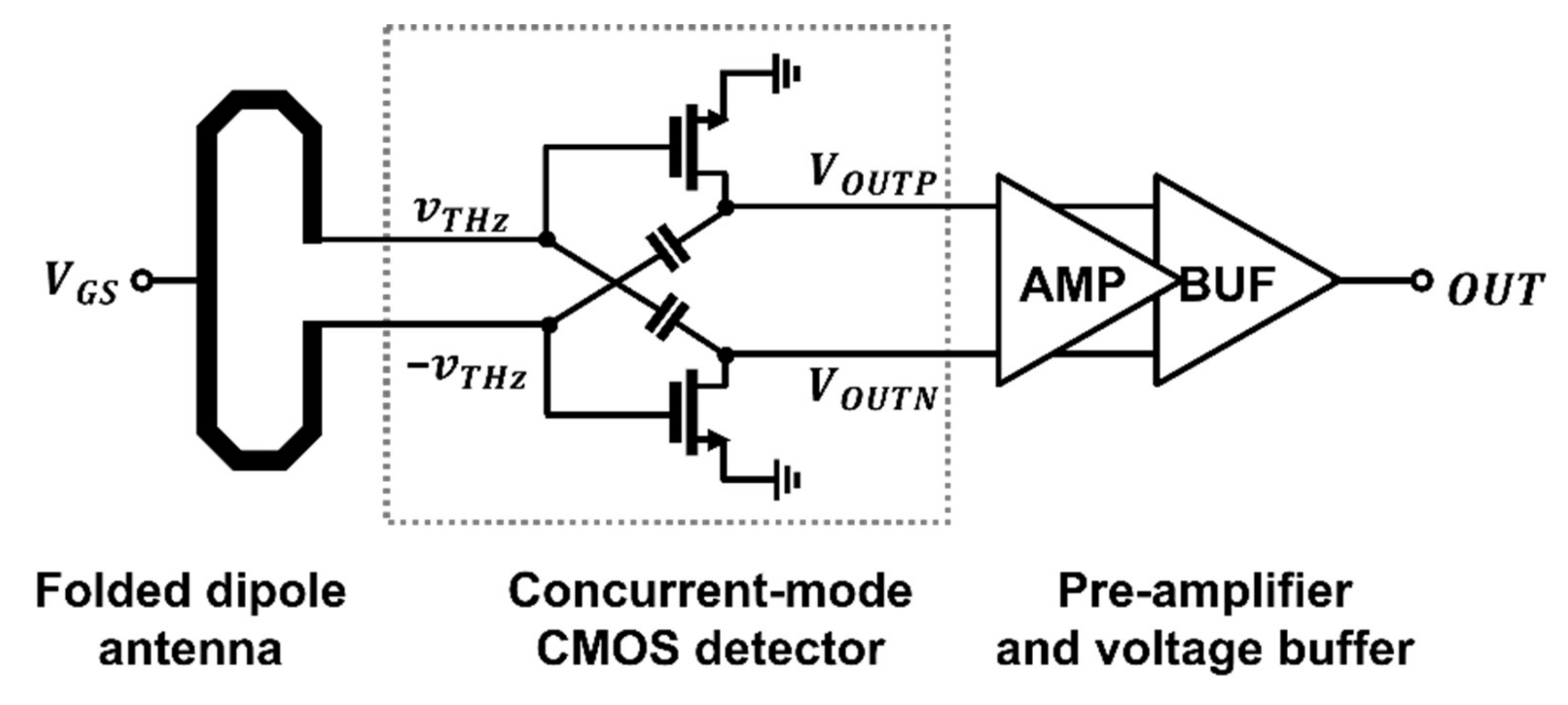

2.3. CMOS Detector IC Implementation

3. Measurement Results and Discussions

3.1. Measurement Setup

3.2. Proposed Detector IC Performance

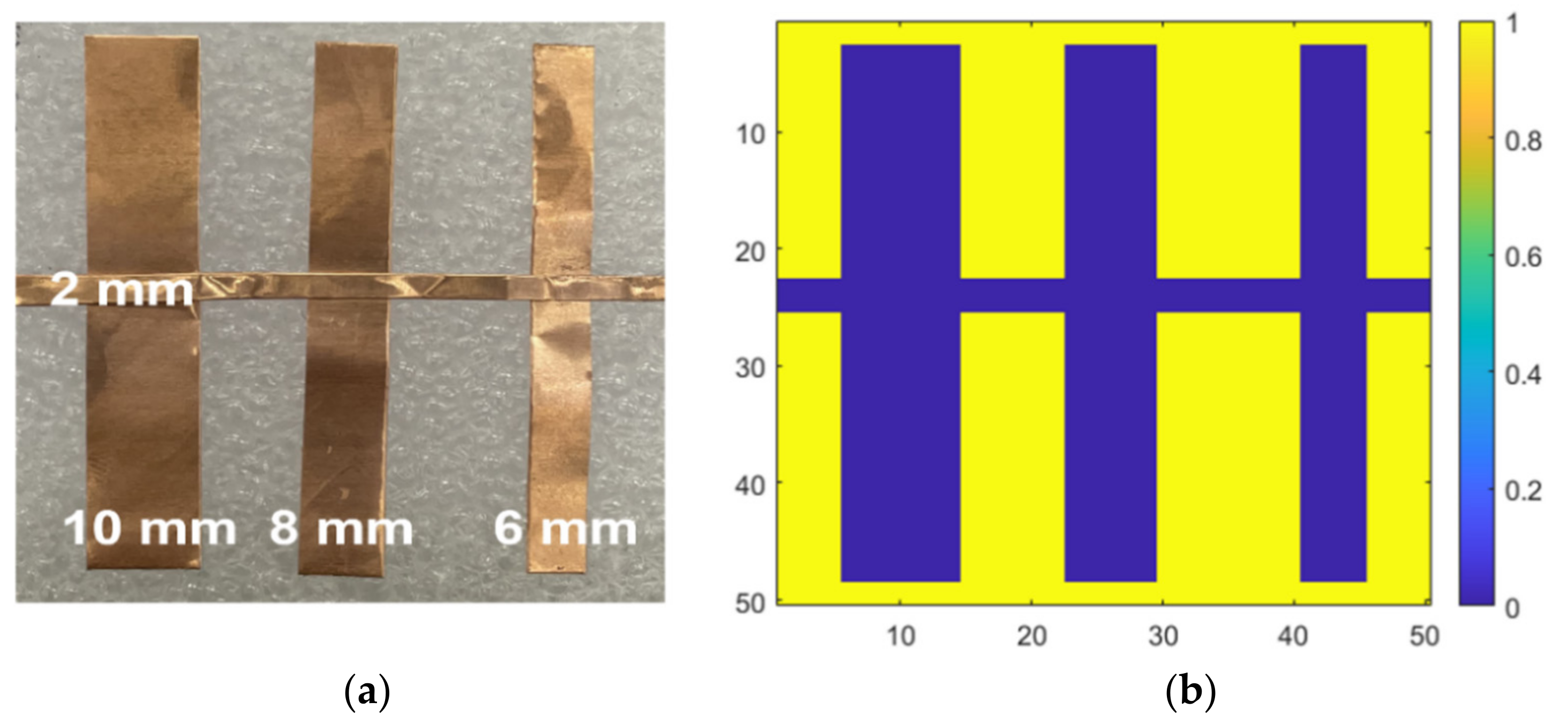

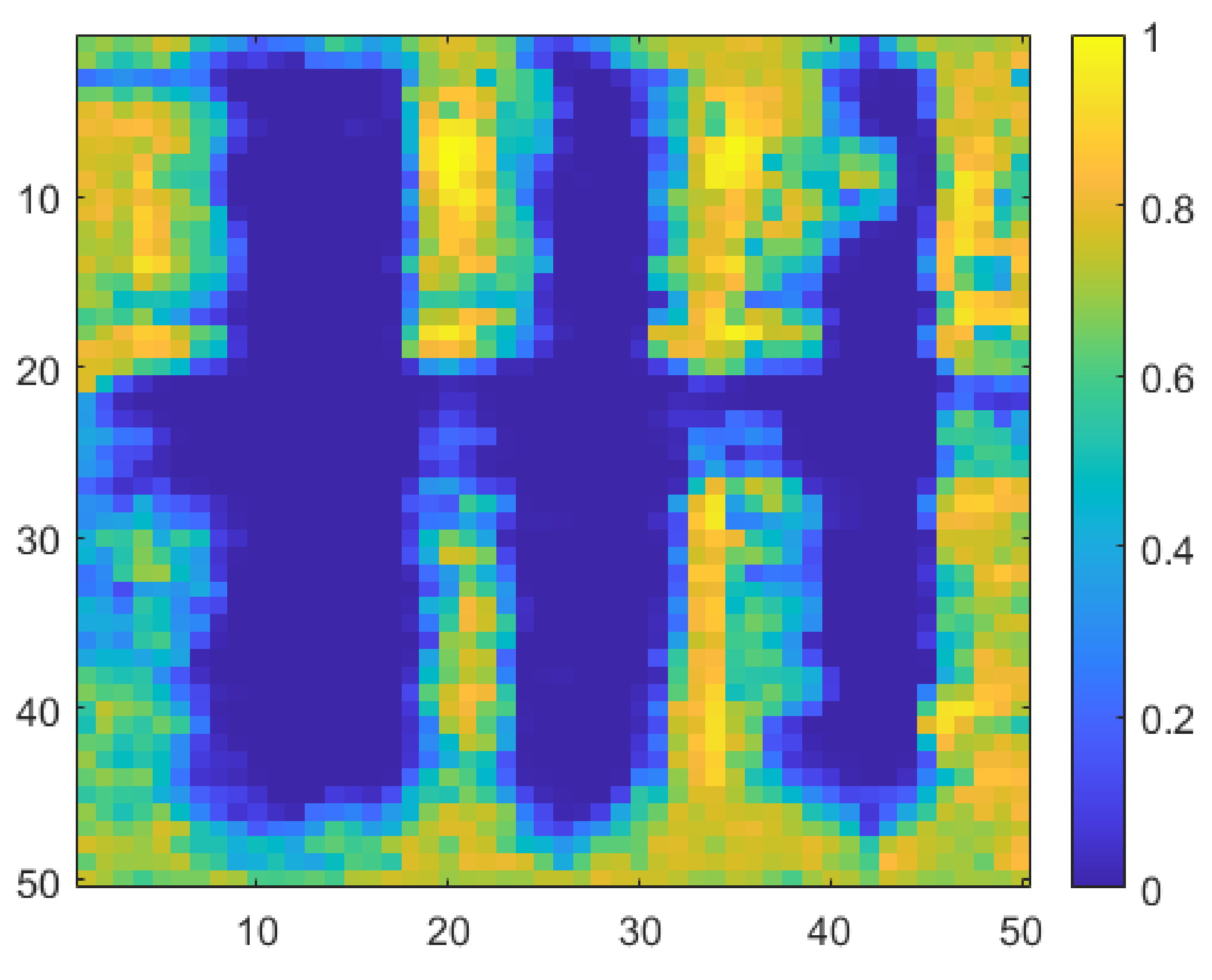

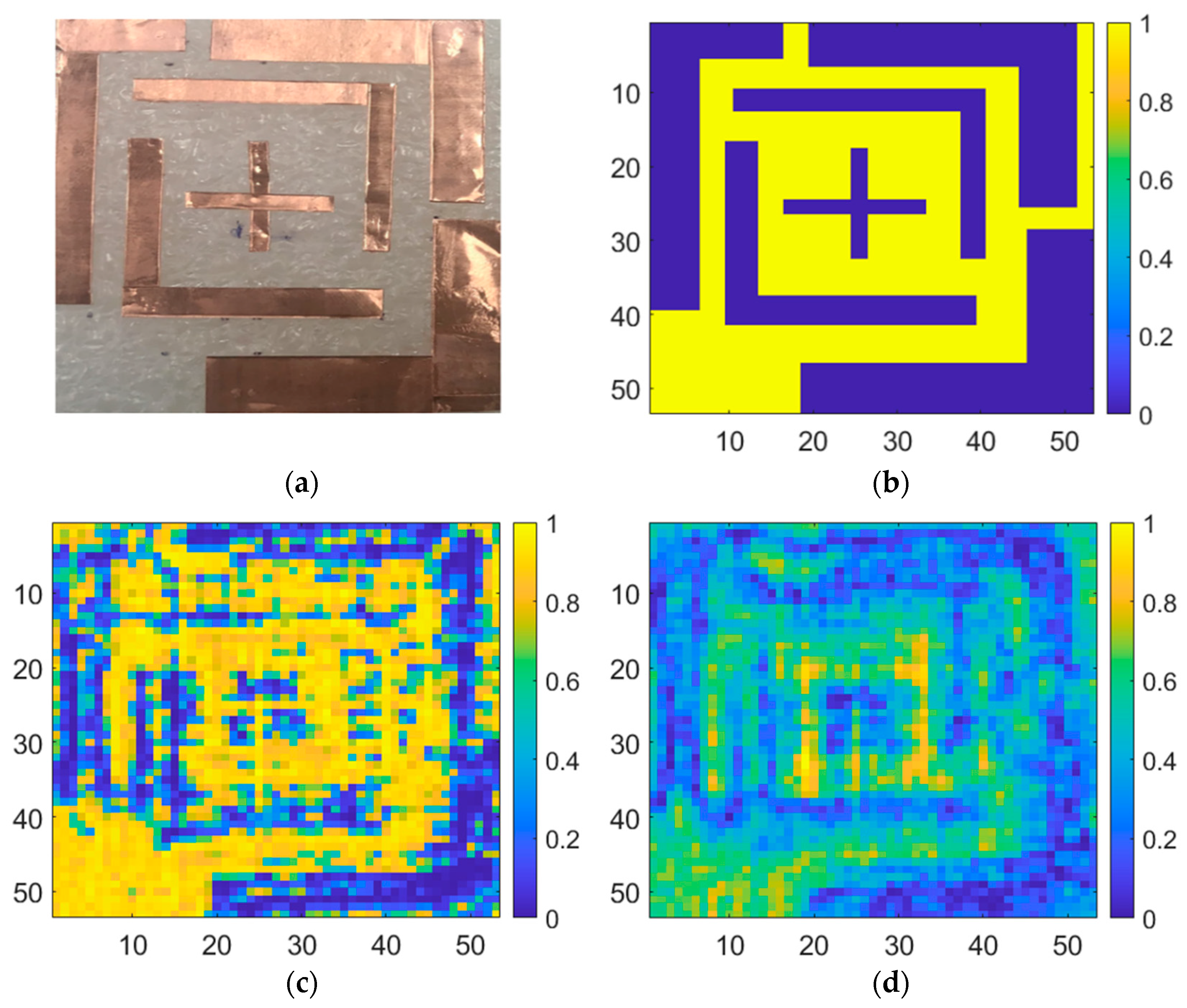

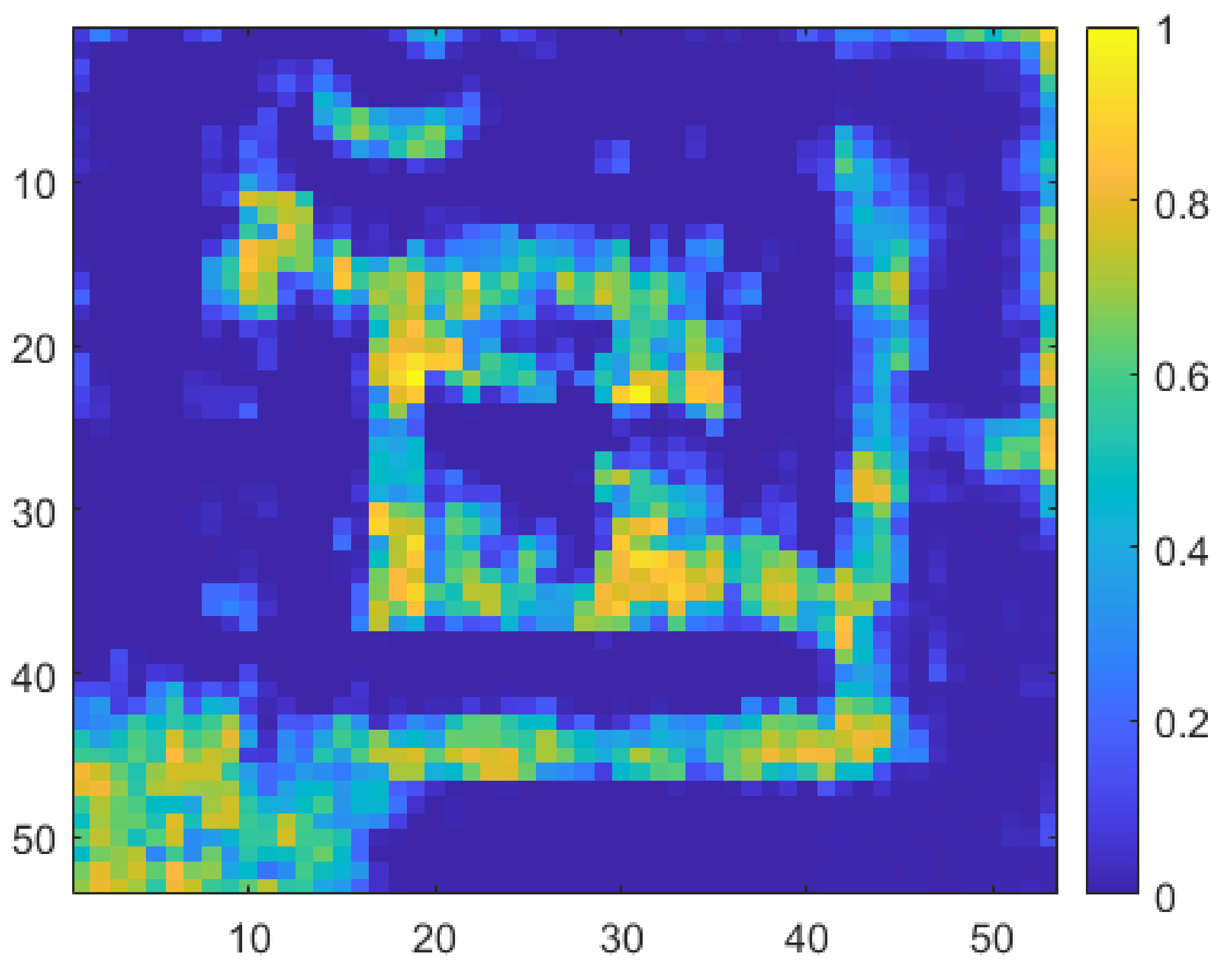

3.3. Images Obtained Using the Proposed Detector IC

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Hu, B.B.; Nuss, M.C. Imaging with terahertz waves. Opt. Lett. 1995, 20, 1716–1718. [Google Scholar] [CrossRef] [PubMed]

- Hillger, P.; Grzyb, J.; Jain, R.; Pfeiffer, U.R. Terahertz imaging and sensing applications with silicon-based technologies. IEEE Trans. Terahertz Sci. Technol. 2019, 9, 1–19. [Google Scholar] [CrossRef]

- Kim, J.; Yoon, D.; Yun, J.; Song, K.; Kaynak, M.; Tillack, B.; Rieh, J.-S. Three-Dimensional Terahertz Tomography with Transistor-Based Signal Source and Detector Circuits Operating Near 300 GHz. IEEE Trans. Terahertz Sci. Technol. 2018, 8, 482–491. [Google Scholar] [CrossRef]

- Yun, J.; Oh, S.J.; Song, K.; Yoon, D.; Son, H.Y.; Choi, Y.; Huh, Y.-M.; Rieh, J.-S. Terahertz reflection-mode biological imaging based on InP HBT source and detector. IEEE Trans. Terahertz Sci. Technol. 2017, 7, 274–283. [Google Scholar] [CrossRef]

- Kawase, K.; Ogawa, Y.; Watanabe, Y.; Inoue, H. Non-destructive terahertz imaging of illicit drugs using spectral fingerprints. Opt. Express 2003, 11, 2549–2554. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Liu, H.-B.; Zhong, H.; Karpowicz, N.; Chen, Y.; Zhang, X.-C. Terahertz spectroscopy and imaging for defense and security applications. Proc. IEEE 2007, 95, 1514–1527. [Google Scholar] [CrossRef]

- Mansourzadeh, S.; Damyanov, D.; Vogel, T.; Wulf, F.; Kohlhass, R.B.; Globisch, B.; Hoffmann, M.; Balzer, J.C.; Saraceno, C.J. High-power lensless THz imaging of hidden objects. IEEE Access 2021, 9, 6268–6276. [Google Scholar] [CrossRef]

- Rieh, J.-S. Introduction to Terahertz Electronics; Springer: Cham, Switzerland, 2021. [Google Scholar]

- Ali, M.; Perenzoni, M.; Stoppa, D. A methodology to measure input power and effective area for characterization of direct THz detectors. IEEE Trans. Instrum. Meas. 2016, 65, 1225–1231. [Google Scholar] [CrossRef]

- Dyakonov, M.; Shur, M.S. Shallow water analogy for a ballistic field effect transistor: New mechanism of plasma wave generation by DC current. Phys. Rev. Lett. 1993, 71, 2465. [Google Scholar] [CrossRef]

- Knap, W.; Teppe, F.; Meziani, Y.; Dyakonova, N.; Lusakowski, J.; Boeuf, F.; Skotnicki, T.; Maude, D.; Rumyantsev, S.; Shur, M.S. Plasma wave detection of sub-terahertz and terahertz radiation by silicon field-effect transistors. Appl. Phys. Lett. 2004, 85, 675–677. [Google Scholar] [CrossRef] [Green Version]

- Kojima, H.; Asano, T. Impact of subthreshold slope on sensitivity of square law detector for high frequency radio wave detection. Jpn. J. Appl. Phys. 2019, 58, SBBL05. [Google Scholar] [CrossRef]

- Lee, H.-J.; Han, S.-T.; Yang, J.-R. CMOS plasmon detector with three different body-biasing MOSFETs. IEEE Access 2020, 8, 215840–215850. [Google Scholar] [CrossRef]

- Kojima, H.; Kido, D.; Kanaya, H.; Ishii, H.; Maeda, T.; Ogura, M.; Asano, T. Analysis of square-law detector for high-sensitive detection of terahertz waves. J. Appl. Phys. 2019, 125, 174506. [Google Scholar] [CrossRef]

- Sengupta, K.; Seo, D.; Yang, L.; Hajimiri, A. Silicon integrated 280 GHz imaging chipset with 4 × 4 SiGe receiver array and CMOS source. IEEE Trans. Terahertz Sci. Technol. 2015, 5, 427–437. [Google Scholar] [CrossRef]

- Shaulov, E.; Jameson, S.; Socher, E. A zero bias J-band antenna-coupled detector in 65-nm CMOS. IEEE Trans. Terahertz Sci. Technol. 2021, 11, 62–69. [Google Scholar] [CrossRef]

- Chai, S.; Lim, S.; Hong, S. THz detector with an antenna coupled stacked CMOS plasma-wave FET. IEEE Microw. Wirel. Compon. Lett. 2014, 24, 869–871. [Google Scholar] [CrossRef]

- Khan, M.I.W.; Kim, S.; Park, D.-W.; Kim, H.-J.; Han, S.-K.; Lee, S.-G. Nonlinear analysis of nonresonant THz response of MOSFET and implementation of a high-responsivity cross-coupled THz detector. IEEE Trans. Terahertz Sci. Technol. 2018, 8, 108–120. [Google Scholar] [CrossRef]

- Lee, H.-N.; Lee, H.-J.; Han, S.-T.; Yang, J.-R. Highly sensitive CMOS plasmon detector with a low-gain buffer amplifier for terahertz imaging system. Microw. Opt. Technol. Lett. 2021, 63, 2587–2591. [Google Scholar] [CrossRef]

- Han, S.-T. Application of a compact sub-terahertz gyrotron for non-destructive inspections. IEEE Trans. Plasma Sci. 2020, 48, 3238–3245. [Google Scholar] [CrossRef]

- Lee, M.-J.; Lee, H.-N.; Lee, H.-J.; Lee, G.-E.; Son, J.-H.; Yang, J.-R. Analysis of the effects of differential integrated antennas on voltage responsivity of sub-terahertz CMOS detectors. IDEC J. Integr. Circuits Syst. 2020, 6, 1–7. [Google Scholar]

- Yang, J.-R.; Han, S.-T.; Baek, D. Differential CMOS sub-terahertz detector with subthreshold amplifier. Sensors 2017, 17, 2069. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Karolyi, G.; Gergelzi, D.; Foldesy, P. Sub-THz sensor array with embedded signal processing in 90 nm CMOS technology. IEEE Sens. J. 2014, 14, 2432–2441. [Google Scholar] [CrossRef]

- Lee, G.-E.; Lee, H.-J.; Han, S.-T.; Yang, J.-R. CMOS detector using customized bolt-wrench capacitor on backend oxide layer. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 1012–1015. [Google Scholar] [CrossRef]

| Ref. | Process (nm) | Freq. (GHz) | Detector Core Configuration | RV (kV/W) | NEP (pW/√Hz) |

|---|---|---|---|---|---|

| [13] | 250 | 200 | Gate-drain cap. | 5696 | 62.4 |

| [16] | 65 | 310 | Drain input | 2 | 3.5 1 |

| [19] | 250 | 200 | Gate-drain cap. | 357.1 | 57.3 |

| [22] | 250 | 200 | Gate-drain cap. | 2020 | 76 |

| [23] | 90 | 365 | Gate source input | 1200 | 200 |

| [24] | 250 | 200 | Gate-drain cap. | 2990 | 46.3 |

| This works | 250 | 200 | Concurrent-mode | 14,130 | 34.42 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, M.-J.; Lee, H.-N.; Lee, G.-E.; Han, S.-T.; Yang, J.-R. Concurrent-Mode CMOS Detector IC for Sub-Terahertz Imaging System. Sensors 2022, 22, 1753. https://doi.org/10.3390/s22051753

Lee M-J, Lee H-N, Lee G-E, Han S-T, Yang J-R. Concurrent-Mode CMOS Detector IC for Sub-Terahertz Imaging System. Sensors. 2022; 22(5):1753. https://doi.org/10.3390/s22051753

Chicago/Turabian StyleLee, Moon-Jeong, Ha-Neul Lee, Ga-Eun Lee, Seong-Tae Han, and Jong-Ryul Yang. 2022. "Concurrent-Mode CMOS Detector IC for Sub-Terahertz Imaging System" Sensors 22, no. 5: 1753. https://doi.org/10.3390/s22051753

APA StyleLee, M.-J., Lee, H.-N., Lee, G.-E., Han, S.-T., & Yang, J.-R. (2022). Concurrent-Mode CMOS Detector IC for Sub-Terahertz Imaging System. Sensors, 22(5), 1753. https://doi.org/10.3390/s22051753