Abstract

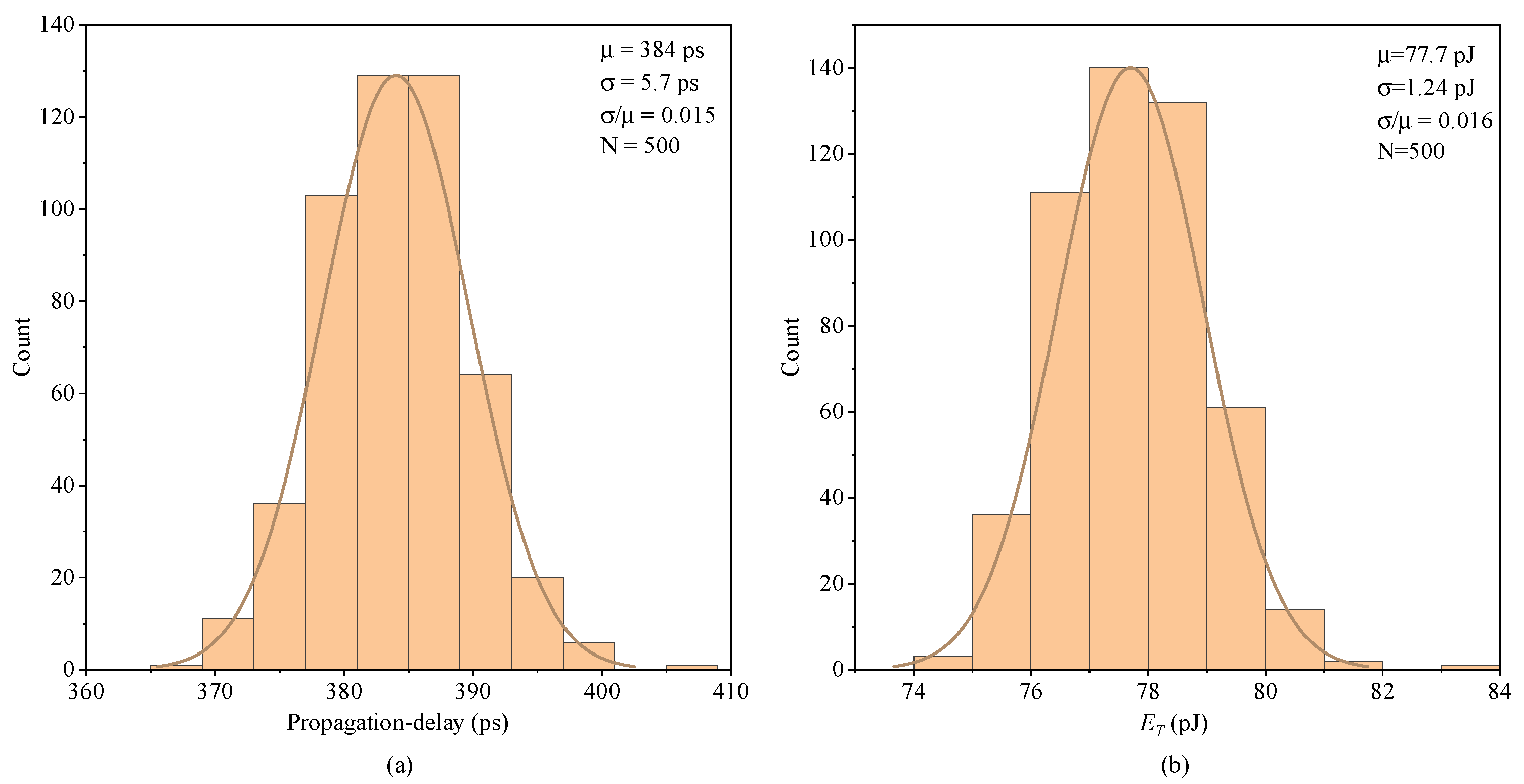

This paper proposes a novel floating high-voltage level shifter (FHV-LS) with the pre-storage technique for high speed and low deviation in propagation delay. With this technology, the transmission paths from input to output are optimized, and thus the propagation delay of the proposed FHV-LS is reduced to as low as the sub-nanosecond scale. To further reduce the propagation delay, a pull-up network with regulated strength is introduced to reduce the fall time, which is a crucial part of the propagation delay. In addition, a pseudosymmetrical input pair is used to improve the symmetry of FHV-LS structurally to balance between the rising and falling propagation delays. Moreover, a start-up circuit is developed to initialize the output state of FHV-LS during the power up. The proposed FHV-LS is implemented using 0.3-µm HVCMOS technology. Post-layout simulation shows that the propagation delays and energy per transition of the proposed FHV-LS are 384 ps and 77.7 pJ @ = 5 V, respectively. Finally, the 500-points Monte Carlo are performed to verify the performance and the stability.

1. Introduction

With the increase in power density and switching speed of the power devices, gate drivers with low propagation delays and high operating frequencies are in high demand [1,2,3]. In the application of feedback-based regulation, the gate drivers are developed to operate in the closed-loop mode to respond to the change of loads [4,5,6]. Moreover, some gate drivers feature functions of over-current protection and fault indication [7,8]. For precise regulation and fast protection, low propagation delay is critical for gate drivers. In commercial applications, the propagation delay of state-of-the-art gate drivers is in the order of ten nanoseconds, excluding the delay induced by bonding wires and pads. In gate drivers, multi-voltage power supply technology is applied to balance between switching speed and power consumption [9,10]. The digital units implementing the logic processing are supplied by low voltage to reduce power dissipation, while the circuits composing the output stage are powered by high voltage to carry enough energy for loads. For communication between circuits supplied with different voltage, the level shifter becomes a critical interface in the gate driver [11,12]. In the medium/high-voltage gate driver or half-bridge gate driver, FHV-LS can transfer the control signal from low-side power rail to high-side power rail with floating-ground, sending commands to the output of gate driver. For the high-speed gate driver, the FHV-LS with nanoseconds of propagation delay will have a negative impact on the total propagation delay in gate driver. Therefore, the reduction in propagation delay of FHV-LS will be an essential destination for high-speed gate driver design.

On the one hand, the existing level-shifting circuits have large propagation delays, which are not suitable for high-speed applications. Especially in feedback-based regulation and protection situations, large propagation delay not only affects the regulating accuracy but also suffers from the risk of damage. On the other hand, large propagation delay will lead to major deviation between rising and falling propagation delay. As the operating frequencies increase, the distortions in duty cycle caused by the deviation become more serious. Therefore, this study focuses on the analysis of factors affecting the propagation delay and methods to reduce the propagation delay and the deviation of FHV-LS. The main contributions of our work are outlined as follows:

- A novel level-shifting circuit structure with pre-storage technology is proposed to achieve low propagation delay. Then, the design approach and implementation of the proposed FHV-LS are presented.

- Based on the proposed FHV_LS, the propagation delay is analyzed in detail. Moreover, the factors affecting the propagation delay are revealed for an in-depth insight into the proposed FHV-LS.

- To further improve the performance of the proposed FHV-LS, the pull-up network with regulated strength technology and the pseudosymmetrical input structure are introduced to optimize the propagation delay and the deviation of the proposed FHV-LS, respectively. In addition, a start-up circuit applied to the register is developed to initialize the output state of FHV-LS during power-up. With the start-up circuit, the output of FHV-LS always follows the input correctly in any operating condition.

The remainder of this paper is organized as follows. Section 2 reviews the conventional FHV-LSs, and three topologies are summarized. Section 3 presents the design principle and implementation of the proposed FHV-LS and also analyzes the propagation delay. Section 4 proposes three improvements to optimize the propagation delay, deviation, and start-up. The performance of post-simulation is shown in Section 5. Section 6 concludes our work.

2. Review of Conventional FHV-LSs

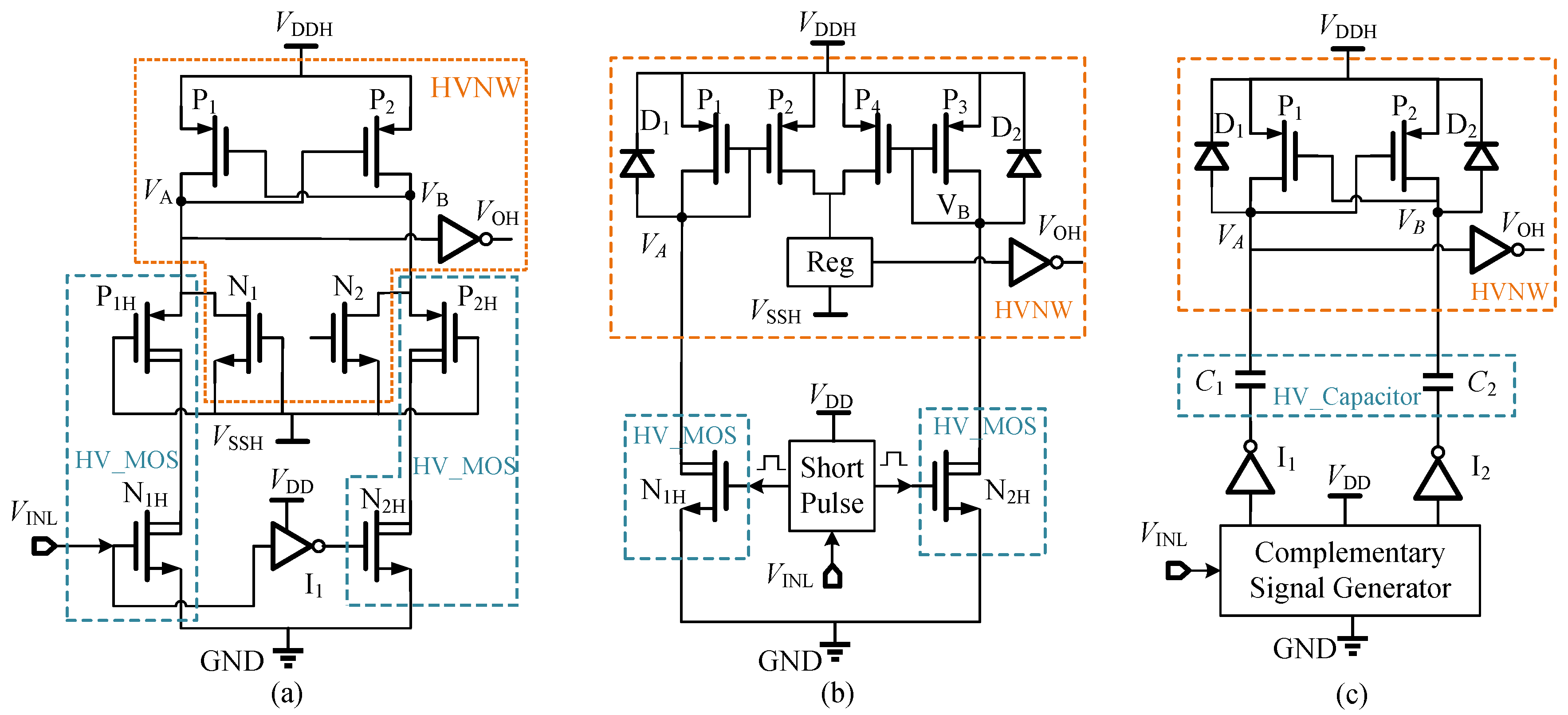

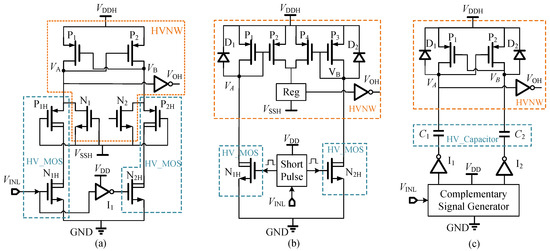

Many FHV-LSs have been proposed in the literature [13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,28,29] to reduce the propagation delay. According to the structures, three topologies (Topology-I, Topology-II, and Topology- III) are summarized in Figure 1. The devices in orange dashed boxes are placed in HV-NWell (HVNW). The body of HVNW biased with can tolerate high voltage. Consequently, the devices in HVNW could operate in the floating high-voltage domain between and . The devices in blue dashed boxes are HVMOS whose drain source and drain gate can handle high voltages, but its gate source switches in the low voltage range.

Figure 1.

Three topologies of FHV-LS: (a) DC-LS, (b) CM-LS, (c) CC-LS.

- (1)

- Topology-I: DC-LS

The first topology of FHV-LS is direct-coupled level shifter (DC-LS), as depicted in Figure 1a. The HV-NMOS transistors / are used to convert the input signal into its drain current. The HV-PMOS transistors / transfer its drain current into voltage and isolate the high drain voltage to protect the devices in HVNW. The NMOS N/N are used to clamp the voltage / to not fall below . The DC-LS in [13,14] is a basic structure of FHV-LSs which features a sample structure and fewer components. The circuits are fabricated using silicon-on-insulator (SOI) technology to improve the voltage rate, but it has a large propagation delay and poor symmetry between the rising and falling propagation delays. The asymmetry between rising and falling propagation delay will induce deviation, which will increase with the decrease of propagation delay. To reduce the static power consumption, the input of FHV-LS is activated by a short pulse generator [15,16], but the propagation delays are still unsatisfactory, and the deviation between rising and falling propagation delay in [15] is not optimized. The DC-LSs proposed in [17,18] decrease the propagation delay and optimize the symmetry between the rising and falling propagation delays; however, the propagation delay is at least 2 ns. The nanosecond delay may not meet the needs of high-speed applications.

- (2)

- Topology-II: CM-LS

The second topology of FHV-LS structure is the current-mirror level shifter (CM-LS), as shown in Figure 1b. Compared with DC-LS, CM-LS has a large quiescent current induced by the current mirror. To improve the power efficiency, the HVNMOS transistors / of CM-LS are controlled by pulse signals. Reg is a register to hold the output state. The current mirrors, composed of / and /, are used to change the state of Reg according to the input state of . The diodes D/D are reversely paralleled with / to clamp the voltage / to protect the devices in HVNW. The CM-LS in [19,20,21] utilizes a short pulse generator to control HV-MOS /. With signal conversion, the state of the latch unit is changed by the short pulse current. To reduce power consumption, an instantaneous-power-consuming level shifter is proposed to increase the efficiency [22] since the output detector is used to turn the level shifter off before the delay time. The CM-LSs proposed in [23,24,25] alter the state of RS-trigger by the voltage cross a resistor. This structure is commonly found in higher-voltage level shifters. It also needs the Schottky diodes in reverse parallel across the resistors to protect the devices in HVNW. Considering the influence of the process, temperature, and parasitic effect, the pulse width of the short pulse should have enough margins to guarantee that the latch unit can be flipped reliably. However, extending the width of the input pulse will lead to an increase in the power consumption and design complexity. Therefore, the pulse width should be optimized according to the power consumption and performance.

- (3)

- Topology-III: CC-LS

The third topology of FHV-LS is a capacitor-coupled level shifter (CC-LS), as shown in Figure 1c. High-voltage capacitors, and , are used to shift the input signal to the output with the high common-mode voltage. The CC-LS proposed in [26] has a propagation delay of 0.5 ns and low static current consumption, but requires an off-chip capacitor to enhance the power PMOS driving capability. The CC-LS in [27] integrates two on-chip capacitors (both 60 fF) to shift the signal from to , but the rising/falling propagation delay of 1.45 ns/1.3 ns is large for the 180 nm process. The CC-LS in [28] achieves a 0.5 ns propagation delay with two 2 pF on-chip capacitors. The CC-LS in [29] achieves a 115 ps propagation delay by isolated low-voltage NMOS transistors and capacitive coupling, but the current mirror of the level shifter in [28,29] is not turned off after converting, resulting in high power consumption.

3. Proposed FHV-LS

3.1. Design Approach of Proposed FHV-LS

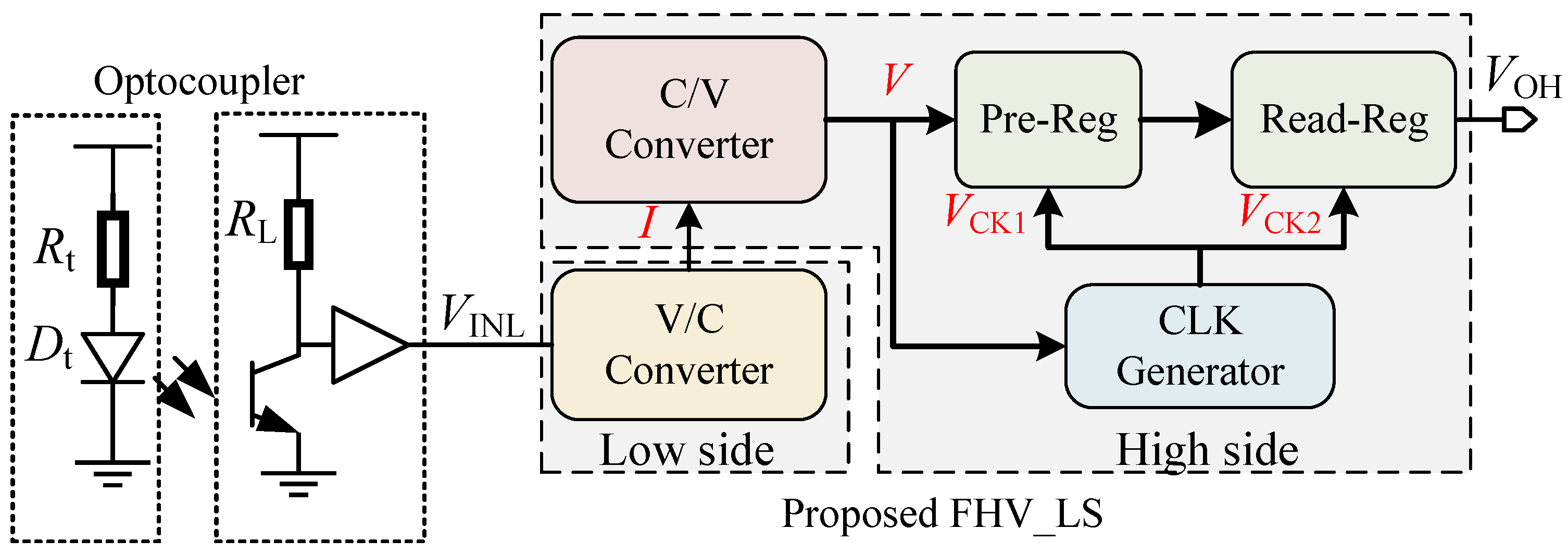

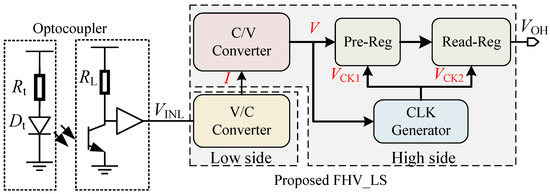

The gate drivers with FHV-LS are commonly used to control the power devices. However, the electrical noise generated by power circuits is also coupled to the driver stage by means of electricity or magnetism. To reduce the risk of false trigger, optocouplers are applied to achieve electrical isolation between the control signals and the high-voltage signals. Then, the optocoupler transmits the control signal to the input of the level-shifting circuit as shown in Figure 2. The proposed FHV_LS is composed of high-side circuit and low-side circuit. The high-side circuit consists of C/V converter, registers (pre-Reg, read-Reg), and CLK generator. The V/C converter on the low side converts the input voltage into the current signal . The C/V converter on the high side then transforms the current into the voltage which is the input to the CLK generator and pre-Reg. The CLK generator generates the control signals and to enable the pre-Reg and read-Reg in the latch or transfer mode. If pre-Reg operates in the transfer mode, the output of the C/V converter is stored in pre-Reg, while read-Reg works in the latch mode to hold . Conversely, pre-Reg operates in latch mode, and read-Reg is in transfer mode to transmit the output of pre-Reg to . Based on the mode switching for registers, the "next" state of is loaded in pre-Reg in the steady state. During the switching of , the input state restored in pre-Reg is transmitted to the output under the control of /. In other words, the present state of is transmitted to . Therefore, the propagation delay of FHV-LS is determined by the delay from to .

Figure 2.

Topology of the proposed FHV-LS.

3.2. Implementation of the Proposed FHV-LS

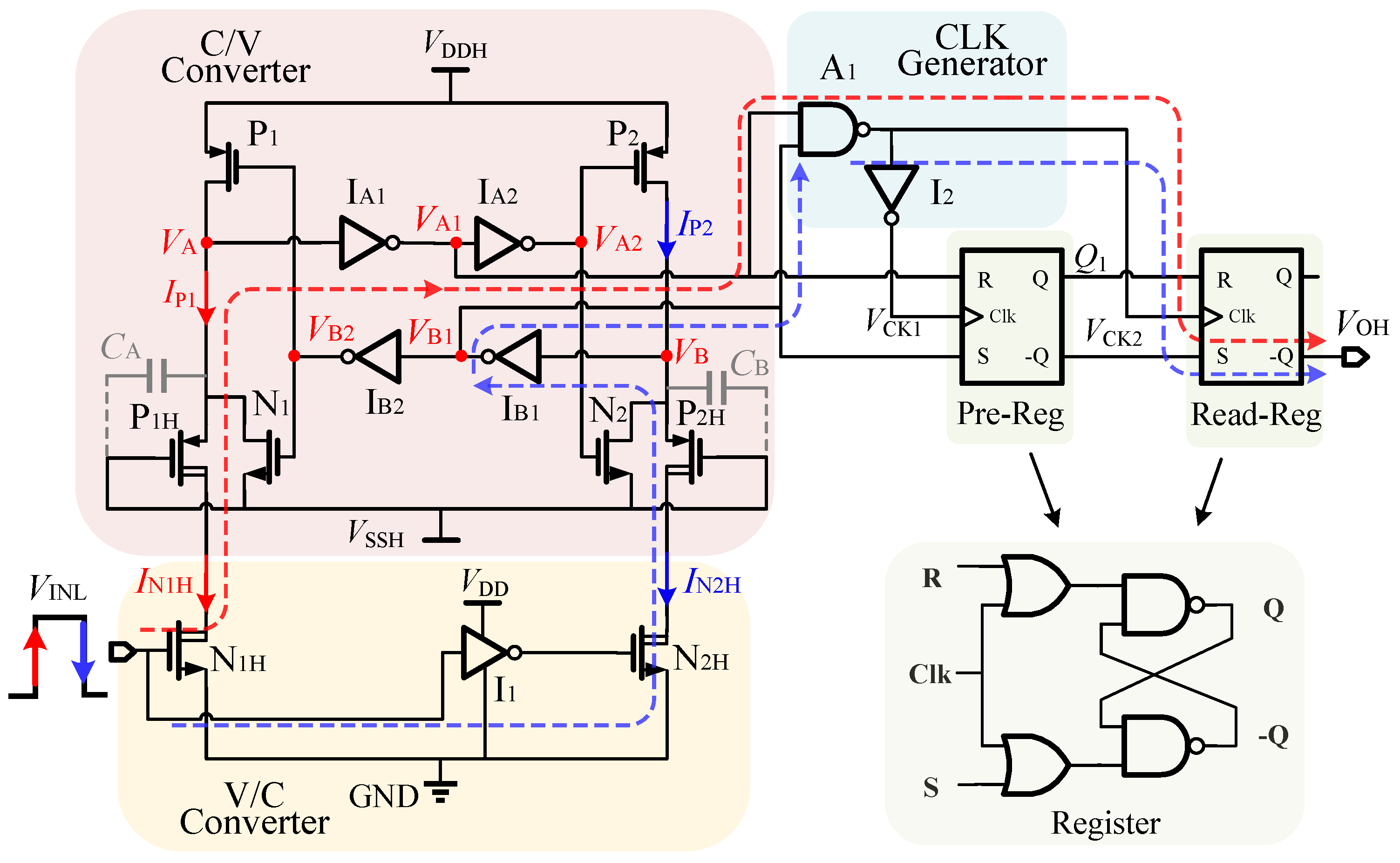

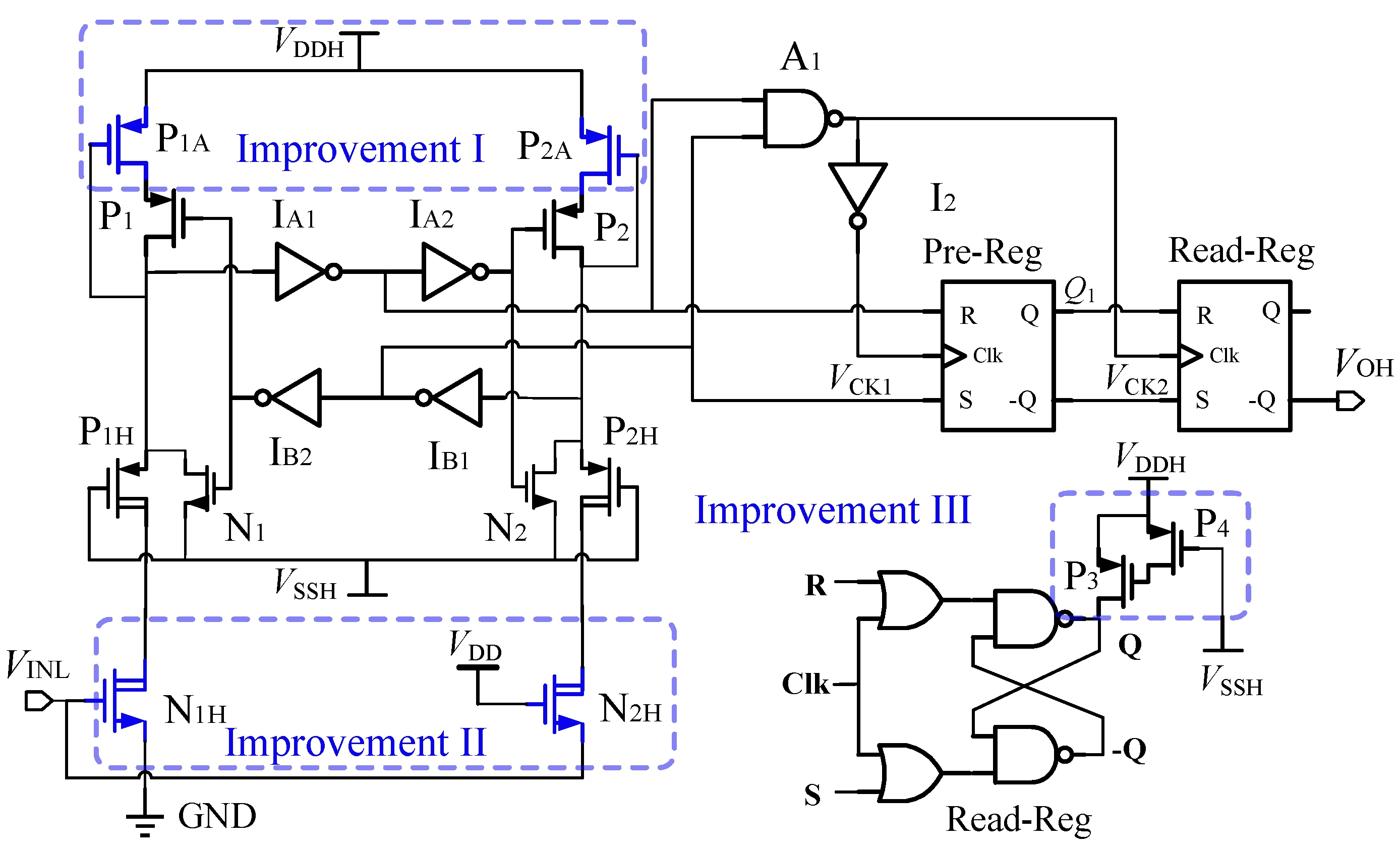

The implementation of the proposed FHV-LS is depicted in Figure 3. It involves two power rails, namely the low-side power rail (-GND) and the high-side power rail (-). The V/C converter on the low side is composed of HV-NMOS (-) and inverter . The logic states of and are flipped by . The C/V converter on the high side consists of transistors (-, -), inverters -, -), and HV-PMOS (-). The CLK generator is composed of the Nand gate and inverter . The pre-Reg/read-Reg registers controlled by / are clock-controlled RS flip-flops. The signal transmission paths of proposed FHV-LS from to are highlighted with red and blue dashed lines during witches. To make the formula clear, "0/1" represent logic low/high for the high-side and low-side logic signals.

Figure 3.

Implementation of the proposed FHV-LS.

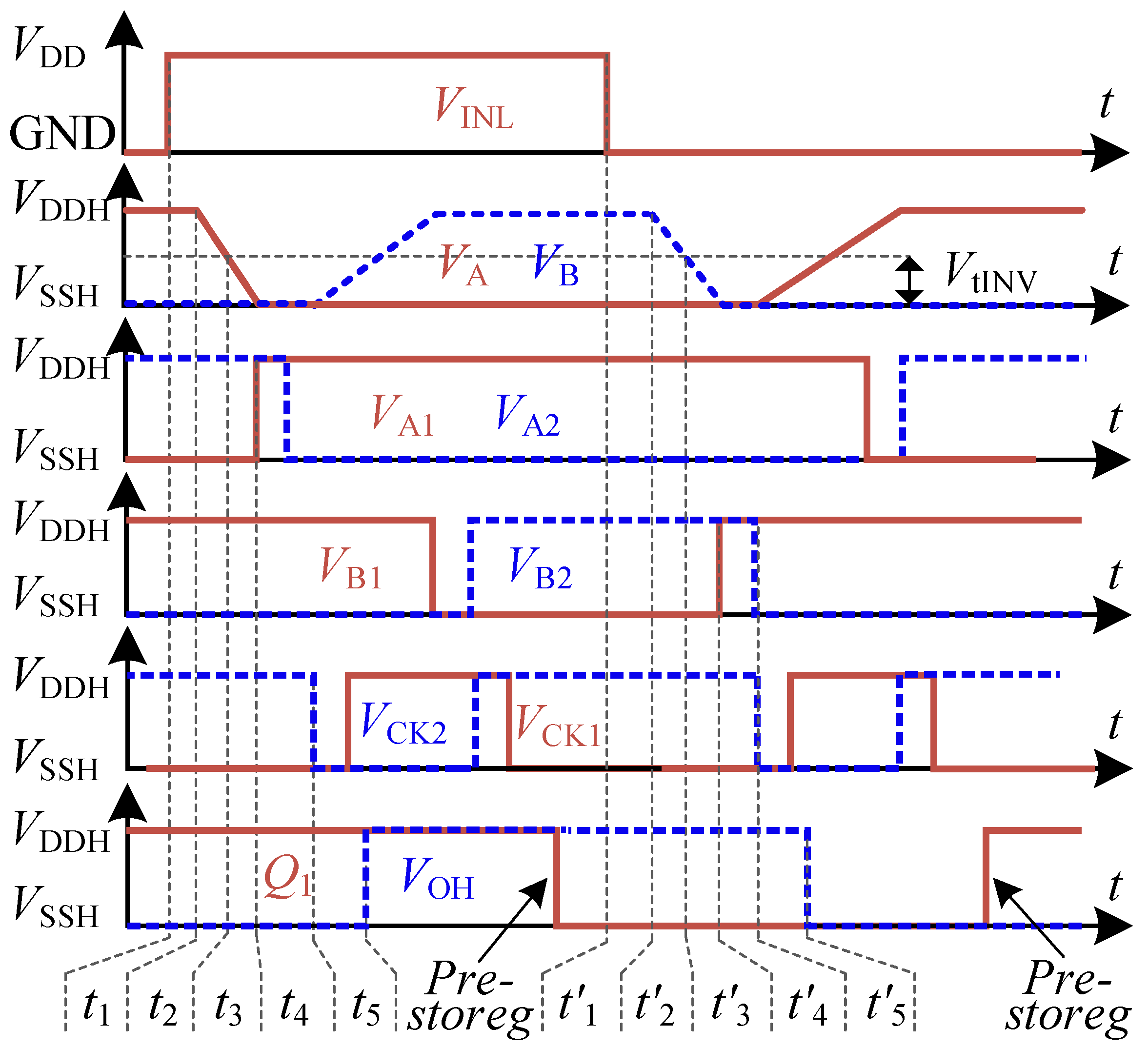

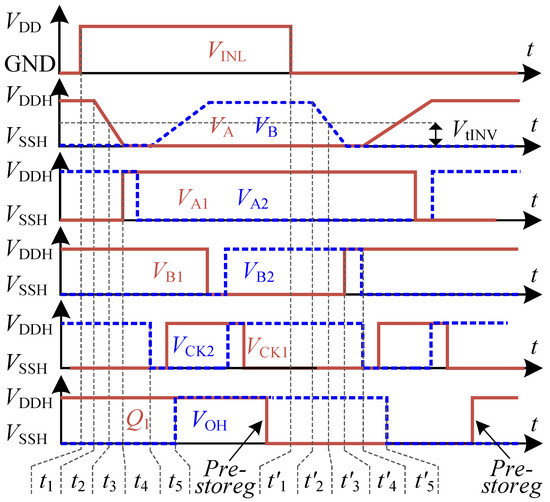

The operating process of the proposed FHV_LS is depicted as shown in Figure 4. We assume that = 0 is the initial input state. In this state, , N, , and are turned off. , N, , and are turned on and operate in the linear region. So, = = = 1, = = = 0. The outputs of the CLK generator are = 0 and = 1. According to the register, pre-Reg operates in the transfer mode, while read-Reg is in the latch mode. The output of pre-Reg is determined by the logic of and , so = 1. It indicates that the next state of is loaded in pre-Reg in the steady state. For the latch mode of read-Reg, it is worth mentioning that the output of read-Reg is an uncertain value during power-up. So, the start-up circuit is required to force the output state of read-Reg to be = 0. The start-up circuits will be discussed in Section 4.

Figure 4.

Propagation delay segments of proposed FHV-LS.

When varies from GND to rapidly, the signals of FHV-LS are transmitted along with the red dashed line. Firstly, is turned on, and operates in saturation. Then is off after the delay of inverter . To ensure the high-side logic circuits work well, we must succeed in taking below the threshold of inverter . It requires that the current / is larger than the current of / before falls below . Otherwise, the state of high-side circuits can not be flipped. As voltage is lower than the threshold of , the output states of inverter are reversed. Thus, = 0, and is turned on to pull up voltage . At the beginning, is lower than the threshold of inverter , = = 1. During this critical time interval, = 1 and = 0. Accordingly, pre-Reg operates in the latch mode while read-Reg in the transfer mode. The state of = 1 stored in the pre-Reg is then transferred to the output of read-Reg. Thus, = = 1. It can be considered that the current input state = 1 is transmitted to during this period. As voltage rises above the threshold of inverter , = 0, = 1. is turned off, and is clamped to floating ground by the conducted NMOS N. Then, goes into linear region to reduce the drain current . Due to = 0, = 1, pre-Reg operates in the transfer mode, and the read-Reg works in latch-mode. The inputs of pre-Reg are = 1 and = 0, so = 0. As a result, pre-Reg is loaded with the next state of again.

When varies from to GND rapidly, is turned off and is turned on after the delay of inverter I. The signal transmission path is shown as the blue dashed line in Figure 3. Due to the symmetrical circuit structures, the transmission paths are similar. It will not be discussed again.

3.3. Propagation Delay Analysis

The propagation delay from to can be subdivided into five segments. The segments of the rising and falling propagation delays are depicted in Figure 4. To simplify the expression of equation, we take the following abbreviation: = − and all voltages on the high side are referenced by .

Delay is the transmission time of the V/C converter from to the current . It is determined by the intrinsic delay of / which can be minimized using the minimum channel length to decrease the parasitic capacitance. Delay is the transmission time from to . Due to the delay of inverter I, delay is longer than . Thus, and are given by

After delay (), () is turned on. The parasitic capacitor () will be discharged to pull down the voltage (). Delay is the time taken for () to fall from to the threshold voltage of inverter (). is denoted as the fall time. In this delay interval, / operating in the saturation region is taken as a current source. The current can be expressed by

Since / operates in the linear region, it can be treated as a resistance .

where and are the threshold voltages of () and (), respectively.

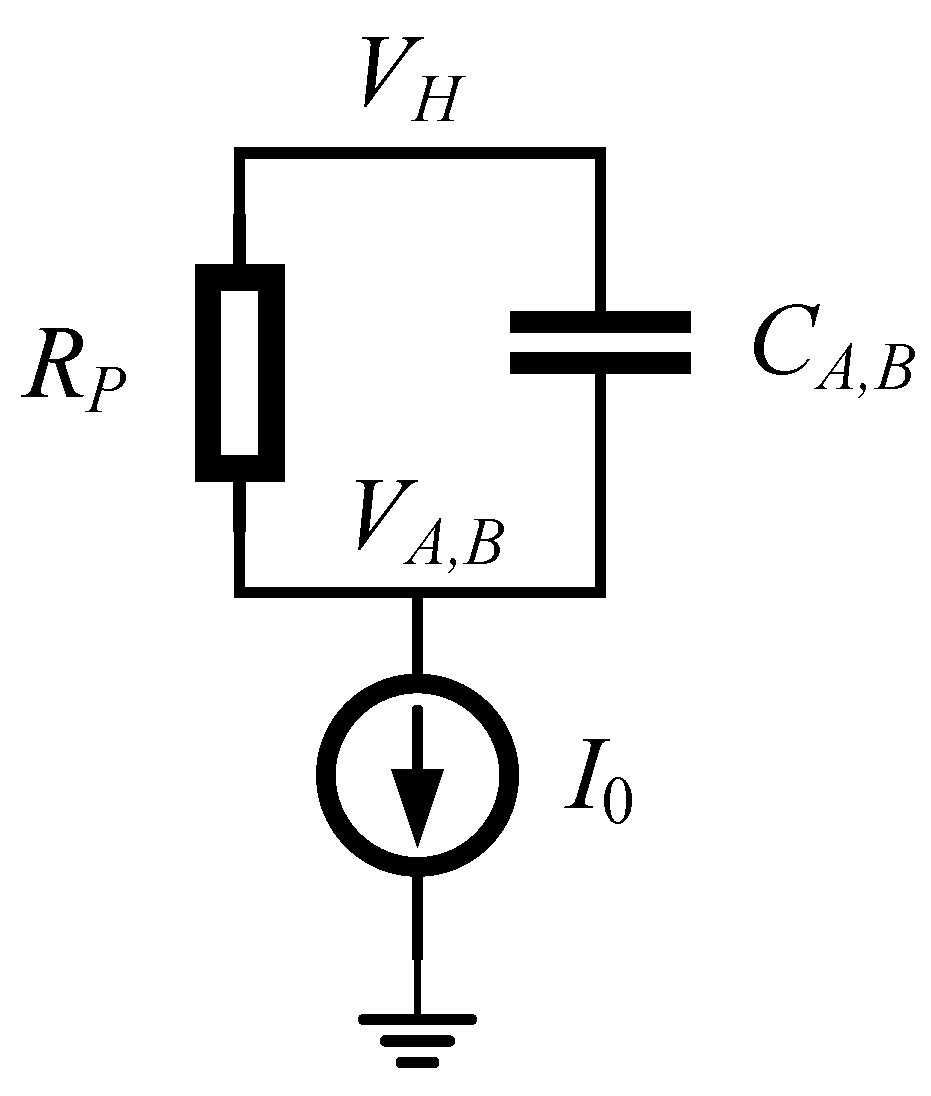

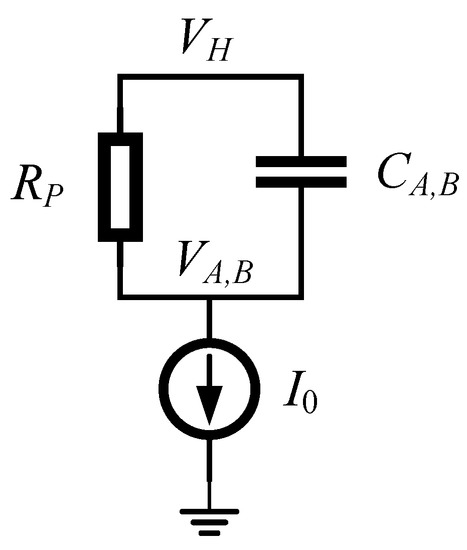

The equivalent circuit during the fall time of is shown in Figure 5. The capacitor () is the total parasitic capacitance at node (). The equivalent circuit can be regarded as an RC network composed of and (), which is discharged by the current source . The RC constant time can be found as . Thus, the voltages can be expressed by

Figure 5.

Equivalent circuit during the fall time of .

It is found from Equation (5) that will decrease with the increase of t. When the time increases to infinity, will be close to . In other words, will decrease to a lower value with the increase of under the same time condition.

It follows from (5) that the fall time () can be derived as

To flip the state of inverter (), () should fall below the threshold voltage of (). Therefore, the relationship should be satisfied in circuit design

Usually, and . Under the typical condition, we have = . Plugging (3) and (4) into (7), the sizes of / and / should satisfy the following:

As can be seen from (6), the fall time can be optimized by altering , and to reduce propagation delay. So, we perform the following arithmetic with .

It can be concluded from (12) that is positively correlated with . If we assume , then . This means that the maximum value of is zero. Thus, the relationship between and is

On the other hand, it can also be seen from Figure 5 that increasing the resistance can help to accelerate the discharge of the capacitor . Therefore, the fall time of will reduce with the increase of .

As can be observed from (9), (10) and (13), the fall time is negatively correlated with , and . In other words, increasing , and can reduce the fall time . We can use large-sized devices / to increase current , but it will also increase the chip area and power consumption. The threshold voltage can be raised by enhancing the pull-up ability or by mitigating the pull-down strength of inverter /. The maximum can be set close to - . is the threshold voltage of the PMOS on the high side. Similarly, ( ) will decrease with the increase of , while minimizing the ratio W/L of / can increase the pull-up resistance .

When () falls below the threshold of inverter (), voltage () will be pulled up to high after the delay of inverter () Therefore, the delay () is the transmission time of inverter ().

As and are both high, tends to be low after the delay of Nand A1. The read-Reg works in transfer-mode, while pre-Reg is in the latch mode. Then the output state of the pre-Reg is transmitted to the output after the read-Reg delay . The read-Reg is composed of two Nand gates with a cross-coupled connection. Usually, we set delay the same as the inverter delay . Thus, delay is twice the delay . As a result, and are expressed by

Thus, the rising propagation delay from the rising edge of to is found by

Likewise, the fall propagation delay from the falling edge of to is found by

As can be seen from (17) and (18), the propagation delay consists of the intrinsic delay of HV-NMOS, logic gate delay, and () fall time. Due to the trade-off between power consumption and area, it is quite limited to decrease the intrinsic delay of MOSFET and the delay of the logic gate. As can be seen from (13), reduction of the fall time is a feasible solution to reducing the propagation delay of the proposed FHV-LS. The improvements will be introduced in the next section.

4. Improvements of Proposed FHV-LS

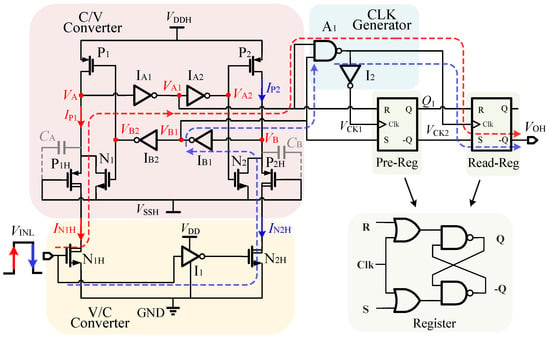

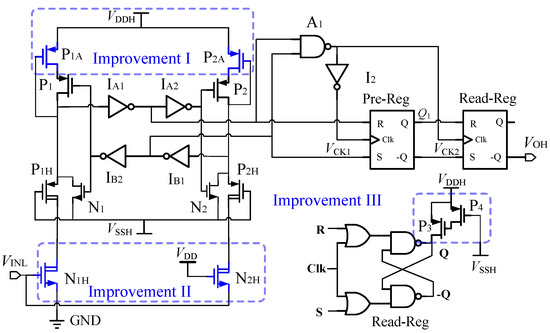

It follows from (13) that the fall time is negatively correlated with the on-resistance of /. During fall time , the pull-up network () operating in the linear region has low on-resistance . It will prolong the discharge time of parasitic capacitance / at / node and also increase the fall time . Hence, an effective solution to reducing the fall time is to increase . Comparing (17) and (18), the difference between the rising and falling propagation delays is caused by delay of the low-side inverter. It will induce a deviation between rising and falling propagation delay. With the decrease in propagation delay, the distortion will increase. In this section, three improvements will be performed to optimize the propagation delay, deviation, and start-up of the proposed FHV-LS. Simple improvements can be made to the basic design, as shown in Figure 6. In addition, the device parameters of the improved FHV_LS are summarized in Table 1.

Figure 6.

Improvements in propagation delay, symmetry, and startup circuit.

Table 1.

Devices parameters of the proposed FHV_LS.

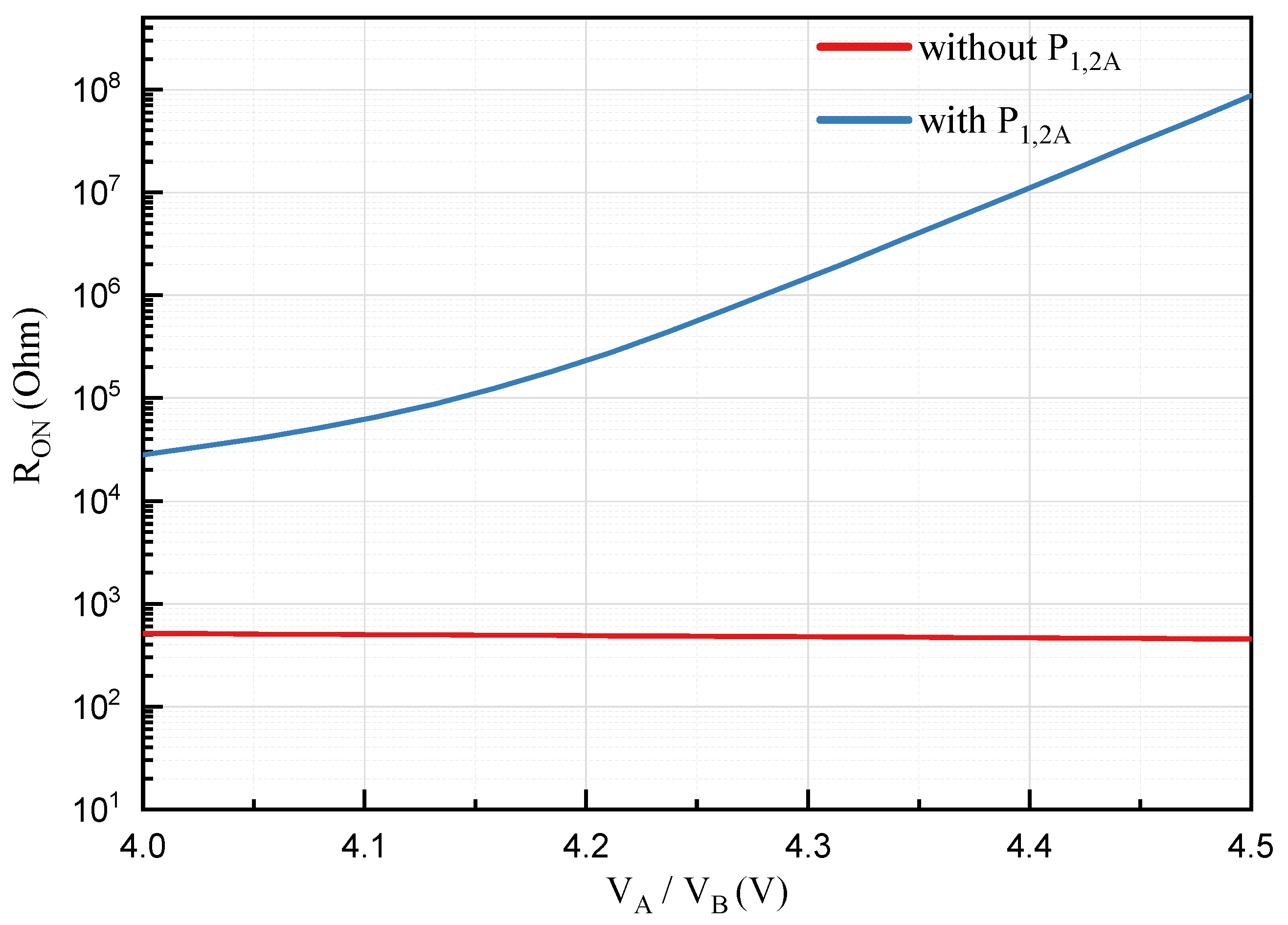

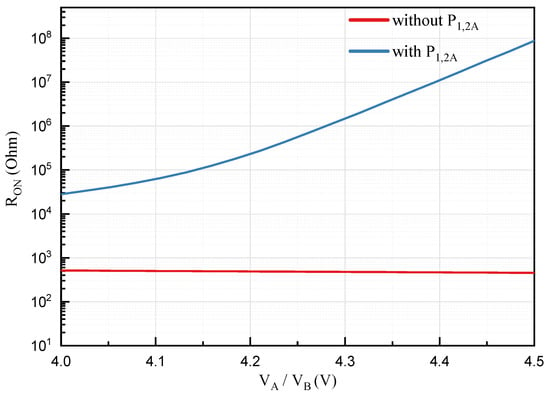

4.1. Improvement-I Reduction of Propagation Delay

To decrease the fall time , the large on-resistance at the drain of / is required. For this purpose, a pull-up network with regulated strength [30,31] composed of () and () is applied as the improvement-I as depicted in Figure 6. During the fall time () interval, () operates in the linear region, and () is in sub-threshold region. In addition, maximizing will be able to reduce the fall time . Thus, is closed to by selecting the device size of . The on-resistance of () and () is simulated as illustrated in Figure 7. When is set to 4.2 V, the on-resistance with () is two orders of magnitude higher than without (), as / varies between 4.2 V and 5 V, as shown in Figure 7. The resistance of the regulated strength pull-up network is higher than the resistance of (). Therefore, the fall time and propagation delay of proposed FHV-LS will be decreased by the pull-up network with the regulated strength. Due to the reduction in pull-up capacity of the pull-up network with the regulated strength, the rise time of will increase. Fortunately, the propagation delay of the proposed FHV-LS is independent of the rise time of since the pre-storage technique optimizes the transmission path. Compared with traditional resistance enhancement techniques (replace with passive resistors), the pull-up network with the regulated strength can achieve a better trade-off between propagation delay, power consumption, and chip area.

Figure 7.

On-resistance of () with and without ().

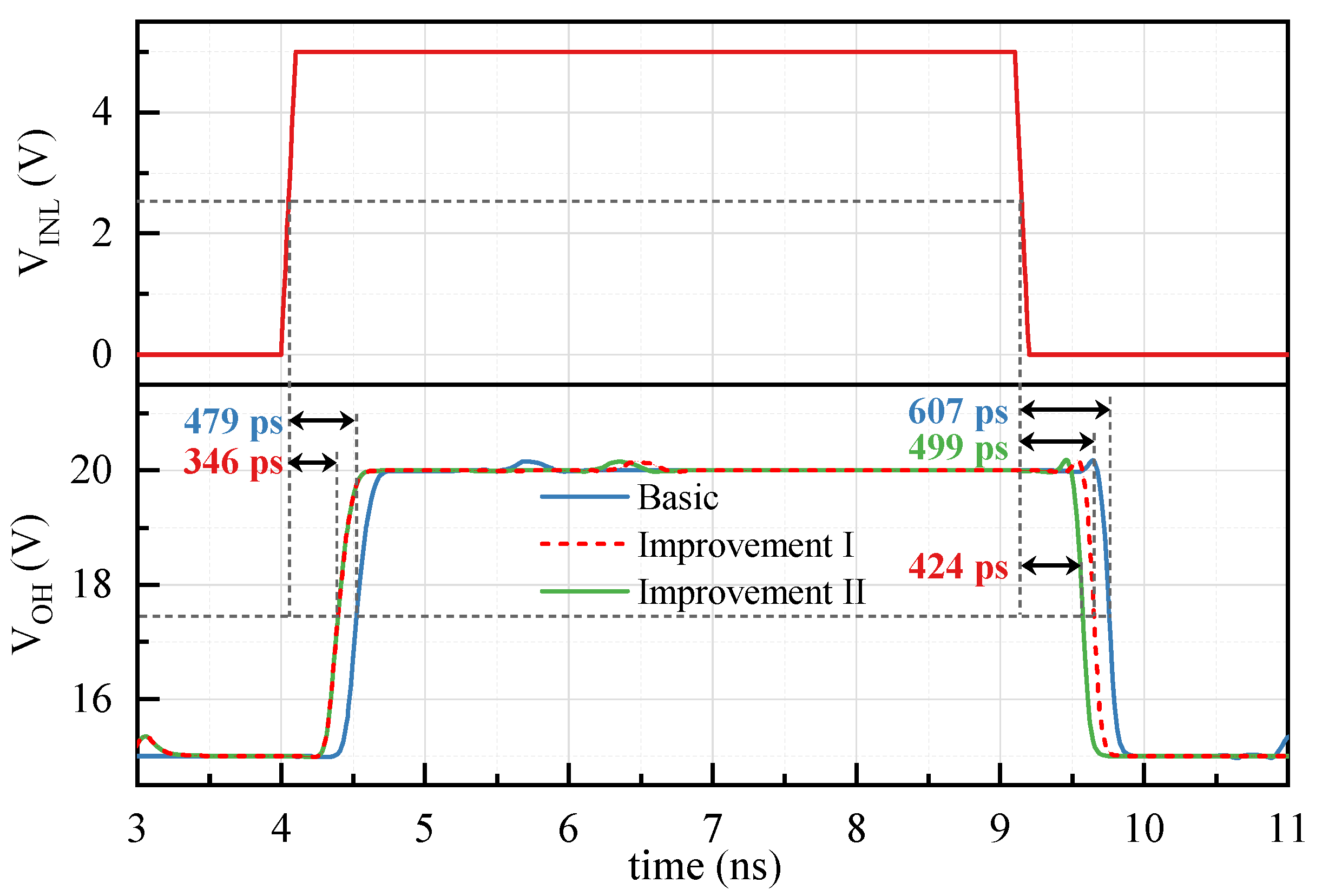

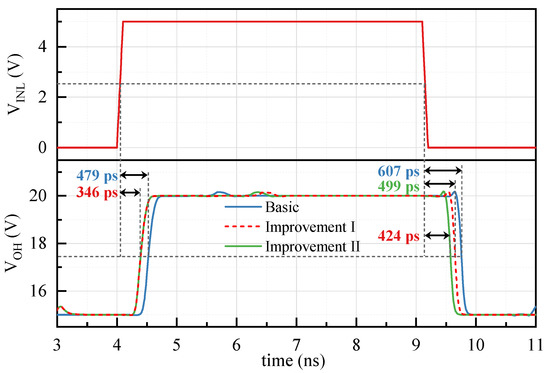

The post-layout simulation with Improvement-I is performed to verify the reduction in propagation delay as depicted in Figure 8. Compared with the basic proposed FHV-LS, the rising propagation delay with Improvement-I decreases from 479 ps to 346 ps, and the fall propagation delay drops from 607 ps to 499 ps. In other word, the average propagation delay is reduced by 22%.

Figure 8.

Simulation on the propagation delay with Improvement-I and Improvement-II.

4.2. Improvement-II Optimizing the Symmetry of Propagation Delay

The deviation between the rising and falling propagation delays is induced by the transmission delay of inverter I on the low side. The common-gate structure is introduced to replace the low-side inverter as Improvement-II [32,33], as shown in Figure 6. The source terminal of is connected to directly, forming a pseudosymmetry input pair. The input of is the gate, while the input of is the source. is the common input signal of and . The switching processes of and are almost simultaneous. From another perspective, the left and right branches of the proposed FHV-LS are quasi-symmetrical structurally. As a result, the deviation between rising and falling propagation delay will be reduced. However, the transistor exhibits body effect as the source/body is separated. With the same size, the intrinsic delay of is longer than that of . Compared with the inverter delay, this difference is very small.

The post-layout simulation with Improvement-II is performed to verify the reduction in deviation between the rising and falling propagation delays in Figure 8. The falling propagation delay decreases from 499 ps to 424 ps, while the rising propagation delay is unchanged. The reduction in falling propagation delay is attributed to the introduction of the quasi-symmetrical input to replace the inverter on the low side. The deviation between rising and falling propagation delay decreases from 36% to 20%. The difference between the rising and falling propagation delays is 75 ps which is caused by the body effect of .

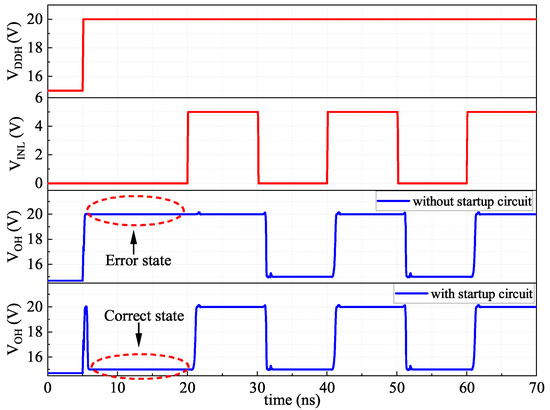

4.3. Improvement-III Start-Up Circuit

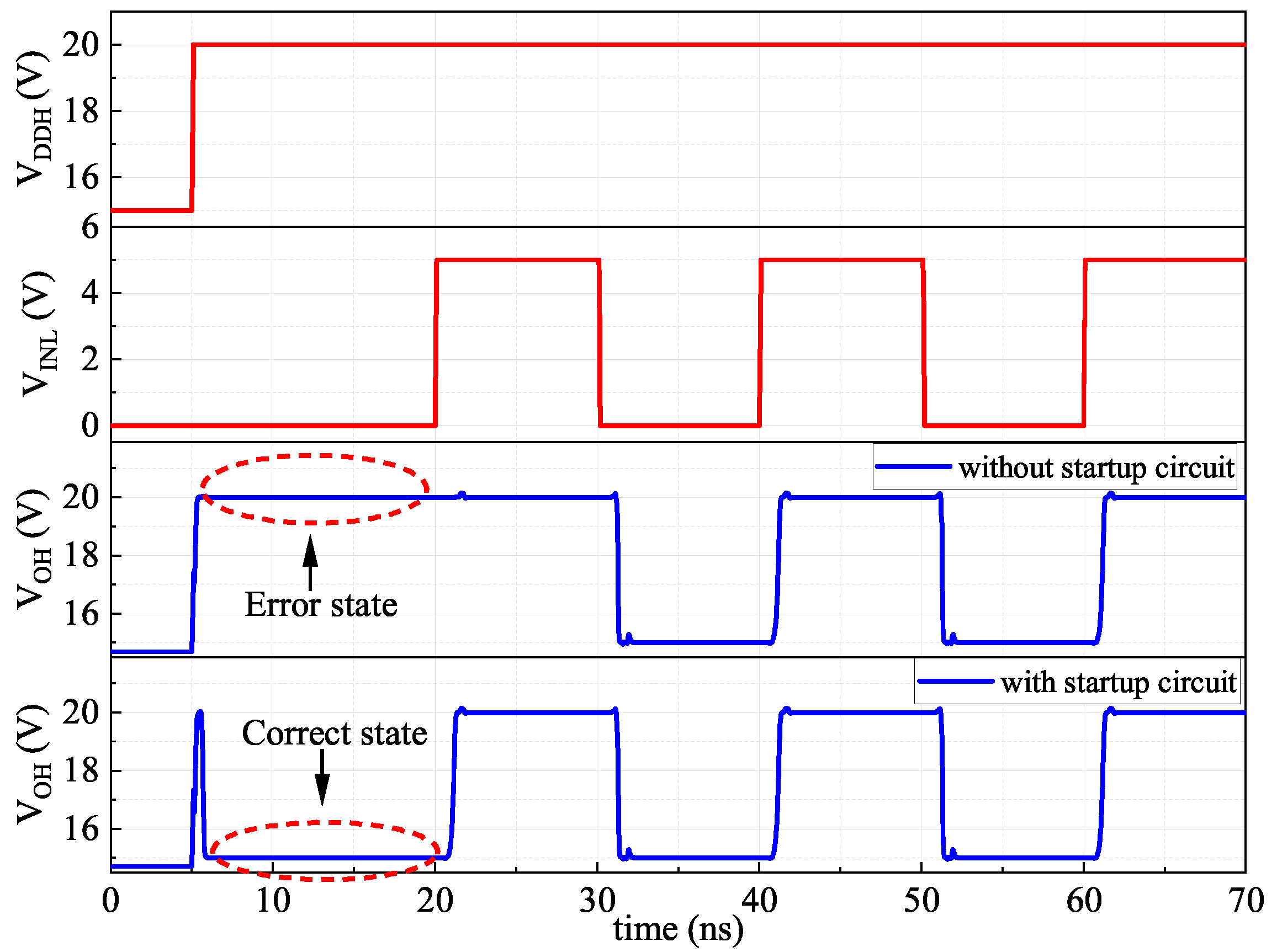

When is powered up, the output of the proposed FHV-LS is a uncertain state due to the read-Reg in latch mode. To overcome this problem, a start-up circuit composed of / is developed to initialize the state of the read-Reg, as shown in Figure 6. During power-up, the current of pulls the Q of read-Reg to high. Consequently, is low. Then is turned off by . There is no quiescent current consumption on / after power-up. The outputs of read-Reg with and without the start-up circuit are simulated in Figure 9. In case of no start-up circuit, the output of read-Reg is high after power-up. It is an error state, which is not in agreement with input . With the start-up circuit, the is pulled down after power-up. As a result, the follows the input correctly under any operating conditions.

Figure 9.

The output state of proposed FHV-LS with and without the start-up circuit during power-up.

5. Post-Layout Simulation

To comprehensively evaluate the performance of the proposed FHV_LS, post-layout simulations are performed for the propagation delay, power consumption, and stability. The simulation tool used for this work is Cadence Spectre Simulator (Cadence Design Systems, Inc., San Jose, CA, USA), version 6.17. In addition, the design and verification tools for the layout of this wok are Cadence Virtuoso Layout Suite (Cadence Design Systems, Inc., San Jose, CA, USA) and Mentor Graphics Calibre (Mentor Graphics Corporation, Plano, TX, USA), respectively.

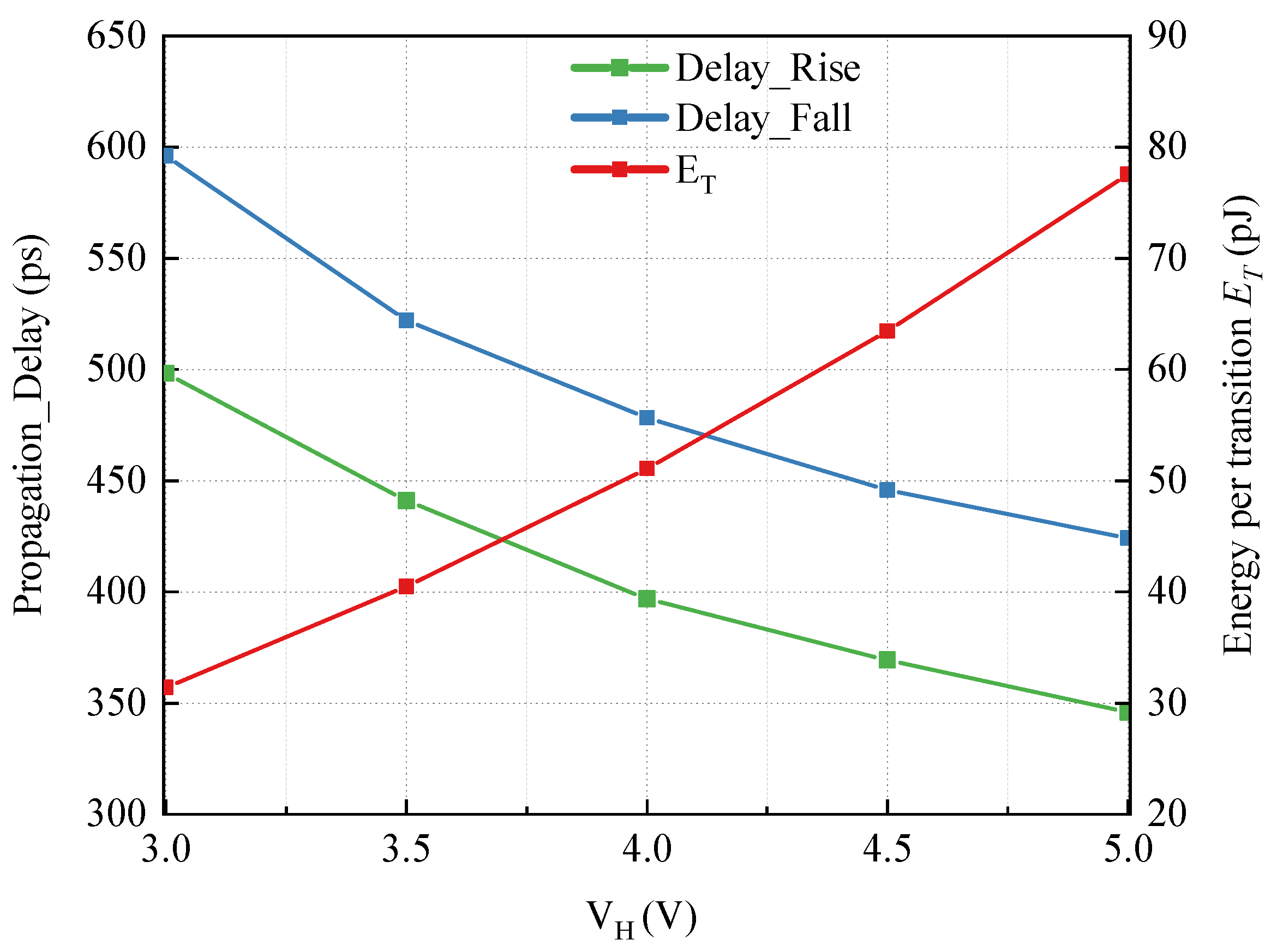

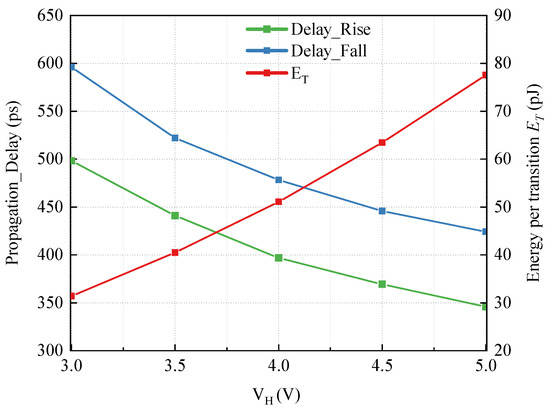

5.1. Supply Voltage Simulation

The average propagation delay and power consumption versus supply voltage are exhibited in Figure 10. As varies from 3 V to 5 V, the rising propagation delay changes from 498 ps to 346 ps and the falling propagation delay changes from 596 ps to 424 ps, while the changes from 31.5 pJ to 77.5 pJ. From Equations (17) and (18), it is known that the propagation delays consist of the delays of logic gates and the fall time of , which are nonlinear with respect to the supply voltage, taking Equations (3) and (4) into condition. Therefore, there is a nonlinear relationship between the propagation delay and supply voltage. On the other hand, the delay of logic gates, as can be seen from Equations (17) and (18), is the major component in the propagation delay. Based on the principle of integrated circuit, the propagation delay of logic gates decreases as the supply voltage increases. As a result, it can be found from Figure 10 that the propagation delays of proposed FHV-LS are negatively correlated with the supply voltage. To achieve low propagation delay, higher supply voltage is required, but power consumption is increased as well. In addition, the rising propagation delay is lower than falling propagation delay since the body effect exists in the input device . With Improvement-II, the deviation between rising and falling propagation is lower than 17%.

Figure 10.

Simulation of the propagation delay and energy per transition () versus power supply .

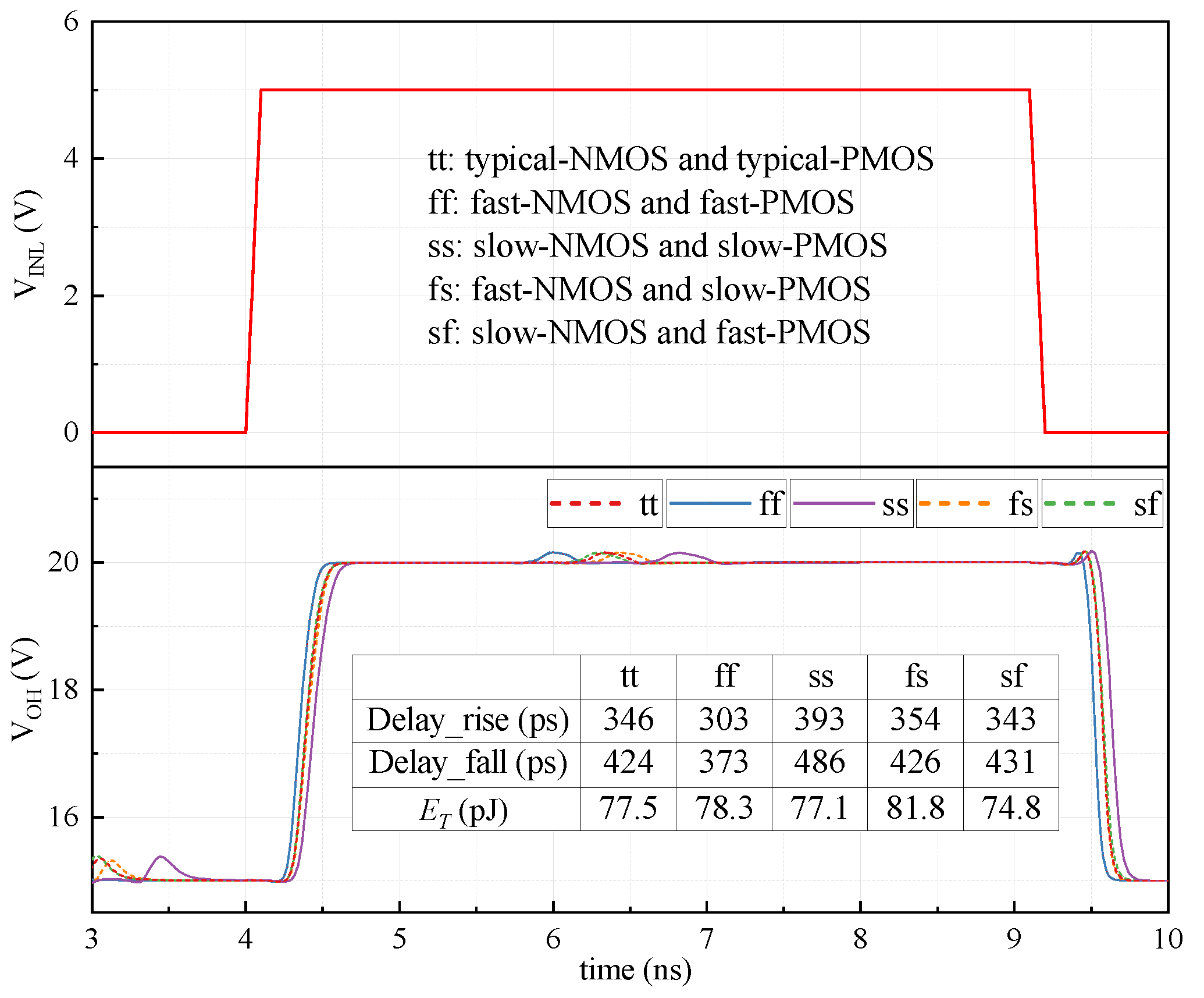

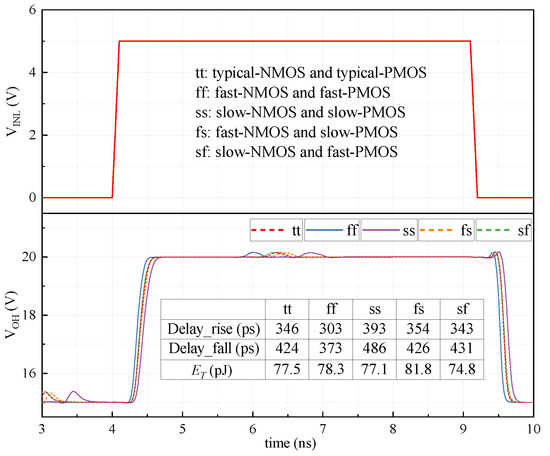

5.2. Process Corners Simulation

The propagation delay and at different process corners are simulated in Figure 11. The rising and falling propagation delay at typical process corner are 346 ps and 424 ps, respectively. Based on the typical process corner, the drift value on propagation delay at ss and ff corners is lower than 15%, and the drift value on propagation delay at fs and sf process corners is lower than 2.5%. As can be seen from Figure 11, the maximum power consumption of appears at the fs corner. At this corner, the logic threshold of is lower than that of other corners. As a result, the dynamic power consumption of at the fs corner will increase. Conversely, the dynamic power consumption of at the sf corner will decrease for the higher logic threshold, since the logic thresholds at tt/ff/ss corners are almost unchanged, and they also have similar energy per transition ().

Figure 11.

Simulations on the propagation delay and at different process corners.

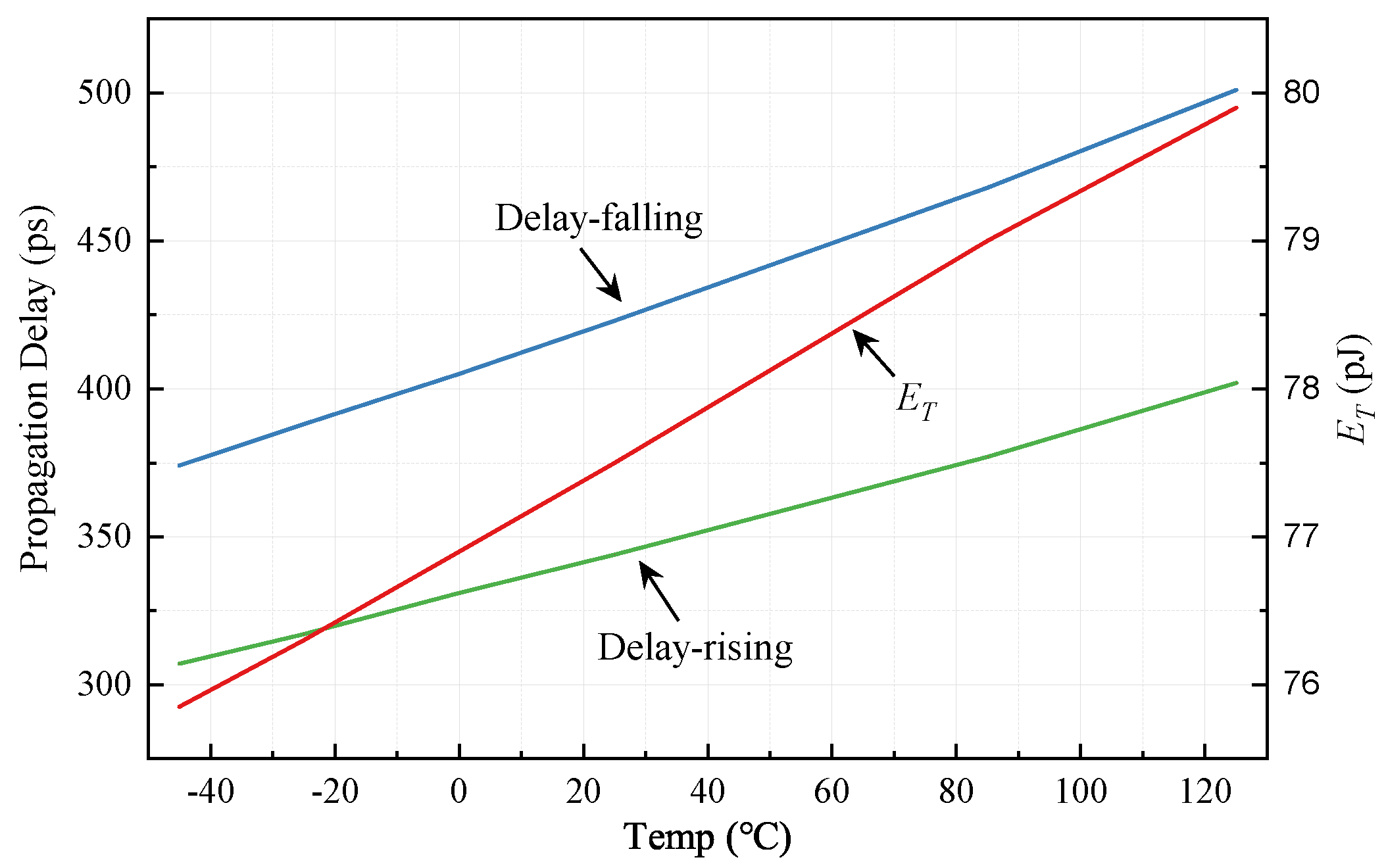

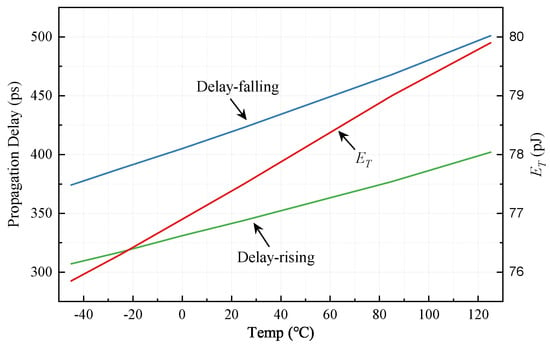

5.3. Temperature Simulation

The simulation of the propagation delay and at different temperature are shown in Figure 12. As temperature varies from −40 C to 125 C, the rising and falling propagation delays increase from 307 ps to 402 ps and from 374 ps to 501 ps, respectively. Therefore, the temperature coefficients of the rising and falling propagation delay are 0.75 ps/C and 0.56 ps/C, respectively. As can be seen from the figure, is positively correlated with the temperature as well. The temperature coefficient of is 0.024 pJ/C.

Figure 12.

Propagation delay and versus temperature simulation.

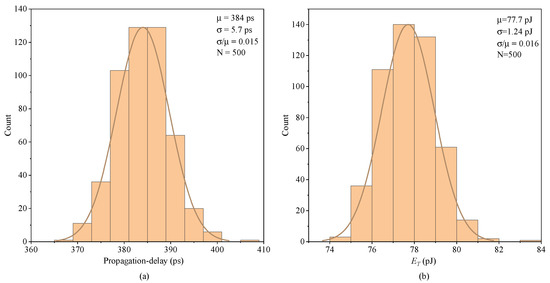

5.4. Monte Carlo Simulation

To study the variation against the device mismatch and process, 500-point Monte Carlo simulations on the propagation delay and of the proposed FHV-LS are carried out in Figure 13. The simulation conditions are = 20 V, =15 V, = 5 V, and = 1 MHz. With statistical analysis, the means of the propagation delays and are 384 ps and 77.7 pJ, respectively. Their normalized standard deviations (/) are 0.015 and 0.016, respectively. As can be seen from the simulation results, the propagation delay and have good stability against process variation and devices mismatch.

Figure 13.

Monte Carlo simulation: (a) Average propagation delay, (b) .

5.5. Discussion

To reduce the propagation delay, a pull-up network with regulated strength is applied to increase the pull-up resistance. The advantage of Improvement I is that the fall time of is reduced. On the one hand, the rise time of is increased due to the large pull-up resistance. As a result, the maximum operating frequency should not exceed 100 MHz for the proposed FHV-LS. However, the operating frequency of insulated gate bipolar transistor (IGBT) and SiC power devices are lower than 10 MHz. Therefore, the frequency of 100 MHz is enough for the applications. On the other hand, the immunity for dV/dt of is reduced compared with the basic proposed FHV-LS. The maximum immunity for dV/dt of is 5 V/ns. Therefore, the proposed FHV-LS is appropriate for the application of half-bridge with low dV/dt or the half-bridge consisting of CMOS structure.

Table 2 summarizes the performance of the proposed LS and previous works. The process, supply voltage, propagation delay, , area, and figure of merit (FoM and FoM*) are listed in the table. The average propagation delay of the proposed FHV-LS is 384 ps using 0.32 m HVCMOS technology. In addition, FoM from [16] and FoM* from [20] are 0.06 and 38, respectively. The low propagation delay of this work mainly benefits from the pre-storage technique and the pull-up network with regulated strength. Specifically, the pre-storage technique decreases the number of delay units along the signal transmission path from to , leading to optimal transmission paths. To reduce the major delay in the propagation delay, a pull-up network with regulated strength is employed to increase the pull-up resistance . Consequently, the proposed FHV-LS features low propagation delay and FoM, as shown in Table 2. In addition, the propagation delay can be optimized according to the analysis of the propagation delay. Based on the operating mechanism of the integrated circuit, the power consumption can be reduced by increasing the propagation delay. In accordance with application requirements, the propagation delay and power consumption of the proposed FHV-LS can be optimized to achieve the trade-off.

Table 2.

Comparison with previous work.

6. Conclusions

In this paper, a novel FHV-LS with pre-storage technique is proposed to achieve low propagation delay. In the steady state, the input state of FHV-LS is stored in a register. As soon as the input starts switching, the state stored in the register is transmitted to the output of FHV-LS under the control of the CLK generator. Thus, the propagation delay of the proposed FHV-LS is reduced to the sub-nanosecond scale. Since the fall time in propagation delay is inversely correlated with the pull-up resistance , a pull-up network with the regulated strength is used to increase the pull-up resistance . Therefore, the average propagation delay reduces. To reduce the deviation between rising and falling propagation delay, a pseudosymmetry input pair is introduced to improve the symmetry of the proposed FHV-LS structurally. Moreover, a start-up circuit is designed to initialize the output state of FHV-LS during power-up. Post-layout simulation indicates that the average propagation delay and of the proposed FHV-LS are 384 ps and 77.7 pJ at = 5 V. Monte Carlo simulation results demonstrate that the proposed FHV-LS has good stability against process variation and devices mismatch.

Author Contributions

Data curation, H.M. and G.Y.; Formal analysis, Q.L.; Investigation, Y.Z.; Methodology, Q.L.; Project administration, Y.Y.; Software, G.Y. and M.Z.; Writing—review and editing, Y.Y. and W.X. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by National Natural Science Foundation of China, grant number 62174134. And Shaanxi Innovation Capability Support Project, grant number 2021TD-25.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Riazmontazer, H.; Mazumder, S.K. Optically Switched-Drive-Based Unified Independent dv/dt and di/dt Control for Turn-Off Transition of Power MOSFETs. IEEE Trans. Power Electron. 2015, 30, 2338–2349. [Google Scholar] [CrossRef]

- Ling, Y.; Zhao, Z.; Zhu, Y. A Self-Regulating Gate Driver for High-Power IGBTs. IEEE Trans. Power Electron. 2021, 36, 3450–3461. [Google Scholar] [CrossRef]

- Chen, H.Y.; Kao, Y.Y.; Zhang, Z.Q.; Liao, C.H.; Yang, H.Y.; Hsu, M.S.; Chen, K.H.; Lin, Y.H.; Lin, S.R.; Tsai, T.Y. 33.1 A Fully Integrated GaN-on-Silicon Gate Driver and GaN Switch with Temperature-compensated Fast Turn-on Technique for Improving Reliability. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 460–462. [Google Scholar] [CrossRef]

- Camacho, A.P.; Sala, V.; Ghorbani, H.; Martinez, J.L.R. A Novel Active Gate Driver for Improving SiC MOSFET Switching Trajectory. IEEE Trans. Ind. Electron. 2017, 64, 9032–9042. [Google Scholar] [CrossRef]

- Yang, Y.; Wen, Y.; Gao, Y. A Novel Active Gate Driver for Improving Switching Performance of High-Power SiC MOSFET Modules. IEEE Trans. Power Electron. 2019, 34, 7775–7787. [Google Scholar] [CrossRef]

- Wen, Y.; Yang, Y.; Gao, Y. Active Gate Driver for Improving Current Sharing Performance of Paralleled High-Power SiC MOSFET Modules. IEEE Trans. Power Electron. 2021, 36, 1491–1505. [Google Scholar] [CrossRef]

- Sun, K.; Wang, J.; Burgos, R.; Boroyevich, D. Design, Analysis, and Discussion of Short Circuit and Overload Gate-Driver Dual-Protection Scheme for 1.2-kV, 400-A SiC MOSFET Modules. IEEE Trans. Power Electron. 2020, 35, 3054–3068. [Google Scholar] [CrossRef]

- Nevarez, J.; Olmedo, A.; Williams, R.; Pechnikova, P. Gate Driver Protection Methods for SiC MOSFET Short Circuit Testing. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–4. [Google Scholar] [CrossRef]

- Seidel, A.; Wicht, B. Integrated Gate Drivers Based on High-Voltage Energy Storing for GaN Transistors. IEEE J. Solid-State Circuit 2018, 53, 3446–3454. [Google Scholar] [CrossRef]

- Zhang, W.J.; Yu, J.; Cui, W.T.; Leng, Y.; Liang, J.; Hsieh, Y.T.; Tsai, H.H.; Juang, Y.Z.; Yeh, W.K.; Ng, W.T. A Smart Gate Driver IC for GaN Power HEMTs with Dynamic Ringing Suppression. IEEE Trans. Power Electron. 2021, 36, 14119–14132. [Google Scholar] [CrossRef]

- Zhang, Z.; Dix, J.; Wang, F.; Blalock, B.J.; Costinett, D.; Tolbert, L.M. Intelligent Gate Drive for Fast Switching and Crosstalk Suppression of SiC Devices. IEEE Trans. Power Electron. 2017, 32, 9319–9332. [Google Scholar] [CrossRef]

- Rouger, N.; Barazi, Y.; Cousineau, M.; Richardeau, F. Modular Multilevel SOI-CMOS Active Gate Driver Architecture for SiC MOSFETs. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 278–281. [Google Scholar] [CrossRef]

- Kobayashi, K.; Yanagigawa, H.; Mori, K.; Yamanaka, S.; Fujiwara, A. High voltage SOI CMOS IC technology for driving plasma display panels. In Proceedings of the 10th International Symposium on Power Semiconductor Devices and ICs. ISPSD’98 (IEEE Cat. No.98CH36212), Kyoto, Japan, 3–6 June 1998; pp. 141–144. [Google Scholar] [CrossRef]

- Choi, B.D. Enhancement of current driving capability in data driver ICs for plasma display panels. IEEE Trans. Consum. Electron. 2009, 55, 992–997. [Google Scholar] [CrossRef]

- Li, Y.; Wen, C.; Yuan, B.; Wen, L.; Ye, Q. A high speed and power-efficient level shifter for high voltage buck converter drivers. In Proceedings of the 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, 1–4 November 2010; pp. 309–311. [Google Scholar] [CrossRef]

- Liu, Z.; Cong, L.; Lee, H. Design of On-Chip Gate Drivers with Power-Efficient High-Speed Level Shifting and Dynamic Timing Control for High-Voltage Synchronous Switching Power Converters. IEEE J. Solid-State Circuits 2015, 50, 1463–1477. [Google Scholar] [CrossRef]

- Moghe, Y.; Lehmann, T.; Piessens, T. Nanosecond Delay Floating High Voltage Level Shifters in a 0.35 μm HV-CMOS Technology. IEEE J. Solid-State Circuits 2011, 46, 485–497. [Google Scholar] [CrossRef]

- Ming, X.; Zhang, X.; Zhang, Z.W.; Feng, X.D.; Hu, L.; Wang, X.; Wu, G.; Zhang, B. A high-voltage half-bridge gate drive circuit for GaN devices with high-speed low-power and high-noise-immunity level shifter. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 355–358. [Google Scholar] [CrossRef]

- Buyle, J.; De Gezelle, V.; Bakeroot, B.; Doutreloigne, J. A new type of level-shifter for n-type high side switches used in high-voltage switching ADSL line-drivers. In Proceedings of the 2008 15th IEEE International Conference on Electronics, Circuits and Systems, Saint Julian’s, Malta, 31 August–3 September 2008; pp. 954–957. [Google Scholar] [CrossRef]

- Liu, D.; Hollis, S.J.; Dymond, H.C.P.; McNeill, N.; Stark, B.H. Design of 370-ps Delay Floating-Voltage Level Shifters With 30-V/ns Power Supply Slew Tolerance. IEEE Trans. Circuits Syst. II Exp. Briefs 2016, 63, 688–692. [Google Scholar] [CrossRef] [Green Version]

- Liu, D.; Hollis, S.J.; Stark, B.H. A New Design Technique for Sub-Nanosecond Delay and 200 V/ns Power Supply Slew-Tolerant Floating Voltage Level Shifters for GaN SMPS. IEEE Trans. Circuits Syst. I Reg. Pap. 2019, 66, 1280–1290. [Google Scholar] [CrossRef] [Green Version]

- Ma, H.; Namgoong, G.; Choi, E.; Bien, F. Instantaneous Power Consuming Level Shifter for Improving Power Conversion Efficiency of Buck Converter. IEEE Trans. Circuits Syst. II Exp. Briefs 2019, 66, 1207–1211. [Google Scholar] [CrossRef]

- Li, F.; Giannopoulos, D.; Wacyk, I. A low loss high-frequency half-bridge driver with integrated power devices using EZ-HV SOI technology. In Proceedings of the APEC. Seventeenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No.02CH37335), Dallas, TX, USA, 10–14 March 2002; pp. 1127–1132. [Google Scholar] [CrossRef]

- Zhu, J.; Zhang, Y.; Sun, W.; Lu, Y.; Shi, L.; Gu, Y.; Zhang, S. Noise Immunity and its Temperature Characteristics Study of the Capacitive-Loaded Level Shift Circuit for High Voltage Gate Drive IC. IEEE Trans. Ind. Electron. 2018, 65, 3027–3034. [Google Scholar] [CrossRef]

- Yuan, B.; Ying, J.; Ng, W.T.; Lai, X.Q.; Zhang, L.F. A High-Voltage DC–DC Buck Converter With Dynamic Level Shifter for Bootstrapped High-Side Gate Driver and Diode Emulator. IEEE Trans. Power Electron. 2020, 35, 7295–7304. [Google Scholar] [CrossRef]

- Lutz, D.; Seidel, A.; Wicht, B. A 50V, 1.45ns, 4.1pJ High-Speed Low-Power Level Shifter for High-Voltage DCDC Converters. In Proceedings of the ESSCIRC 2018—IEEE 44th European Solid State Circuits Conference (ESSCIRC), Dresden, Germany, 3–6 September 2018; pp. 126–129. [Google Scholar] [CrossRef]

- Liu, Z.; Lee, H. A 100V gate driver with sub-nanosecond-delay capacitive-coupled level shifting and dynamic timing control for ZVS-based synchronous power converters. In Proceedings of the IEEE 2013 Custom Integrated Circuits Conference, San Jose, CA, USA, 22–25 September 2013; pp. 1–4. [Google Scholar] [CrossRef]

- Salimath, A.; Gonano, G.; Bonizzoni, E.; Brambilla, D.; Botti, E.; Maloberti, F. A high-speed level shifting technique and its application in high-voltage, synchronous DC-DC converters with quasi-ZVS. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Abdelmoaty, A.; Al-Shyoukh, M.; Fayed, A. A high-voltage level shifter with sub-nano-second propagation delay for switching power converters. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 2437–2440. [Google Scholar] [CrossRef]

- Lanuzza, M.; Corsonello, P.; Perri, S. Low-Power Level Shifter for Multi-Supply Voltage Designs. IEEE Trans. Circuits Syst. II Exp. Briefs 2012, 59, 922–926. [Google Scholar] [CrossRef]

- Kabirpour, S.; Jalali, M. A Low-Power and High-Speed Voltage Level Shifter Based on a Regulated Cross-Coupled Pull-Up Network. IEEE Trans. Circuits Syst. II Exp. Briefs 2019, 66, 909–913. [Google Scholar] [CrossRef]

- Le, V.L.; Kim, T.T.H. An Area and Energy Efficient Ultra-Low Voltage Level Shifter With Pass Transistor and Reduced-Swing Output Buffer in 65-nm CMOS. IEEE Trans. Circuits Syst. II Exp. Briefs 2018, 65, 607–611. [Google Scholar] [CrossRef]

- Kabirpour, S.; Jalali, M. A Power-Delay and Area Efficient Voltage Level Shifter Based on a Reflected-Output Wilson Current Mirror Level Shifter. IEEE Trans. Circuits Syst. II Exp. Briefs 2020, 67, 250–254. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).