Development of 3D Wafer Level Hermetic Packaging with Through Glass Vias (TGVs) and Transient Liquid Phase Bonding Technology for RF Filter

Abstract

:1. Introduction

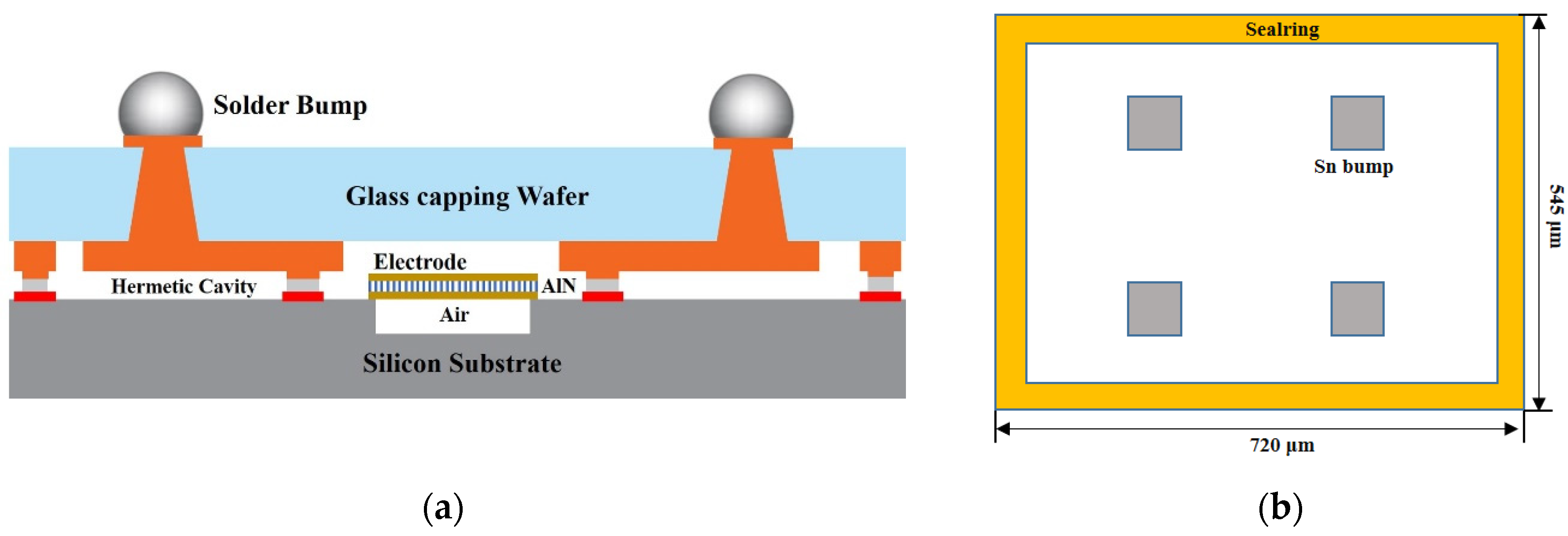

2. RF Filter the Package Design

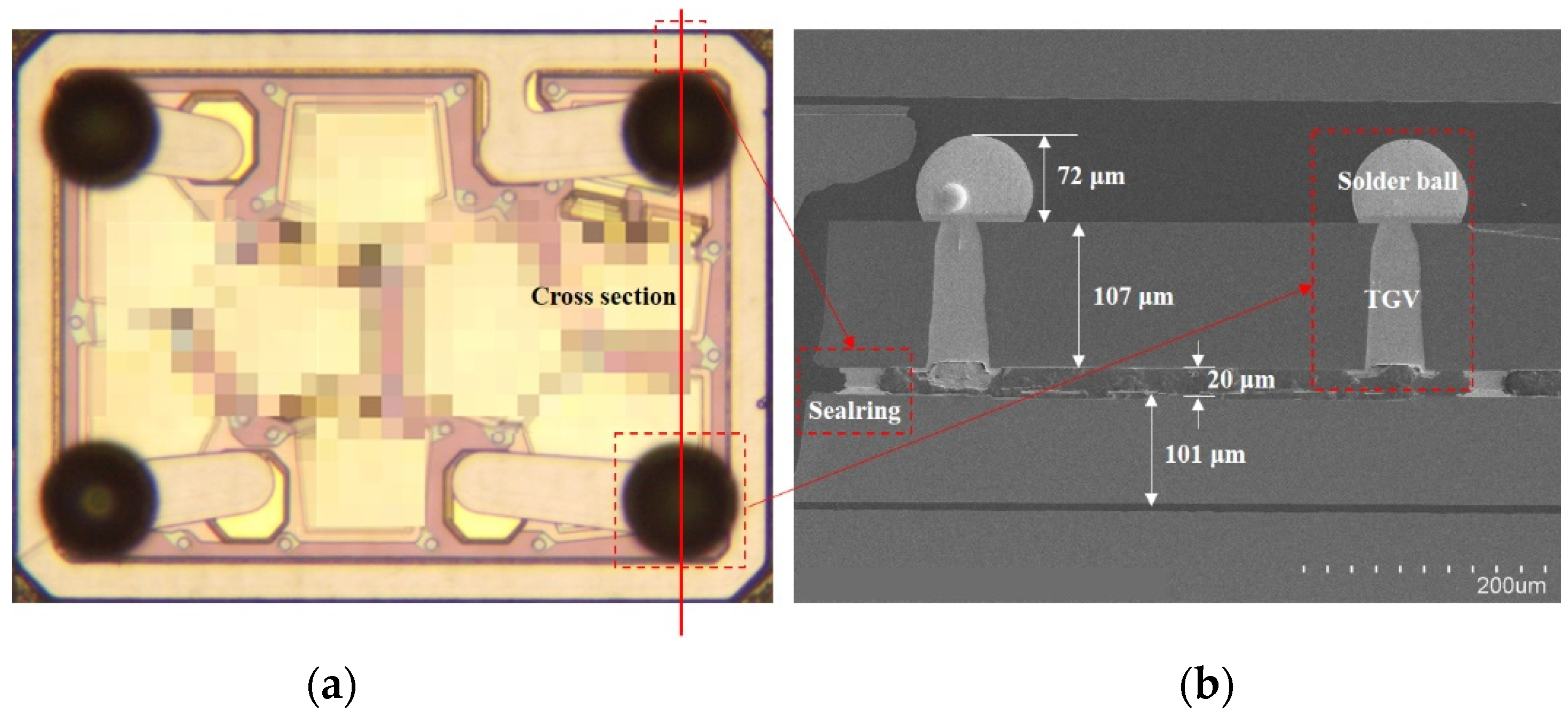

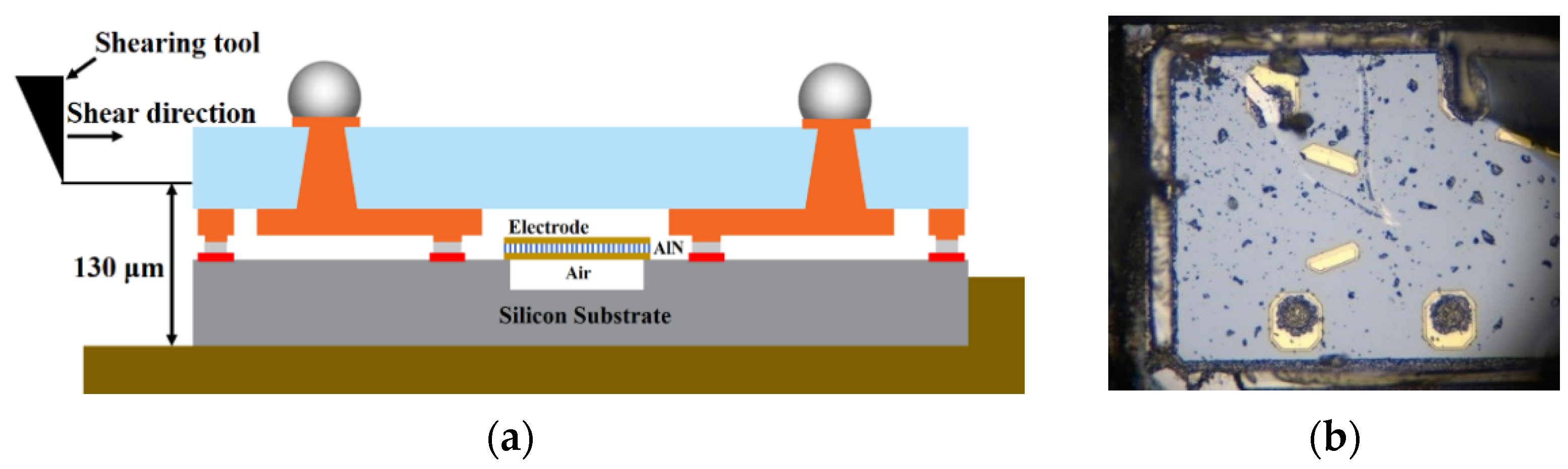

2.1. 3D WLP Structure for RF Filter

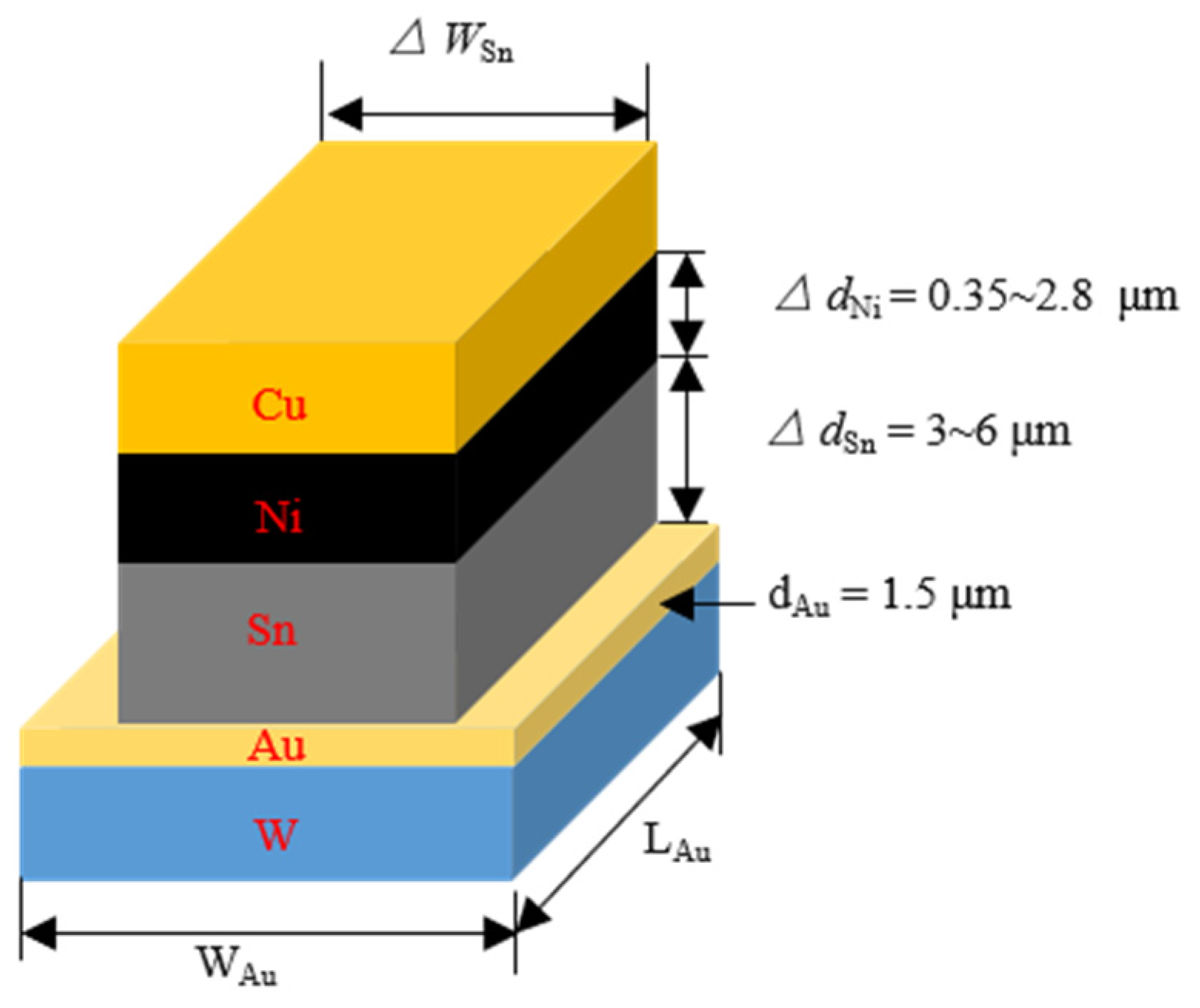

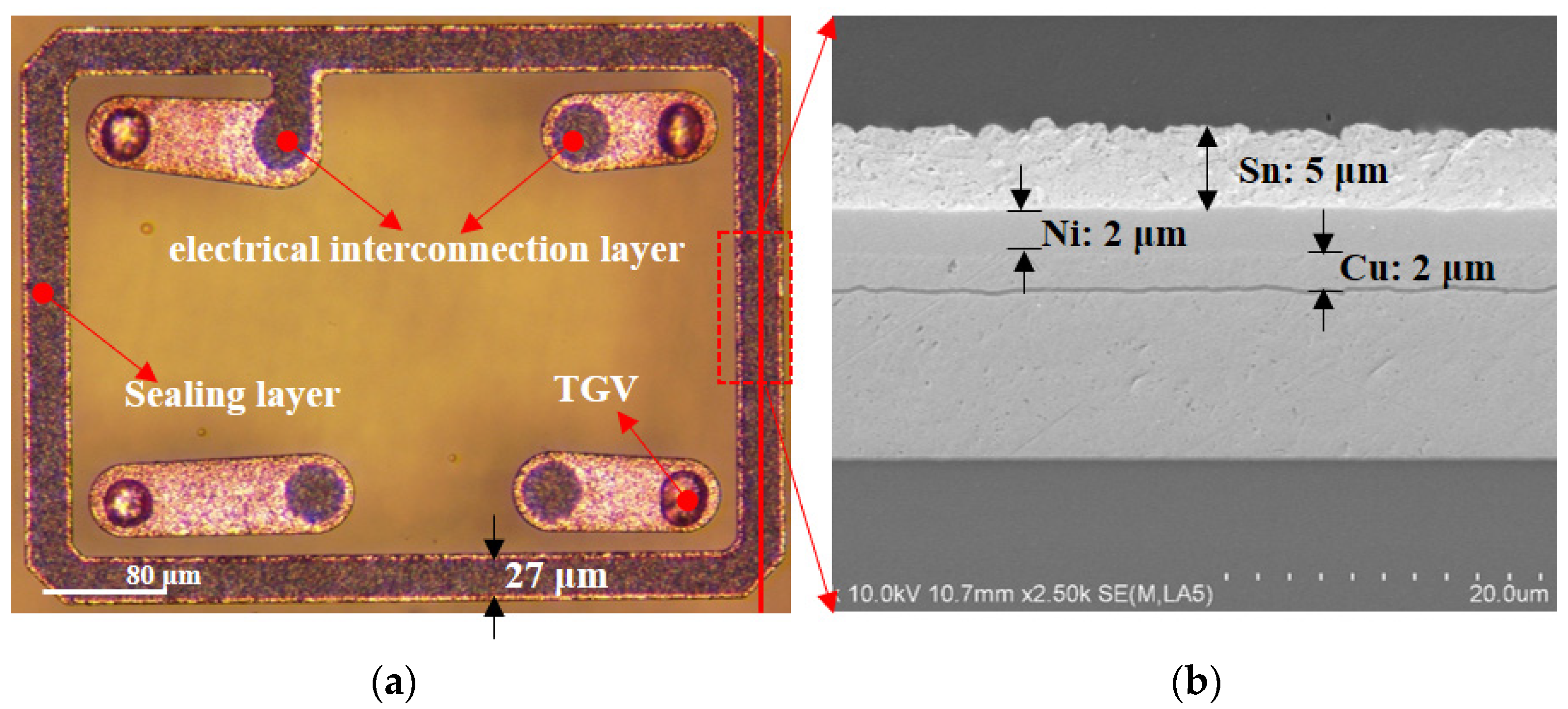

2.2. Optimization of the Bonding Structure and Bonding Parameters

2.2.1. Optimization of the Thickness of the Sn and Ni Layer

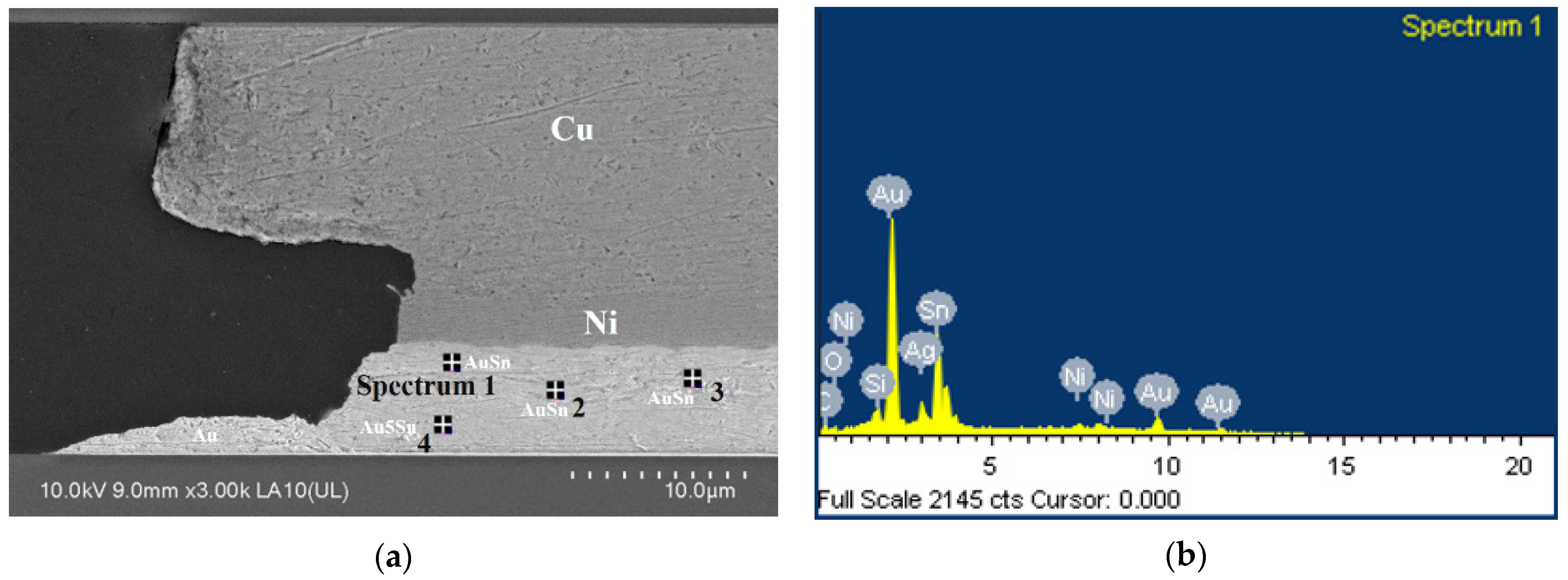

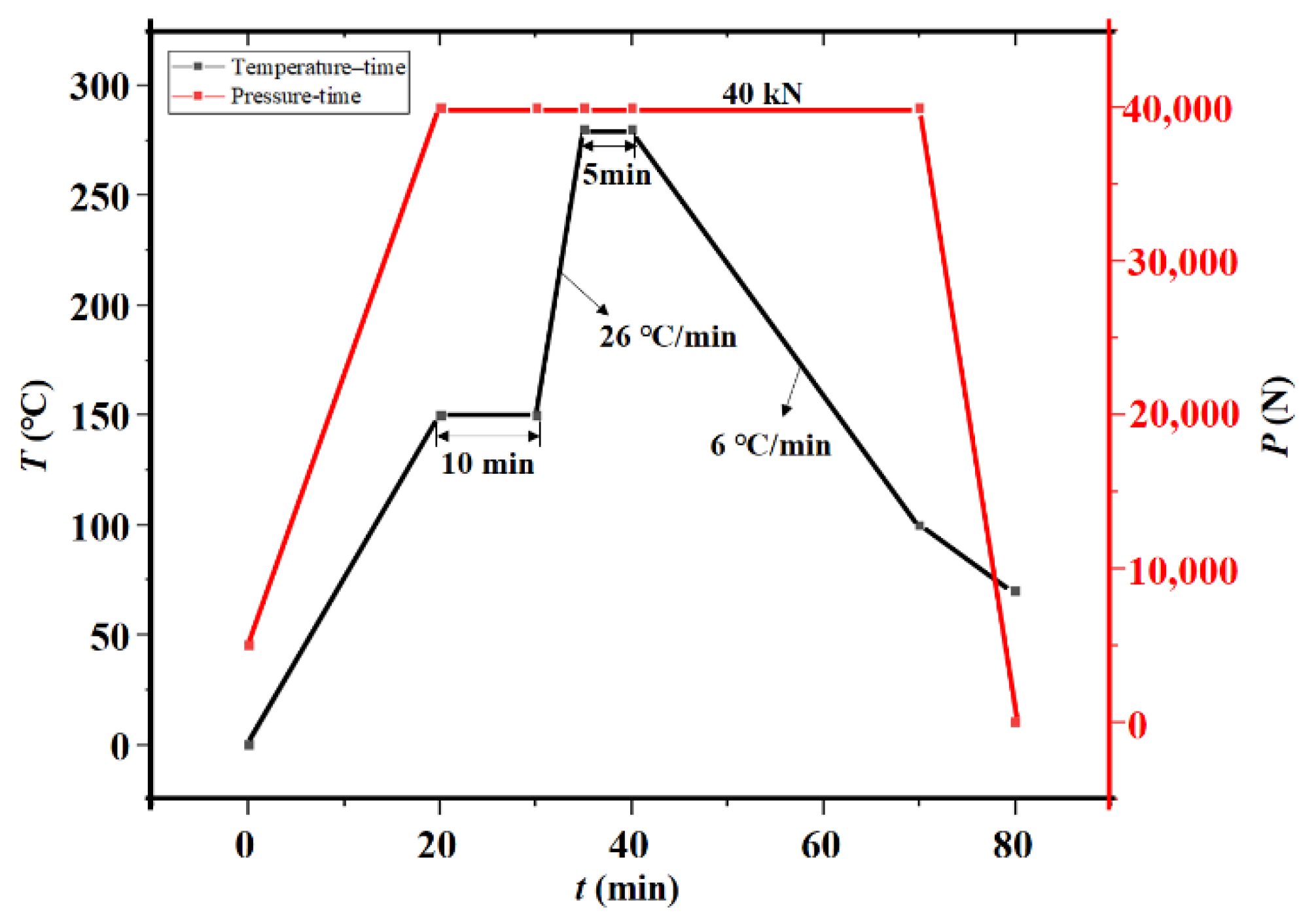

2.2.2. Experimental Examination of TLP Bonding

3. Packaging Process

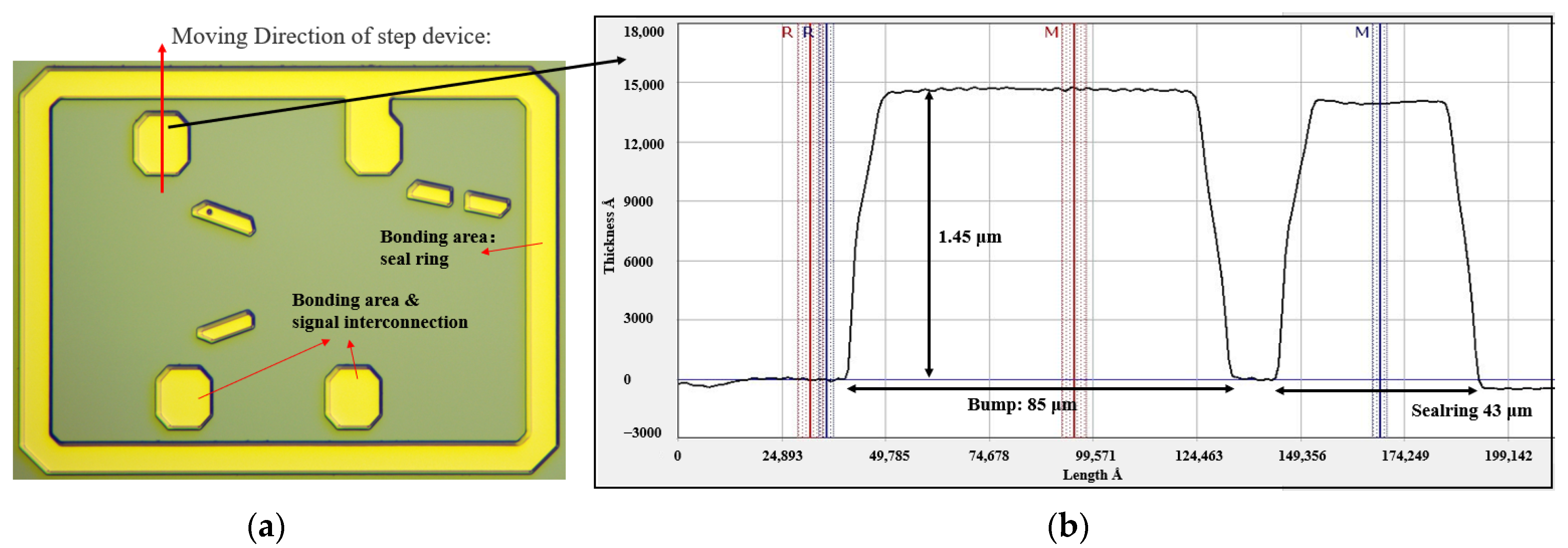

3.1. Dummy Device Wafer Fabrication Process

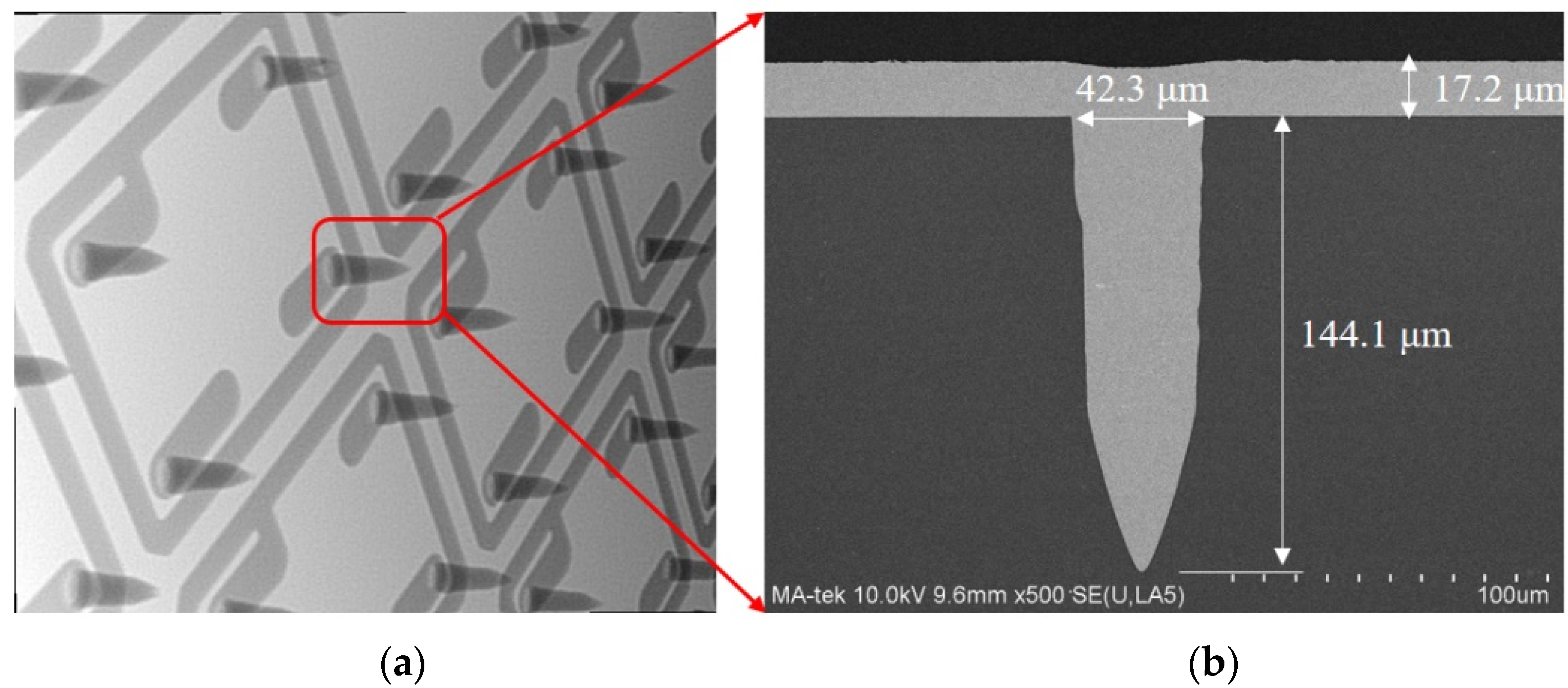

3.2. Glass Cap Wafer Fabrication Process

- Step 1. SiO2 layer by PECVD.

- Step 2. Apply photoresist and mask, then use photolithography techniques to open vias on the SiO2;

- Step 3. RIE of SiO2;

- Step 4. Strip off the photoresist.

3.3. Bonding Procedure

4. Reliability Test

4.1. Shear Strength Test

4.2. Deflection Assessment

4.3. Reliability Assessment Results

5. Conclusions

- (1)

- The glass interposer capping wafer is fabricated by LIDE, Cu plated blind TGVs, and RDL process to provide protection and electrical access to the RF filter. Following, the prepared glass capping wafer is bonded to the RF device wafer by Au-Sn TLP bonding. Shear strength’s of approx. 54.5 MPa can be determined, which is higher than the standard requirement (MIL-STD-883: method No. 2019.5 Die shear strength).

- (2)

- The glass interposer capping wafer is fabricated by LIDE, making improving process efficiency compared to the FBAR device package using silicon lid bonding technology. In addition, the glass is transparent, we can track the packaging yield in real-time during processing.

- (3)

- Through comparing the electrical performance after standard reliability tests, there is no difference in insertion attenuation across the passband (<0.2 dB). It is proved that the RF filter WLP with TGVs connection and cavity hermetic is a very promising solution due to its high robustness.

6. Patents

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Hagelauer, A.; Fattinger, G.; Ruppel, C.C.W.; Ueda, M.; Hashimoto, K.-Y.; Tag, A. Microwave Acoustic Wave Devices: Recent Advances on Architectures, Modeling, Materials, and Packaging. IEEE Trans. Microw. Theory Tech. 2018, 66, 4548–4562. [Google Scholar] [CrossRef]

- Boldeiu, G.; Ponchak, G.E.; Nicoloiu, A.; Nastase, C.; Zdru, I.; Dinescu, A.; Muller, A. Investigation of Temperature Sensing Capabilities of GaN/SiC and GaN/Sapphire Surface Acoustic Wave Devices. IEEE Access 2021, 10, 741–752. [Google Scholar] [CrossRef]

- Kang, Y.-R.; Kang, S.-C.; Paek, K.-K.; Kim, Y.-K.; Kim, S.-W.; Ju, B.-K. Air-gap type film bulk acoustic resonator using flexible thin substrate. Sens. Actuators A Phys. 2005, 117, 62–70. [Google Scholar] [CrossRef]

- Fattinger, G.; Aigner, R.; Stokes, P.; Volatier, A.; Dumont, F. Bulk acoustic wave technology advances. In Proceedings of the CS MANTECH Conference, New Orleans, LA, USA, 13–16 May 2013; pp. 315–318. [Google Scholar]

- Fattinger, G.; Stokes, P.; Potdar, V.; Volatier, A.; Dumont, F.; Aigner, R. Miniaturization of BAW devices and the impact of wafer level packaging technology. In Proceedings of the 2013 IEEE International Ultrasonics Symposium (IUS), Prague, Czech Republic, 21–25 July 2013; pp. 228–231. [Google Scholar]

- Gilbert, S.R.; Small, M.; Parker, R.; Callaghan, L.; Ortiz, S.; Bi, F.; Kekoa, L.; Tan, J.; Bin Alias, N.; Ong, G.; et al. Manufacturing and reliability of chipscale packaged FBAR oscillators. In Proceedings of the 2014 IEEE International Ultrasonics Symposium, Prague, Czech Republic, 21–25 July 2013; pp. 89–92. [Google Scholar]

- Small, M.; Ruby, R.; Ortiz, S.; Parker, R.; Zhang, F.; Shi, J.; Otis, B. Wafer-scale packaging for FBAR-based oscillators. In Proceedings of the 2011 Joint Conference of the IEEE International Frequency Control and the European Frequency and Time Forum (FCS) Proceedings, San Francisco, CA, USA, 2–5 May 2011; pp. 1–4. [Google Scholar]

- Lin, C.-H.; Lu, J.-M.; Fang, W. Encapsulation of film bulk acoustic resonator filters using a wafer-level microcap array. J. Micromech. Microeng. 2005, 15, 1433–1438. [Google Scholar] [CrossRef] [Green Version]

- Yu, A.; Premachandran, C.S.; Nagarajan, R.; Kyoung, C.W.; Trang, L.Q.; Kumar, R.; Lim, L.S.; Han, J.H.; Jie, Y.G.; Damaruganath, P. Design, process integration and characterization of wafer level vacuum packaging for MEMS resonator. In Proceedings of the 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 1669–1673. [Google Scholar]

- Wang, Z. 3-D Integration and Through-Silicon Vias in MEMS and Microsensors. J. Microelectromechanical Syst. 2015, 24, 1211–1244. [Google Scholar] [CrossRef]

- Tian, J.; Sosin, S.; Iannacci, J.; Gaddi, R.; Bartek, M. RF–MEMS wafer-level packaging using through-wafer interconnect. Sens. Actuators A Phys. 2008, 142, 442–451. [Google Scholar] [CrossRef]

- Hilton, A.; Temple, D.S. Wafer-level vacuum packaging of smart sensors. J. Sens. 2016, 16, 1819. [Google Scholar] [CrossRef]

- Torunbalci, M.M.; Alper, S.E.; Akin, T. A method for wafer level hermetic packaging of SOI-MEMS devices with embedded vertical feedthroughs using advanced MEMS process. J. Micromech. Microeng. 2015, 25, 125030. [Google Scholar] [CrossRef]

- Dragoi, V.; Cakmak, E.; Pabo, E. Metal wafer bonding for MEMS devices. Rom. J. Inf. Sci. Technol. 2010, 13, 65–72. [Google Scholar]

- Welch, W.C.; Najafi, K. Gold-indium Transient Liquid Phase (TLP) wafer bonding for MEMS vacuum packaging. In Proceedings of the 2008 IEEE 21st International Conference on Micro Electro Mechanical Systems, Tucson, AZ, USA, 13–17 January 2008; pp. 806–809. [Google Scholar]

- Flötgen, C.; A Pawlak, M.; Pabo, E.; Van De Wiel, H.J.; Hayes, G.R.; Dragoi, V. Cu-Sn transient liquid phase wafer bonding for MEMS applications. In Proceedings of the Smart Sensors, Actuators, and MEMS VI. International Society for Optics and Photonic, Grenoble, France, 24–26 April 2013; Volume 8763, p. 87630A. [Google Scholar]

- Yu, D.-Q.; Yan, L.L.; Lee, C.; Choi, W.K.; Thew, S.; Foo, C.K.; Lau, J.H. Wafer-Level Hermetic Bonding Using Sn/In and Cu/Ti/Au Metallization. IEEE Trans. Compon. Packag. Technol. 2009, 32, 926–934. [Google Scholar] [CrossRef] [Green Version]

- Yu, D.-Q.; Lee, C.; Yan, L.L.; Thew, M.L.; Lau, J.H. Characterization and reliability study of low temperature hermetic wafer level bonding using In/Sn interlayer and Cu/Ni/Au metallization. J. Alloy. Compd. 2009, 485, 444–450. [Google Scholar] [CrossRef]

- Chen, B.; Sekhar, V.N.; Jin, C.; Lim, Y.Y.; Toh, J.S.; Fernando, S.; Sharma, J. Low-Loss Broadband Package Platform with Surface Passivation and TSV for Wafer-Level Packaging of RF-MEMS Devices. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 1443–1452. [Google Scholar] [CrossRef]

- Xu, D.; Jing, E.; Xiong, B.; Wang, Y. Wafer-Level Vacuum Packaging of Micromachined Thermoelectric IR Sensors. IEEE Trans. Adv. Packag. 2010, 33, 904–911. [Google Scholar] [CrossRef]

- Tofteberg, H.R.; Schjølberg-Henriksen, K.; Fasting, E.J.; Moen, A.S.; Taklo, M.M.; Poppe, E.U.; Simensen, C.J. Wafer-level Au–Au bonding in the 350–450 C temperature range. J. Micromech. Microeng. 2014, 24, 084002. [Google Scholar] [CrossRef] [Green Version]

- Al Farisi, M.S.; Hirano, H.; Frömel, J.; Tanaka, S. Wafer-level hermetic thermo-compression bonding using electroplated gold sealing frame planarized by fly-cutting. J. Micromech. Microeng. 2016, 27, 015029. [Google Scholar] [CrossRef]

- Yamamoto, S.I.; Higurashi, E.; Suga, T.; Sawada, R. Low-temperature hermetic packaging for microsystems using Au–Au sur-face-activated bonding at atmospheric pressure. J. Micromech. Microeng. 2012, 22, 055026. [Google Scholar] [CrossRef]

- Chen, Z.; Yu, D.; Zhang, M.; Jiang, F. Development and Reliability Study of 3-D Wafer Level Packaging for SAW Filter Using Thin Film Capping. IEEE Trans. Compon. Packag. Manuf. Technol. 2021, 11, 1047–1054. [Google Scholar] [CrossRef]

- Chen, Z.; Yu, D. A Packaging Method and Structure of Acoustic Surface Filter Based on Glass Capping Technology. CN Patent 202010973819.1, 12 February 2021. [Google Scholar]

- Topper, M.; Ndip, I.; Erxleben, R.; Brusberg, L.; Nissen, N.; Schroder, H.; Yamamoto, H.; Todt, G.; Reichl, H. 3-D Thin film interposer based on TGV (Through Glass Vias): An alternative to Si-interposer. In Proceedings of the 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 66–73. [Google Scholar]

- Yang, F.; Han, G.; Yang, J.; Zhang, M.; Ning, J.; Yang, F.; Si, C. Research on Wafer-Level MEMS Packaging with Through-Glass Vias. Micromachines 2018, 10, 15. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Lee, J.Y.; Lee, S.W. Wafer level packaging for RF MEMS devices using void free copper filled through glass via. In Proceedings of the 2013 IEEE 26th International Conference on Micro Electro Mechanical Systems (MEMS), Taipei, Taiwan, 20–24 January 2013; pp. 773–776. [Google Scholar]

- Shih, W.L.; Yang, T.L.; Chuang, H.Y.; Kuo, M.S.; Kao, C.R. Inhibition of Gold Embrittlement in Micro-joints for Three-Dimensional Integrated Circuits. J. Electron. Mater. 2014, 43, 4262–4265. [Google Scholar] [CrossRef]

- Alam, M.; Wu, B.; Chan, Y.; Rufer, L. Reliability of BGA Solder Joints on the Au/Ni/Cu Bond Pad-Effect of Thicknesses of Au and Ni Layer. IEEE Trans. Device Mater. Reliab. 2006, 6, 421–428. [Google Scholar] [CrossRef]

- Chen, L.; Yu, D. Investigation of low-cost through glass vias formation on borosilicate glass by picosecond laser-induced selective etching. J. Mater. Sci. Mater. Electron. 2021, 32, 16481–16493. [Google Scholar] [CrossRef]

- Peng, J.; Liu, H.S.; Ma, H.B.; Shi, X.M.; Wang, R.C. Microstructure evolution and mechanical reliability of Cu/Au–Sn/Cu joints during transient liquid phase bonding. J. Mater. Sci. 2018, 53, 9287–9296. [Google Scholar] [CrossRef]

- Tang, D.; Jin, Z.; Si, M.; Luo, X.; Xie, D.; Xie, X. Study on Cavity Collapse Resisting Molding Pressure in WLP of SAW Filter. J. Piezoelectrics Acoustooptics 2021, 43, 4. [Google Scholar]

- Chen, Z.; Yu, D.; Jiang, F. Development of 3-D Wafer Level Packaging for SAW Filters Using Thin Glass Capping Technology. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 375–381. [Google Scholar] [CrossRef]

- Szostak, K.M.; Keshavarz, M.; Constandinou, T.G. Hermetic chip-scale packaging using Au: Sn eutectic bonding for implantable devices. J. Micromech. Microeng. 2021, 31, 095003. [Google Scholar] [CrossRef]

| Element | Spectrum1 | Spectrum2 | Spectrum3 | Spectrum4 | ||||

|---|---|---|---|---|---|---|---|---|

| Weight% | Atomic% | Weight% | Atomic% | Weight% | Atomic% | Weight% | Atomic% | |

| Ni | 2.86 | 4.65 | Not detected | Not detected | 3.61 | 7.12 | Not detected | Not detected |

| Ag | 6.32 | 5.59 | 2.00 | 1.88 | Not detected | Not detected | Not detected | Not detected |

| Sn | 34.44 | 27.69 | 50.37 | 43.14 | 50.62 | 49.38 | 35.28 | 37.84 |

| Au | 50.37 | 24.40 | 42.90 | 22.14 | 43.27 | 25.44 | 62.67 | 40.51 |

| Items | Thickness | Young Modulus | Poisson Ratio | Critical Size |

|---|---|---|---|---|

| Thin glass capping layer | 100 μm | 64 GPa | 0.3 | 475 μm × 650 μm |

| Items | Conditions | Result | |

|---|---|---|---|

| Pre-Con L3 | Bake | 125 °C/24 H | Pass |

| Soak | 30 °C /60%/192 H | Pass | |

| Reflow | 260 °C (+5/−0) 3x | Pass | |

| uHAST | 130 °C/85% RH, 96 H | Pass | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, Z.; Yu, D.; Zhong, Y. Development of 3D Wafer Level Hermetic Packaging with Through Glass Vias (TGVs) and Transient Liquid Phase Bonding Technology for RF Filter. Sensors 2022, 22, 2114. https://doi.org/10.3390/s22062114

Chen Z, Yu D, Zhong Y. Development of 3D Wafer Level Hermetic Packaging with Through Glass Vias (TGVs) and Transient Liquid Phase Bonding Technology for RF Filter. Sensors. 2022; 22(6):2114. https://doi.org/10.3390/s22062114

Chicago/Turabian StyleChen, Zuohuan, Daquan Yu, and Yi Zhong. 2022. "Development of 3D Wafer Level Hermetic Packaging with Through Glass Vias (TGVs) and Transient Liquid Phase Bonding Technology for RF Filter" Sensors 22, no. 6: 2114. https://doi.org/10.3390/s22062114

APA StyleChen, Z., Yu, D., & Zhong, Y. (2022). Development of 3D Wafer Level Hermetic Packaging with Through Glass Vias (TGVs) and Transient Liquid Phase Bonding Technology for RF Filter. Sensors, 22(6), 2114. https://doi.org/10.3390/s22062114