Abstract

Testing is an important part of the design flow in the semiconductor industry. Unfortunately, it also consumes up to half of the production cost. On-silicon stimulus generators and response analyzers can be integrated with the Device-Under-Test (DUT) to reduce production costs with a minimum increment in power and area consumption. This practice is known as the Built-In Self-Test (BIST). This work presents a single-tone generator for BIST applications that is based on the Harmonic-Canceling (HC) technique. The main idea is to cancel or filter out the harmonics of a square-wave signal in order to obtain a highly pure sine wave. The design challenges of this technique are the precise implementation of irrational coefficients in silicon and the strong dependence of the output’s linearity on the coefficients’ precision. In order to reduce this dependence, this work introduces an irrational coefficient generator that is based on the recursive use of special matrices called skew-circulant matrices (SCMs). A complete study of the SCM-based HC synthesizer, its properties, and the proposed implementation in 180 nm CMOS technology are presented. The measured results show that the proposed HC synthesizer is able to filter out up to the 47th harmonic of a given square wave and to generate signals from to 100 MHz with a maximum Spurious-Free Dynamic Range (SFDR) of 66 dB.

1. Introduction

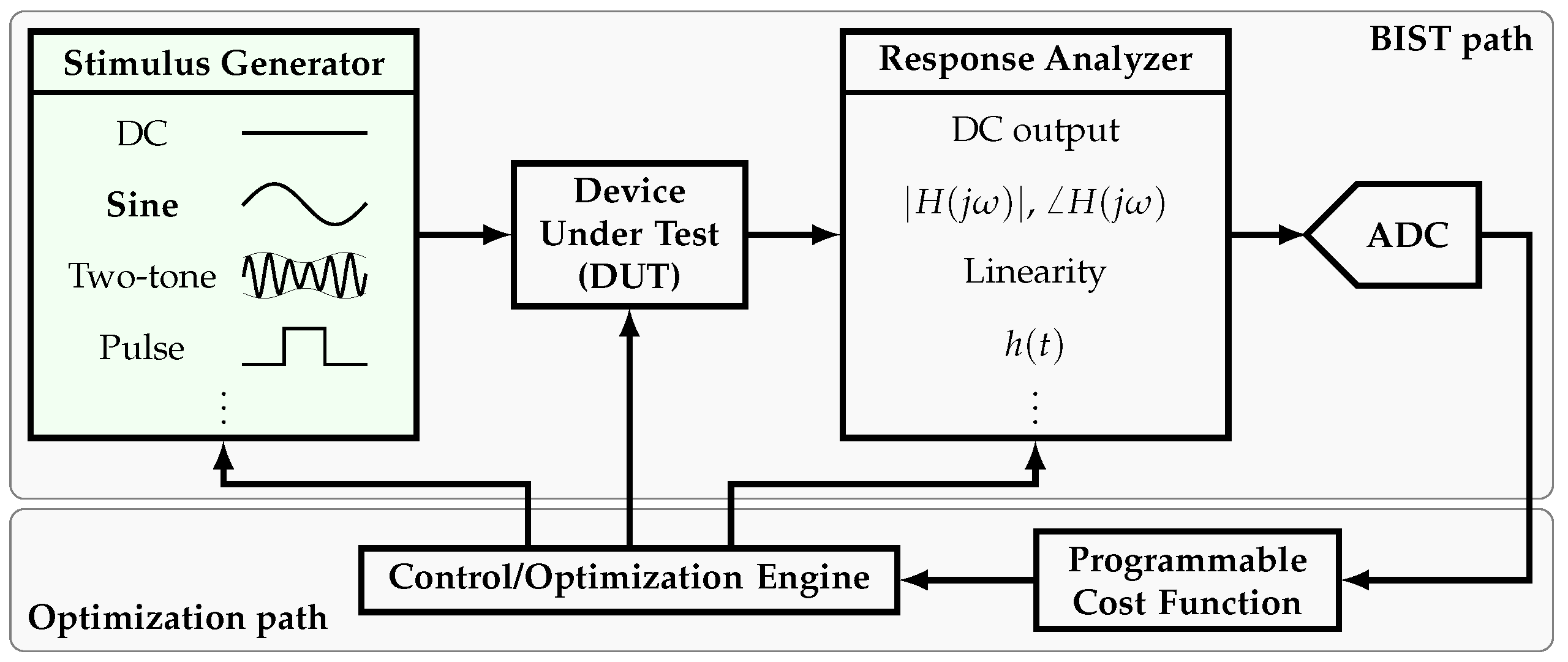

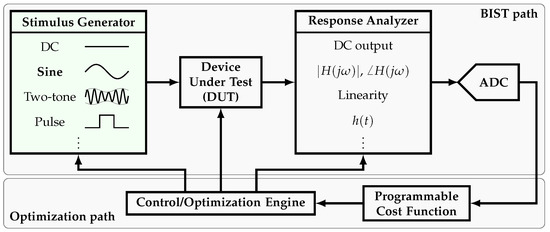

The semiconductor industry has evolved significantly since its creation in the 1950s. Nowadays, testing has proven to be a decisive stage of the production flow. However, testing can consume as much as 55% of the production cost [1]. Consequently, adding on-chip, self-testing capabilities to the Device-Under-Test (DUT), provided by signal generators and response analyzers, has become a practical solution known as the Built-In Self-Test (BIST) approach. In order to make this an efficient solution, the required circuitry must be small in area and consume low power relative to the DUT. A block diagram of a BIST system and the complementary optimization system is shown in Figure 1. The BIST system consists of the stimulus generator, the response analyzer, and an Analog-to-Digital converter (ADC). In order to characterize the DUT, several stimuli can be made available, such as sine wave (single-tone) generators [2,3,4,5,6,7,8,9,10,11,12,13,14,15], two-tone generators [16,17], etc. Complementarily, in order to study the DUT response, several on-chip analyzers have been proposed such as spectrum analyzers [18,19,20,21], linearity analyzers [22,23,24], etc. Based on the BIST path output, the optimization path is able to take a decision and feed back the corresponding tuning signals into the BIST path.

Figure 1.

Simplified block diagram of a BIST and optimization systems.

This work focuses on the stimulus generator block, specifically, in the single-tone generator. In addition, it is an expanded version of a previous work [2]. For BIST applications, besides the low-area and power requirements, this block’s output must present a high linearity. For instance, in order to characterize a 10-bit ADC, a sinewave with Total Harmonic Distortion (THD) lower than dB is required, which is challenging to obtain with a fully integrated system. Furthermore, technology scaling increases the design complexity due to the addition of nonlinearities and reduced voltage headroom.

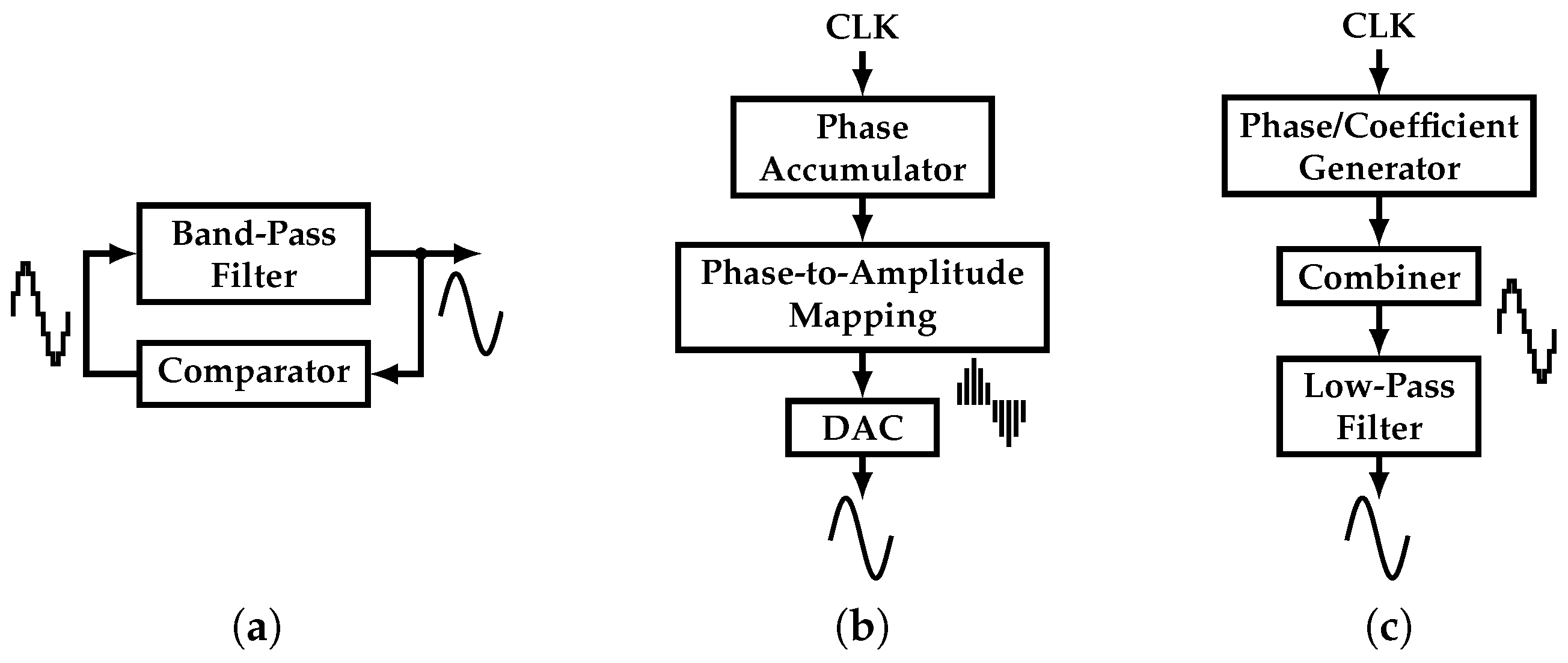

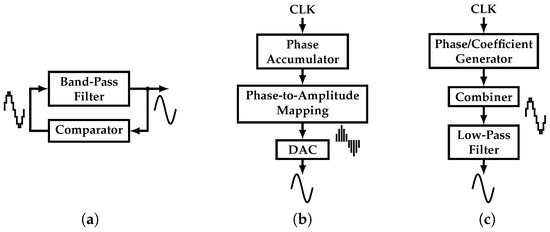

Different approaches to tackle this challenge have been proposed. As presented in [3,4], a low-distortion, single-tone signal can be synthesized by a band-pass filter (BPF) in positive feedback with a multi-level comparator block, as shown in Figure 2a. Unfortunately, the output’s THD is directly proportional to the quality factor of the BPF and complexity of the comparator. This translates into a power hungry, large area filter. In addition, the BPF suffers from a limited frequency tuning range. In addition, the multi-level comparator is sensitive to process variations, introducing more distortion sources.

Figure 2.

Different single-tone generators: (a) BPF-based oscillator, (b) DDFS, and (c) Harmonic-Canceling synthesizer.

In order to expand the frequency tuning range, the Direct Digital Frequency Synthesizer (DDFS) is proposed in [5,6,7,8,9]. It can produce a highly linear tone based on a clock signal, and it usually is divided into a phase accumulator, a phase-to-amplitude mapping (P2AM) block, and a DAC (Figure 2b). Its digital nature makes it robust to technology scaling. However, this approach suffers from a high power consumption due to the P2AM block, which is typically based on a Read-Only Memory (ROM).

On the other hand, Harmonic-Canceling (HC) synthesizers appear as a solution with superior power consumption and tuning range capabilities compared to the previous approaches [10,11,12,13,14,15,16]. It uses phase-shifted versions of a clock signal which are scaled by coefficients that belong to a half-period sine function, i.e., irrational coefficients. It presents a phase generator, a coefficient generator (CG), and a combiner, as shown in Figure 2c. Previous works have integrated the required irrational coefficients in silicon by using ratios of integer numbers [11,12,13,14,15,16]. The main drawback of this approach is the trade-off between output linearity and process-variation sensitive coefficient precision. This imposes the use of calibration techniques that add to the system’s complexity.

This work proposes a programmable, high-order HC synthesizer that presents an irrational coefficient generator that ideally produces high-precision coefficients with no calibration scheme. This coefficient generator exploits the properties of a special family of matrices called skew-circulant matrices (SCMs) in a recursive approach. Its programmability allows the user to select the position of the non-cancelable harmonics, which are intrinsic to any HC synthesizer, in order to meet different linearity requirements. On the other hand, its high order reduces the complexity of the required additional low-pass filter (LPF) [12,13,15].

The document is organized as follows. Section 2 presents the mathematical background and classification of the HC synthesizer. Section 3 shows the relationship between the HC synthesizer and the SCMs. In addition, it presents the proposed SCM-based HCF and its properties. Next, a detailed circuit implementation is shown in Section 4. Section 5, Section 6 and Section 7 show the measurement results of the fabricated synthesizer, discussion, and conclusions, respectively.

2. Harmonic-Canceling Filter

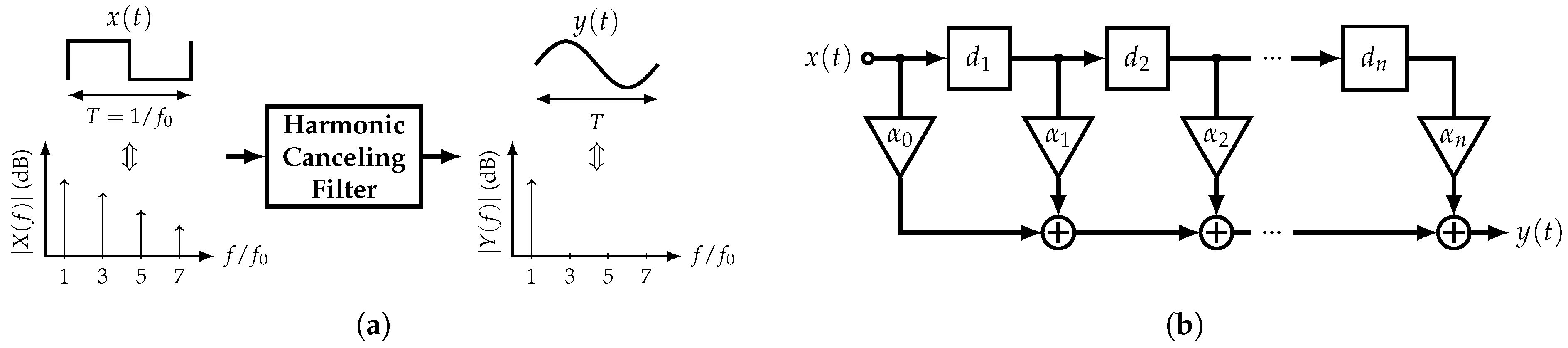

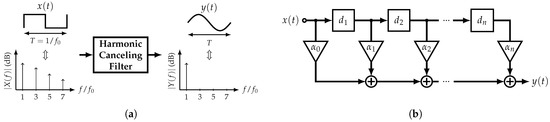

The main concept behind this type of filter is the rejection of the harmonics of a specific input signal in order to obtain a highly pure sine wave at its output; hence, they can be used as single-tone generators. Due to their frequency behavior, digital nature, and not very complex implementation, square waves (SWs) are considered as the filter’s input in this work. Figure 3a presents the operation of an ideal HCF when it is driven by a 50% duty cycle SW with fundamental angular frequency . The ideal output corresponds to a pure single-tone signal with period . Based on the Fourier series theory, any periodic signal can be expressed as

where and are the Fourier coefficients, and is the fundamental angular frequency of .

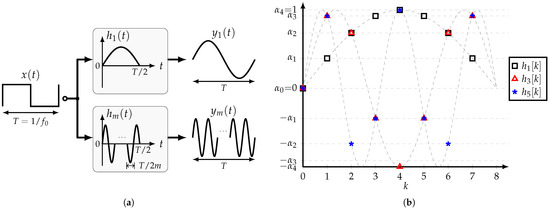

Figure 3.

Harmonic-Canceling Filter: (a) Main concept and (b) a generic block diagram.

If M periodic signals with weight , delay , and no DC component are considered, the Fourier series of the resultant signal is

where its Fourier coefficients are

The goal of an HCF is to eliminate and for . In order to achieve this, from (3) and (4), there are two available degrees of freedom: and . Depending on which one is fixed, there are two approaches to implement an HCF, which are the constant-amplitude HCF and the constant-delay HCF. Figure 3b shows a generic block diagram of an HCF which resembles a Finite Impulse Response (FIR) filter.

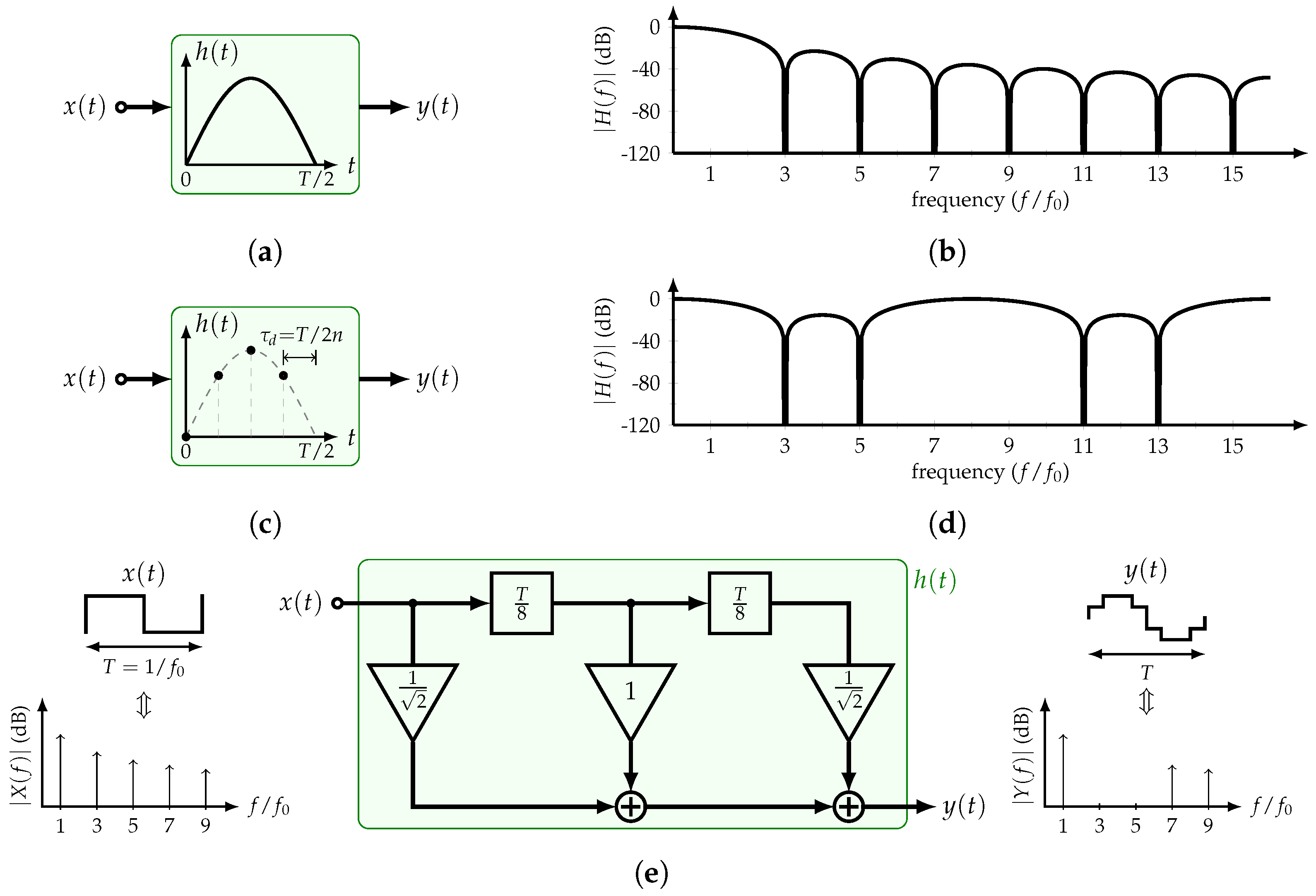

2.1. Constant-Amplitude HCF

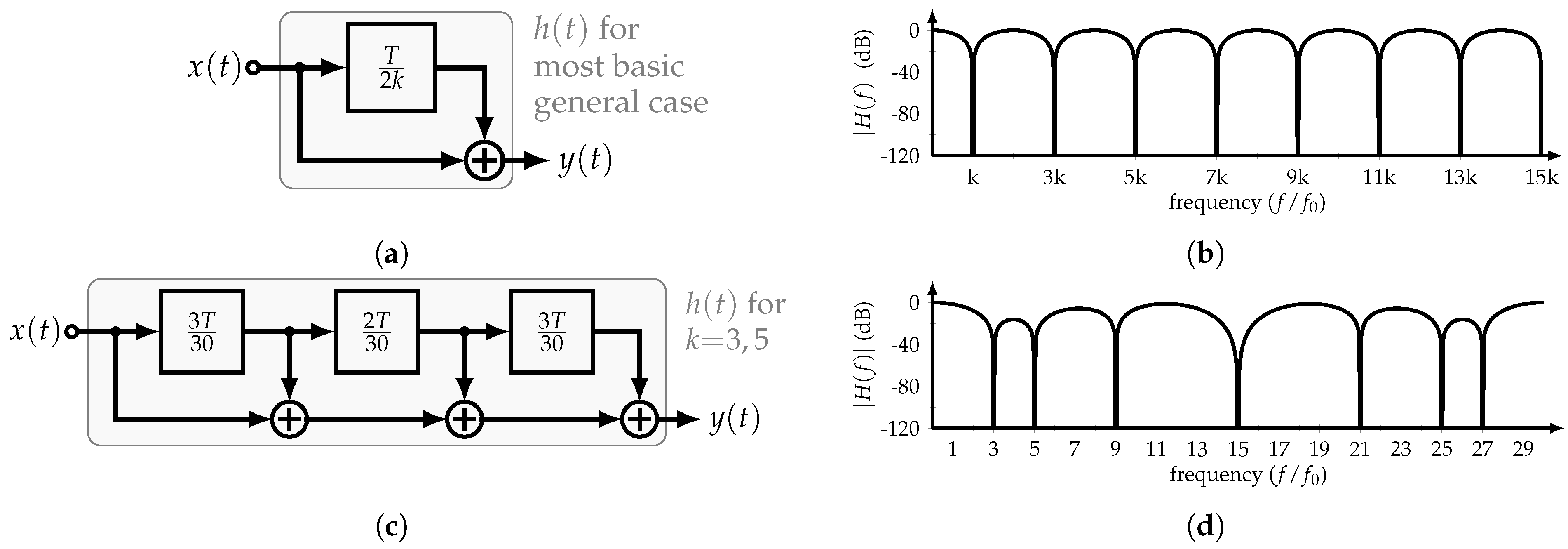

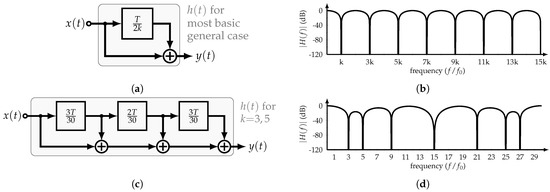

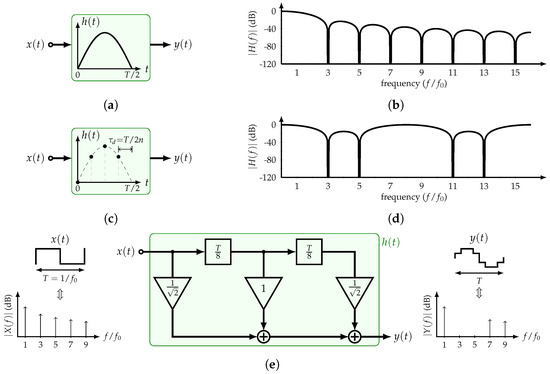

The basic implementation and transfer function of the constant-amplitude or time-mode HCF are shown in Figure 4a,b, respectively. Its transfer function is equal to

where f is the frequency in Hz. Interestingly, with only one delay element and a summer, the filter’s transfer function presents nulls at odd multiples of . Therefore, considering the input with period T, and setting , it is possible to cancel the odd multiples of the input’s k-th harmonic. Consequently, by adding several time delays in a specific manner, more harmonics can be canceled. For example, if the 3rd and 5th harmonics are to be suppressed, the corresponding HCF transfer function is

Figure 4.

Constant–amplitude HCF: (a) Block diagram and (b) transfer function of most basic implementation, and (c) block diagram and (d) transfer function of HCF with rejection of 3rd and 5th harmonic and their odd multiples.

Figure 4c,d show the block diagram and transfer function of this HCF, respectively. As expected, the odd multiples of the 3rd and 5th harmonics are canceled.

Unfortunately, the number of harmonics to be canceled is inversely proportional to the size of the required delay unit. For instance, a delay unit of is needed to suppress the odd multiples of the 3rd, 5th, and 9th harmonics. This trade-off turns the constant-amplitude HCFs into an impractical solution for high-speed applications. Nonetheless, some solutions have combined constant-amplitude HCFs with passive filters and optimization algorithms to tackle this problem [10].

2.2. Constant-Delay HCF

This type of filter is based on the concept of half-sine impulse response filters, which is shown in Figure 5a and was first proposed by [25]. Its transfer function is expressed as

and is plotted in Figure 5b. This filter is able to suppress all the odd harmonics of the fundamental frequency of the SW input with period T, providing a highly pure tone as its output.

Figure 5.

Constant–delay HCF: (a) Block diagram and (b) transfer function of the half-sine HCF; (c) block diagram, (d) transfer function, and (e) implementation of the 4-tap sampled half-sine HCF.

Recent publications have proposed practical implementations of this type of filters that used sampled versions of the half-sine impulse response [11,12,13,14,15,16]. If n samples of the impulse response are taken every , the filter is able to suppress all the input’s odd harmonics except those located at for . Every sample corresponds to a tap coefficient expressed as

This filter is also known as the n-tap HCF. Its transfer function is equal to

Figure 5c,d illustrate the sampled impulse response and the transfer function of the 4-tap HCF. It is clear that the transfer function is periodic with a period of . Furthermore, Figure 5e shows its block diagram, SW input, and staircase sine-wave output. Since , only three coefficients and two delay units are required. Note that an irrational coefficient is used, and the 7th and 9th harmonics are non-cancelable due to the sampling operation. If the non-cancelable harmonics are required to be pushed to higher frequencies, it is necessary to increase the number of taps. At this point, a simple passive filter can attenuate them.

As discussed in this section, the sampled half-sine or constant-delay HCFs present advantages with respect to the constant-amplitude HCFs. For comparison purposes, an HCF that suppresses the 3rd and 5th harmonics is considered. On the one hand, a constant-delay 4-tap HCF requires a time step of and two unique coefficients. On the other hand, a constant-amplitude HCF requires a time step of . It is clear that the former can achieve the same performance with a larger time delay. However, this comes with the challenge of implementing irrational coefficients. Considering BIST applications that use moderate to high frequency ranges in the order of MHz, this work focuses on the constant-delay HCFs. In the next section, a recursive approach to implement this filter is presented.

3. Proposed SCM-Based HCF

3.1. Matrix Representation of the HCF

From this point, a sampled half-sine HCF or constant-delay HCF is simply referred to as HCF. As presented in previous sections, an n-tap HCF requires n input SWs and n tap coefficients. Considering a 50% duty-cycle SW with period T, then the n-tap HCF needs n versions of with a delay of with respect to each other. These are referred to as the input phases and can be expressed as

Note that this set of SWs is periodic and odd symmetric. Hence, and .

On the other hand, the tap coefficients are given by (8). For an even n, it holds that , and . In other words, the HCF is a linear phase FIR filter; i.e., it provides a constant input-to-output group delay of . For this specific case, the HCF’s output can be defined as

Assuming that n outputs with a group delay ranging from 0 to are required, the system can be expressed in matrix form as

or in compact notation,

where , , and are the input phase vector, output phase vector, and the coefficients matrix, respectively. Interestingly, corresponds to a special matrix type called Skew-Circulant Matrix (SCM).

A SCM is a matrix that presents a right cyclic shift between each consecutive row and the sub-diagonal elements change of sign [26]. Consequently, it is completely defined by the elements of its first row as . Another feature of the SCMs is that their eigenvectors only depend on their order n and can be expressed as

where j is the unit imaginary number and T is the transpose operator. In addition, the eigenvalues of are

Considering the eigenvalues and eigenvectors of , its eigen decomposition is expressed as , where , and is the conjugate transpose of . Based on these properties, all SCMs of the same order n share the same eigenvectors; hence, the same matrix .

3.2. HCF with Multi-Stage Open-Loop SCM-Based Coefficient Generator

As shown in (13), an n-tap HCF can be represented by an SCM such that

where for . For this case, it is proven in Appendix A that the eigenvalues of are equal to

Consider the normalized, even-order n SCM , and its eigen decomposition

where is the Euclidean norm of . Furthermore, from (17), it follows that matrix .

For practical implementations, the main drawback of is that its elements potentially can be irrational numbers. In order to avoid this, matrix is defined such that

where , and is the sign function. In this fashion, is an integer-coefficient SCM. In Appendix B, it is proven that the eigenvalues of are given by

Its normalized version presents an eigen decomposition equal to

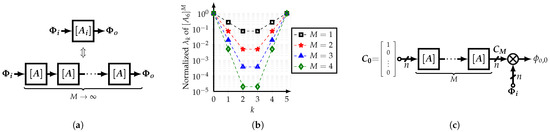

Interestingly, using (20), where 1. Based on this property, and recalling that all SCMs of the same order n share the same eigenvectors, if M replicas of are cascaded, then

where . Then

Therefore, a cascade of M normalized, even-order n, integer-coefficient SCMs can be used to approximate an irrational-coefficient SCM , as shown in Figure 6a. In addition, Figure 6b shows the eigenvalues of the resultant SCM for different values of M and . Note that the intermediate eigenvalues decrease as M increases. In other words, these intermediate eigenvalues can be considered as the error of the integer-coefficient SCM. It is important to note that the reason for using normalized matrices is that the outputs are bounded to the absolute magnitude of the input phases.

Figure 6.

(a) Implementation of ideal HCF based on cascade of non-ideal SCMs, and (b) normalized eigenvalues of M SCMs in cascade, and (c) improved implementation.

Since only one HCF’s output is required, the system architecture can be modified as shown in Figure 6c where the coefficients and phases generation processes are independent from each other. This improved approach allows that coefficients can be generated from a vector of DC signals and the phases present a faster path to the output, reducing potential phase errors. Nonetheless, this comes with the need for a combiner block.

Note that even if the challenge of using an irrational-coefficient-based SCM is met, it appears to be moved to the norm since now, it can be an irrational number. It can be proven that . However, since this value affects the complete matrix , it does not affect the coefficients’ relative ratio between each other; i.e., it can be considered as a gain error. In this work, the approximation is used.

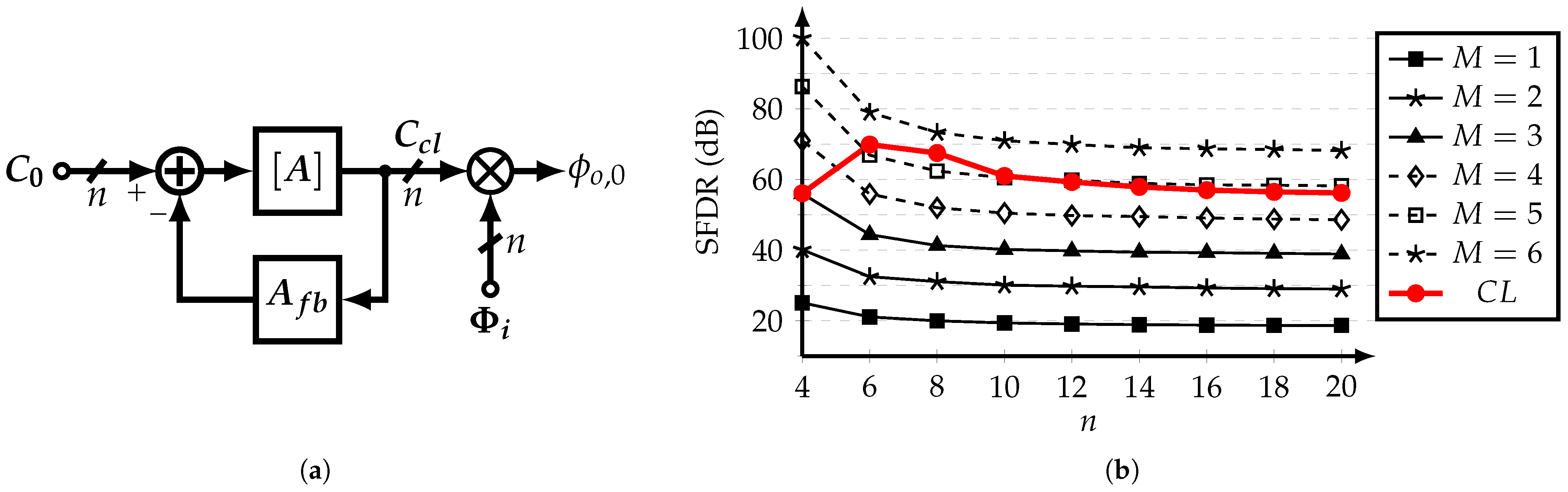

3.3. HCF with Single-Stage Closed-Loop SCM-Based Coefficient Generator

From (23), it is implied that if , the outputs of and the cascade of are similar. This suggests the concept of the closed-loop SCM-based coefficient generator, which is presented in Figure 7a. Using the improved approach and at steady-state, the output vector of the closed-loop coefficient generator is expressed as:

where , and . This is correct only if the ideal matrix norm is used. The use of the approximation affects the coefficients’ relative ratio between each other; hence, it generates a systematic error.

Figure 7.

(a) Block diagram of the closed-loop CG, and (b) THD versus CG’s order n, for different M-stages open-loop CGs and single-stage closed-loop CG, with .

In order to compare the performance of the multi-stage open-loop and single-stage closed-loop approaches, the spurious-free dynamic range (SFDR) of the filter’s output is evaluated using a system-level model. The SFDR is calculated as the ratio of the power of the fundamental frequency and the strongest cancelable harmonic up to the -th harmonic. Figure 7b shows the values of SFDR for different n-tap SCM-based HCFs using M open-stages and the closed-loop approach. It is observed that the closed-loop coefficient generator with is capable of achieving similar SFDR values as a 5-stage open-loop CG for . Thus, the closed-loop CG with a non-ideal norm represents a less complex solution in comparison with the straightforward M-stage open-loop CG approach.

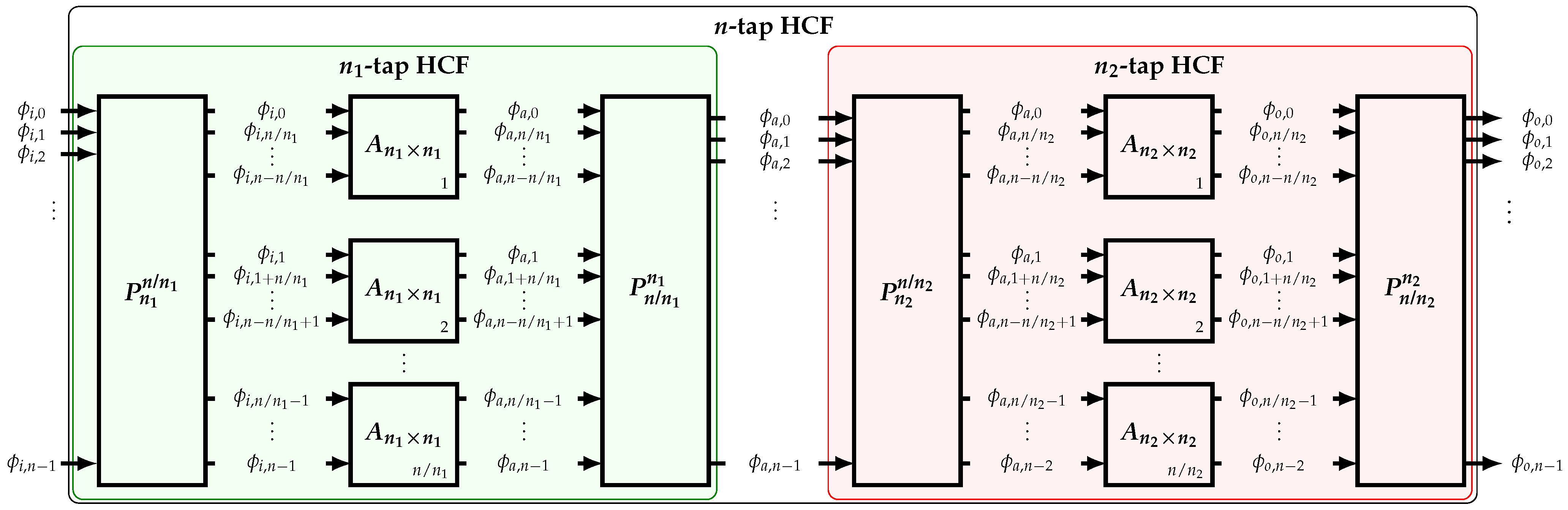

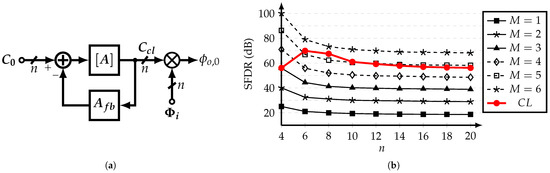

3.4. High-Order HCF

As introduced in [16], a high-order n-tap HCF can be implemented by cascading lower-order -tap and -tap HCFs (Figure 8). A formal proof is shown in this section.

Figure 8.

Implementation of a high-order HCF based on the cascade of two low-order HCFs.

In order to use both HCFs, n input phases equally spaced by are required such that , where is the least common multiple operator. For the first stage to properly operate, parallel -tap HCFs are needed. The phases are distributed based on a perfect shuffle permutation such that

where and is the identity matrix. The MATLAB colon notation to designate submatrices is used. At the output of the -tap HCFs, a perfect shuffle permutator is required to reorganize the output phases back to their original order. A similar process is done for the -tap HCF. For each stage, these operations can be expressed as

where ⊗ is the Kronecker product operator. For and , their Kronecker product is the matrix given by

Based on the properties of the Kronecker product, (26) can be simplified to:

As derived in Appendix C, matrix is simply a scaled version of if and only if , and it is equal to

where is the greatest common divisor operator. Hence, the cascade of the -tap and -tap HCFs is equivalent to an HCF of order if and only if and have a common factor; i.e., .

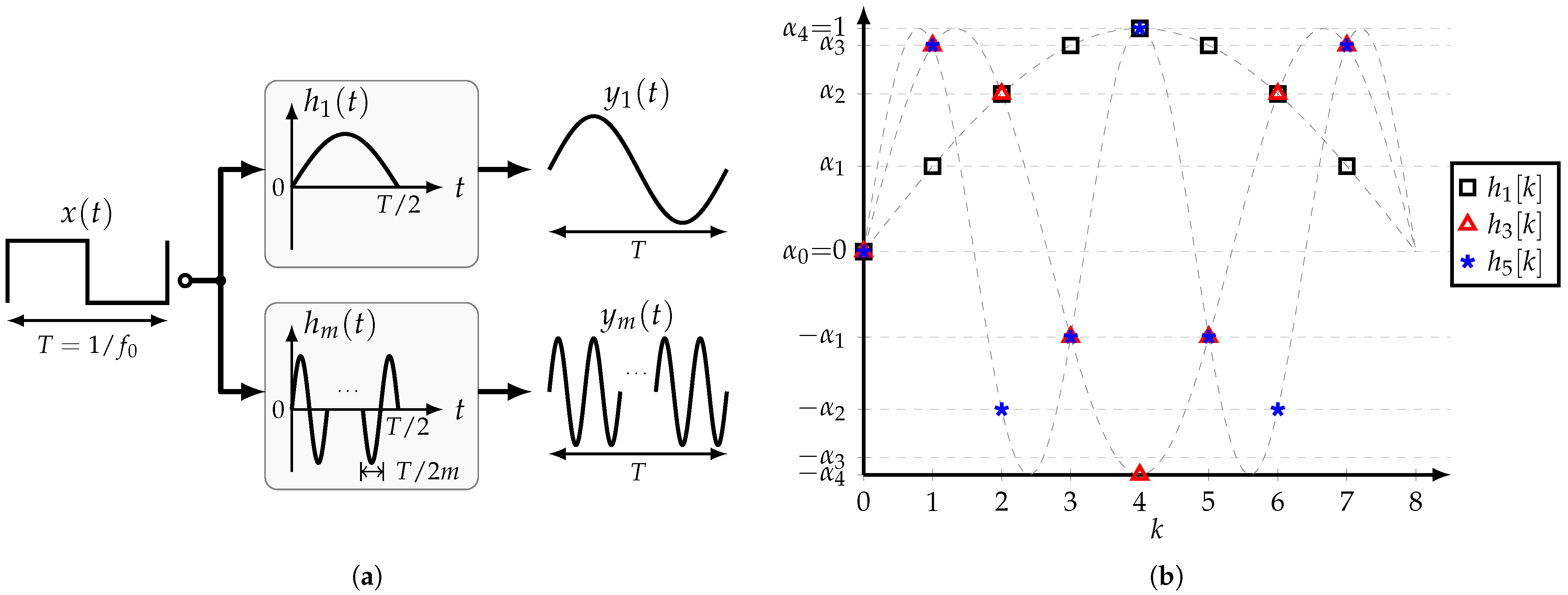

3.5. Band-Pass HCF

As shown in Section 2, the objective of the half-sine HCF is to filter out all the harmonics of the input SW except its fundamental frequency. Nonetheless, it is possible to select the input’s m-th harmonic, which gives place to the band-pass HCF. Its impulse response is given by

Figure 9a shows a comparison between the basic and band-pass HCFs. If the m-th harmonic is to be bypassed to the output, then the HCF’s impulse response presents m half-sine segments.

Figure 9.

(a) Comparison between impulse responses of the basic and band-pass HCFs, and (b) impulse response of several band-pass HCFs for .

For practical implementation, the impulse response is sampled at , where to satisfy the Nyquist sampling theorem. Thus, for a given n-tap HCF, several band-pass HCFs can be obtained. Moreover, the sampled values are all different if m and are relatively prime, i.e., their greatest common divisor is 1. Figure 9b shows several band-pass HCFs for . Note that is symmetric around , and that the coefficients are similar for all the filters except that they present different orders and signs. Hence, assuming that the tap coefficients are available, it is possible to implement different band-pass HCFs by rearranging the tap coefficients accordingly.

4. Circuit Implementation

4.1. System Architecture

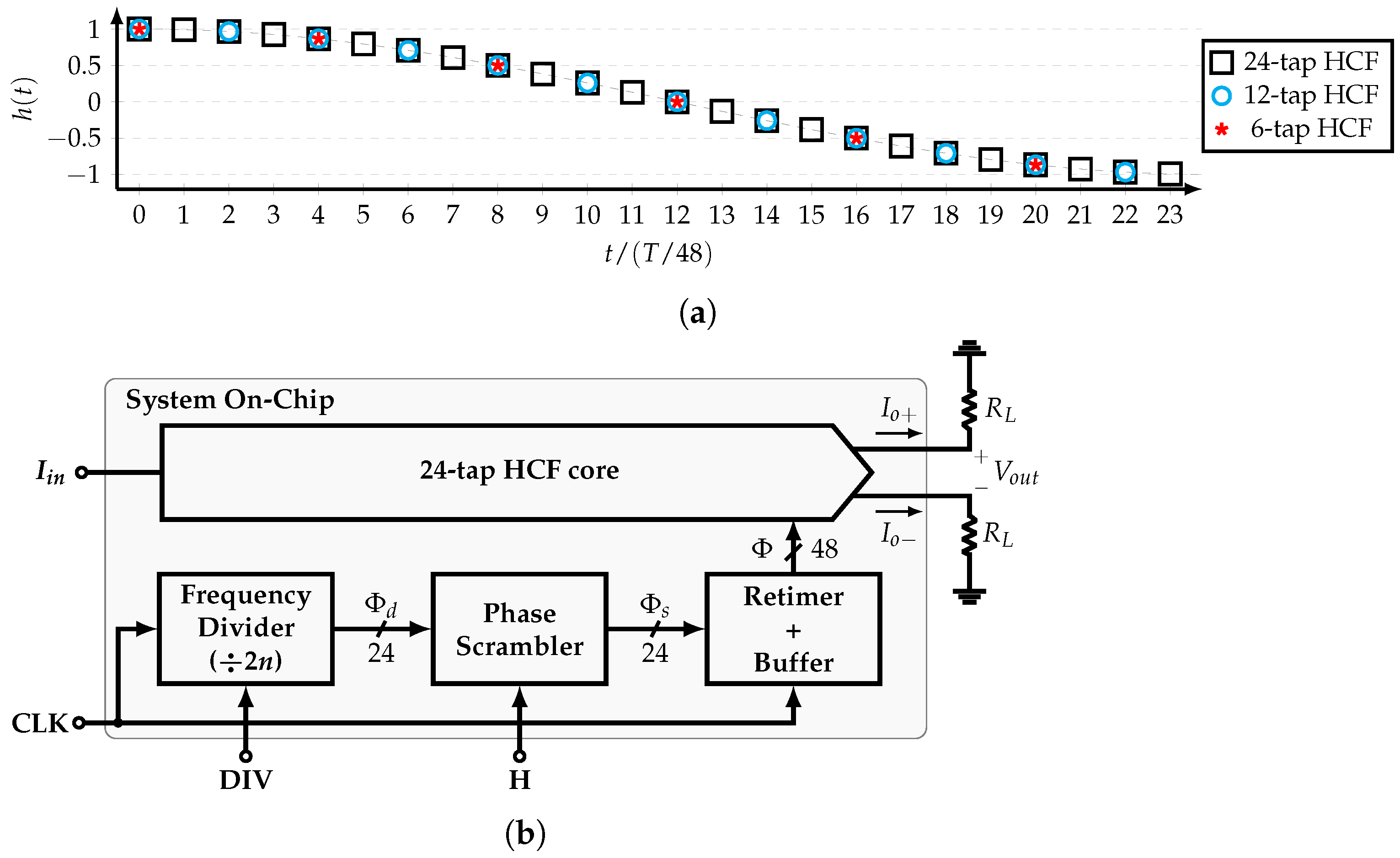

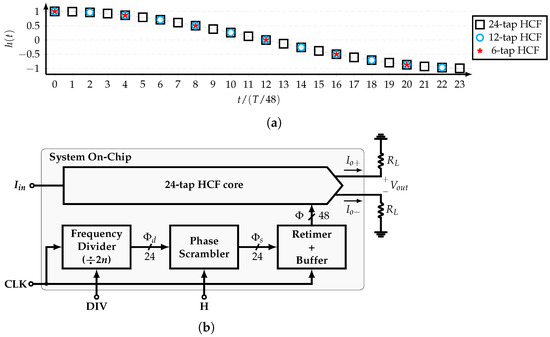

In this work, a reconfigurable, SCM-based, 24-tap HCF is implemented. This filter is able to cancel up to the 47th harmonic of the SW signal with frequency . In other words, this HCF is used as a single-tone generator that produces a stepwise sine-wave differential current signal with frequency . Figure 10a shows its impulse response , which corresponds to a cosine function . It is noted that the coefficients related to , and , correspond to the 12-tap, and 6-tap HCFs, respectively. Thus, by selecting specific phases, the 24-tap, 12-tap, and 6-tap HCFs are available. This feature allows to extend the maximum frequency of the output signal to .

Figure 10.

(a) Impulse response and (b) block diagram of system architecture.

Figure 10b shows the block diagram of the complete system, which is divided in four main blocks: the frequency divider, the phase scrambler, the retimer and buffer, and the 24-tap HCF core. The frequency divider generates the 24 equally-spaced phases from a clock signal with programmable frequency division ratios in order to select between the 24-tap, 12-tap, and 6-tap HCFs. The phase scrambler allows for the rearrangement of the phases such that it can bypass the fundamental or the 5th input’s harmonic to its output. The 24-tap HCF core is divided in the CG and combiner. In order to achieve the required SCM order, 8-tap and 5-tap SCM-based CGs are used in cascade. All the required coefficients are generated using only one input DC current . By means of a combiner, the system produces the differential output current , which is converted to voltage by the load resistors . Each block is presented in detail in the next subsections.

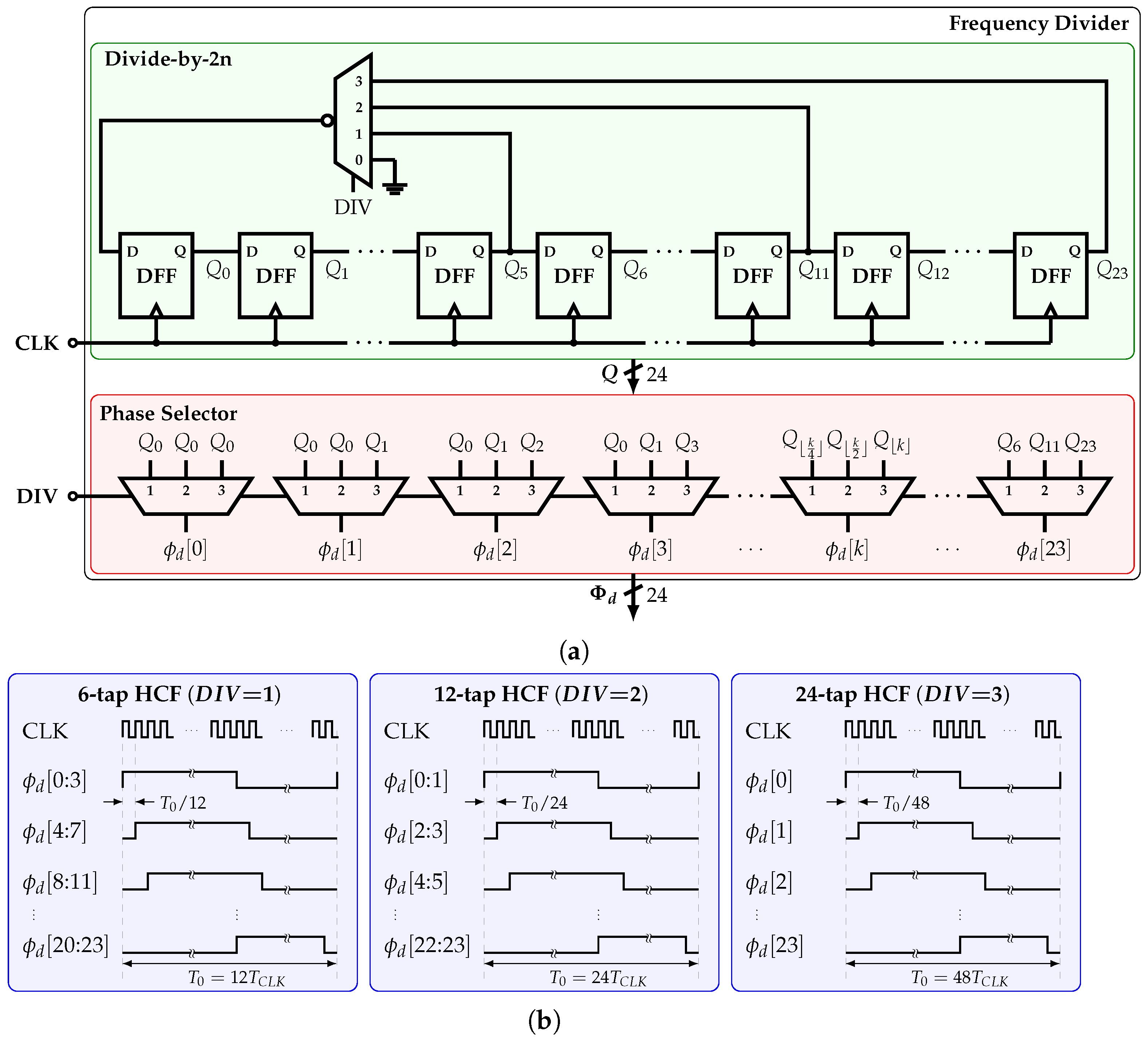

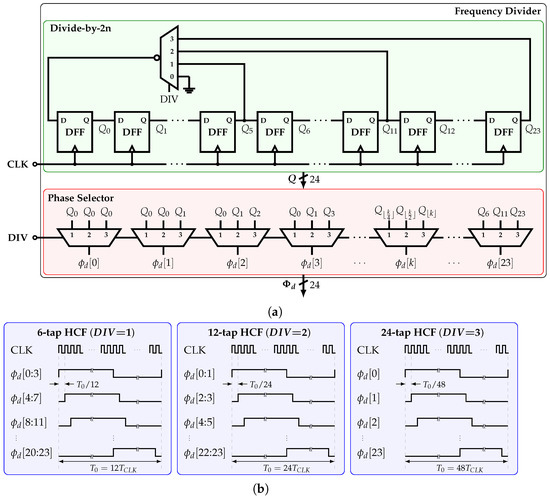

4.2. Frequency Divider

The frequency divider (FD) is shown in Figure 11a. The 24 equally spaced phases are generated from the input clock signal by a variable-length ring counter, which is based on a cascade of D flip-flops (DFFs). The outputs of this counter are , for . Depending on the value of the input , the outputs , , or are fed back to the input of the first DFF by an inverting feedback multiplexer, providing with a frequency division ratio of 12, 24, or 48, respectively.

Figure 11.

(a) Implementation and (b) output signals of the frequency divider.

The bus signal is connected to a phase selector with output . Depending on the value of , each signal is connected to , , or . Figure 11b shows the FD’s output phases pattern for each value of . For example, for , every two consecutive phases are connected; i.e., the corresponding coefficients are connected in parallel. In this fashion, the number of tap coefficients is kept constant for all available HCFs; hence, all the HCFs present the same output peak-to-peak amplitude.

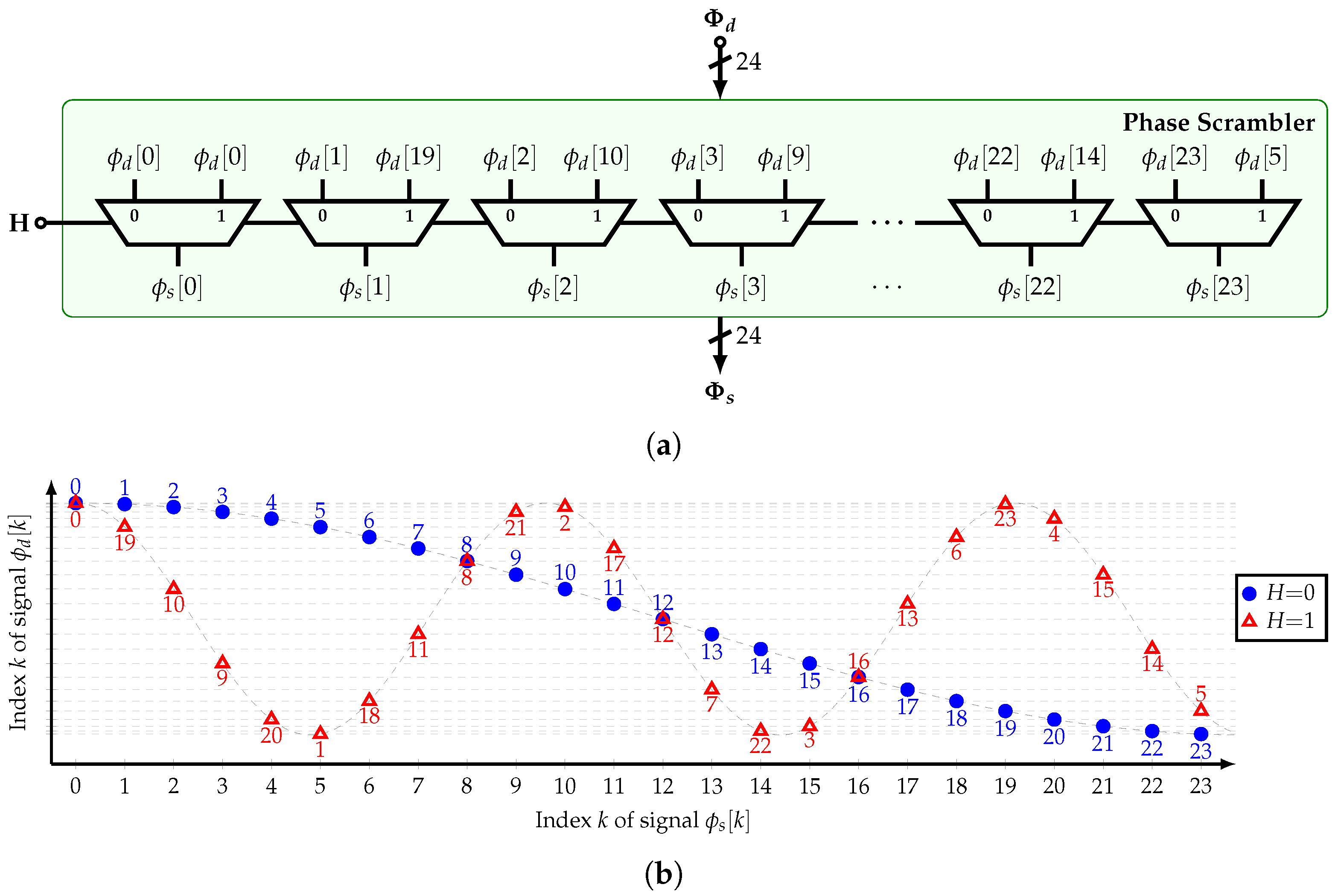

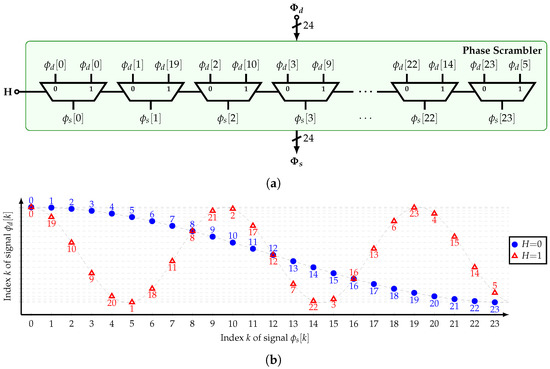

4.3. Phase Scrambler

As shown in Section 3.5, the proposed HCF can be configured to bypass an input signal’s harmonic different from the fundamental frequency by rearranging its coefficients or phases. The latter approach is chosen due to its lower implementation complexity based on digital multiplexers.

Figure 12a shows the implementation of the phase scrambler (PS). Depending on the value of , the fundamental frequency or the 5th harmonic of are bypassed to the filter’s output, respectively. Note that 5 is coprime with for the three available HCFs. Then, it is true that the tap coefficients of the bandpass HCF are similar to those of the low-pass HCF but with a different order and sign. Figure 12b presents the input-to-output connections.

Figure 12.

(a) Implementation and (b) input-to-output connections of the phase scrambler.

4.4. Retimer and Buffer

The required routing and operation of the phase selector and phase scrambler introduce phase errors. These are reduced by sampling the phase scrambler outputs at the rising edge of the input clock . This is done by an array of DFFs. Each of them provides an inverted version of each phase. The output of the retimer and buffer (R&B) is the bus , where each signal for . This work does not present any additional phase calibration scheme.

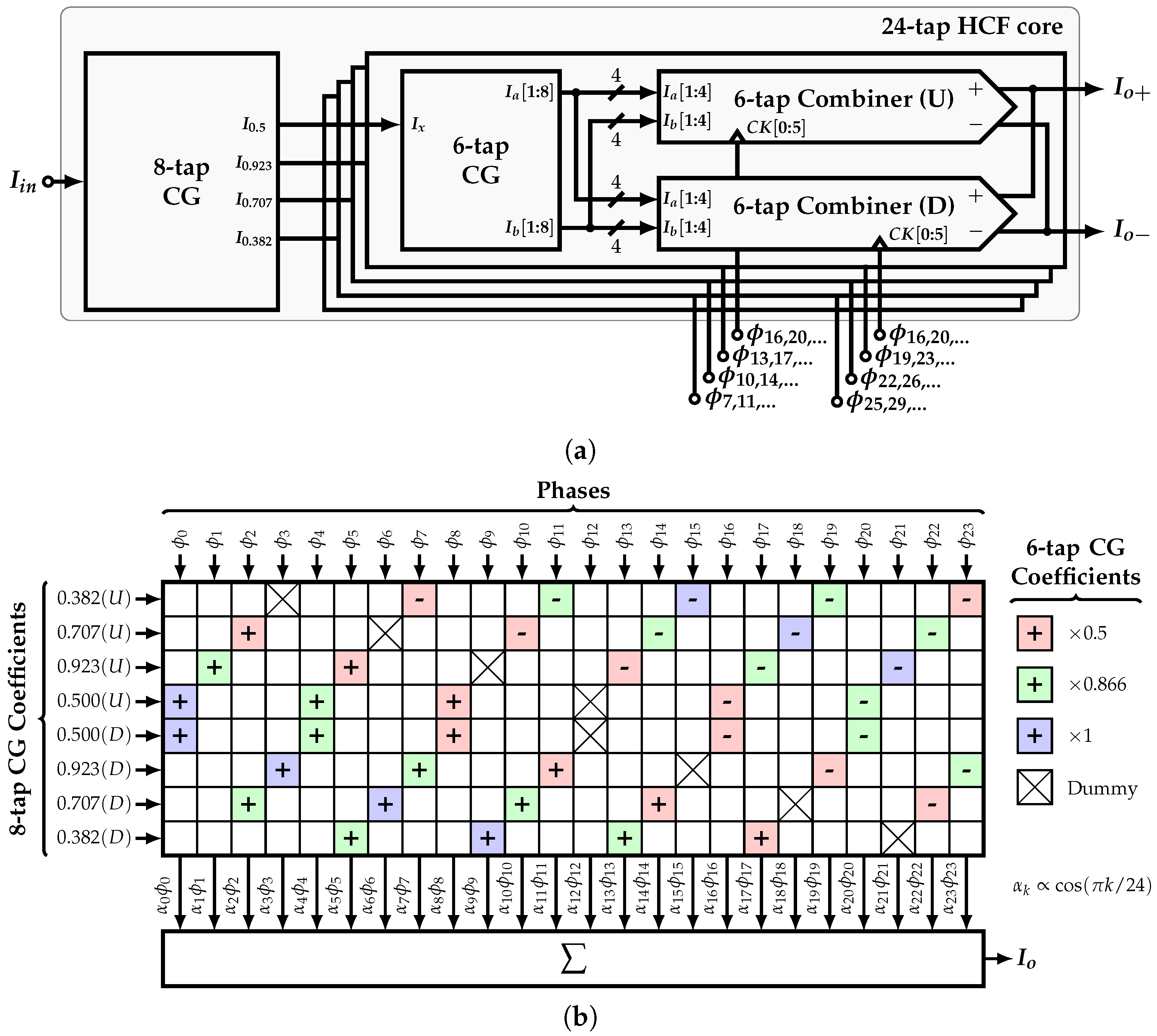

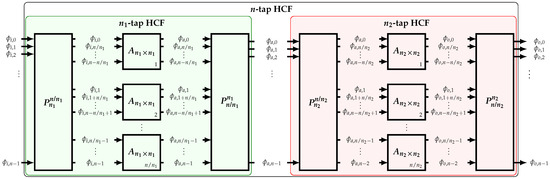

4.5. 24-Tap HCF Core

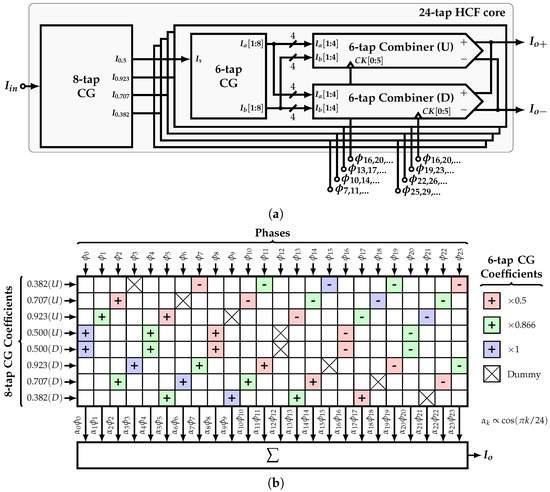

The required tap coefficients of the 24-tap HCF are generated by cascading the 8-tap and 6-tap CGs. Once these coefficients are available, they need to be combined with the phases accordingly in order to produce the system’s output. These operations are performed by the 24-tap HCF core.

The quarter-wave symmetry of the cosine function is used to reduce the implementation complexity of the CGs. In other words, by taking advantage of the SMC’s symmetry around , any given even-order SCM can be expressed as an SCM such that

This reduced matrix contains the information related to only one quadrant of the cosine function. Using this property, matrix can be reduced to

In addition, can be reduced even further, considering that it produces the coefficients and . Then

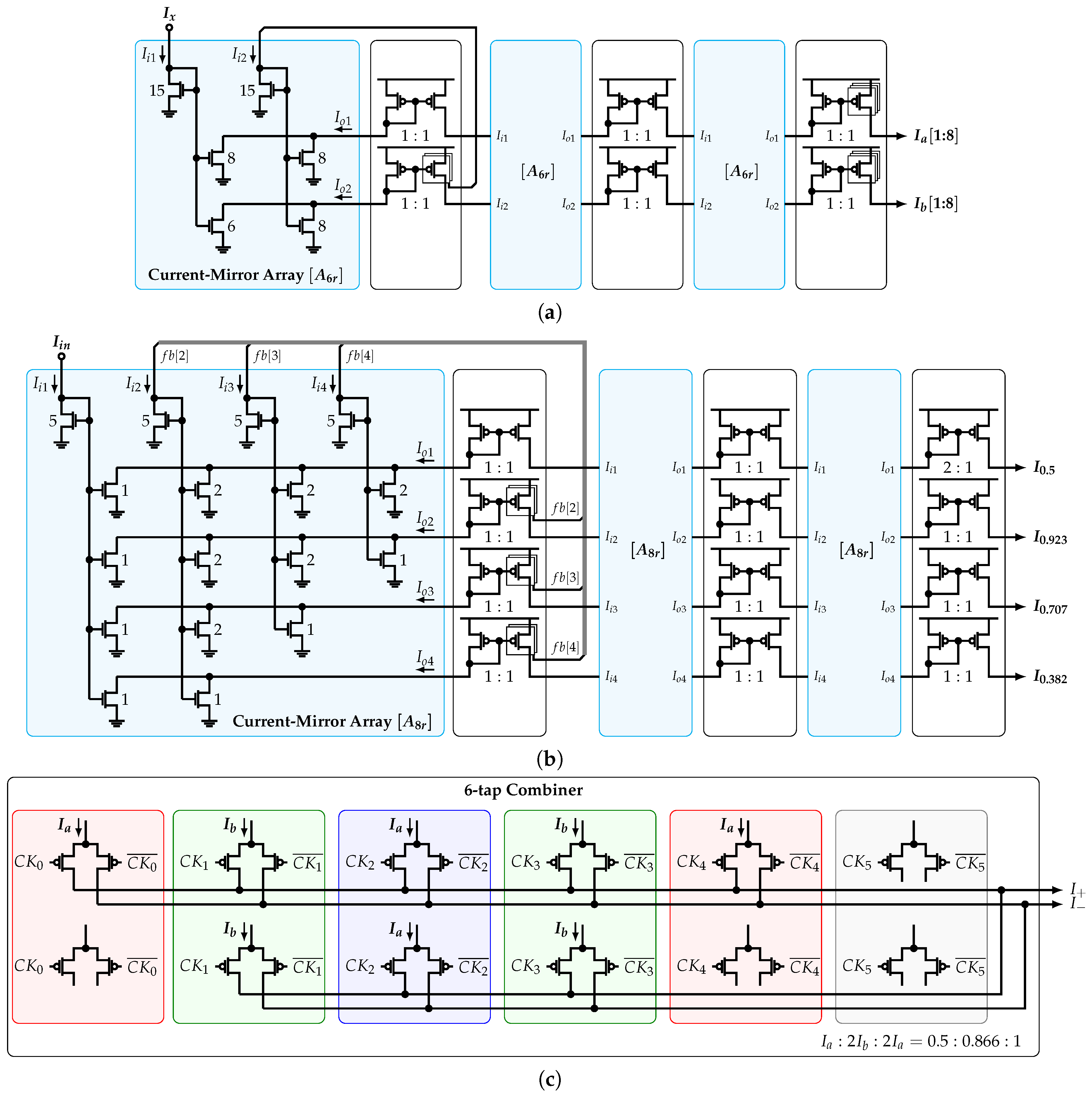

Figure 13a shows the 24-tap HCF core block diagram. Based on the improved implementation presented in Section 3.3, input vector is used; i.e., a single input current is required to generate all the current-mode coefficients. The 8-tap CG implements the reduced SCM . It produces four output currents whose relative ratios with respect to each other correspond to the coefficients , , , and . Each of these outputs is connected to four 6-tap CGs, which in turn implement the SCM and produce eight replicas of the currents and such that .

Figure 13.

(a) Block diagram of the 24-tap HCF core and (b) phase-to-coefficient distribution.

The connection between the phases and coefficients is shown in Figure 13b. The absolute value and sign of the coefficients related to the 6-tap CG are color-coded. Each of them are scaled in the shown order by the 8-tap CG coefficients associated with each row. Moreover, each row shows the order of the phases connected to each 6-tap combiner unit. It is important to mention that the time delay between two consecutive combiner subcells of each row is , that is, the unit delay of the 6-tap HCF, whereas the time delay between each row and the one below is , which is the unit delay of the 8-tap HCF. In this way, all the phases present the same load, which reduces the systematic phase mismatch that limits the filter’s performance. Next, the resultant coefficient corresponding to the sum of elements of the k-th column is multiplied by the corresponding phase. Finally, the output is equal to the sum of all products.

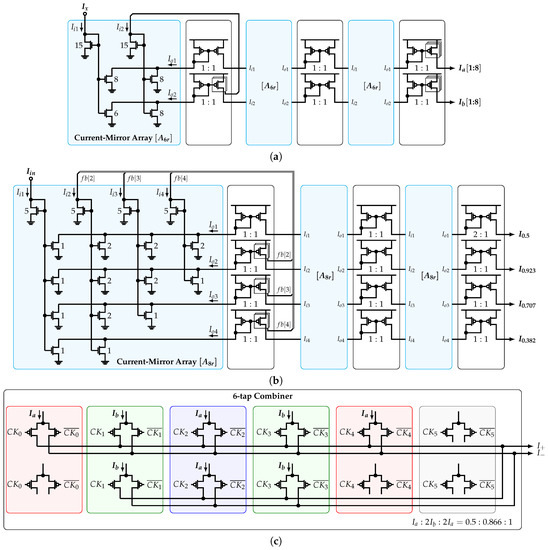

The circuit-level implementation of the 6-tap CG is shown in Figure 14a. It implements a cascade of three stages of matrix along with its norm based on NMOS current mirrors (CMs). As presented in Section 3.3, the first stage is connected in a closed loop in order to achieve a filter’s output with SFDR dB. In this work, the number of SCM stages is set to three due to a trade-off between the coefficient accuracy and area overhead. The PMOS CMs are used to transport the currents from stage to stage. The last PMOS CM provides eight copies of currents and . The same approach is used to implement the 8-tap CG, as shown in Figure 14b. The implementation of the combiner unit is shown in Figure 14c. It is divided in twelve differential pairs and uses four copies of and that are connected as tail currents. In addition, six phases , each with its corresponding inverted version, are used to steer the input currents accordingly to the pattern presented in Figure 13b. If a negative sign is required, the differential clock is connected in opposite polarity. In this way, each section of the combiner inside the colored rectangles corresponds to each 6-tap coefficients; i.e., , , 1, , , and 0.

Figure 14.

Circuit-level implementation of (a) 6-tap CG, (b) 8-tap CG, and (c) 6-tap combiner unit.

5. Measurement Results

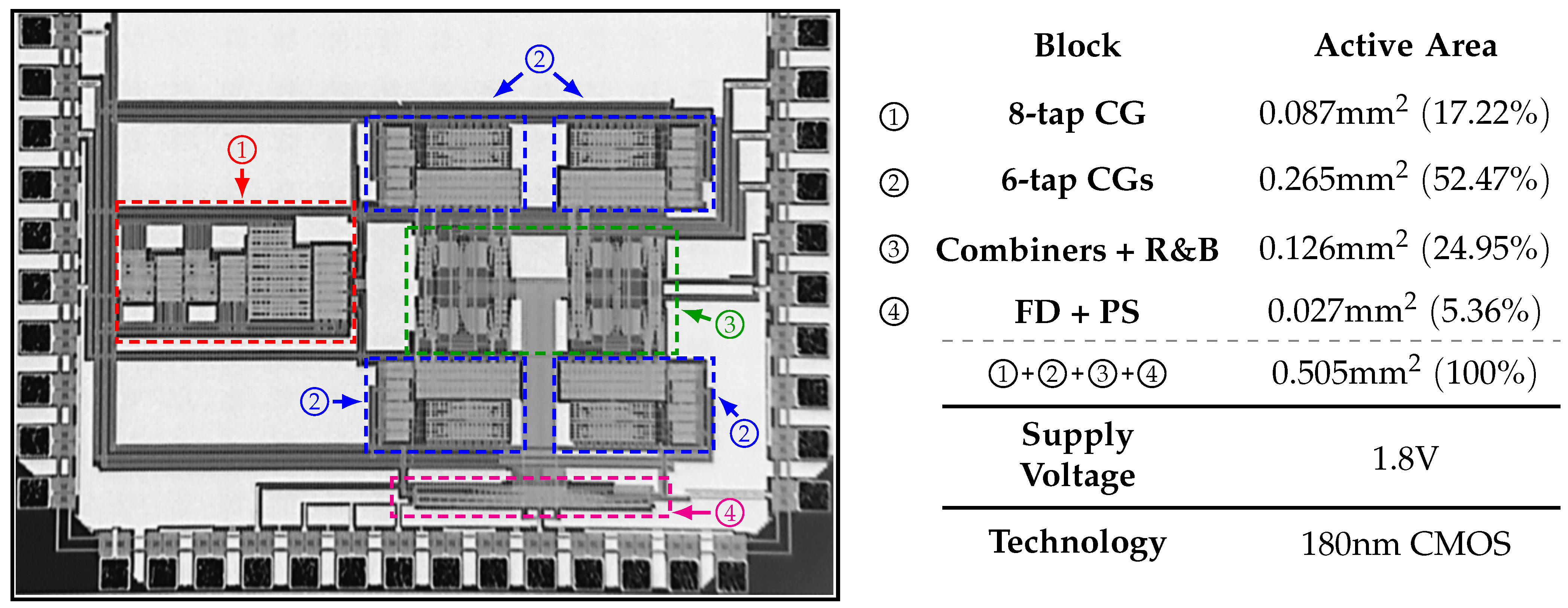

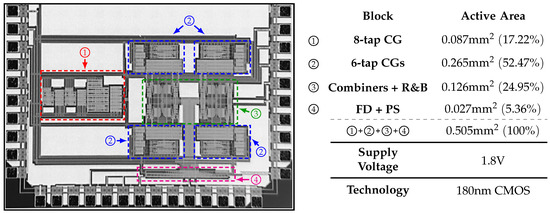

The proposed single-tone generator is fabricated in 180 nm CMOS technology, operates with a supply voltage of V, and occupies an area of mm. Its micrograph is shown in Figure 15 along with the area occupied by each sector and its corresponding percentage with respect to the total area. The CGs occupy around of the total area, since they are composed of a large amount of CMs. Furthermore, these CMs use large transistors in order to reduce their current–ratio mismatch, i.e., to improve the coefficients’ precision. In a CMOS process, the mismatch between two nominally identical transistors is inversely proportional to their channel length. Furthermore, recall that due to the recursive nature of the proposed solution, several identical blocks are required in order to obtain a specific SFDR, increasing the occupied area even further. In addition, the uncoupling of the phase generator from the coefficient generator contributes to the area cost.

Figure 15.

Micrograph of the fabricated single-tone generator.

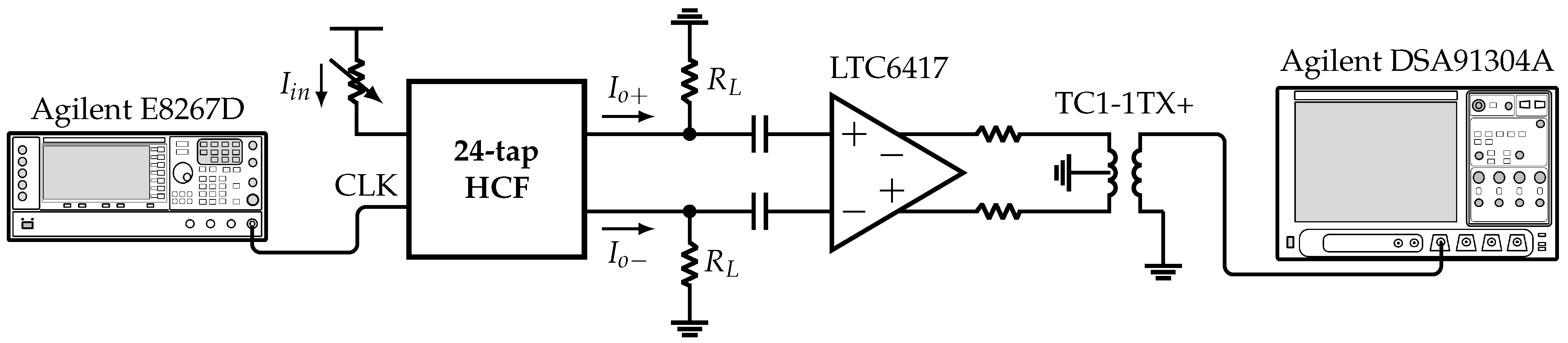

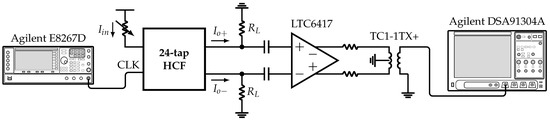

As presented in Section 4, the system incorporates six HCFs, which are selectable based on the value of the inputs and . The former selects between the 6-tap, 12-tap, or 24-tap HCFs, and the latter selects between the fundamental or 5th harmonic of the SW signal with frequency . Figure 16 shows the measurement setup. The clock signal with frequency is provided by an Agilent E8267D vector signal generator. The input current is set by a variable resistor. The differential output current is converted to voltage by the off-chip load resistors . Next, this signal is buffered and converted to single-ended by the LTC6417 and TC1-1TX+, respectively. Finally, the resulting signal is analyzed using the Agilent DSA91304A Infiniium digital signal analyzer.

Figure 16.

Measurement setup.

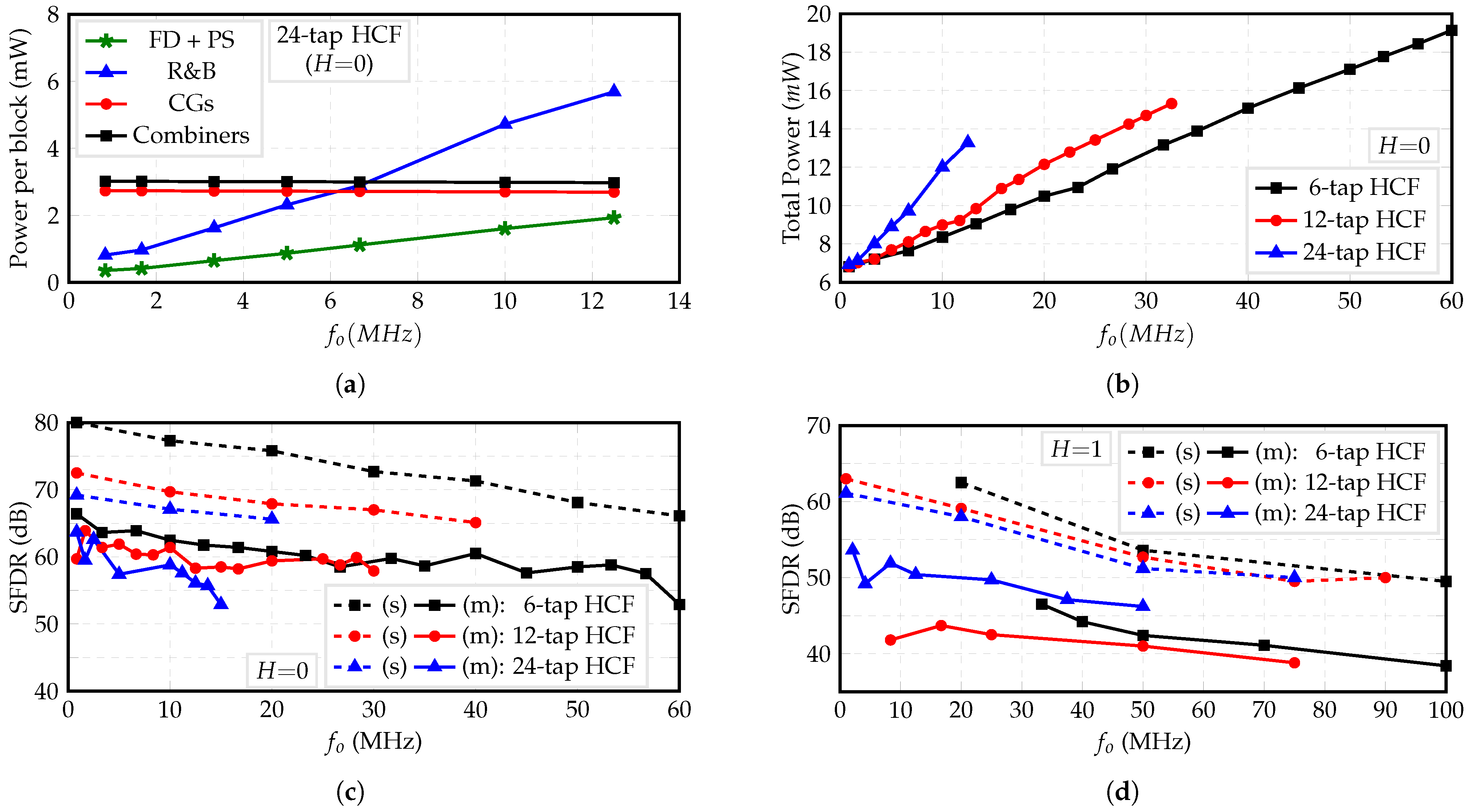

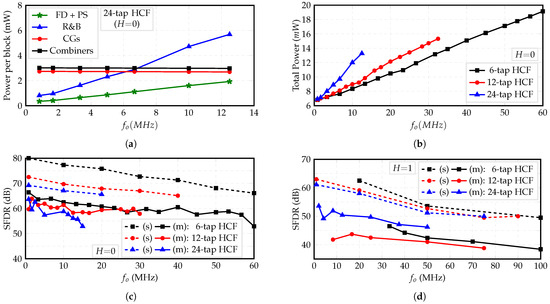

Figure 17a shows the measured power consumption of each block versus the output frequency of the 24-tap HCF when the fundamental frequency of , , is of interest or . Since the CGs only carry DC currents, its power consumption is independent of frequency. Furthermore, these currents are fed to the unit combiners, which steer them according to the pattern shown in Figure 13; hence, the combiner’s power consumption is also constant. Due to their digital nature, the FD, PS, and R&B blocks consume power proportional to the output frequency. In addition, Figure 17b shows the total power consumption of the 6-tap, 12-tap, and 24-tap HCFs versus the output frequency when . These results show that the slopes of the curves are proportional to the filter’s order. This difference is mainly dictated by the fully digital blocks FD, PS, and R&B, especially the former, which enables only the required n DFFs.

Figure 17.

(a) Measured total power consumption of HCFs, (b) power consumption per block of 24-tap HCF for , and simulated (s) and measured (m) SFDR for (c) and (d) .

The SFDR versus output frequency is shown in Figure 17c,d, for and , respectively. It is noted that the SFDR decreases as the output frequency increases. This is due to the increasing phase error from the FD that causes even harmonics to show at the output [14]. Only the waveforms that present even harmonics with lower power than the odd cancelable harmonics are considered. Since the working frequency of the FD is greater for than for , smaller SFDR values are obtained for .

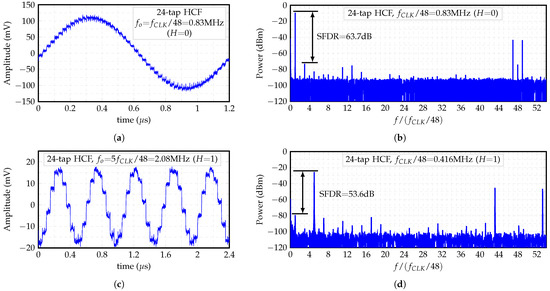

Figure 18a,b show the output’s waveform and power spectral density (PSD) of the 24-tap HCF, respectively, when . The obtained staircase sine-wave waveform presents the first pair of non-cancelable harmonics at and , which can be suppresed with a low-order passive LPF [12,13,15]. In addition, Figure 18c,d show the output’s waveform and PSD of the 24-tap HCF, respectively, when . The first pair of non-cancelable harmonics is located at and . Note that the carrier is located at .

Figure 18.

(a) Transient waveform and (b) PSD of HCF’s output for , and (c) Transient waveform and (d) PSD of HCF’s output for .

Table 1 summarizes the performance of the six HCFs proposed in this work and compares them to previous works. The Figure of Merit (FoM) used in this work is given by

where is the maximum output frequency, is the highest measured SFDR, AF is the number of available filters, FNCH is the first non-cancelable harmonic, is the maximum total power consumption, and A is the area. This FoM is based on the one used by [13,14] with the addition that it accounts for the programmability and the harmonic-canceling range of the system. In this fashion, the number of implemented HCFs in the same area, i.e., the system’s area efficiency, is included in the FoM. On the other hand, recall that an external LPF is still required at the output of the HC-based generators due to the presence of the non-cancelable harmonics at . The order (and therefore, the complexity and power consumption) of the required external LPF is inversely proportional to the order n of the HCF. For this reason, it is relevant to include the FNCH in the FoM.

Table 1.

Performance comparison.

In summary, this work presents the only programmable HCF and the highest-order HCF. The 24-tap HCF allows the cancellation up to the 47th harmonic of the SW signal , which is the highest FNCH reported to the best knowledge of the authors. It also implements the first band-pass HCF. The proposed SCM-based HCFs provide SFDR and power consumption values comparable to previous works that use calibration techniques. For this work, the calculated FoM only includes the three HCFs when . Considering the FoM values, this work performs better than most of the previous works except [13] only after it uses calibration.

6. Discussion

In the presented analysis, only ideal SCM elements and equally spaced SWs are considered. Therefore, it does not include non-idealities such as coefficients mismatch due to variations during fabrication or phase errors produced by the FD, PS, and R&B blocks. Under ideal conditions, as shown in Figure 7, the SFDR of the output signal increases as the number of SCM stages, M, increases, for a given HCF order n. Unfortunately, as presented in [16], non-idealities set a maximum limit for the output linearity. In other words, it is expected that the SFDR saturates and remains constant regardless of the number of SCM stages. This is reflected in the measured SFDR values, which are lower than expected from the ideal analysis. For this reason, an statistical analysis is required to optimize the HCF design in a future work. For instance, a model of the proposed HCF that considers the standard deviation of the CMs and the phase errors can be used to evaluate the trade-off between phase error, coefficient precision, and SFDR.

The use of a first-order approximation of the matrix norm is another source of SFDR limitation. Nonetheless, a better approximation requires the ratio of higher-integer numbers. For instance, consider the HCF of order . Its ideal norm is approximated as . The next set of integer numbers, the ratio of which is closer to , is . The use of 15 and 56 in the matrix norm implementation implies the use of more unit transistors and a more complex device layout, i.e., more error sources that affect the SFDR.

In order to increase the output frequency range, the phase error produced by the FD, PS, and R&B blocks must be reduced. Note that these blocks operate at . This is the main reason for the difference between the frequency ranges of the 6-tap, 12-tap, and 24-tap HCFs. In order to reduce the phase error in a future work, a delay error correction mechanism would be required. This can be provided by a Delay-Locked Loop (DLL) that generates the required phases with a negative feedback loop.

7. Conclusions

In this work, a harmonic-canceling single-tone synthesizer that uses an SCM-based coefficient generator for BIST applications is proposed. This coefficient generator produces irrational coefficients from integer numbers in a recursive approach with no calibration scheme. Measured SFDR values prove the effectiveness of the proposed SCM-based coefficient generator architecture, since they are comparable with those of previous works that use calibration. The selectable 24-tap, 12-tap, and 6-tap HCFs are implemented along with their band-pass versions. They cover a frequency range from to 100 MHz and provide the highest number of operation modes and the highest first non-cancellable harmonic reported.

Author Contributions

Conceptualization, H.O.; formal analysis, H.O.; investigation, H.O. and G.G.G.-L.; resources, G.G.G.-L.; data curation, G.G.G.-L.; writing—original draft preparation, G.G.G.-L.; writing—review and editing, G.G.G.-L., H.O., J.J.E.-L. and O.M.-T.; visualization, G.G.G.-L.; supervision, J.J.E.-L. and O.M.-T.; project administration, O.M.-T. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Acknowledgments

The authors would like to thank Edgar Sanchez-Sinencio for his inspiration and contribution to this work. His legacy will transcend in his family, friends and students. In addition, the authors would like to thank Silicon Labs and MOSIS for their contribution to this work.

Conflicts of Interest

The authors declare no conflict of interest.

Abbreviations

The following abbreviations are used in this manuscript:

| BIST | Built-In Self-Test |

| HC | Harmonic Canceling |

| HCF | Harmonic-Canceling Filter |

| SCM | Skew-Circulant Matrix |

| SFDR | Spurious-Free Dynamic Range |

| DUT | Device-Under-Test |

| ADC | Analog-to-Digital Converter |

| THD | Total Harmonic Distortion |

| BPF | Band-Pass Filter |

| DDFS | Direct Digital Frequency Synthesizer |

| P2AM | Phase-to-Amplitude Mapping |

| CG | Coefficent Generator |

| SW | Square-Wave |

| CMOS | Complementary Metal-Oxide Semiconductor |

| CM | Current-Mirror |

| FD | Frequency Divider |

| PS | Phase Scrambler |

| R&B | Retimer and Buffer |

| NR | Not Reported |

| VCCS | Voltage-Controlled Current Source |

| DEM | Dynamic Element Matching |

Appendix A. Eigenvalues of the Even-Order SCM with Ideal (Irrational) HCF Coefficients

Consider the even-order SCM , where for . From (15), the eigenvalues of are

Then

Consequently, the eigenvalues of the even-order SCM are given by

Appendix B. Eigenvalues of the Even-Order SCM with Non-Ideal (Integer) HCF Coefficients

Consider the even-order SCM , where for , and is the sign function. From (15), the eigenvalues of are

Then

From (A7), the geometric series can be further reduced using their closed form. It follows that

Simplifying

Therefore, the eigenvalues of the even-order SCM are

Appendix C. Equivalence between a Cascade of Lower Order HCFs and a Higher Order HCF

Consider Equation (28), which describes the cascade of two SCM-based HCFs of order and . Since matrix is an SCM, it is true that is also an SCM with its first row elements upsampled by . The same holds for . Their eigenvalues are given by (A1) and are equal to

where

where

Since matrices and are SCMs, their product is also an SCM. Furthermore, since all of them present the same size , they all share the same eigenvectors. The eigenvalues , of the resultant matrix are expressed as

where , , and if and only if . It follows that

Since n phases equally spaced by are required, such that , and considering that , can be expressed as

References

- Stroud, C.E. An Overview of BIST. In A Designer’s Guide to Built-In Self-Test; Springer: Boston, MA, USA, 2002; pp. 1–12. [Google Scholar]

- Garayar-Leyva, G.G.; Osman, H.; Estrada-López, J.J.; Sánchez-Sinencio, E. A Harmonic-Canceling Synthesizer using Skew-Circulant-Matrix-Based Coefficient Generator. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–5. [Google Scholar]

- Bahmani, F.; Sanchez-Sinencio, E. Low THD bandpass-based oscillator using multilevel hard limiter. IET Circuits Devices Syst. 2007, 1, 151–160. [Google Scholar] [CrossRef] [Green Version]

- Park, S.W.; Ausin, J.L.; Bahmani, F.; Sanchez-Sinencio, E. Nonlinear Shaping SC Oscillator With Enhanced Linearity. IEEE J. Solid-State Circuits 2007, 42, 2421–2431. [Google Scholar] [CrossRef] [Green Version]

- Mohieldin, A.N.; Emira, A.A.; Sanchez-Sinencio, E. A 100-MHz 8-mW ROM-less quadrature direct digital frequency synthesizer. IEEE J. Solid-State Circuits 2002, 37, 1235–1243. [Google Scholar] [CrossRef]

- Byung-Do, Y.; Choi, J.H.; Seon-Ho, H.; Lee-Sup, K.; Hyun-Kyu, Y. An 800-MHz low-power direct digital frequency synthesizer with an on-chip D/a converter. IEEE J. Solid-State Circuits 2004, 39, 761–774. [Google Scholar] [CrossRef]

- Yeoh, H.C.; Jung, J.; Jung, Y.; Baek, K. A 1.3-GHz 350-mW Hybrid Direct Digital Frequency Synthesizer in 90-nm CMOS. IEEE J. Solid-State Circuits 2010, 45, 1845–1855. [Google Scholar] [CrossRef]

- Yoo, T.; Yeoh, H.C.; Jung, Y.; Cho, S.; Kim, Y.S.; Kang, S.; Baek, K. A 2 GHz 130 mW Direct-Digital Frequency Synthesizer with a Nonlinear DAC in 55 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 2976–2989. [Google Scholar] [CrossRef]

- Yang, C.; Weng, J.; Chang, H. A 5-GHz Direct Digital Frequency Synthesizer Using an Analog-Sine-Mapping Technique in 0.35-μm SiGe BiCMOS. IEEE J. Solid-State Circuits 2011, 46, 2064–2072. [Google Scholar] [CrossRef]

- Elsayed, M.M.; Sanchez-Sinencio, E. A Low THD, Low Power, High Output-Swing Time-Mode-Based Tunable Oscillator via Digital Harmonic-Cancellation Technique. IEEE J. Solid-State Circuits 2010, 45, 1061–1071. [Google Scholar] [CrossRef]

- Soda, M.; Bando, Y.; Takaya, S.; Ohkawa, T.; Takaramoto, T.; Yamada, T.; Kumashiro, S.; Mogami, T.; Nagata, M. On-chip sine-wave noise generator for analog IP noise tolerance measurements. In Proceedings of the 2010 IEEE Asian Solid-State Circuits Conference, Beijing, China, 8–10 November 2010; pp. 1–4. [Google Scholar]

- Barragan, M.J.; Leger, G.; Vazquez, D.; Rueda, A. On-chip sinusoidal signal generation with harmonic cancelation for analog and mixed-signal BIST applications. Analog. Integr. Circuits Signal Process. 2015, 82, 67–79. [Google Scholar] [CrossRef] [Green Version]

- Shi, C.; Sánchez-Sinencio, E. 150–850 MHz High-Linearity Sine-wave Synthesizer Architecture Based on FIR Filter Approach and SFDR Optimization. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2227–2237. [Google Scholar] [CrossRef]

- Aluthwala, P.D.; Weste, N.; Adams, A.; Lehmann, T.; Parameswaran, S. Partial Dynamic Element Matching Technique for Digital-to-Analog Converters Used for Digital Harmonic-Cancelling Sine-Wave Synthesis. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 296–309. [Google Scholar] [CrossRef]

- Malloug, H.; Barragan, M.J.; Mir, S. A 52 dB-SFDR 166 MHz sinusoidal signal generator for mixed-signal BIST applications in 28 nm FDSOI technology. In Proceedings of the 2019 IEEE European Test Symposium (ETS), Baden-Baden, Germany, 27–31 May 2019; pp. 1–6. [Google Scholar]

- Shi, C.; Sánchez-Sinencio, E. On-Chip Two-Tone Synthesizer Based on a Mixing-FIR Architecture. IEEE J. Solid-State Circuits 2017, 52, 2105–2116. [Google Scholar] [CrossRef]

- Ahmad, S.; Azizi, K.; Zadeh, I.E.; Dabrowski, J. Two-tone PLL for on-chip IP3 test. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010; pp. 3549–3552. [Google Scholar]

- Méndez-Rivera, M.; Valdes, A.; Silva-Martínez, J.; Sanchez-Sinencio, E. An On-Chip Spectrum Analyzer for Analog Built-In Testing. J. Electron. Test. 2005, 21, 205–219. [Google Scholar] [CrossRef]

- Jose, A.; Jenkins, K.; Reynolds, S. On-chip spectrum analyzer for analog built-in self test. In Proceedings of the 23rd IEEE VLSI Test Symposium (VTS’05), Palm Strings, CA, USA, 1–5 May 2005; pp. 131–136. [Google Scholar]

- Shoghi, P.; Weldon, T.P.; Barnwell, C.J. Experimental results for a Successive Detection Log Video Amplifier in a single-chip frequency synthesized radio frequency spectrum analyzer. In Proceedings of the IEEE Southeastcon 2009, Atlanta, GA, USA, 5–8 March 2009; pp. 379–382. [Google Scholar]

- Nose, K.; Mizuno, M. A 0.016 mm2, 2.4 GHz RF signal quality measurement macro for RF test and diagnosis. In Proceedings of the 2007 IEEE Symposium on VLSI Circuits, Kyoto, Japan, 14–16 June 2007; pp. 212–213. [Google Scholar]

- Chauhan, H.; Choi, Y.; Onabajo, M.; Jung, I.S.; Kim, Y.B. Accurate and Efficient On-Chip Spectral Analysis for Built-In Testing and Calibration Approaches. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 497–506. [Google Scholar] [CrossRef]

- Choi, Y.; Chang, C.H.; Jung, I.S.; Onabajo, M.; Kim, Y.B. A built-in calibration system with a reduced FFT engine for linearity optimization of low power LNA. In Proceedings of the 2014 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Amsterdam, The Netherlands, 1–3 October 2014; pp. 222–227. [Google Scholar]

- Shi, C.; Sánchez-Sinencio, E. An On-Chip Built-in Linearity Estimation Methodology and Hardware Implementation. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 897–908. [Google Scholar] [CrossRef]

- Davies, A.C. Digital Generation of Low-Frequency Sine Waves. IEEE Trans. Instrum. Meas. 1969, 18, 97–105. [Google Scholar] [CrossRef]

- Gray, R.M. Circulant Matrices. In Toeplitz and Circulant Matrices: A Review; Now Publishers Inc.: Boston, MA, USA, 2006; pp. 31–34. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).