A 90 GHz Broadband Balanced 8-Way Power Amplifier for High Precision FMCW Radar Sensors in 65-nm CMOS

Abstract

:1. Introduction

2. Design of 4-Way Push-Pull Power Amplifier

2.1. Architecture of 4-Way PA

2.2. Differential PA Unit Cell

2.3. Transformer-Based Matching Network

2.4. Transformer-Based Parallel Combiner

3. Design of Balanced 8-Way Power Amplifier

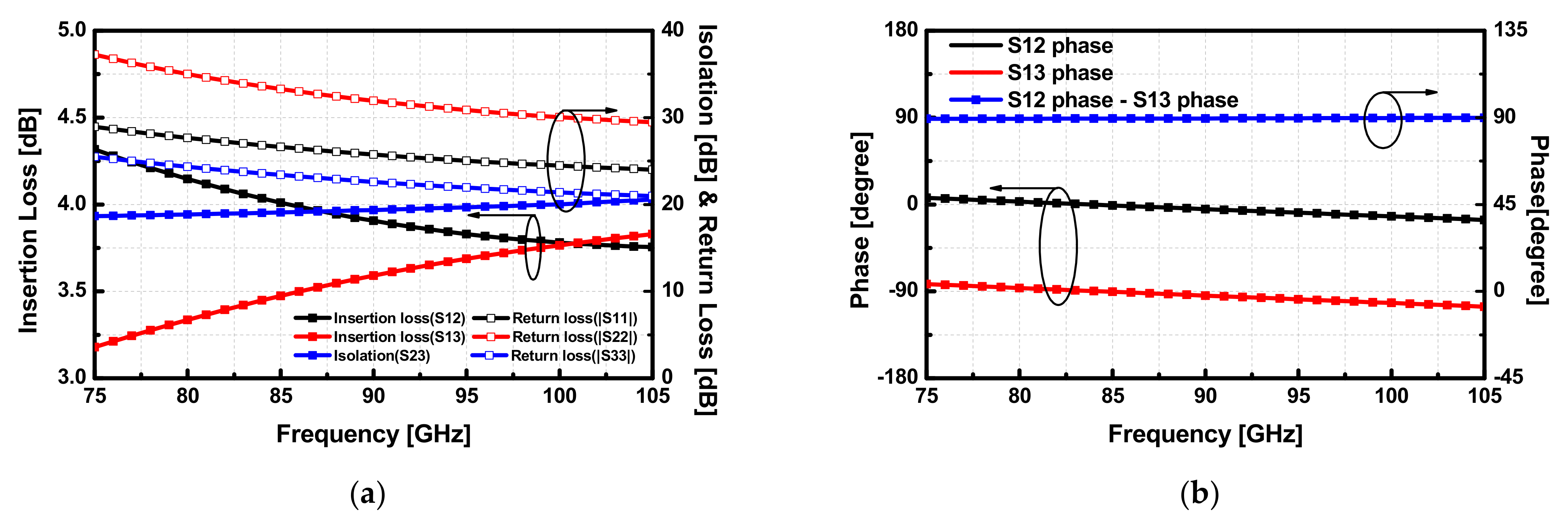

3.1. W-Band Microstrip Lange Coupler

3.2. Robustness to Load Mismatch

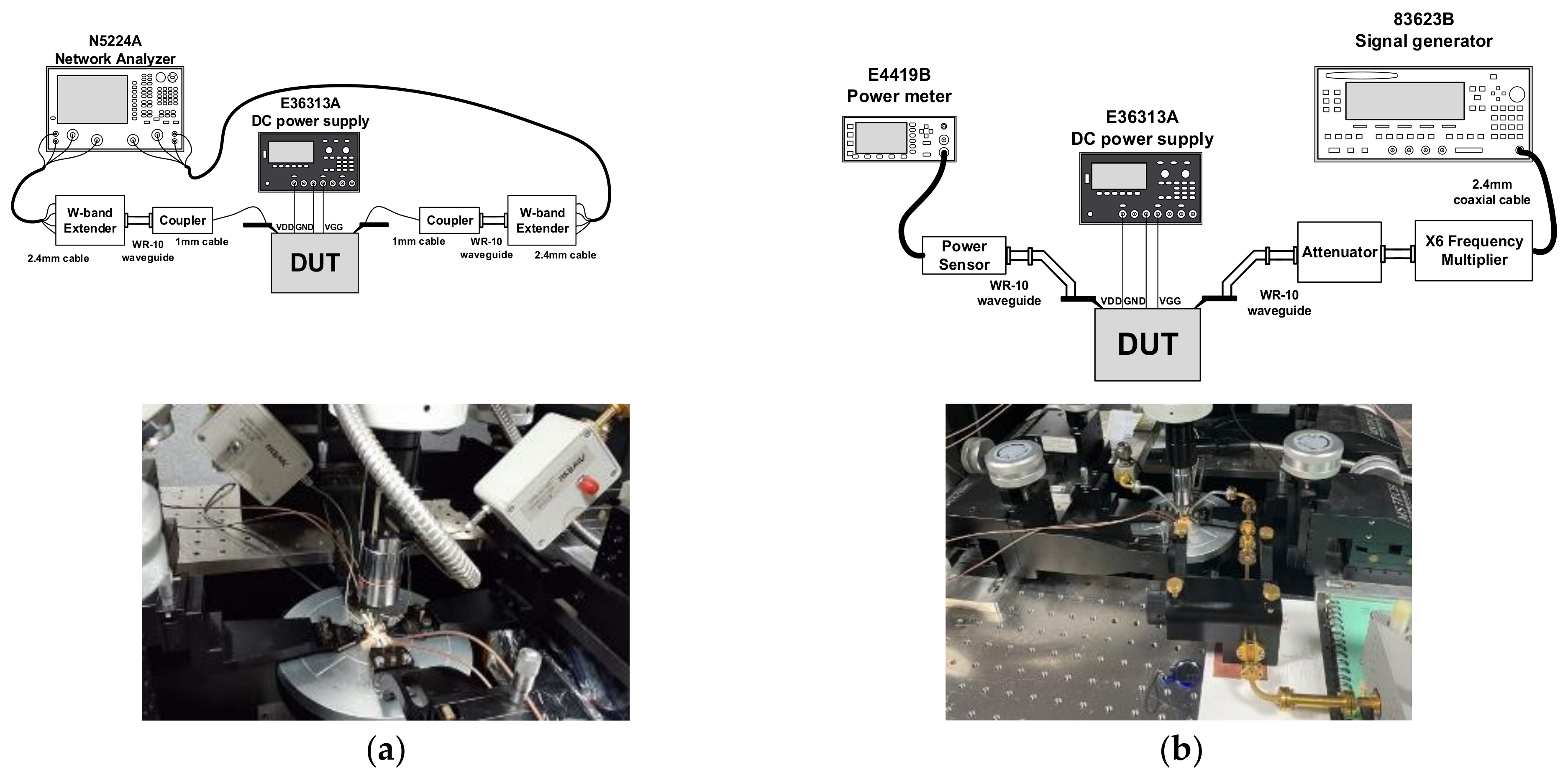

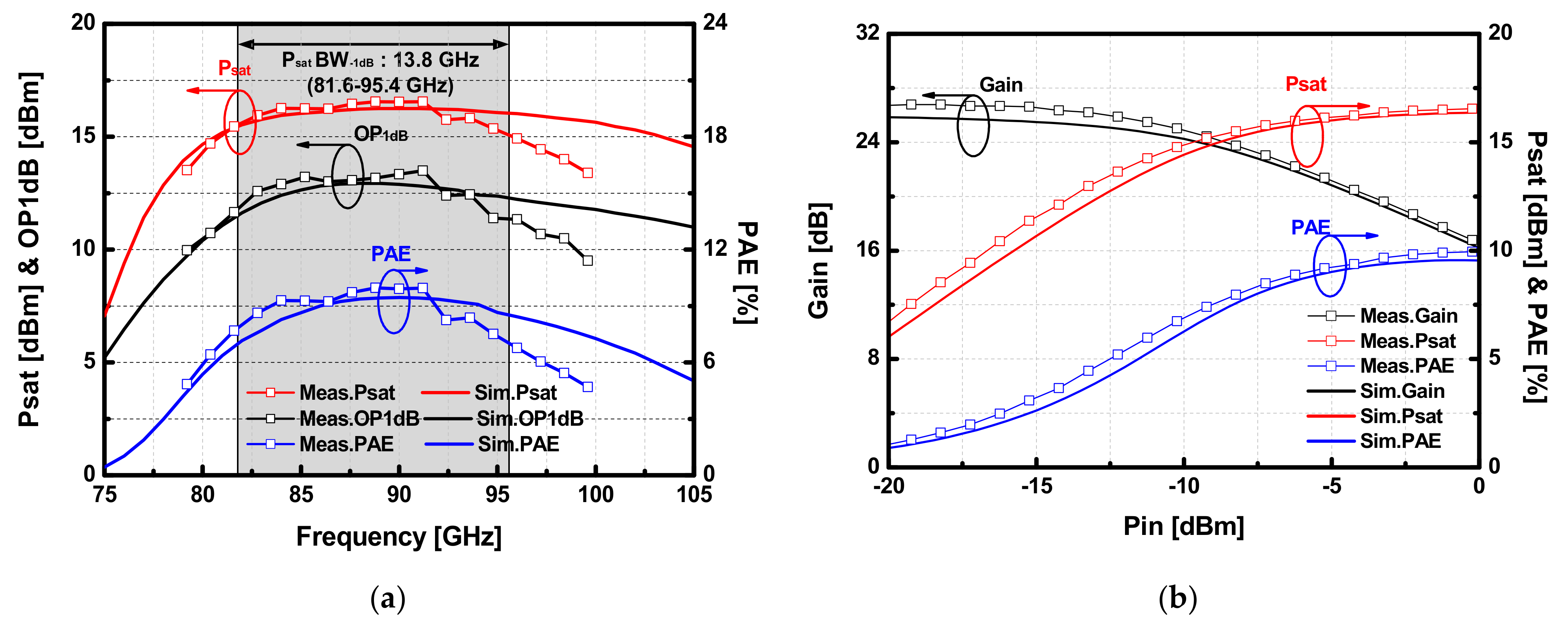

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Welp, B.; Hansen, S.; Briese, G.; Kuppers, S.; Thomas, S.; Bredendiek, C.; Pohl, N. Versatile Dual-Receiver 94-GHz FMCW Radar System with High Output Power and 26-GHz Tuning Range for High Distance Applications. IEEE Trans. Microw. Theory Tech. 2020, 68, 1195–1211. [Google Scholar] [CrossRef]

- Milosavljevic, I.M.; Glavonjic, D.P.; Krcum, D.P.; Jovanovic, S.; Mihajlovic, V.R.; Milovanovic, V.M. A 55-64-GHz Fully Integrated Miniaturized FMCW Radar Sensor Module for Short-Range Applications. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 677–679. [Google Scholar] [CrossRef]

- Asada, H.; Matsushita, K.; Bunsen, K.; Okada, K.; Matsuzawa, A. A 60GHz CMOS power amplifier using capacitive cross-coupling neutralization with 16 % PAE. In Proceedings of the 2011 6th European Microwave Integrated Circuit Conference, Manchester, UK, 10–13 October 2011; pp. 554–557. [Google Scholar]

- Pornpromlikit, S.; Jeong, J.; Presti, C.D.; Scuderi, A.; Asbeck, P.M. A Watt-Level Stacked-FET Linear Power Amplifier in Silicon-on-Insulator CMOS. IEEE Trans. Microw. Theory Tech. 2010, 58, 57–64. [Google Scholar] [CrossRef]

- Wu, K.L.; Lai, K.T.; Hu, R.; Jou, C.F.; Niu, D.C.; Shiao, Y.S. 77-110 GHz 65-nm CMOS Power Amplifier Design. IEEE Trans. Terahertz Sci. Technol. 2014, 4, 391–399. [Google Scholar] [CrossRef]

- Hsiao, Y.H.; Tsai, Z.M.; Liao, H.C.; Kao, J.C.; Wang, H. Millimeter-Wave CMOS Power Amplifiers with High Output Power and Wideband Performances. IEEE Trans. Microw. Theory Tech. 2013, 61, 4520–4533. [Google Scholar] [CrossRef]

- Jia, H.K.; Chi, B.Y.; Kuang, L.X.; Wang, Z.H. A W-Band Power Amplifier Utilizing a Miniaturized Marchand Balun Combiner. IEEE Trans. Microw. Theory Tech. 2015, 63, 719–725. [Google Scholar] [CrossRef]

- Chen, L.; Zhang, L.; Wang, Y. A 26.4-dB Gain 15.82-dBm 77-GHz CMOS Power Amplifier with 15.9%; PAE Using Transformer-Based Quadrature Coupler Network. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 78–81. [Google Scholar] [CrossRef]

- Sandstrom, D.; Martineau, B.; Varonen, M.; Karkkainen, M.; Cathelin, A.; Halonen, K.A. 94GHz power-combining power amplifier with +13dBm saturated output power in 65nm CMOS. In Proceedings of the 2011 IEEE Radio Frequency Integrated Circuits Symposium, Baltimore, MD, USA, 5–7 June 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Gu, Q.J.; Xu, Z.W.; Chang, M.C.F. Two-Way Current-Combining W-Band Power Amplifier in 65-nm CMOS. IEEE Trans. Microw. Theory Tech. 2012, 60, 1365–1374. [Google Scholar] [CrossRef]

- Son, H.S.; Jang, J.Y.; Kang, D.M.; Lee, H.J.; Park, C.S. A 109 GHz CMOS Power Amplifier with 15.2 dBm Psat and 20.3 dB Gain in 65-nm CMOS Technology. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 510–512. [Google Scholar] [CrossRef]

- Trinh, V.; Park, J.D. A 16.3 dBm 14.1% PAE 28-dB Gain W-Band Power Amplifier with Inductive Feedback in 65-nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 193–196. [Google Scholar] [CrossRef]

- Trinh, V.-S.; Park, J.-D. An 85-GHz Power Amplifier Utilizing a Transformer-Based Power Combiner Operating beyond the Self-Resonance Frequency. IEEE J. Solid-State Circuits 2022, 57, 882–891. [Google Scholar] [CrossRef]

- Long, J.R. Monolithic transformers for silicon RF IC design. IEEE J. Solid-State Circuits 2000, 35, 1368–1382. [Google Scholar] [CrossRef]

- Inagaki, N. Theory of Image Impedance Matching for Inductively Coupled Power Transfer Systems. IEEE Trans. Microw. Theory Tech. 2014, 62, 901–908. [Google Scholar] [CrossRef]

- Trinh, V.S.; Park, J.D. Theory and Design of Impedance Matching Network Utilizing a Lossy On-Chip Transformer. IEEE Access 2019, 7, 140980–140989. [Google Scholar] [CrossRef]

- Engelbrecht, R.S.; Kurokawa, K. A Wide-Band Low Noise L-Band Balanced Transistor Amplifier. Proc. IEEE 1965, 53, 237–247. [Google Scholar] [CrossRef]

- Xue, Y.; Shi, C.; Chen, G.; Chen, J.; Zhang, R. Two W-Band Wideband CMOS MMW PAs for Automotive Radar Transceivers. In Proceedings of the 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 4–6 August 2020. [Google Scholar]

- Kim, J.; Dabag, H.; Asbeck, P.; Buckwalter, J.F. Q-Band and W-Band Power Amplifiers in 45-nm CMOS SOI. IEEE Trans. Microw. Theory Tech. 2012, 60, 1870–1877. [Google Scholar] [CrossRef]

- Lin, C.-H.; Chang, H.-Y. A High Efficiency Broadband Class-E Power Amplifier Using a Reactance Compensation Technique. IEEE Microw. Wirel. Compon. Lett. 2010, 20, 507–509. [Google Scholar] [CrossRef]

| This | [5] | [6] | [9] | [10] | [11] | [18] | [19] | |

|---|---|---|---|---|---|---|---|---|

| Freq (GHz) | 83–96 @90 | 77–110 @87 | 75–100 @90 | 85–100 @94 | 101–117 @109 | 100–117 @109 | 73–89 @81 | 75–90 @80 |

| VDD (V) | 1.2 | 1.2 | 1.2 | 1.8 | 2/1.2 | 1.2 | 2.5 | 2 |

| Gain (dB) | 26.7 | 18 | 12.5 | 13 | 14.1 | 20.3 | 16.1 | 11 |

| (dBm) | 16.5 | 14 | 18 | 14 | 14.8 | 15.2 | 18 | 12.4 |

| (GHz) | 13.8 | 38 † (OP1dB) | 12 | >11 ‡ | >7 ‡ | >9 ‡ | N/A | >7 ‡ (OP1dB) |

| (GHz) | 20.4 | N/A | N/A | 15 | >10 ‡ | >16 ‡ | N/A | >10 ‡(OP1dB) |

| (dBm) | 13.3 | 12 | 17.5 | 10.3 | 11.6 | 12.5 | 12.9 | 12 |

| PAE (%) | 9.9 | 4.5 | 9 | 4 | 9.4 | 10.3 | 12.6 | 14.2 |

| Way | 8 | 4 | 16 | 4 | 4 | 4 | 4 | 1 |

| Size ( | 0.752 | 0.57 | 0.82 | 0.24 | 0.322 | 0.343 | 0.21 (core) | 0.321 |

| FoM * | 92.2 | 77.3 | 79.1 | 72.5 | 79.4 | 86.4 | 83.2 | 73.0 |

| ** | 2420.0 | 204.8 | 237.2 | 28.3 | 127.3 | 677.2 | 419.7 | 37.3 |

| Topology | 4 stage CS + BA | 6 stage CS | 3 stage CS | 3 stage CC | 2 stage CC + 1 stage CS | 4 stage CS | 2 stage CC | 2 stage CC |

| Process | 65 nm | 65 nm | 65 nm | 65 nm | 65 nm | 65 nm | 55 nm | 45 nm SOI |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, H.; Trinh, V.-S.; Park, J.-D. A 90 GHz Broadband Balanced 8-Way Power Amplifier for High Precision FMCW Radar Sensors in 65-nm CMOS. Sensors 2022, 22, 3114. https://doi.org/10.3390/s22093114

Lee H, Trinh V-S, Park J-D. A 90 GHz Broadband Balanced 8-Way Power Amplifier for High Precision FMCW Radar Sensors in 65-nm CMOS. Sensors. 2022; 22(9):3114. https://doi.org/10.3390/s22093114

Chicago/Turabian StyleLee, Hyeonseok, Van-Son Trinh, and Jung-Dong Park. 2022. "A 90 GHz Broadband Balanced 8-Way Power Amplifier for High Precision FMCW Radar Sensors in 65-nm CMOS" Sensors 22, no. 9: 3114. https://doi.org/10.3390/s22093114