Abstract

Research indicates that phase-to-ground short-circuits in a frequency converter can subject the rectifier diode and IGBT to excessive voltage and current, potentially causing damage if the component selection margin during hardware design is insufficient. In order to solve the above problems, this paper studies the design of the LCL filter and ground short circuit problem of the hundred-kilowatt inverter. Firstly, an analytical method for calculating the DC bus capacitance and reactor of the inverter is proposed. The interaction between the DC bus capacitance and the reactor parameters and performance is considered in the implementation process. The parameters of the DC bus capacitor and reactor are given. Secondly, the one-to-ground short circuit of the inverter is studied, and the energy flow mode and mathematical expression of the double boost circuit, considering the influence of the leakage inductance of the power transformer, are given. Based on the above analysis, a method for determining the rectifier diode and IGBT, considering the one-to-ground short circuit of the inverter, is proposed. Finally, a one-hundred-kilowatt inverter is developed, and the corresponding experiments are carried out. The feasibility of the proposed scheme is verified by simulation and experiment.

1. Introduction

Due to the vulnerability of power electronic devices and the complexity of their control, the inverter part, especially the inverter part that implements various PWM control strategies, is a weak link in the system that is prone to failure [1]. Therefore, it is of great practical significance to study how to improve the reliability of the inverter and avoid downtime caused by faults.

The existing research on direct current(DC) bus capacitors either focuses on the reliability of DC capacitors from the perspective of harmonic distribution and electro-thermal stress [2] or uses complex control techniques to reduce the root mean square value of DC bus current [3,4]. There is no literature to discuss the design of DC containers; DC reactor can effectively reduce the peak and rising rate of DC fault current. The current research mainly focuses on the design and optimization of medium and high-voltage DC reactors [5], which has little guiding significance for the design of low-voltage DC reactors.

Although domestic and foreign scholars have performed a lot of research on the selection of DC bus capacitance and DC reactor parameters, they have not considered the impact of a single-phase ground short circuit of the inverter. Aiming at the problem of large voltage and large current caused by the single-phase grounding of the inverter, this paper deduces the formula of DC bus capacitance parameters considering voltage temperature and other factors based on the Newton–Raphson method and gives the method of determining the parameters of rectifier diode and IGBT considering single-phase short circuit. A 380 V/110 kW inverter is fabricated, and the relative ground short circuit test is carried out. The simulation and experimental results show the accuracy and feasibility of the proposed method.

2. Design of Capacitor and DC Reactor in DC Bus

All units of measurement involved in this paper and their abbreviations are shown in Table 1.

Table 1.

Unit of measurement and corresponding abbreviations.

Table 2 shows the system parameters of the 380 V/110 kW frequency converter to be designed in this paper.

Table 2.

380 V/110 kW converter system parameters.

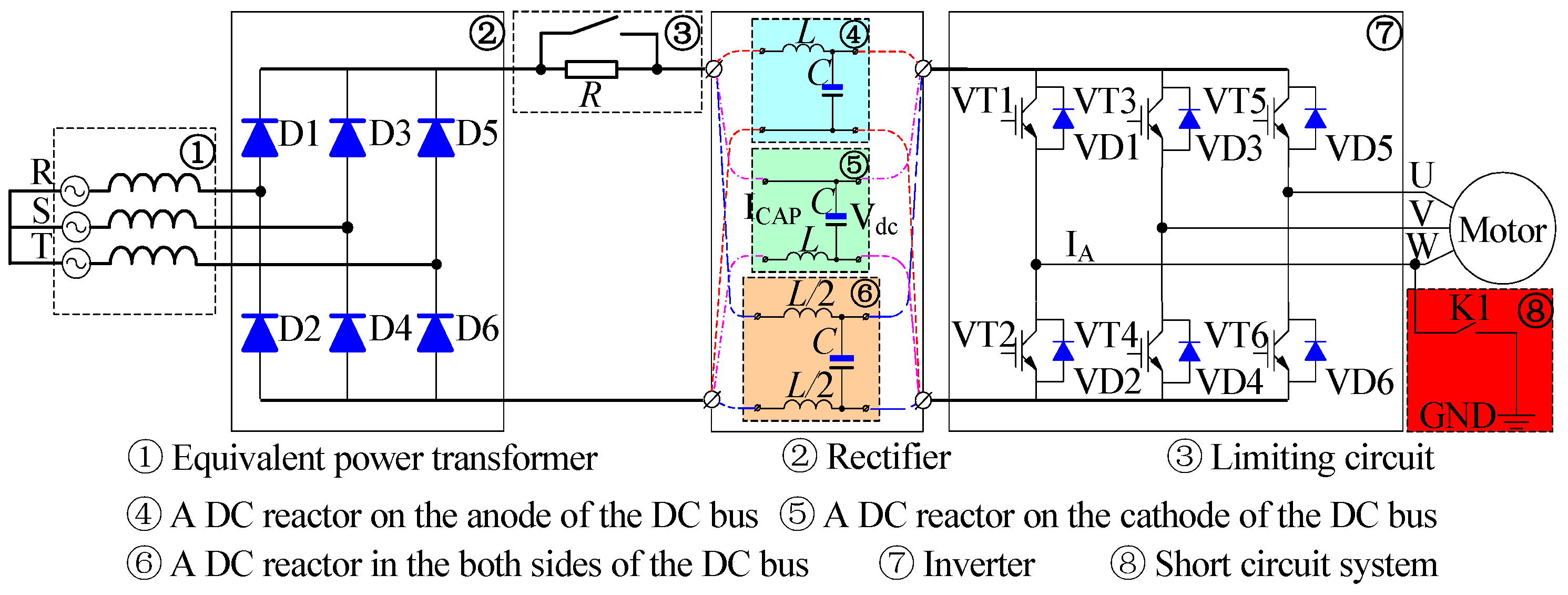

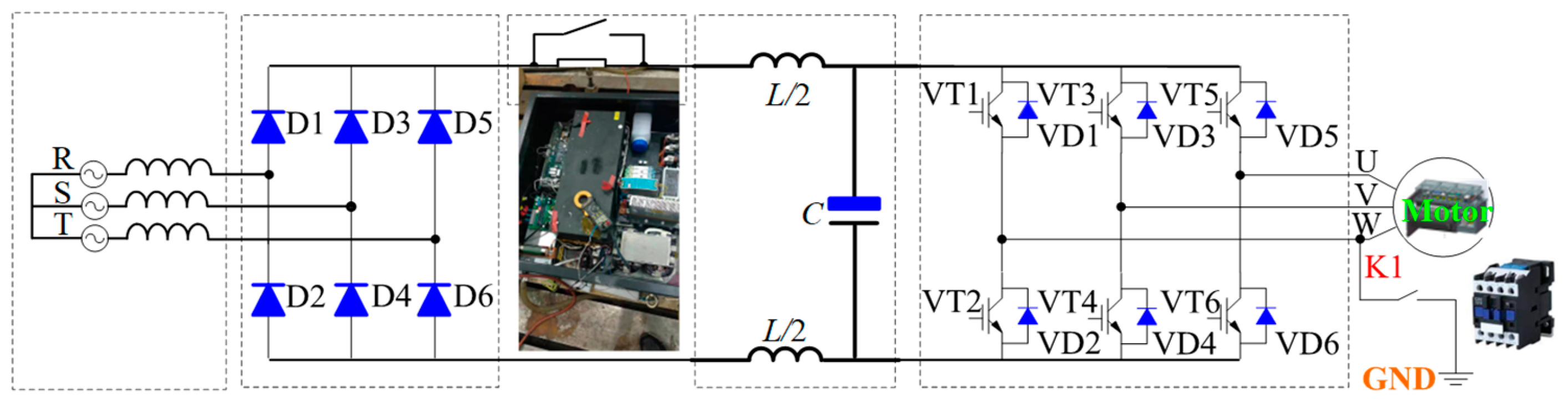

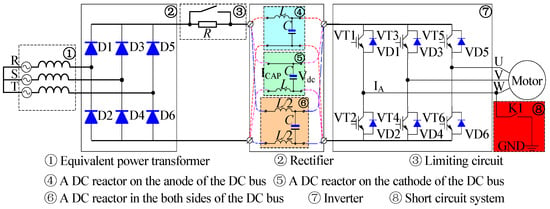

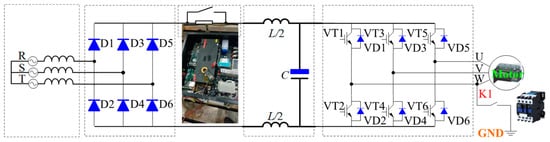

Figure 1 shows the topology of the AC-DC-AC voltage-type frequency control device. It mainly includes a rectifier diode, LC filter, soft start circuit, inverter, load, etc. As shown in Figure 1, for the small and medium power frequency control devices, the system only needs to install the incoming reactor. However, when the system power is large, the DC reactor will be connected in series on DC should be limited to a specific value to maintain the continuity of the current and reduce the current ripple. Enhancing the mitigation of input current waveform distortion arising from capacitor filtering, improving the power factor, and reducing and preventing damage to the rectifier bridge and capacitor overheating due to excessive pulse current [6,7,8,9].

Figure 1.

The topology of the inverter.

2.1. DC Bus Capacitance Design

2.1.1. DC Bus Capacitance Calculation

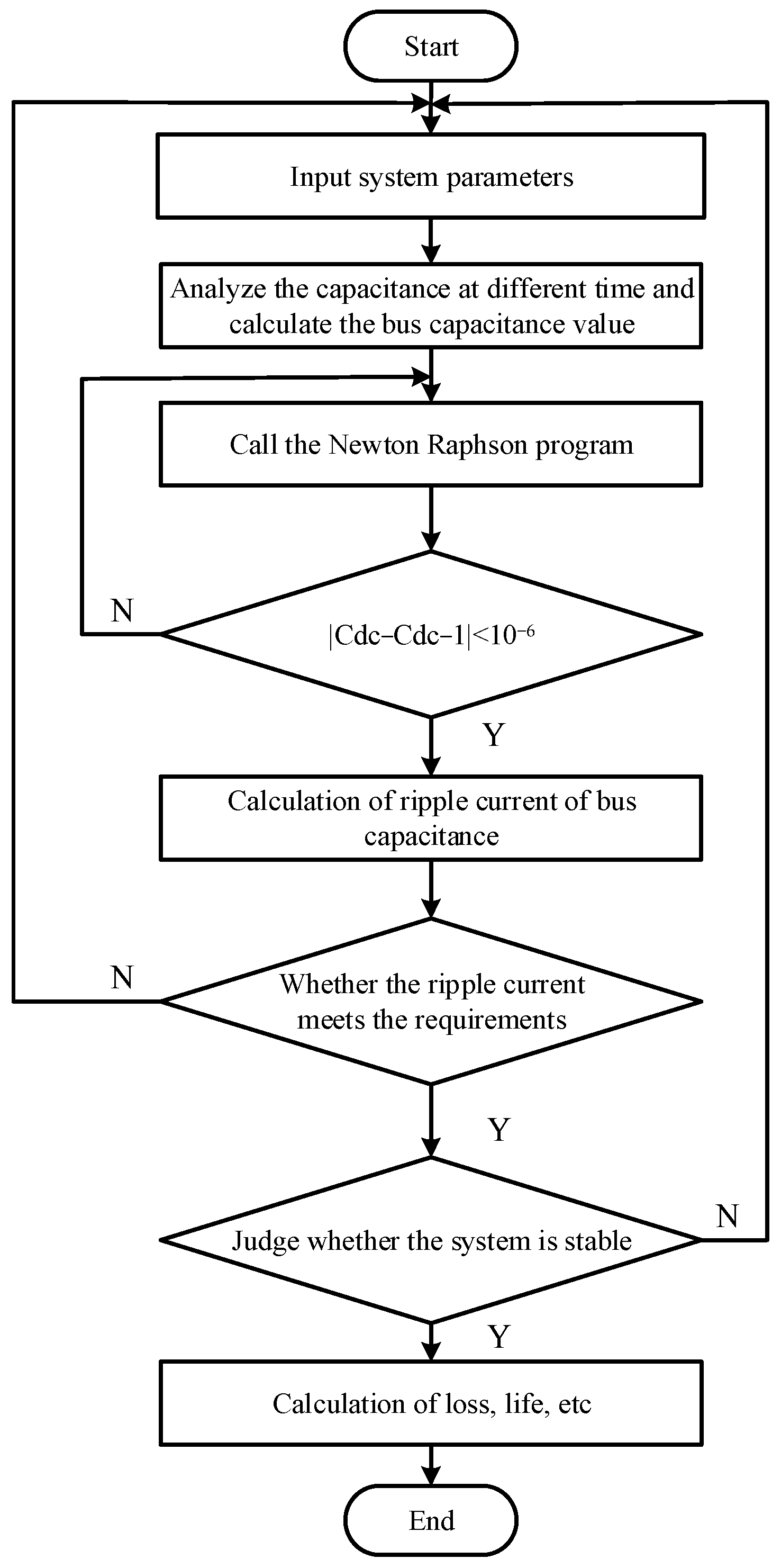

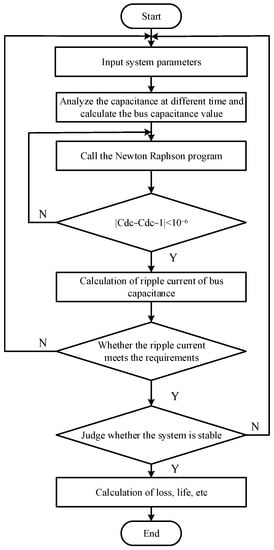

The DC bus capacitance is adopted in the inverter to absorb the fluctuation of the wave so that the output of the system is more steady [10,11]. This paper presents a comprehensive design for the DC Bus Capacitor from the aspects of voltage, volume, temperature, power consumption, and lifetime. Figure 2 illustrates the design process of a DC bus capacitor using the Newton–Raphson approach.

Figure 2.

The calculation process of bus capacitance parameter.

First, the charging and discharging process of the capacitor at different times is analyzed according to the system structure and parameter values. Secondly, the capacitance value is calculated using Newton–Raphson’s method, and then the ripple current is calculated. Finally, the stability of the system is judged.

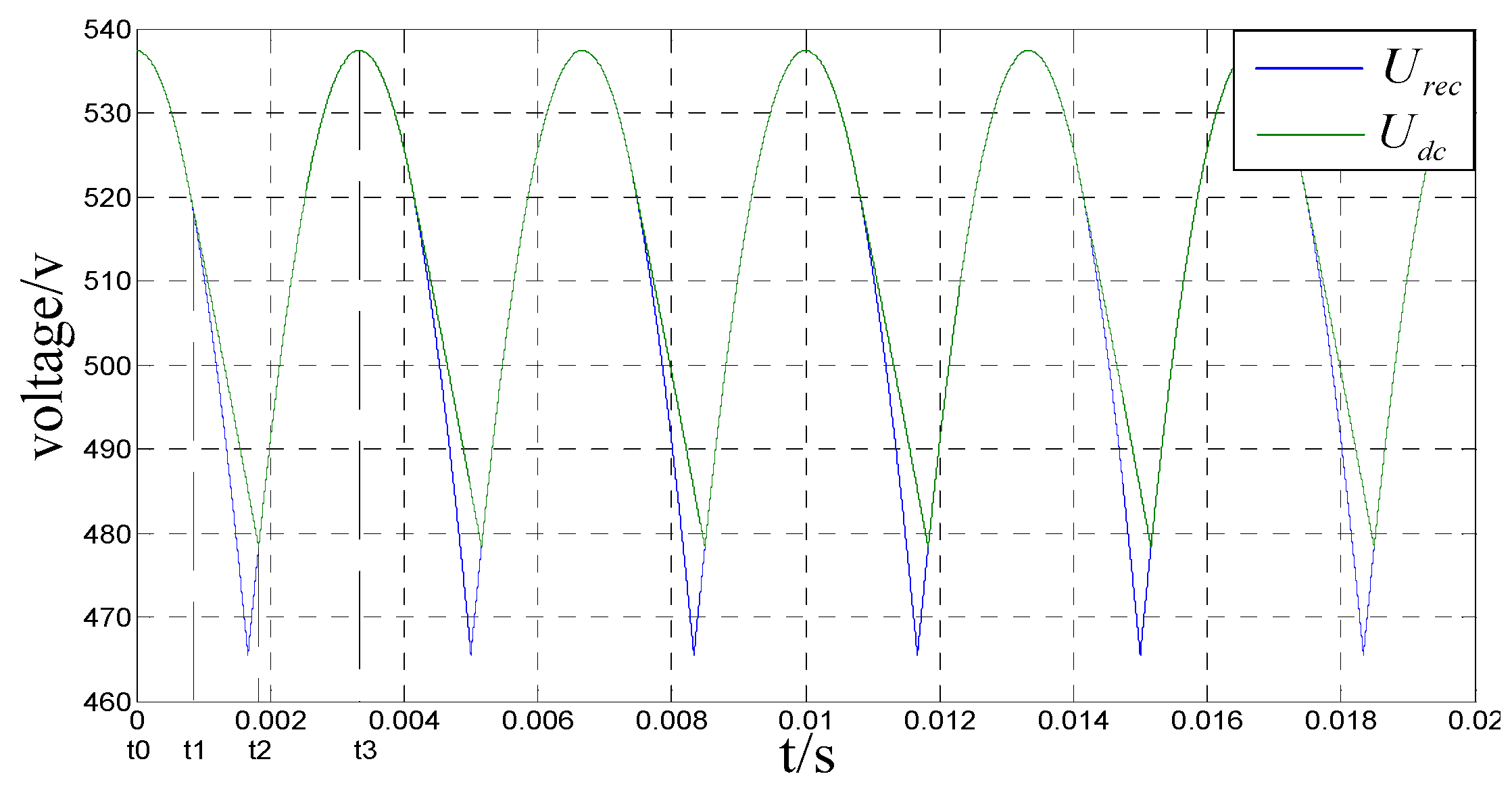

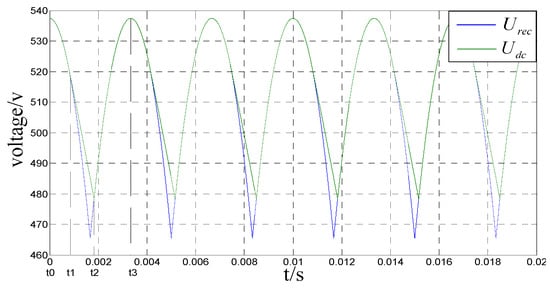

When the DC bus capacitance is large enough, the waveform of the diode rectified output voltage in one cycle is shown in Figure 3. Among them, Urec and Udc are the output voltage waveforms of three-phase uncontrolled rectifier circuits with or without DC bus capacitance.

Figure 3.

Waveform in rectified output cycle.

According to the output characteristics of a three-phase uncontrolled rectifier circuit in one rectifier cycle:

where Idc, Uc, Po_dc, and Cdc are DC bus current, bus voltage, bus capacitance output power, and bus capacitance, respectively.

Stage (t0~t1):

The power required by the load is provided by the three-phase input and the bus capacitor. At this time, the capacitor is in a discharge state.

When t = t1, Ic = −Iload, that is:

Stage (t1~t2):

The power required by the load is completely provided by the bus capacitor, and the bus capacitor is in a discharged state.

To solve the differential Equation:

When t = t1, that is:

At this time, the bus voltage drop percentage and t2 can be obtained, as shown in Equations (7) and (8).

Stage (t2~t3):

The three-phase input supplies power to the load and the bus capacitors. At this time, the capacitor begins to charge.

When the capacitance of the bus is not enough to fully absorb the ripple current on the bus:

Substituting Equation (3) into Equation (10), get:

When the circuit parameters meet the conditions of Equation (11), Uc = Urec is valid for the entire circuit working process. At this time, the percentage of bus voltage drop is:

Now suppose that the load current is completely obtained from the bus capacitance at time t0, when t1 = t0, according to Equation (5):

When t = t2, combining Equations (7) and (13) can have:

In this situation, the discharge time is longer than the actual discharge time. Therefore, the calculated value of Cdc obtained by Equation (14) is greater than the actual value. If capacitance calculated by Equation (14) is the max of the bus capacitance Cdc_max, then the initial search interval of Newton–Raphson method can be determined as [0, Cdc_max]. It is assumed that the bus capacitance can completely absorb the ripple current and then leave a little margin, taking:

According to the above principle, the bus capacitance is determined as 5500 μF, which is composed of six 3900 μF/450 V capacitors in series and parallel.

2.1.2. Calculation of Bus Capacitance Loss

The loss of capacitance consists of two parts: one is caused by equivalent series resistance(ESR), and the other part is caused by leakage current [12]. Since the leakage current loss is usually much smaller than the ESR loss, it can be ignored in the calculation.

The DC bus capacitor ripple current is [13]:

where M is the PWM modulation ratio, cosφ is the power factor, fc_rms is the pulse frequency, tc is the charging time of the DC bus capacitor, and tf is the discharge time of the DC bus capacitor.

The loss of bus capacitance is:

where EIr_Cdc is the equivalent ripple current flowing through the bus capacitor, ESRCdc is the ESR of the bus capacitor, Ir_Cdc is the ripple current flowing through the bus capacitor, and KFC is the frequency coefficient of the bus capacitor.

After three-phase rectification and filtering, the fundamental frequency of the current is six times the input frequency. For this system, the bus capacitance frequency coefficient KFC = 1.1 is calculated, and the loss of the bus capacitor is calculated as shown in Table 3.

Table 3.

Calculation results of bus capacitance loss.

2.1.3. Life Evaluation of Bus Capacitance

According to the technical documents of the Hitachi capacitor, considering the ripple current and ambient temperature, the capacitor life is estimated as:

where Lr is the service life of the bus capacitor at the rated ripple current and the highest operating temperature, T0 is the highest guaranteed temperature, T is the actual working temperature, ΔT0 is the allowable temperature rise of the capacitor center at the highest operating temperature, ΔT is the actual center temperature rise, K is acceleration factor of ripple current (K = 2 is the allowable range of ripple current, K = 4 is beyond the ripple current range).

where ELr is the equivalent ripple current flowing through the capacitor, Ir_C is rated ripple current at max working temperature, and Ir is the ripple current flowing through the capacitor.

According to the ambient temperature of the system, it is assumed that the operating temperature of the capacitor under rated load is 50 °C, and it is 60 °C under heavy load. The calculation results of the bus capacitor life are shown in Table 3.

According to the data analysis in Table 3, it can be seen that under load, the loss of single bus capacitance and total bus capacitance is the highest, and under overload, the service life of the capacitor bus is the shortest.

2.2. DC Reactor Design

2.2.1. Color/Grayscale Figures

The DC reactor is connected before the bus capacitor, as shown in Figure 1. The main function of the DC reactor is to improve the input current distortion caused by the capacitor filtering, improve the power factor, and reduce and prevent the rectifier bridge damage and capacitor overheating caused by the inrush current.

The inductance value of the DC reactor should not be too large or too small. An excessively large induction value will cause a large voltage drop on the reactor, resulting in a low DC bus voltage. In a variable frequency speed control system with a constant power load, instability will occur. The too-small inductance will cause excessive ripple current to flow through the bus capacitor, causing greater loss, affecting the service life of the capacitor, and also causing too-high Total Harmonic Distortion (THD) and reducing the power factor of the system.

In this paper, the upper limit of the inductance value is determined by ensuring the system stability and the voltage on the reactor is not large, and the lower limit of the inductive value is determined by ensuring the life of the bus capacitor. By using the small signal analysis method, the characteristic Equation of the circuit transfer function can be deduced as follows:

where Rdc is the DC equivalent resistance on the rectifier filter circuit, Ldc is DC inductance, and is the average value of DC bus voltage.

is the average value of voltage after rectification. The results are as follows:

In general:

According to Equation (20), to ensure the system’s stability, it shall meet the following requirements:

According to experience, the value of a DC reactor generally does not exceed three times the 3% impedance inductance of the same inverter input AC reactor. Considering the overload, taking the DC equivalent resistance RDC = 0.04 Ω, and calculating Equation (25), the upper limit of the inductance value of the DC reactor can be obtained, as shown in Table 4.

Table 4.

The upper limit of the inductance value of the DC reactor.

The longevity of an electrolytic capacitor predominantly relies upon the rated lifespan of the capacitor itself, the ambient temperature to which it is exposed, and the magnitude of ripple current traversing through it. Additionally, the inductor within the circuit significantly impacts the amplitude of the ripple current flowing through the bus capacitor. Consequently, ensuring a specific inductance value becomes imperative to attain the desired operational lifespan of the bus capacitor, thereby averting premature failures.

When the design life L is known, the maximum ripple current that the capacitor can withstand can reach Equation (26), and the minimum inductance of the DC reactor can be determined according to the maximum ripple current.

The circuit model, shown in Figure 1, corresponds to a nonlinear second-order differential equation, which is difficult to solve, and it is impossible to determine the initial values of the variables in the steady state of the circuit. This paper uses the constant step Euler algorithm to simulate the circuit. Finally, average voltage, peak-to-peak ripple voltage, root mean square (RMS) voltage, ripple current of the bus capacitor, and RMS current, average current, and ripple current of the DC reactance can be acquired.

In the simulation calculation process, since the sampling period is much shorter than the operating period of the circuit, the rectified voltage can be approximated as a constant voltage source within a sampling period, and the load is approximated as a resistance, which can not only greatly simplifies the mathematical model of the circuit, but also does not have much impact on the calculation results.

Thus, the circuit model can be expressed as:

where IL is the current flowing through the DC reactor, is load equivalent resistance, and Vrec is the equivalent voltage after rectification.

To solve the system of differential equations, acquire:

When LDC is known, the simulation calculation can be carried out by Equation (28) and Equation (29), and the VC and IL of each transient can be acquired, and then calculating the required voltage and current data. If using dichotomy to find LDC in the range of [0, LDC_Max], which is in accordance with the calculation result of Equation (29), the lower limit LDC_Min of the inductance value of the DC reactor is received. Considering the rated load, the lower limit of the inductance value of the DC reactor can be calculated according to the above method, as shown in Table 5.

where C1~C7 are all constants, and:

Table 5.

The lower limit of inductance value of the DC reactor.

It can be seen from Table 5 that in the case of 200% overload in heavy load application, the lower limit value of LDC still cannot meet the life requirement of bus capacitor, but the time of 200% overload in heavy load application is very short and can be ignored. According to the real situation, the inductance value of a DC reactor is 230 μH.

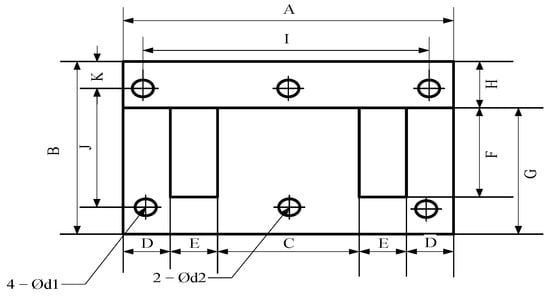

2.2.2. Electromagnetic Design of DC Reactor

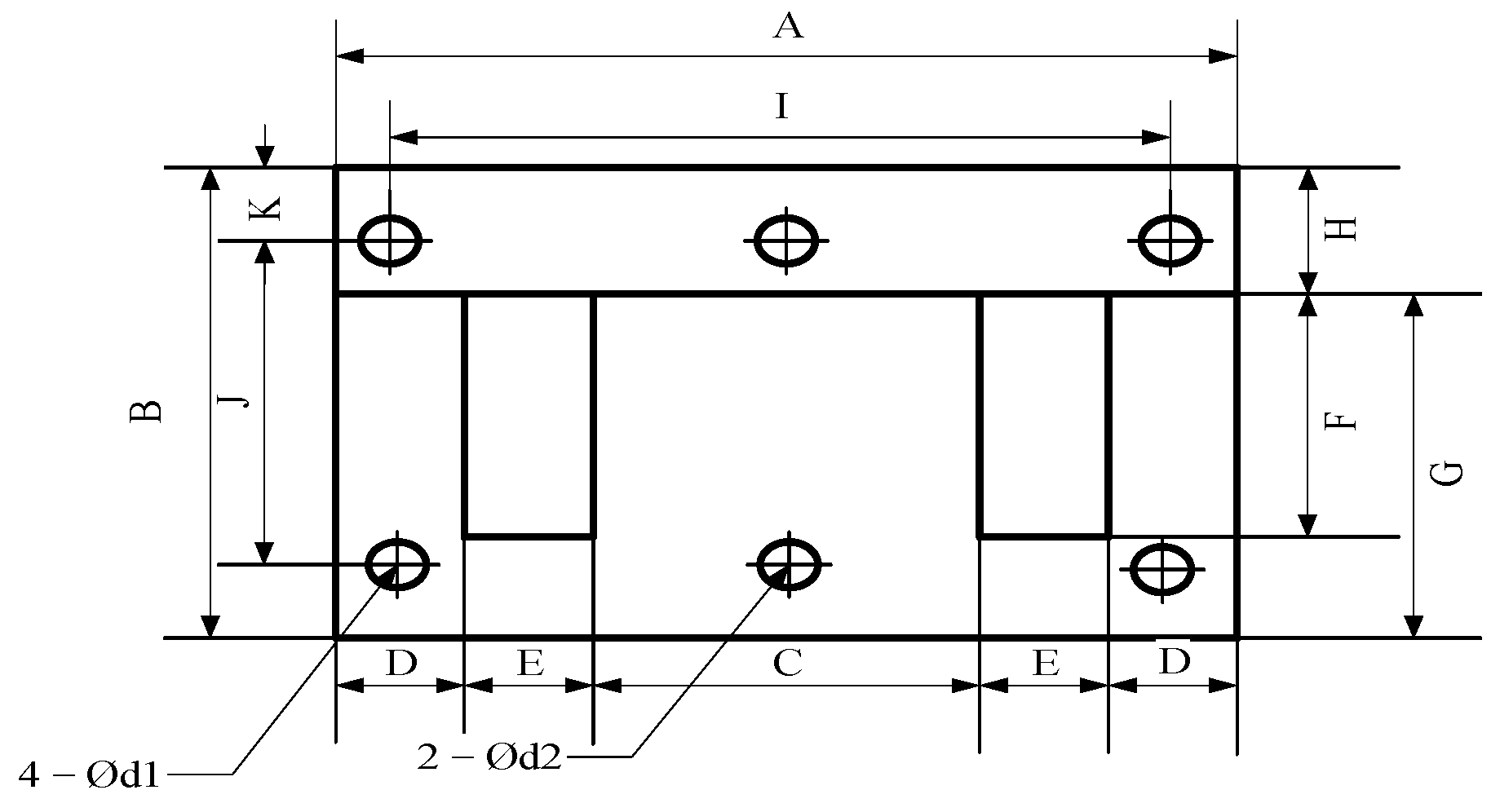

According to the actual situation, the silicon steel sheet 35Z155 of Nippon Steel Co., Ltd., Tokyo, Japan. is selected as the core material of the reactor, and EI type core of EI133.2 is selected, as shown in Figure 4, and core parameters are shown in Table 6.

Figure 4.

EI-type core structure.

Table 6.

Size parameters of reactor core.

According to the requirements of reactor inductance and current, 220 silicon steel sheets are used to form the EI core. The thickness of the core is:

According to Equation (30), the core thickness of the DC reactor is T = 77 mm, the core size of the DC reactor is 133.2 mm × 111 mm × 77 mm, and the relevant parameters of the core can be calculated as follows: Ae = 3.4188 × 103 mm2; Le = 266.4 mm; Ve = 9.1077 × 105 mm3; ACW = 1.4785 × 103 mm2; Wt = 6.9674 kg; PCL = 10.1724 W (50 Hz, 1.7 T).

According to the law of ampere and flux:

where Ipeak is the peak current under rated load, and Bm is the max working flux density.

Take Bm = 1.4 T, and calculate Equation (31) to obtain the number of turns of DC reactor winding Nturns = 8. The calculated length of the air gap is:

where Ag is the cross-sectional area of the magnetic circuit considering the air gap, and μe is the permeability of the core material, which can usually be calculated from the B = f(H) curve of the core material.

When the air gap is large, the edge magnetic flux cannot be ignored. The cross-sectional area of the magnetic circuit considering the edge magnetic flux is:

where lg is the length of the air gap, and m is the width of edge flux diffusion.

Perform iterative operation on Equations (32) and 33), making Ag = Ae, calculating lg using Equation (32), and then substitute the calculated lg into Equation (33) to obtain a new Ag, then substitute the new Ag into Equation (32), to cycle until lg no longer has a big change, then calculate the air gap length that the reactor needs. If m = lg and calculated according to the above algorithm, the air gap length of DC reactor lg = 2.6 mm can be acquired.

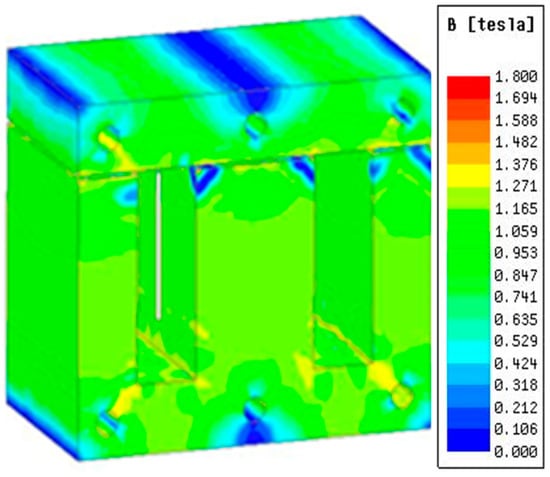

Core saturation verification using Equation (34):

When Imax = 386 A, the maximum operating flux density of the core Bmax = 1.6188 T. When the current reaches the maximum value, the inductance will drop, but it can meet the design requirements.

According to the set current density, the current-carrying area required by the copper wire can be calculated as follows:

where Sturns is the current-carrying area required for single-turn copper wire, and J is the current density.

Take J = 3.57 A/mm2, calculate Equation (35), and obtain the current-carrying area required for turning copper wire Sturns = 71.4297 mm2.

Therefore, according to the actual situation, 60 mm × 0.3 mm copper foil is selected for winding the reactor. When using four layers of copper foil for a single turn, the current density can meet the requirements. The current density is 3.47227 A/mm2.

The formula for calculating the window occupancy rate is

Calculate Equation (36), KCW = 0.3896.

In summary, considering the thickness of the core, insulation layer, and wire package, it can be estimated that the size of the DC reactor is approximately 133.2 mm × 111 mm × 101.6 mm.

The loss of the DC reactor is composed of copper loss and iron loss. Copper loss refers to the loss of current through the copper wire, and iron loss refers to the loss in the iron core. This relationship can be expressed as:

where PCu is the copper consumption of the DC reactor, and PFe is the iron consumption of the DC reactor.

The series equivalent resistance of the DC reactor is:

where is the resistivity of copper wire and MLT is the average length of winding.

The copper consumption of the DC reactor is:

The iron consumption of the DC reactor is:

where f is the frequency of the ripple current flowing through the DC reactor, BAC is the AC magnetic flux density, Kf is the frequency coefficient, and KB is the magnetic flux density coefficient.

Among them, the AC flux density is:

where Kf and KB can be calculated based on the data provided in the core material specifications. For 35Z155, the frequency coefficient Kf = 1.5067, and the magnetic flux density coefficient KB = 2.8969.

For a three-phase uncontrolled rectifier circuit, ripple current frequency f = 300 Hz.

Equations (37)–(41) can be used to acquire the equivalent series resistance and loss of each part of the DC reactor, as shown in Table 7.

Table 7.

Equivalent series resistance and loss of each part of the DC reactor.

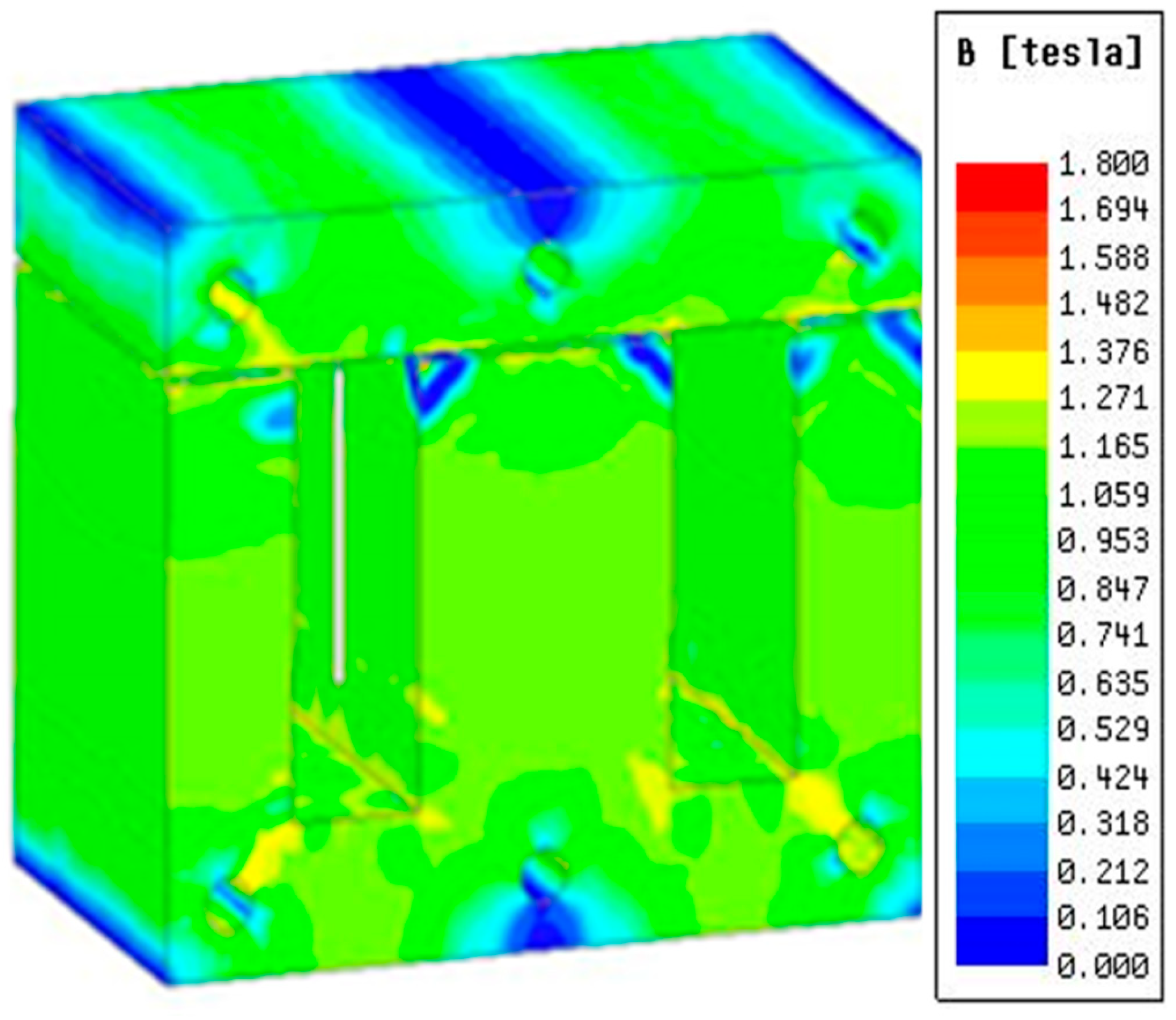

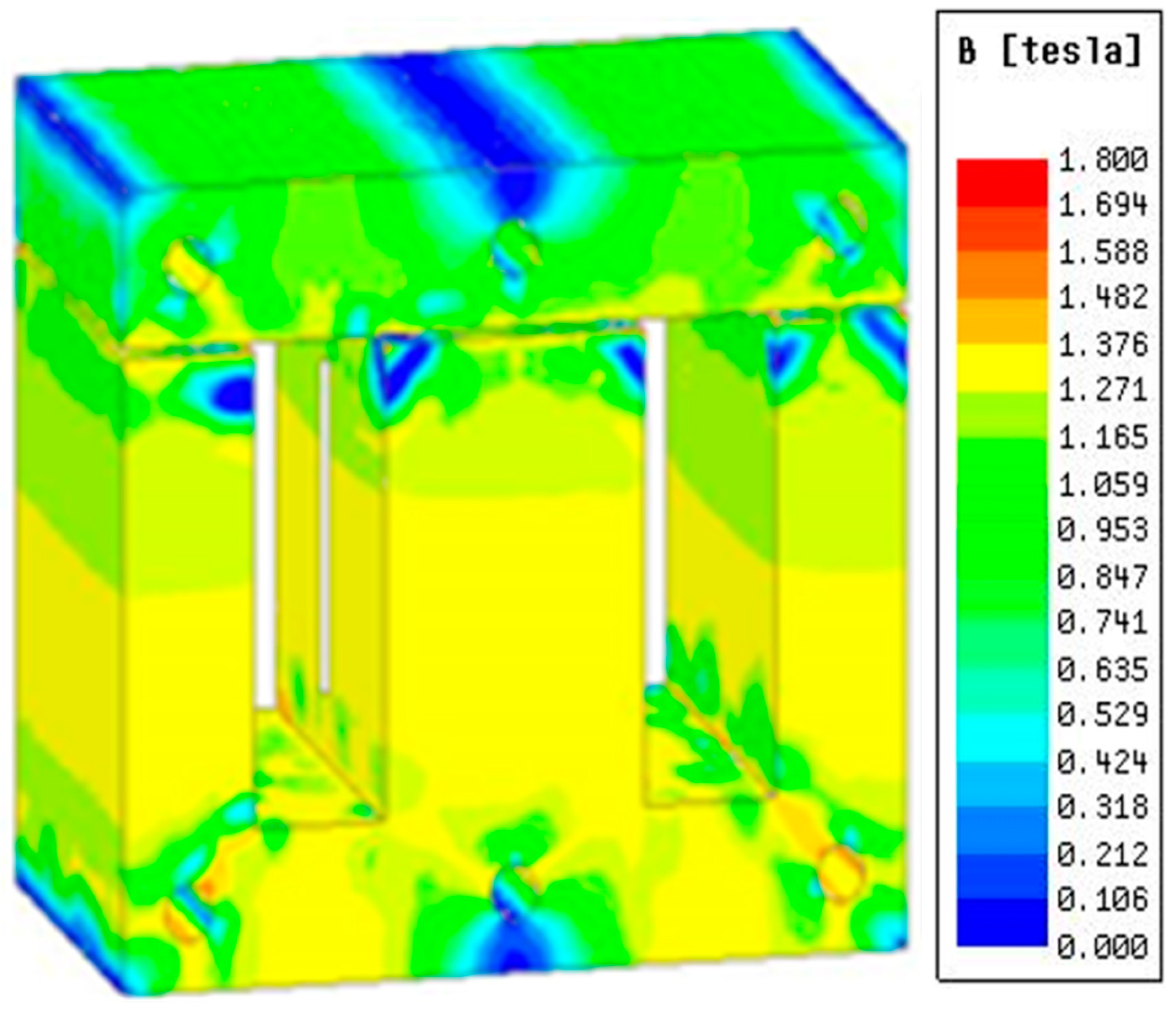

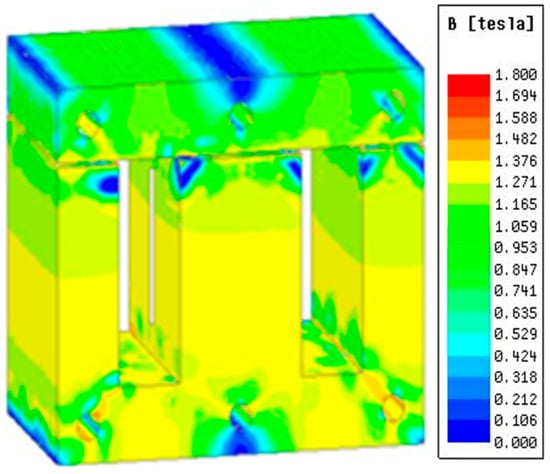

The magnetic flux density distribution of the DC reactor under rated load current is shown in Figure 5. The magnetic flux density distribution of the DC reactor under overload conditions is shown in Figure 6.

Figure 5.

Flux density under rated load.

Figure 6.

Flux density under overload.

3. Simulation Analysis of Bus Capacitance and DC Reactor under Normal Conditions

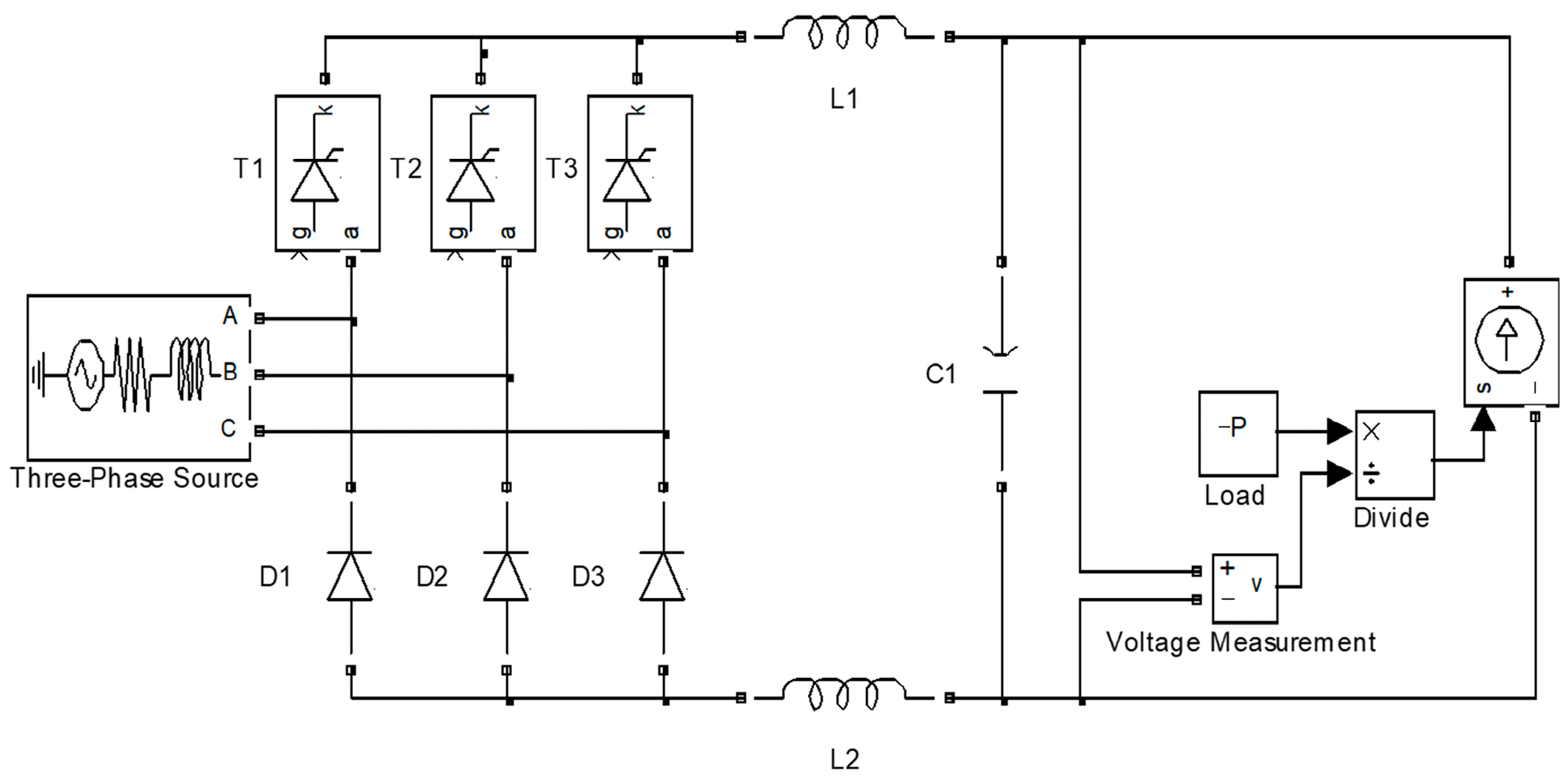

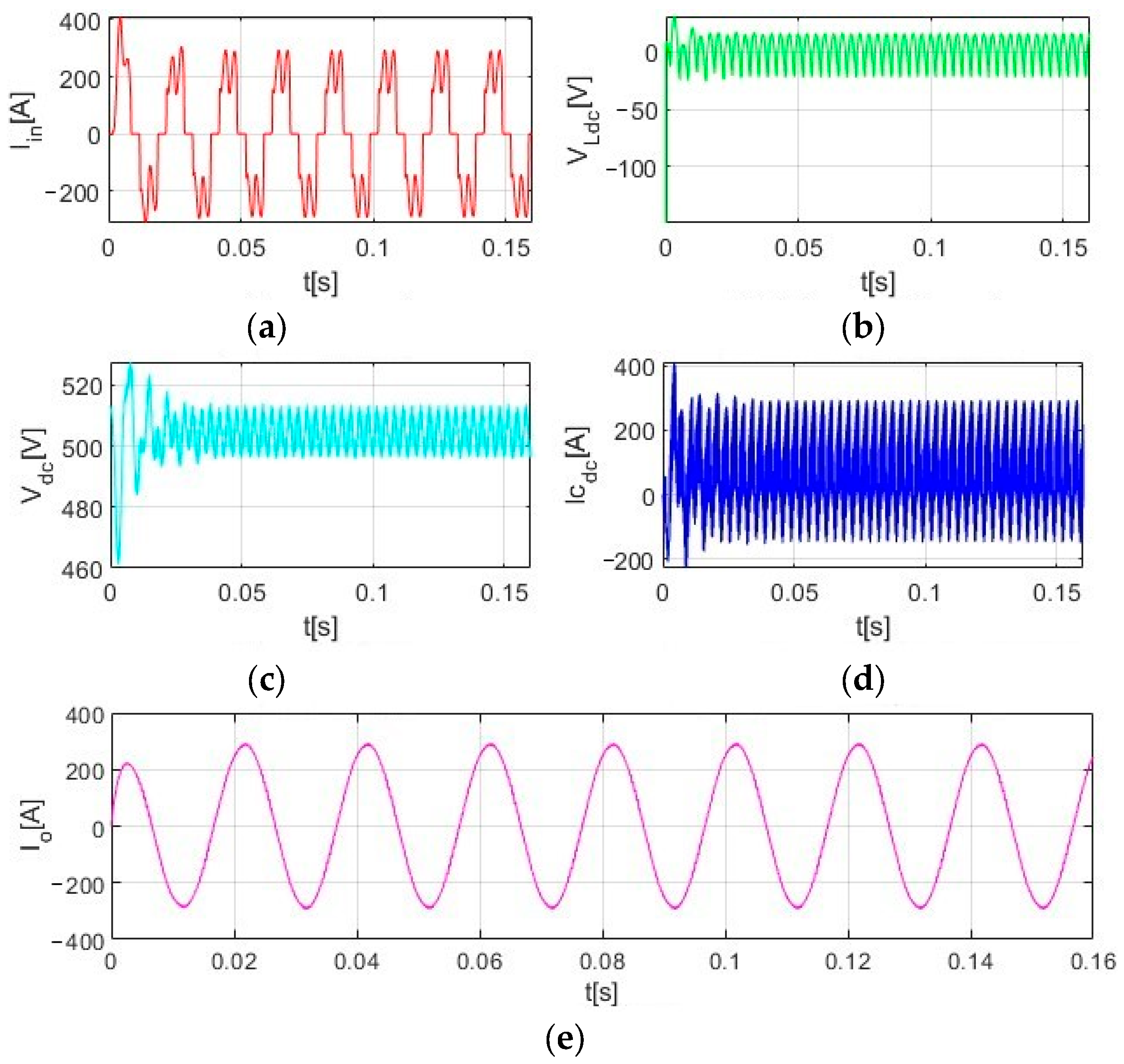

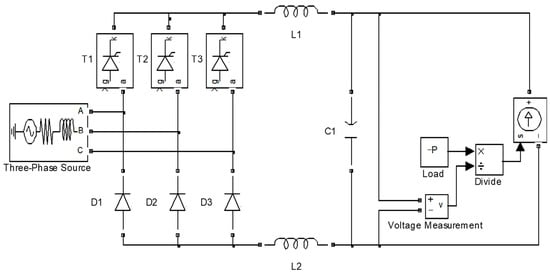

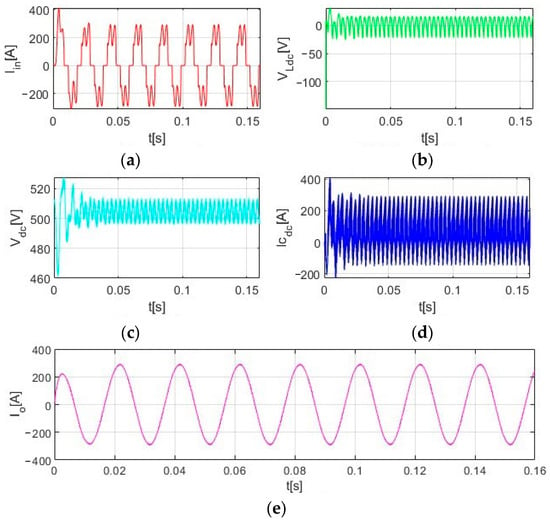

Figure 7 shows the simulation block diagram of the inverter LC system based on MATLAB/Simulink software. It mainly includes an equivalent power transformer, rectifier circuit, LC filter circuit, load, etc. In this paper, the simulation switching frequency is 5 kHz. Figure 8 shows the bus voltage waveform. Figure 9 shows the ripple current waveform of bus capacitance. Figure 10 shows the output current waveform of the frequency converter.

Figure 7.

Simulation block diagram of inverter LC system.

Figure 8.

Output current waveform. (a) Input current; (b) Voltage of DC reactor; (c) Bus voltage; (d) Ripple current of bus capacitor; (e) Output current.

Figure 9.

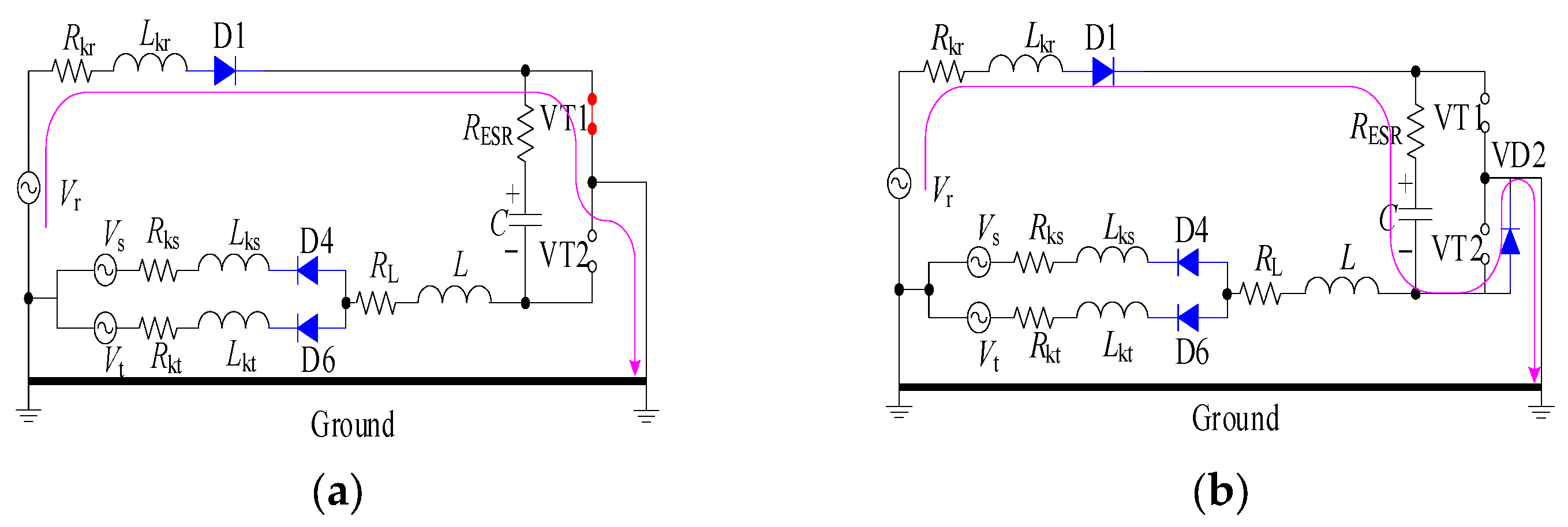

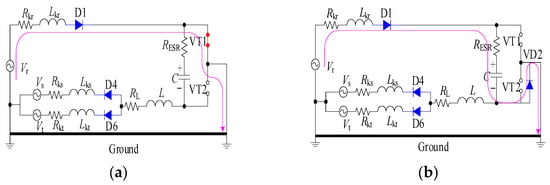

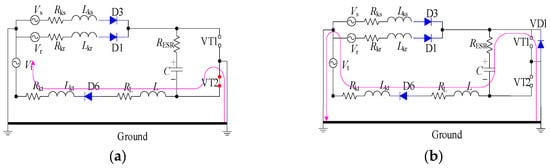

Energy transmission of VT1 turns on and turns off. (a) The equivalent circuit of VT1 turns on; (b) The equivalent circuit of VT1 turns off.

Figure 10.

Energy transmission of VT2 turns on and turns off. (a) The equivalent circuit of VT2 turns on; (b) The equivalent circuit of VT2 turns off.

According to Figure 8, it can be seen that the selection of system bus capacitance and DC reactor is reasonable, the output current waveform is stable, and the correctness of the proposed scheme is verified.

Further analysis: without adding a reactor, considering the influence of a power transformer, when a phase-to-ground short circuit occurs (for instance, phase K is closed, phase W to ground short circuit), it is possible to explore the machine. The energy transmission mode when a phase-to-ground short circuit occurs in the frequency control device is analyzed.

3.1. DC Bus Capacitance Design

In instances where a ground short circuit (K1 closed) arises, and the output current assumes a positive direction, an isolated circuit is configured, comprising the maximum phase voltage Vr, along with its corresponding diodes D1, VT1, VD2, and capacitor C.

Figure 9 shows a diagram of the VT1 rotor with energy transfer at shutdown.

Upon the activation of VT1, the Lkr voltage is charged from the power supply, subsequently leading to a rise in output current. Conversely, upon the deactivation of VT1, an instantaneous change occurs in the Lkr current, wherein the unobstructed circuit path encompasses D1, C, and VD2. During this phase, C charges, resulting in an augmentation of the bus voltage.

3.2. VT2 Turns On and Off Energy Transmission Modes

Figure 10 depicts energy transfer modes when VT2 is alternately switched on and off.

Upon the current of Lkr attaining a decrease to 0, a boost circuit is formed, comprising the lowest phase voltage Vr, the leakage inductance Lkt, along with the corresponding diode D6, DC reactor L, VT2, VD1, and capacitor C. When VT2 is switched on, Vt, Lkt, D6, L, and VT2 form a circuit, Lkt is charged from the supply, and the output current is reversed. When VT2 is switched off, the current L, Lkt is not immediately switched, the current is frozen by D6, C, and VD1 is charged, and the voltage of the bus is increased.

4. Simulation of Single-Phase Earthing Short Circuit Scenarios for Inverters

The incorporation of a DC reactor preceding the bus capacitor serves as a primary measure to ameliorate the adverse effects induced by abnormal fluctuations in the capacitor filter input current. This arrangement aims to enhance power factor, mitigate the potential hazards of rectifier bridge damage, and prevent overheating of the capacitor caused by inrush currents. There are generally two structures: one is to connect a DC reactor in series with the cathode of the DC bus, and the other is to connect a DC reactor in series with the anode.

4.1. A DC Reactor on the Cathode of the DC Bus

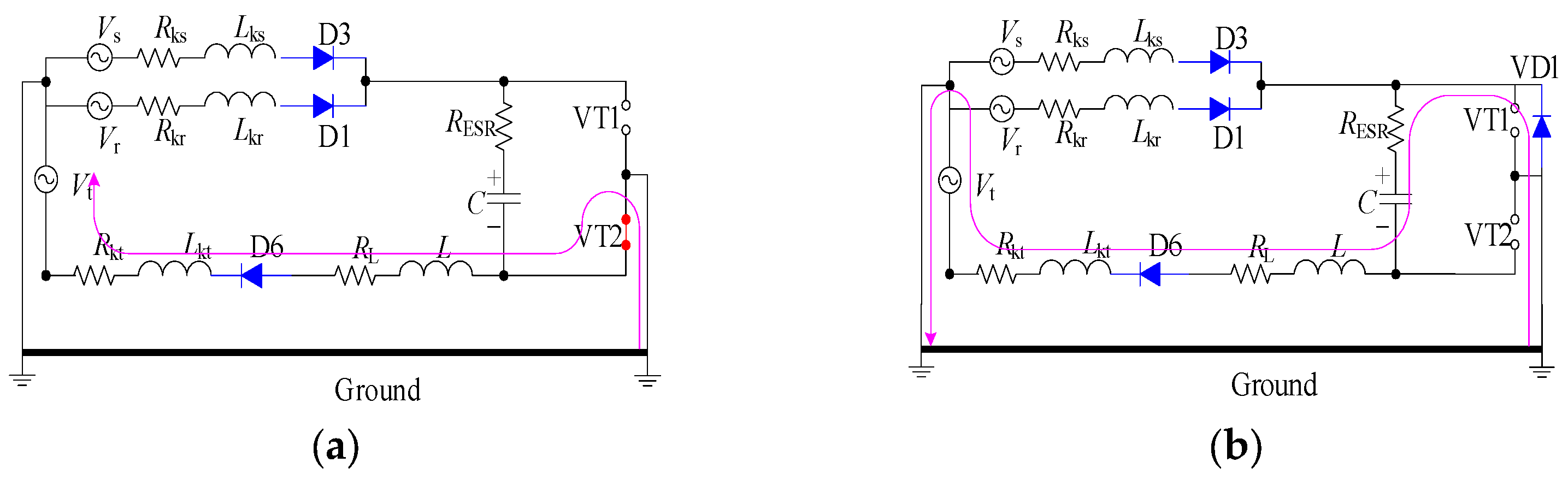

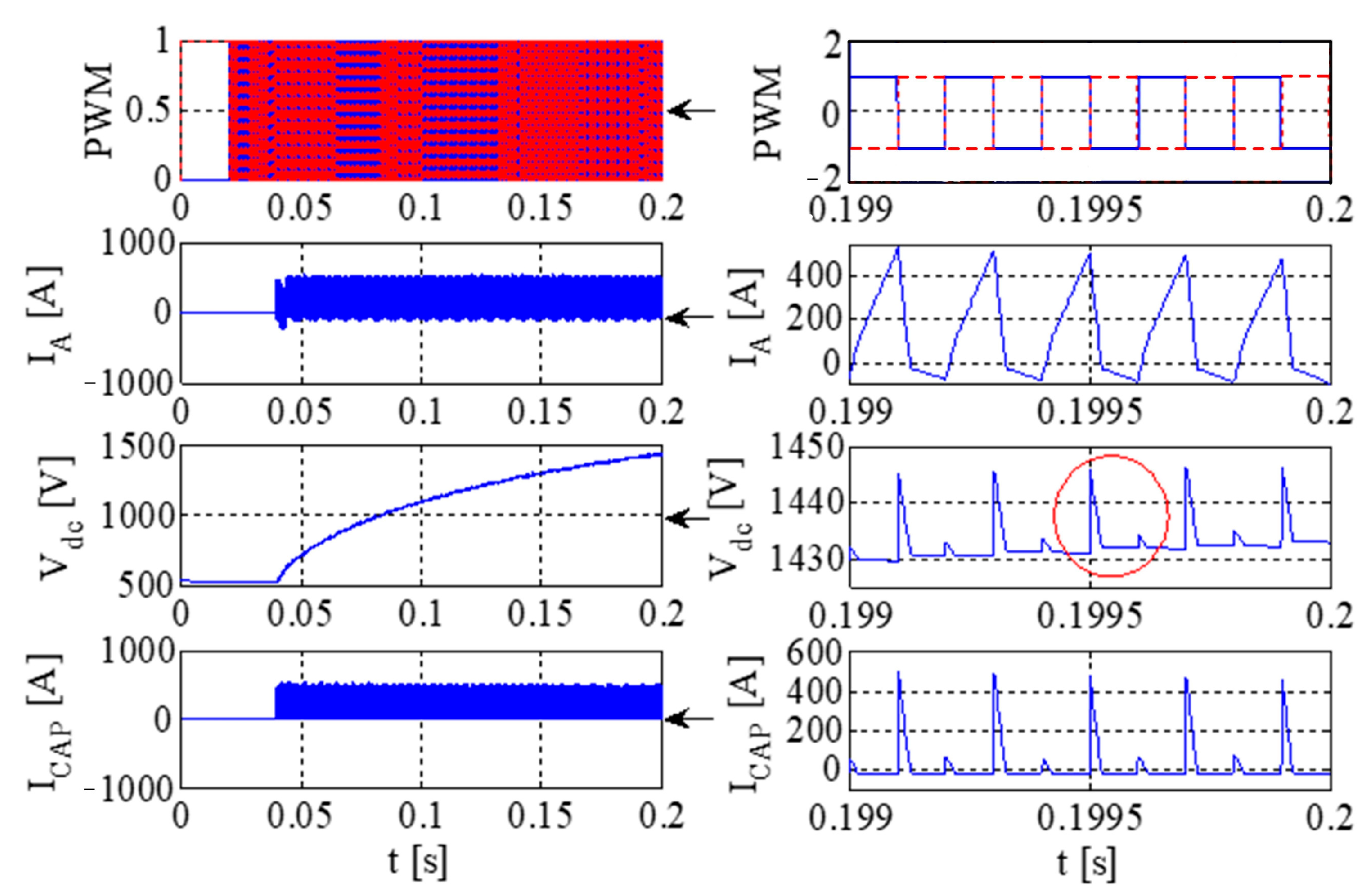

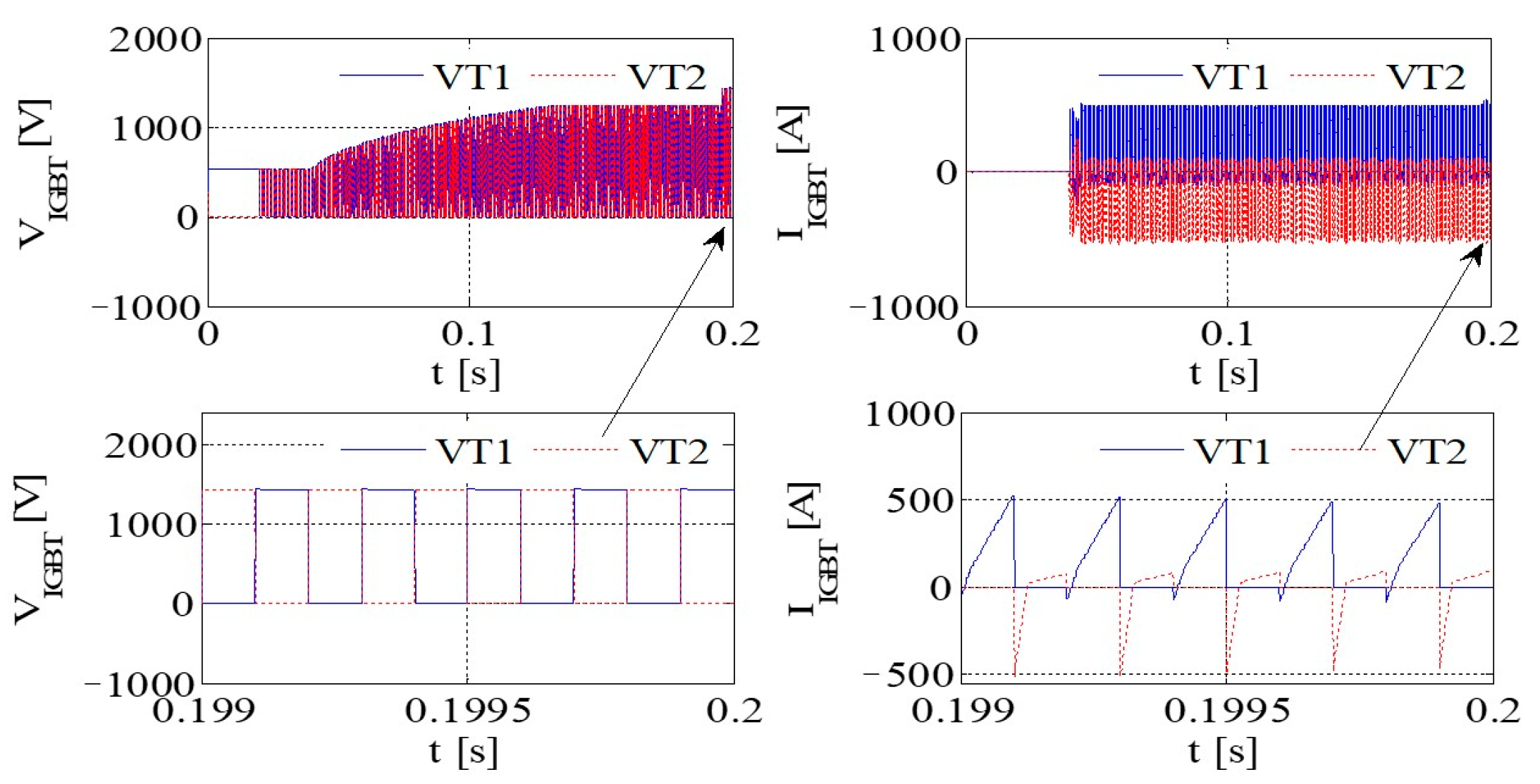

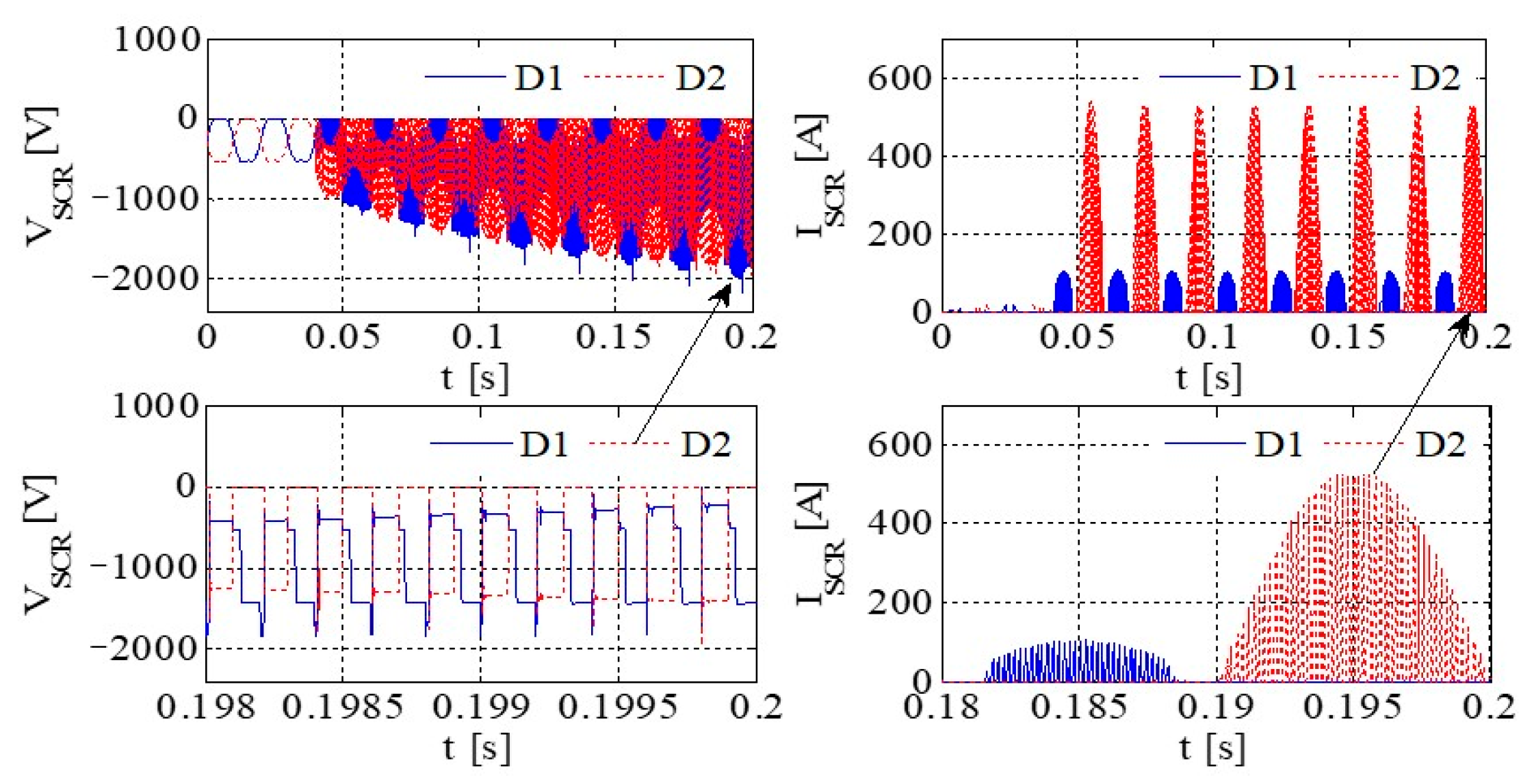

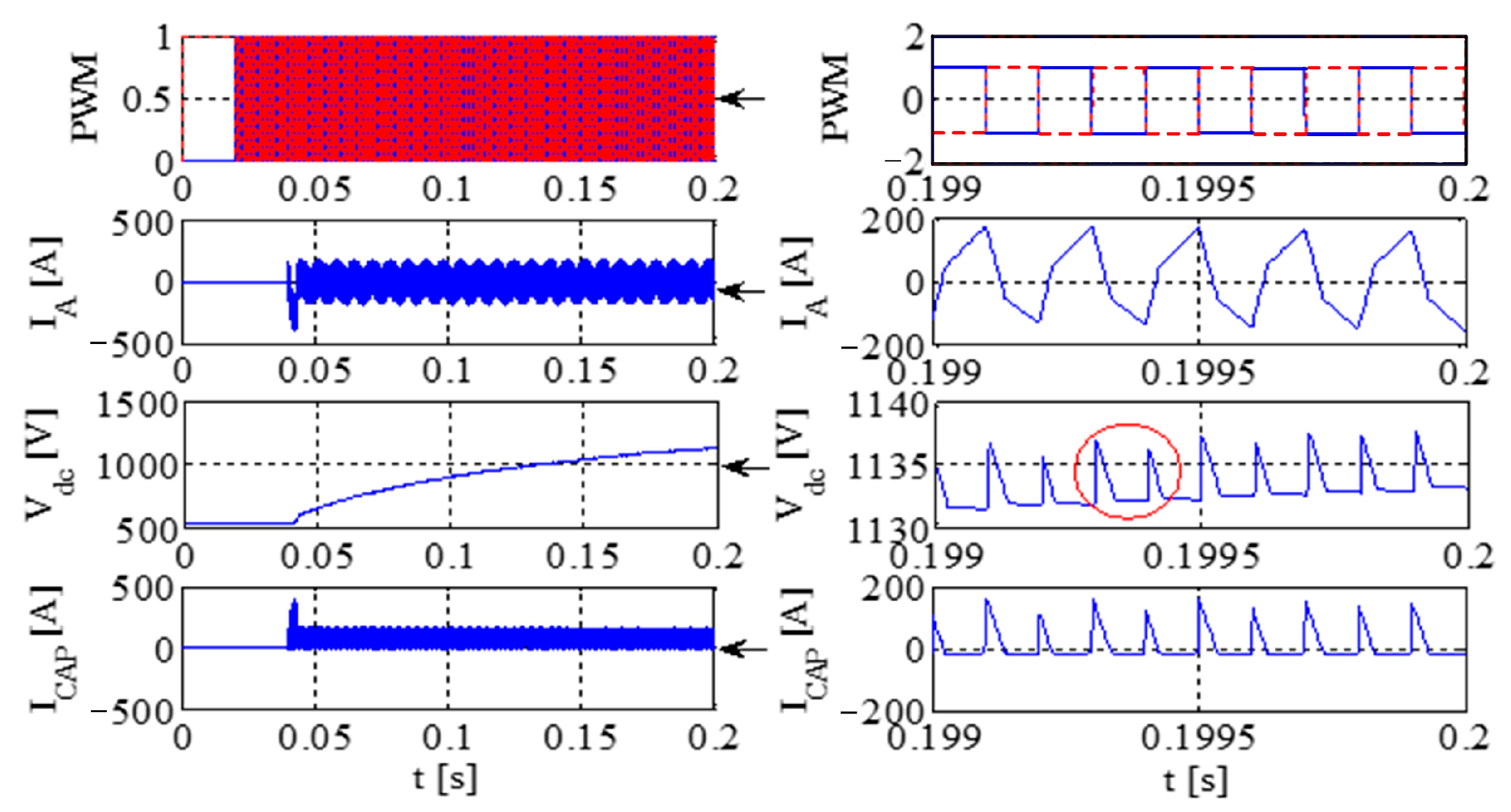

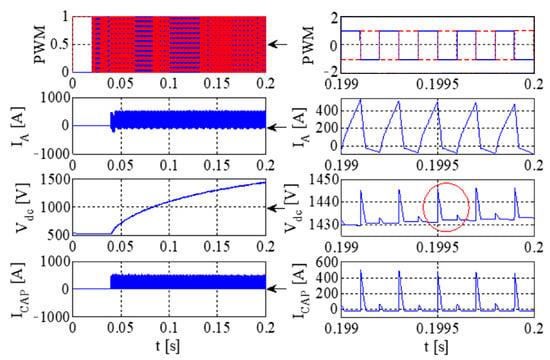

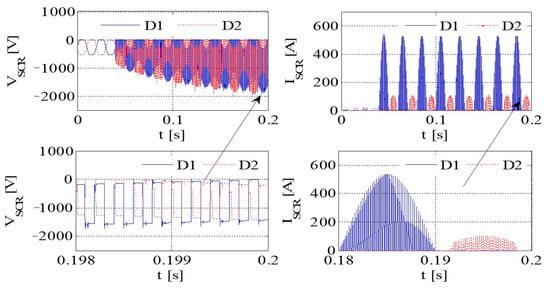

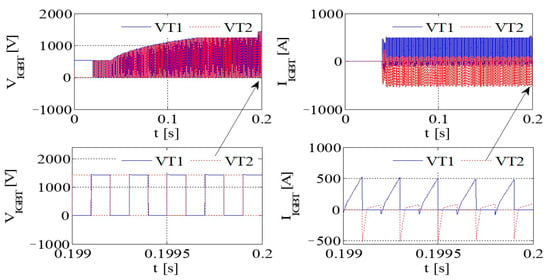

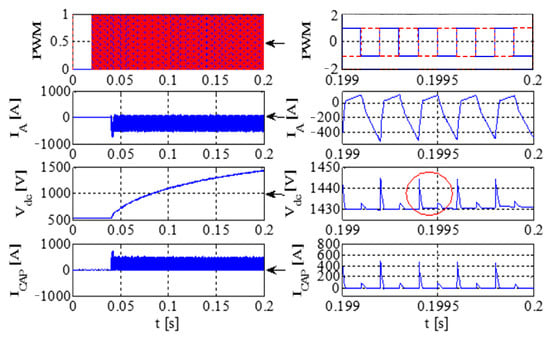

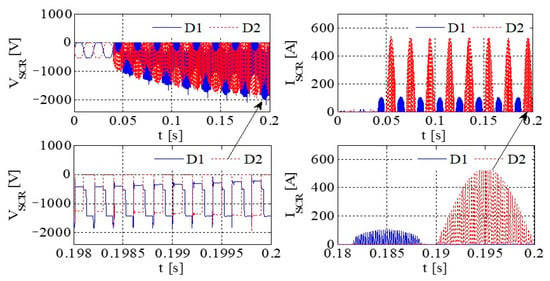

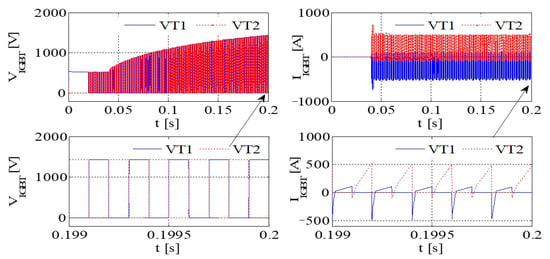

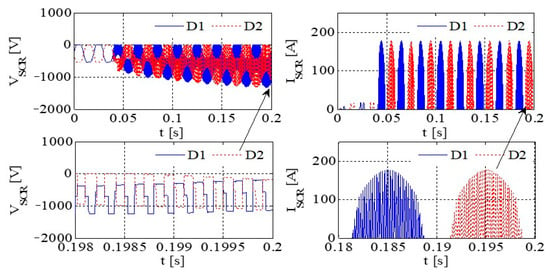

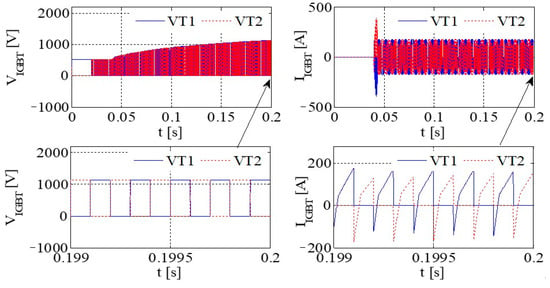

Figure 11 illustrates the PWM waveform, output current, DC bus voltage wave, and capacitance current wave of the IGBT. Additionally, Figure 12 presents the output voltage and output current characteristics of the bridge arm on the rectifier. Furthermore, Figure 13 depicts the output voltage and current behaviors of the IGBT bridge arm.

Figure 11.

The PWM waveform, output current, DC bus voltage waveform, and capacitor current waveform of IGBT.

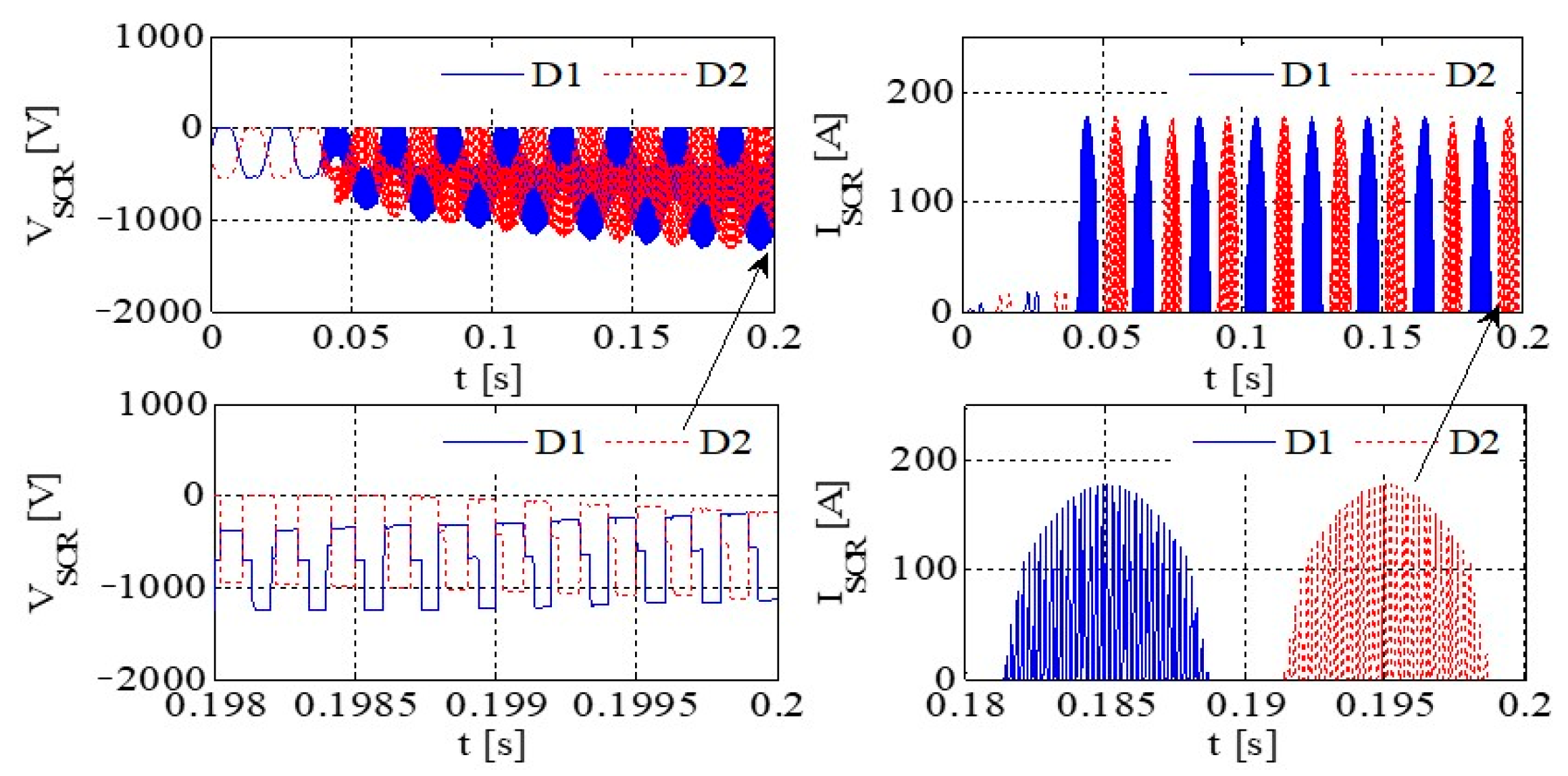

Figure 12.

The output voltage and output current of a bridge arm of the rectifier.

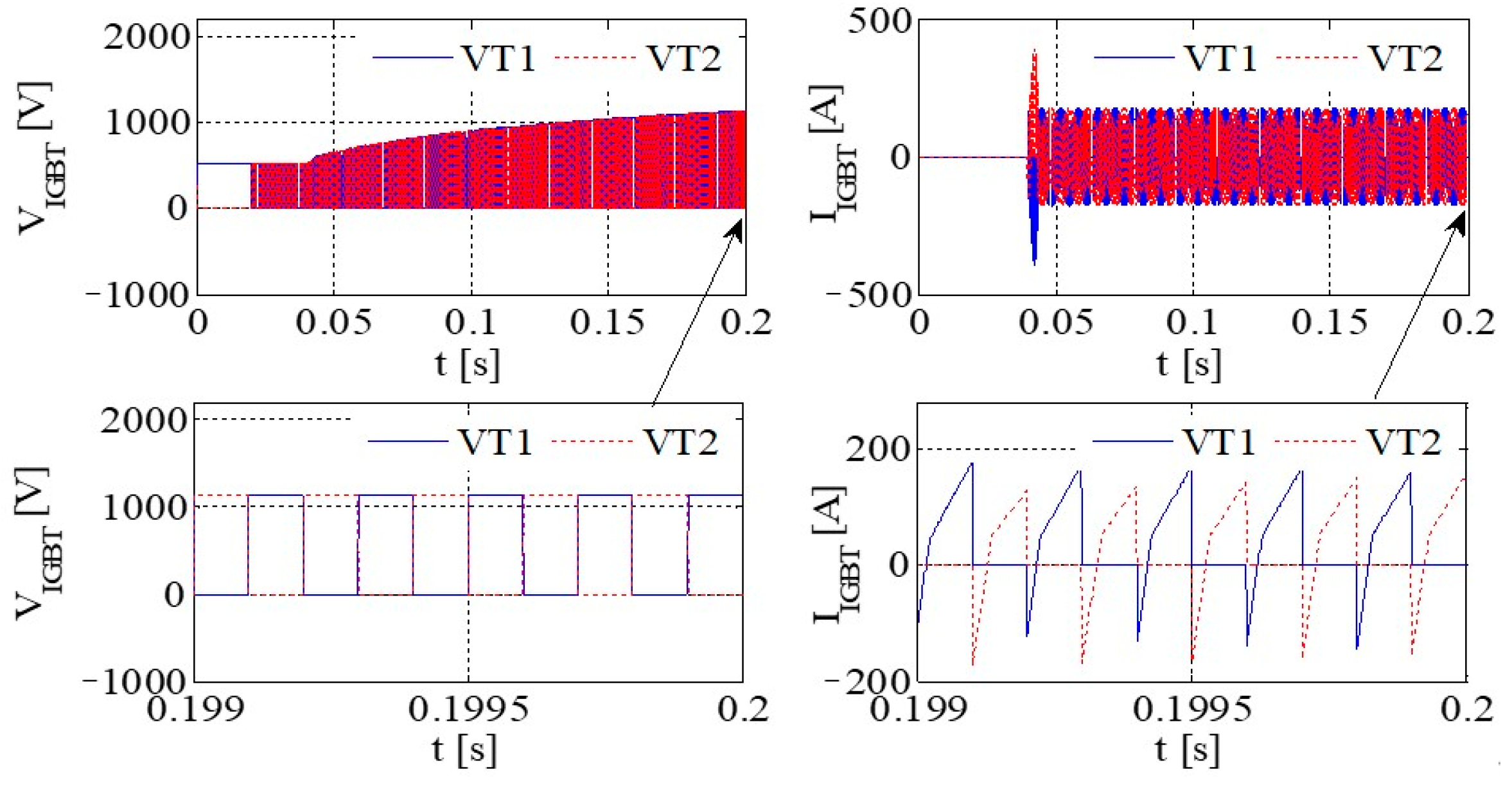

Figure 13.

The output voltage and current of an IGBT bridge arm on IGBT.

Upon the occurrence of an earthing short circuit in the inverter system, there is an evident rise in the currents IA and ICAP, along with a corresponding increase in the DC bus voltage, denoted as Vdc. The voltage Vdc exhibits a transient behavior characterized by abrupt ascents and descents, a phenomenon attributed to the ESR of the capacitor.

Because of the way it transmits the earth’s short circuit, the rectifier will not work properly under the condition of earthing. When some diodes turn on, the Corresponding diode turns off. When D6 and VT2 are turned on, Vt < Vr and Vt < Vs, the capacitor is the same as the capacitor and ground, so VD3 = −Vt + Vdc. Actually, due to parasitic effects, the situation becomes much more serious.

The output voltage and the current in the AC–DC converter are high, so IGBT is easily destroyed due to overheating.

4.2. A DC Reactor on the Anode of the DC Bus

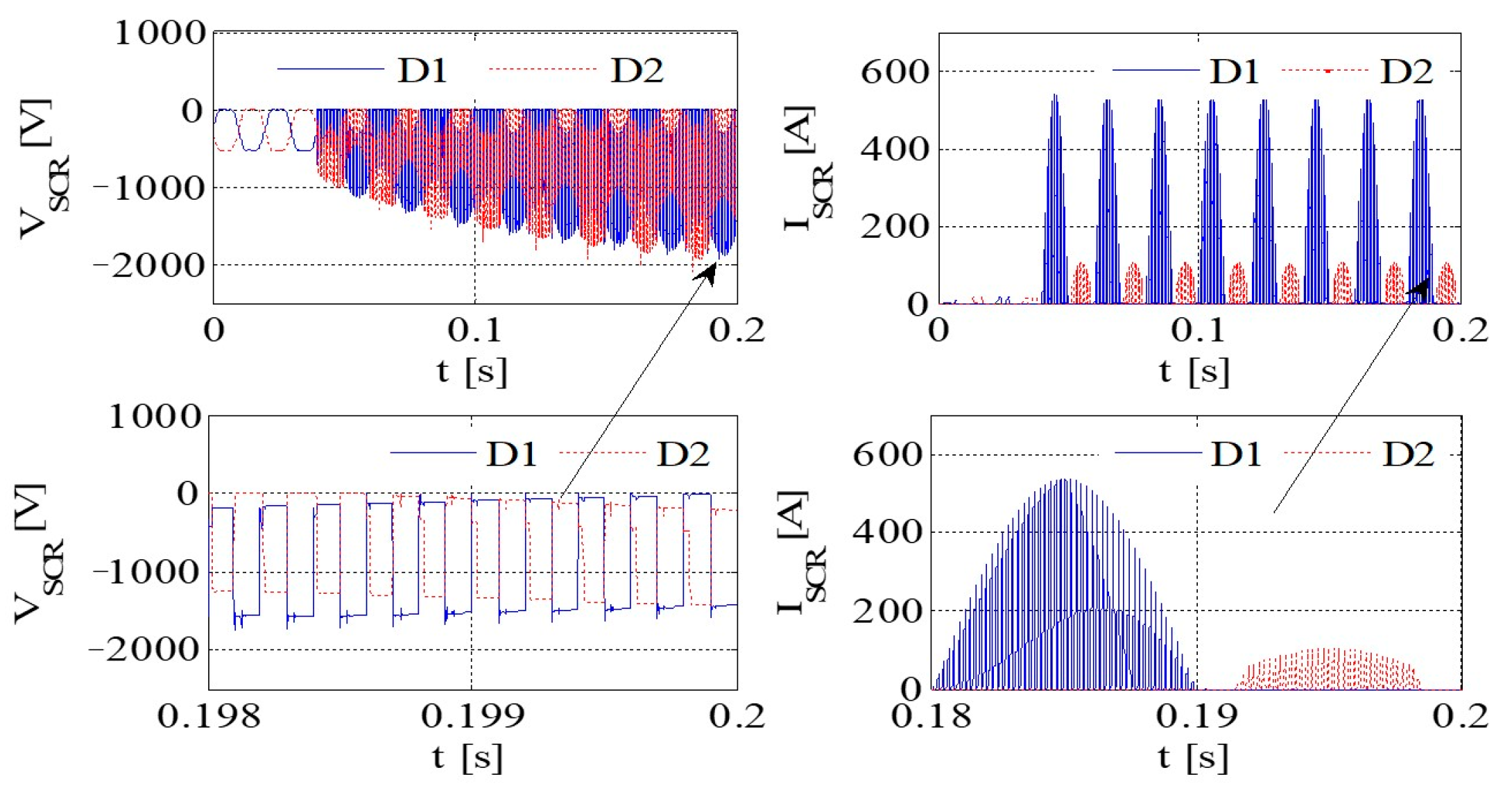

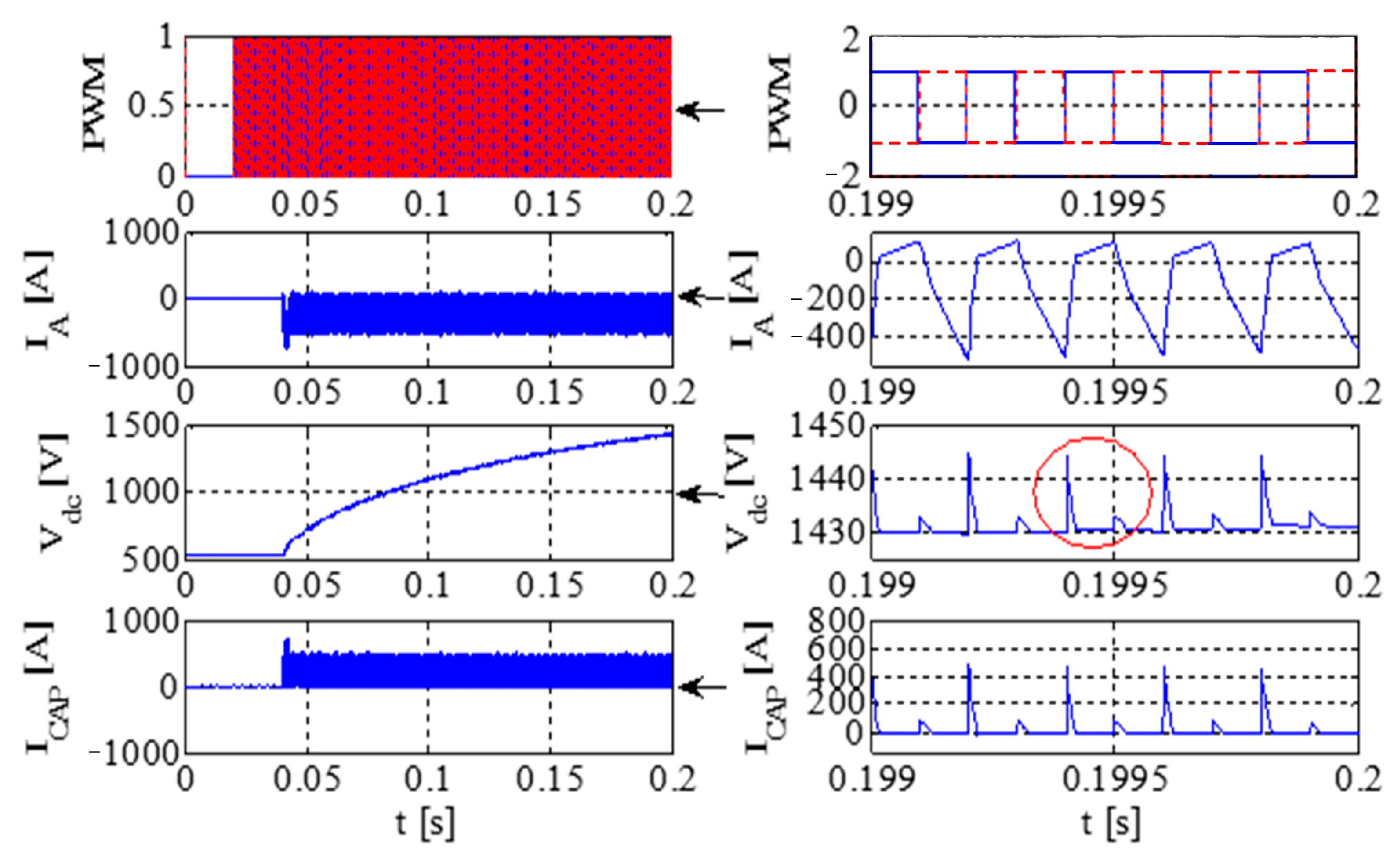

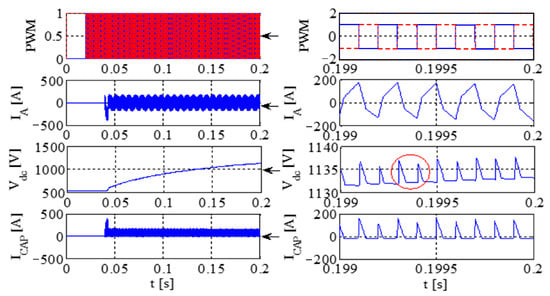

Figure 14 presents graphical representations of the PWM waveform, the output current, the DC bus voltage wave, and the capacitance current wave associated with the IGBT. Subsequently, Figure 15 provides an illustrative depiction of the output voltage and output current characteristics exhibited by the bridge arm within the rectifier. Furthermore, Figure 16 offers a detailed account of the output voltage and current attributes of the IGBT bridge arm.

Figure 14.

IGBT PWM waveform, output current, DC bus voltage waveform, and capacitor current waveform.

Figure 15.

The voltage and current at the output of a rectifier bridge arm.

Figure 16.

The voltage and current at the output of an IGBT bridge arm.

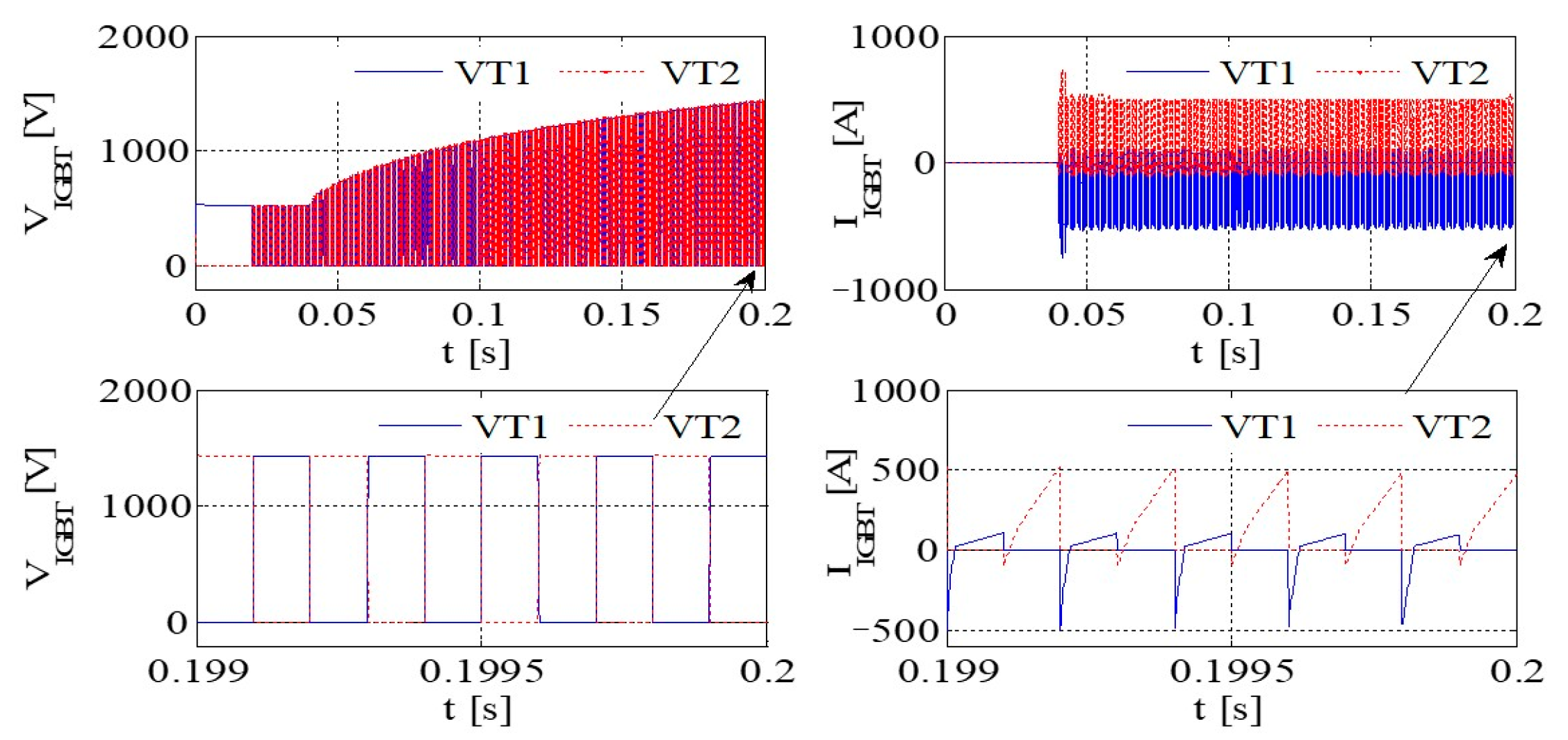

4.3. A DC Reactor on the Anode and Cathode of the DC Bus

Figure 17 depicts the PWM waveform of the IGBT, the output current, the DC bus, and the capacitor current. Similarly, Figure 18 showcases the output voltage and output current characteristics of an abridge arm on a rectifier. Furthermore, Figure 19 presents the output voltage and current behaviors specific to the IGBT bridge arm.

Figure 17.

The PWM waveform of an IGBT, the output current, the DC bus voltage waveform, and the capacitor current waveform.

Figure 18.

The output voltage and current of a bridge arm on rectifier.

Figure 19.

The output voltage and current of a bridge arm on IGBT.

If, by the depictions in Figure 11, Figure 14 and Figure 17, the original reactor’s value is halved and symmetrically positioned on the positive and negative DC buses, a more equilibrated distribution of current through the devices is achieved, thereby contributing to an enhanced operational state.

Simulation results for each type of inverter are given in Table 8. If the DC inductor is divided into two reactors with the same value, one on the positive bus and the other on the negative bus, it can have a better common mode filtering effect and improve EMC performance. When the output of the system is short-circuited to the ground, since there are reactors on the positive and negative bus bars, it can evenly protect the up and downpipes of the rectifier bridge and enhance the reliability of the system. Thus, the DC inductor of this system is designed as two reactors of 115 A/250 μH, which are, respectively, placed in the positive and negative buses.

Table 8.

Simulation results of different inverter topologies.

5. Design of Rectifying Diode

When the output of the inverter is short-circuited to the ground, and the bus voltage rises, the reverse voltage drop that the rectifier may bear is:

Therefore, the reverse repetitive peak voltage VRRM of the rectifier should be higher than the calculation result of Equation (42), and there shall be a margin to obtain:

Considering the maximum bus voltage of the frequency converter and the maximum input grid voltage, according to Equation (43), the minimum repetitive peak reverse voltage VRRM_Rec of the rectifier is 1349.1 V. The average current flowing through each rectifier is:

The RMS current flowing through each rectifier is:

Additionally, the rectifier diode should meet the following requirements:

Table 9 is the effective average current and rated effective current of the rectifier diode calculated by the formula Equations (44)–(47).

Table 9.

The effective average current and rated effective current of the rectifier.

Based on the above, this system uses the thyristor diode module of Infineon model TD180N16KOF as the rectifier of the machine, which is composed of three modules.

Thus, in future design, the impact of short-circuit to ground should be considered. The rectifier module should be a module with a withstand voltage of more than 1600 V (the voltage level of the currently selected module is 1600 V), and the diode in series with the soft starting resistor should also select the diode with a voltage of more than 1600 V (the voltage level of the currently selected diode is 1000 V). If possible, the DC reactor should be designed as a double wound Group, one for each positive and negative bus.

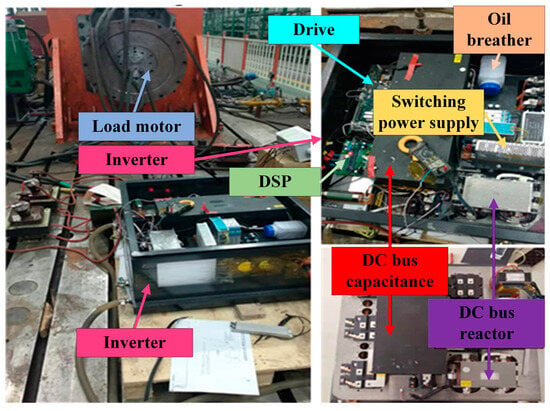

6. Inverter Single-Phase Ground Short Circuit Experiment

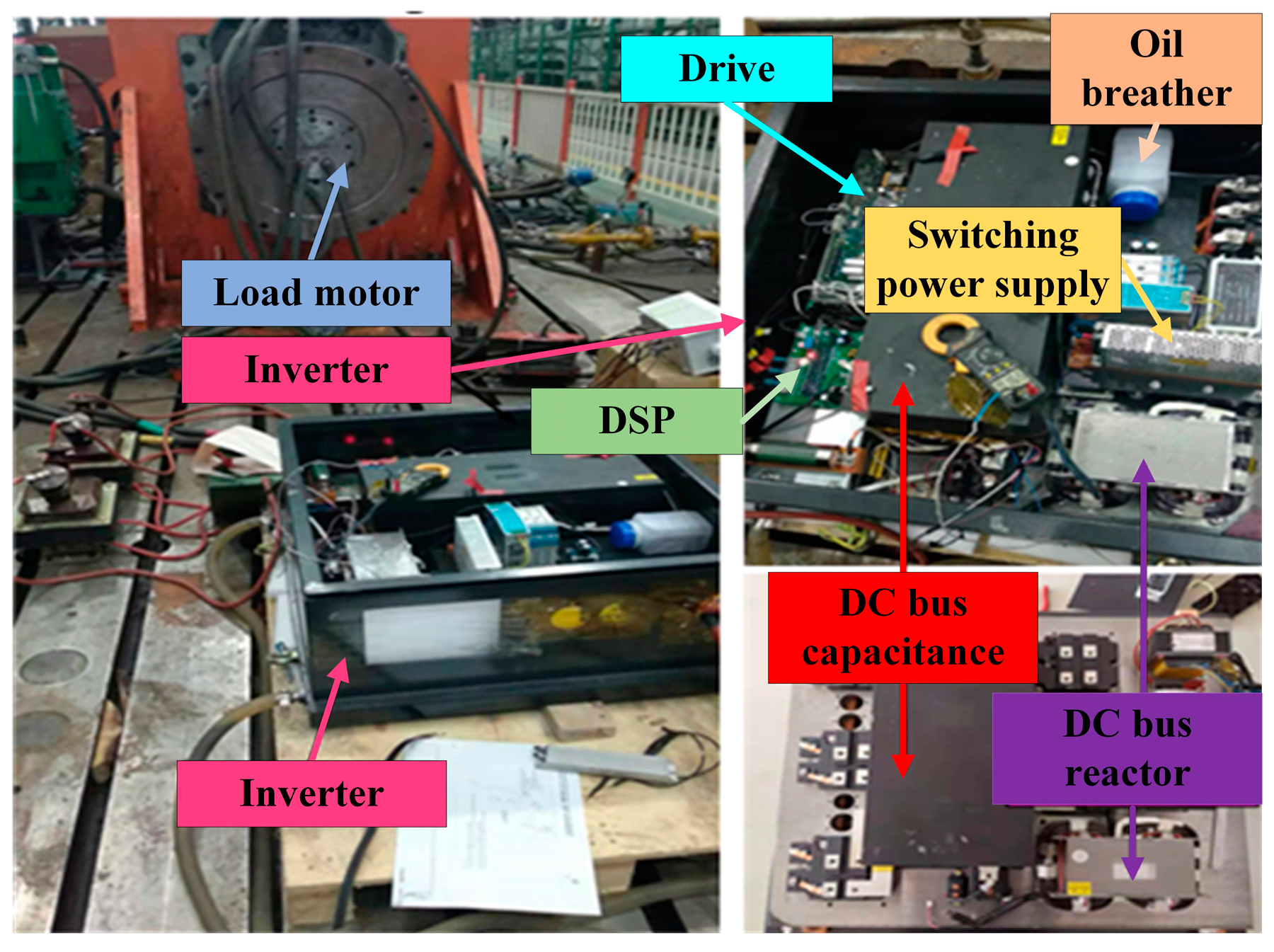

In this paper, the single-phase-to-ground short-circuit experiment of the inverter is carried out. The main experimental devices include three parts: a permanent magnet synchronous motor, inverter, and oscilloscope. Figure 20 shows the experimental circuit diagram. The inverter adopts an AC-DC-AC structure, and Figure 21 is the experimental site.

Figure 20.

Experimental circuit diagram.

Figure 21.

Inverter, permanent magnet motor, and experimental system.

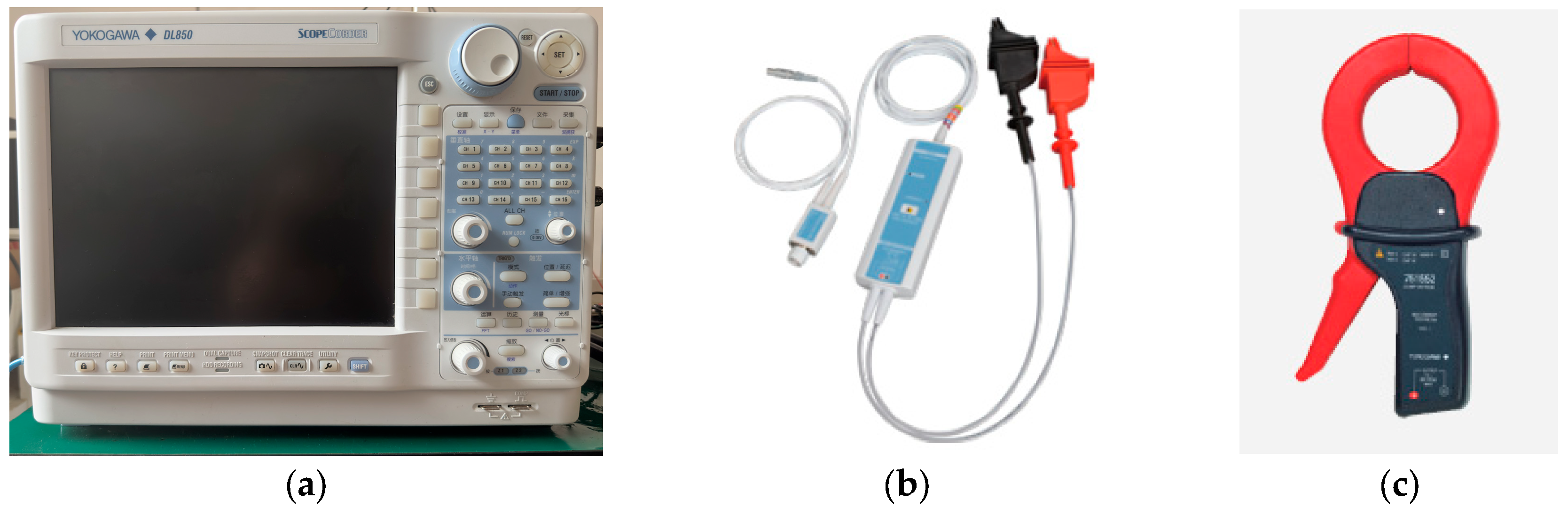

The oscilloscope, current, and voltage measurement device used in this experiment are shown in Figure 22.

Figure 22.

Experimental measurement equipment: (a) YOKOGAWA/DL850 oscilloscope; (b) High voltage differential probe; (c) Current sensor.

Table 10 lists the measurement conditions of this experiment.

Table 10.

The measurement conditions of this experiment.

According to the experimental circuit shown in Figure 20, the experimental system in Figure 21 is built. As shown in Figure 21, a contactor is connected between the output end of one phase of the inverter and the earth. By adding or removing 220 V voltage to the control end of the contactor, the on-off of the contactor can be controlled. The specific experimental steps are as follows:

Step 1: Set the oscilloscope channel 1 as the upper bridge arm drive signal with the ground short circuit bridge arm, channel 2 as the short circuit phase output current, channel 3 as the DC bus voltage, and channel 4 to the diode reverse tube voltage drop.

Step 2 Set the oscilloscope channel 3 as the trigger signal.

Step 3: Let the contactor in the disconnected state, and let the inverter output a certain frequency of alternating current and stable.

Step 4: Suddenly close the contactor so that a phase of the inverter outputs a short circuit with the ground.

Step 5: Collect data.

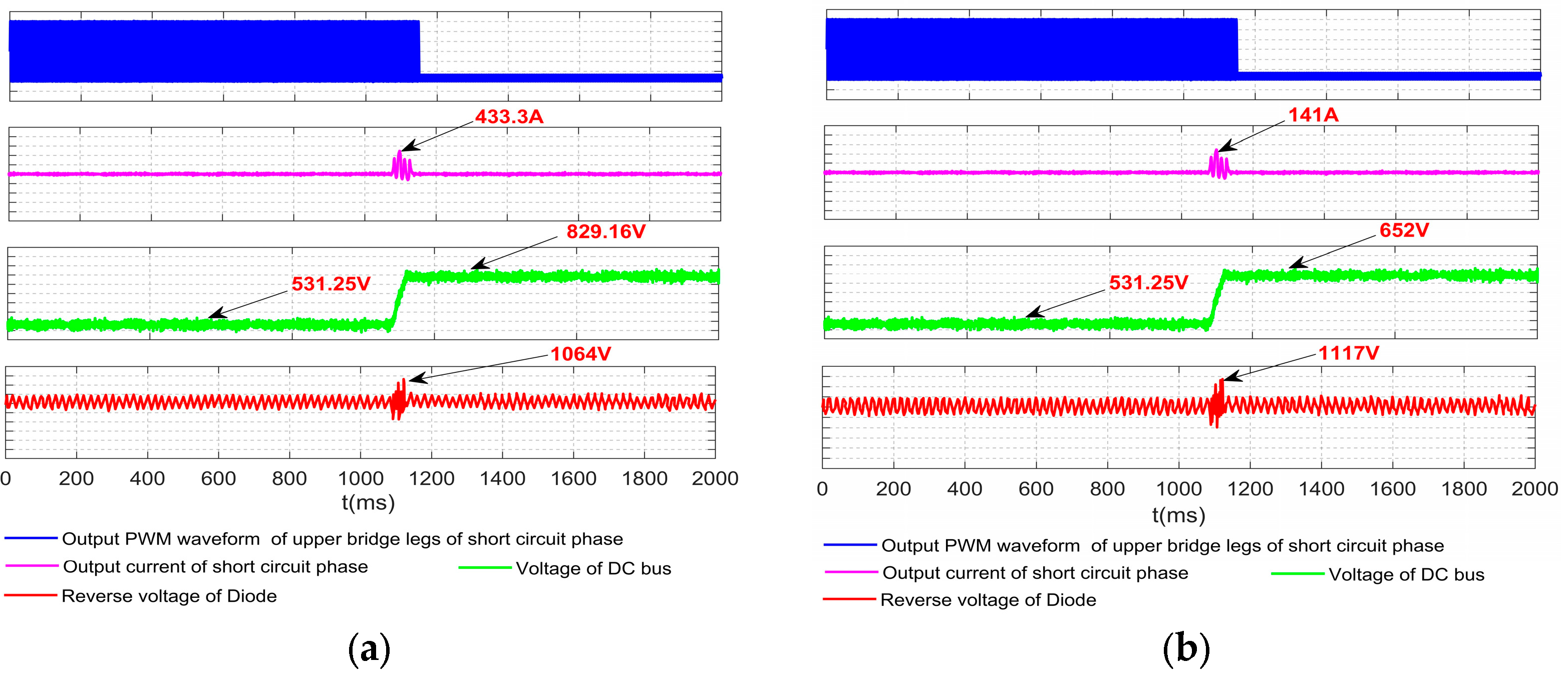

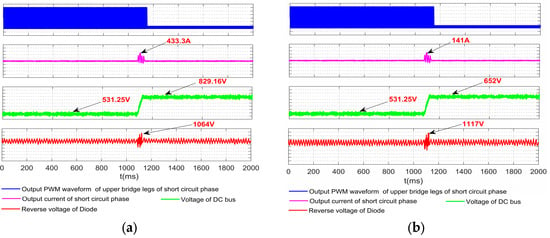

Table 11 shows the experimental results of the one-to-ground short circuit of the inverter.

Table 11.

The experimental results of inverter one-to-ground short circuit.

As shown in Table 2 and Table 11, the simulation and experiment results show that there is a sudden rise and fall of Vdc caused by the capacitance of the ESR. When D6 and VT2 turn on, VT is the lowest in the three phases, and the bus capacitor anode potential is equal to the earth, so D3 has a high voltage of −VT +VDC when L is charged by −VT.

The experimental results are shown in Figure 23. Things will be worse practically due to the parasitic parameters. It can be seen from the experiment results that when the output current increases to 433.3 A, the bus voltage increases to 829 V, and the diode reverse voltage rises to 1604 V. The current flowing through all devices will be balanced and reduced if the DC reactor with half the value of the original reactor is placed on the positive and negative sides of the DC bus, respectively.

Figure 23.

Experimental results waveform (a) DC reactor on the cathode of the DC bus; (b) DC reactor on the anode and cathode of the DC bus.

On the positive and negative of the bus installed a DC reactor, when inverter earthing short circuit happens, VDC and IA, etc., decrease significantly. It has proved to be an effective way to avoid damage due to short circuits caused by the device.

7. Conclusions

Aiming at the fault caused by a phase-to-ground short circuit of the frequency converter, this paper systematically studies the LC filter, rectifier diode, and a phase-to-ground short circuit of the 380 V/110 kW frequency converter.

- (1)

- Based on the Newton–Raphson method, the DC bus capacitance of the frequency converter is analyzed and designed. By building a power electronic model of the power supply state of the frequency converter, the expression of DC bus capacitance at different times and the calculation results of loss and life are given.

- (2)

- Under the two conditions of ensuring the stability of the system and ensuring the voltage on the reactor not to be too large, the power electronic modeling of the DC reactor is carried out, and the calculation expression of inductance value, magnetic field distribution, and loss calculation process of DC reactor are given.

- (3)

- This paper analyzes the one-phase earthing short of inverters considering the effect of leakage inductance of the power transformer, establishes a double boost circuit and introduces its energy transmission process, and comes to a conclusion that the main reasons the DC bus voltage rises are the increase in diode reverse voltage drop caused by the charge and discharge of DC reactor as well as ESR. The current and voltage through rectifiers, DC bus, and diodes decrease a lot by installing DC reactors on both sides of the DC bus when earthing short happens. Simulation and experimental results verify the effectiveness of the proposed scheme.

Author Contributions

Conceptualization, D.C.; methodology, D.C.; software, Z.Z.; validation, Z.Z., S.Z. and Y.S.; formal analysis, W.Z. (Wenbo Zhao); investigation, W.Z. (Wenliang Zhao); resources, D.C.; data curation, D.C.; writing—original draft preparation, Z.Z.; writing—review and editing, D.C.; visualization, S.Z.; supervision, D.C.; project administration, D.C.; funding acquisition, D.C. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Acknowledgments

Thank you to Su Zhonghuan for providing resources and assistance for this paper.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Baburajan, S.; Peyghami, S.; Kumar, D.; Blaabjerg, F.; Davari, P. Effect of unipolar and bipolar SPWM on the lifetime of DC-link capacitors in single-phase voltage source inverters. In Proceedings of the 2020 22nd European Conference on Power Electronics and Applications (EPE’20 ECCE Europe), Lyon, France, 7–11 September 2020; pp. P.1–P.10. [Google Scholar]

- Wang, H.; Huang, S.; Kumar, D.; Wang, Q.; Deng, X.; Zhu, G.; Wang, H. Lifetime prediction of DC-link capacitors in multiple drives system based on simplified analytical modeling. IEEE Trans. Power Electron. 2021, 36, 844–860. [Google Scholar] [CrossRef]

- Qi, Y.; Fang, J.; Liu, J.; Tang, Y. Coordinated control for harmonic mitigation of parallel voltage-source inverters. CES Trans. Elect. Mach. Syst. 2018, 2, 276–283. [Google Scholar] [CrossRef]

- Zhou, L.; Wu, W.; Chen, Y.; Jiang, J.; Zhou, X.; Yang, L.; He, Z.; Yan, K.; Luo, A. Harmonic voltage distortion damping method for parallel-connected LCL-type inverters in islanded operation. IEEE Trans. Ind. Electron. 2019, 66, 9032–9044. [Google Scholar] [CrossRef]

- Peng, C.; Wen, J.; Wang, Y.; Wu, J.; Chen, X. Potential use of fault current limiter in vsc based dc transmission systems. In Proceedings of the 2012 Asia-Pacific Power and Energy Engineering Conference, Shanghai, China, 27–29 March 2012; pp. 1–4. [Google Scholar]

- Iijima, R.; Isobe, T.; Tadano, H. Investigation of eliminating freewheeling diode conduction of Z-source inverter using SiC-MOSFET. In Proceedings of the IECON 2015-41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015; pp. 3649–3652. [Google Scholar]

- Kamoshida, N.; Iijima, R.; Isobe, T.; Tadano, H. Loss analysis of quasi Z-source inverter with Superjunction-MOSFET. Electr. Eng. Jpn. 2018, 205, 54–61. [Google Scholar] [CrossRef]

- Takashima, K.; Iijima, R.; Mannen, T.; Isobe, T.; Iwamuro, N.; Tadano, H. Design Strategy of Z-source Inverter for Utilization of Power Semiconductors with Extremely Low Short-circuit Capability. In Proceedings of the IECON 2019-45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon, Portugal, 14–17 October 2019; Volume 1, pp. 4997–5002. [Google Scholar]

- Iijima, R.; Kamoshida, N.; Isobe, T.; Tadano, H. Loss Analysis of Quasi Z-Source Inverter Using Superjunction-MOSFET. In Proceedings of the 2018 20th European Conference on Power Electronics and Applications (EPE’18 ECCE Europe), Riga, Latvia, 17–21 September 2018; pp. P.1–P.8. [Google Scholar]

- Hou, R.; Lu, J. An Ultrafast Discrete Protection Circuit Utilizing Multi-Functional Dual-Gate Pads of GaN HEMTs. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–3 October 2019; pp. 818–823. [Google Scholar]

- Hooshyar, H.; Baran, M.E. Fault analysis on distribution feeders with high penetration of PV systems. IEEE Trans. Power Syst. 2013, 28, 2890–2896. [Google Scholar] [CrossRef]

- Katiraei, F.; Sun, C.; Enayati, B. No Inverter Left Behind: Protection, Controls, and Testing for High Penetrations of PV Inverters on Distribution Systems. IEEE Power Energy Mag. 2015, 13, 43–49. [Google Scholar] [CrossRef]

- Claudio, A. Enhaneed Transition Mode Power Factor Corrector. STAN966 APPlication Note. Available online: https://www.belchip.by/sitedocs/00008013.pdf (accessed on 12 September 2023).

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).