A 2-V 1.4-dB NF GaAs MMIC LNA for K-Band Applications

Abstract

:1. Introduction

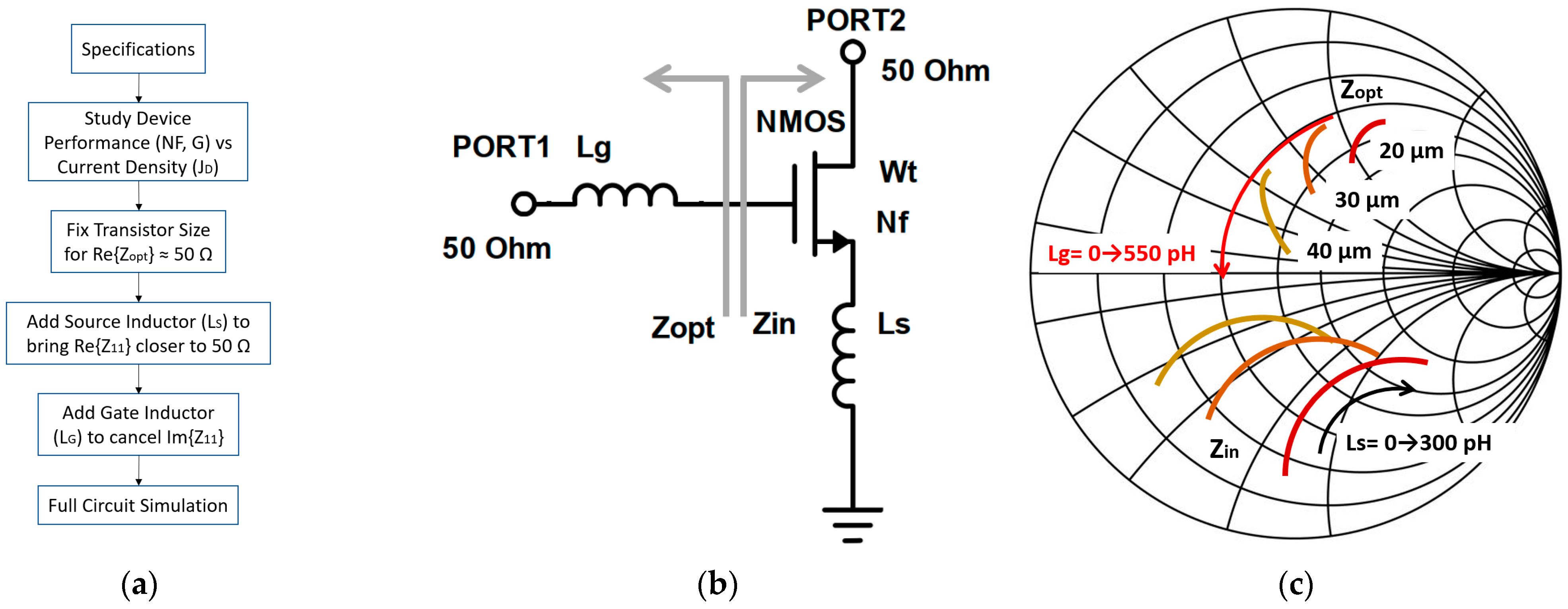

2. Circuit Design

Design Approach

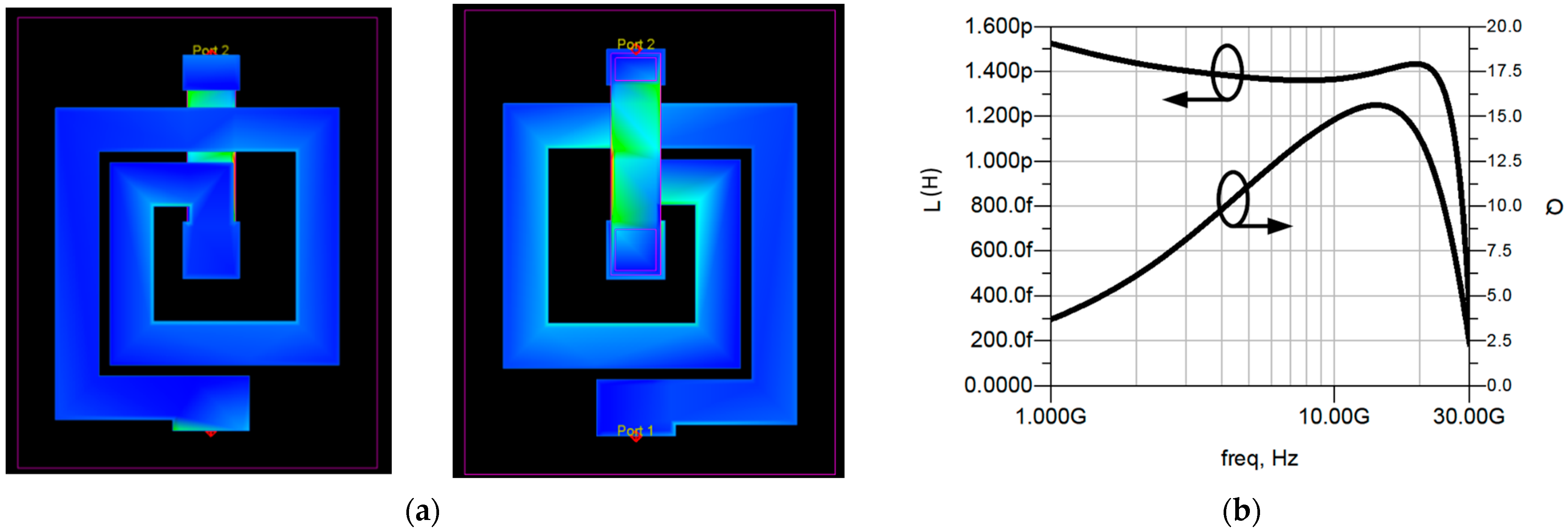

3. Proposed Circuit

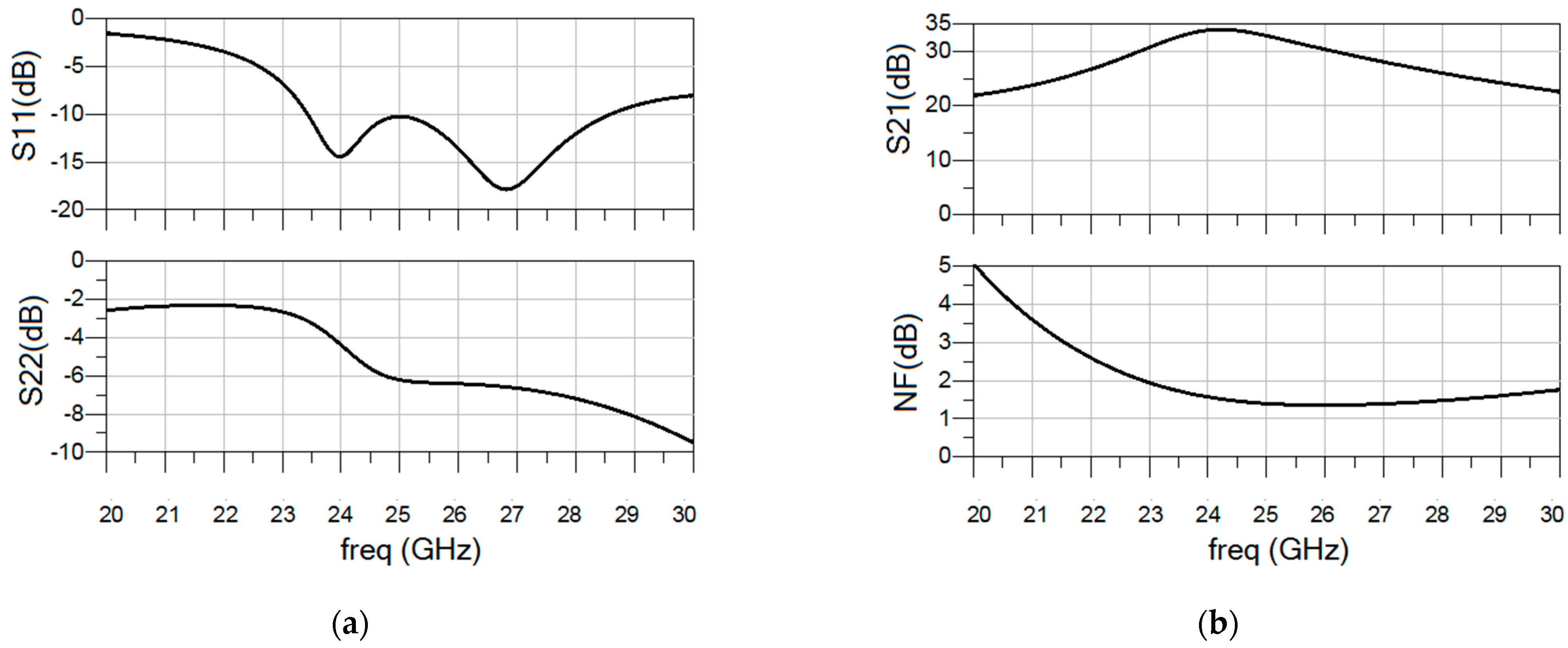

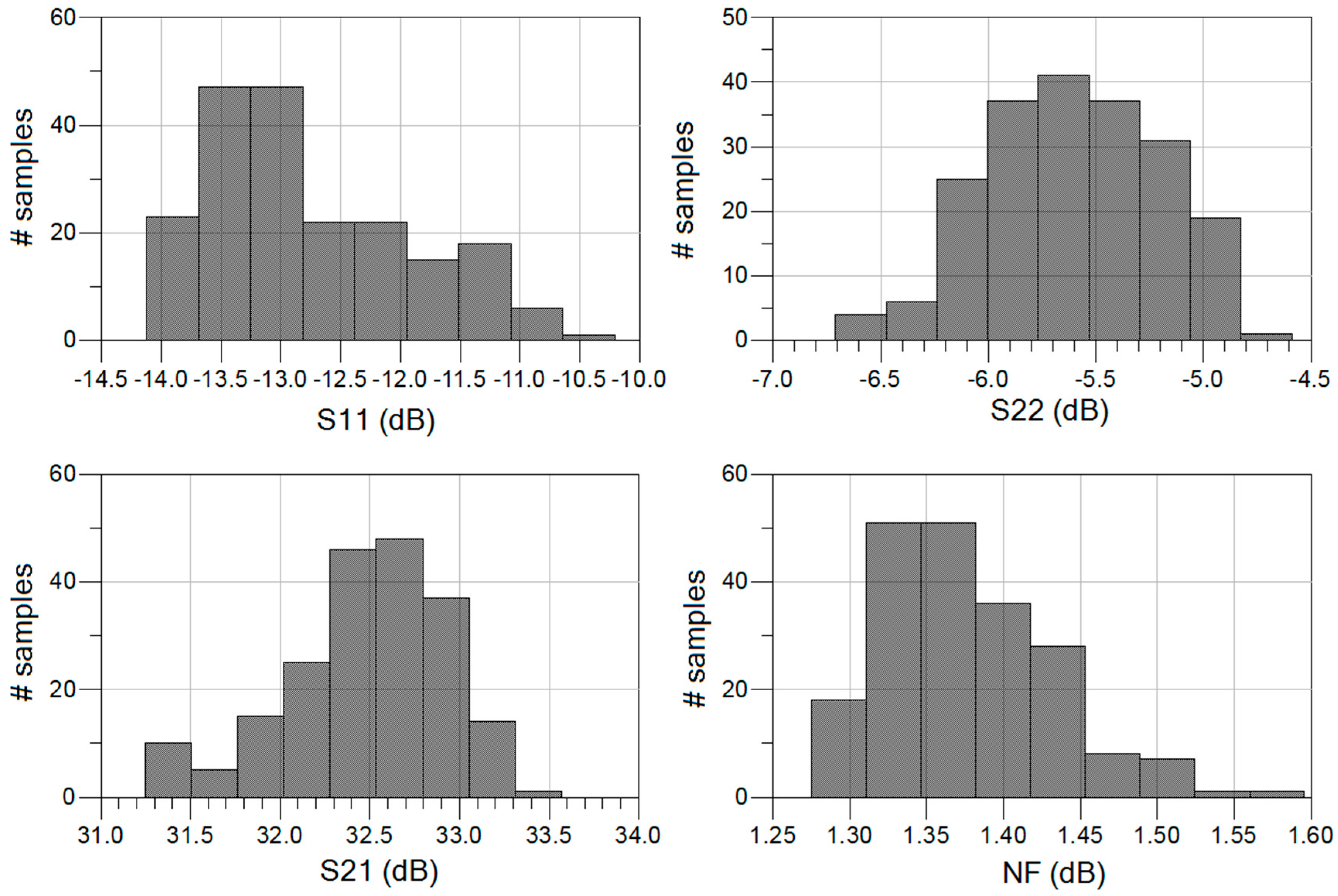

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- El-Aassar, O.; Rebeiz, G.M. Design of Low-Power Sub-2.4 dB Mean NF 5G LNAs Using Forward Body Bias in 22 nm FDSOI. IEEE Trans. Microw. Theory Tech. 2020, 68, 4445–4454. [Google Scholar] [CrossRef]

- Pozar, D.M. Microwave Engineering, 4th ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2012; ISBN 9780470631553. [Google Scholar]

- Colangeli, S.; Bentini, A.; Ciccognani, W.; Limiti, E.; Nanni, A. GaN-based robust low-noise amplifiers. IEEE Trans. Electron Devices 2013, 60, 3238–3248. [Google Scholar] [CrossRef]

- Letailleur, L.; Villegas, M.; Hajjar, A.A.; Kacou, C.E. Performance analysis of GaN/Si versus GaAs LNAs in 5G mm-wave frontend context. In Proceedings of the 2022 14th Global Symposium on Millimeter-Waves & Terahertz (GSMM), Seoul, Republic of Korea, 18–20 May 2022; pp. 9–11. [Google Scholar]

- Letailleur, L.; Hajjar, A.A.; Villegas, M.; Edoua, K.C.; Kamouchi, M.E.; Leblanc, R. GaN/Si vs. GaAs LNA Linear and Nonlinear Characterizations, New FOMs, in Millimeter Wave T/R Chip Context. In Proceedings of the 2022 International Workshop on Integrated Nonlinear Microwave and Millimetre-Wave Circuits (INMMiC), Cardiff, UK, 7–8 April 2022; pp. 22–24. [Google Scholar] [CrossRef]

- Dahlman, E.; Parkvall, S.; Skold, J. 5G NR: The Next Generation Wireless Access Technology, 1st ed.; Academic Press: Cambridge, MA, USA, 2020. [Google Scholar]

- Razavi, B. RF Microelectronics; Prentice Hall Communications Engineering and Emerging Technoogies Series; Prentice Hall: New York, NY, USA, 2012; pp. 1–941. [Google Scholar]

- Kyung-Whan, Y. Microwave Circuit Design a Practical Approach Using ADS; Prentice Hall: New York, NY, USA, 2014; ISBN 9780134086781. [Google Scholar]

- Uko, M.; Ekpo, S. A 23-28 GHz pHEMT MMIC Low-Noise Amplifier for Satellite-Cellular Convergence Applications. Int. Rev. Aerosp. Eng. 2021, 14, 240. [Google Scholar] [CrossRef]

- Florian, C.; Traverso, P.A.; Santarelli, A. A Ka -Band MMIC LNA in GaN-on-Si 100-nm Technology for High Dynamic Range Radar Receivers. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 161–164. [Google Scholar] [CrossRef]

- Wang, Z.; Hou, D.; Zhou, P.; Li, H.; Li, Z.; Chen, J.; Hong, W. A Ka -Band Switchable LNA With 2.4-dB NF Employing a Varactor-Based Tunable Network. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 385–388. [Google Scholar] [CrossRef]

- Yan, X.; Luo, H.; Zhang, J.; Zhang, H.; Guo, Y. Design and Analysis of a Cascode Distributed LNA with Gain and Noise Improvement in 0.15-μm GaAs pHEMT Technology. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 4659–4663. [Google Scholar] [CrossRef]

- Chiong, C.; Wang, Y.; Chang, K.-C.; Wang, H. Low-Noise Amplifier for Next-Generation Radio Astronomy Telescopes: Review of the State-of-the-Art Cryogenic LNAs in the Most Challenging Applications. IEEE Microw. Mag. 2022, 23, 31–47. [Google Scholar] [CrossRef]

- López-Villegas, J.M.; Samitier, J.; Cane, C.; Losantos, P.; Bausells, J. Improvement of the quality factor of RF integrated inductors by layout optimization. October 1998, 48, 169–172. [Google Scholar] [CrossRef] [Green Version]

- Vanukuru, V.N.R. High-Q Inductors Utilizing Thick Metals and Dense-Tapered Spirals. IEEE Trans. Electron Devices 2015, 62, 3095–3099. [Google Scholar] [CrossRef]

- Li, C.; El-Aassar, O.; Kumar, A.; Boenke, M.; Rebeiz, G.M. LNA Design with CMOS SOI Process-l. 4dB NF K/Ka band LNA. In Proceedings of the 2018 IEEE/MTT-S International Microwave Symposium—IMS, Philadelphia, PA, USA, 10–15 June 2018; pp. 1484–1486. [Google Scholar]

- Cuadrado-Calle, D.; George, D.; Fuller, G. A GaAs Ka-band (26-36 GHz) LNA for radio astronomy. In Proceedings of the 2014 IEEE International Microwave and RF Conference (IMaRC), Kolkata, India, 28–30 November 2018; pp. 301–303. [Google Scholar] [CrossRef]

- Nguyen, D.P.; Pham, B.L.; Pham, T.; Pham, A.-V. A 14–31 GHz 1.25 dB NF enhancement mode GaAs pHEMT low noise amplifier. In Proceedings of the 2017 IEEE MTT-S International Microwave Symposium (IMS), Honolulu, HI, USA, 4–9 June 2017; pp. 1961–1964. [Google Scholar]

- Xie, H.; Cheng, Y.J.; Fan, Y. A K-Band High Interference-Rejection GaAs Low-Noise Amplifier Using Multizero Control Method for Satellite Communication. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 1069–1072. [Google Scholar] [CrossRef]

| Parameter | [17] | [18] | [16] | [19] | [4] | This Work |

|---|---|---|---|---|---|---|

| Data | Simulated | Measured | Measured | Measured | Measured | Simulated |

| Freq. range (GHz) | 26–36 | 15–25 | 23–30 | 17.5–22.5 | 24–30 | 23–29 |

| Gain (dB) | 33 | 30 | 12.8 | 23.9 | 25 | 33 |

| Noise figure (dB) | 1.8 | 1.5 | 1.5 | 1.3 | 1.5 | 1.4 |

| |S11| (dB) | 12 | 10 | 6 | 12 | 10 | 10 |

| |S22| (dB) | 12 | 10 | 6 | 5 | 10 | 5 |

| Power consumption (mW) | - | 212 | 15 | 66 | 150 | 118.2 |

| Publication year | 2015 | 2017 | 2018 | 2020 | 2022 | 2023 |

| FoMSS | 41.25 | 60 | 25.6 | 79.67 | 50 | 82.5 |

| Process | GaAs 100 nm | GaAs 150 nm | SOI 45 nm | GaAs 90 nm | GaAs 70 nm | GaAs 100 nm |

| Area (mm2) | 3.64 | 1.87 | 0.3021 | 2.6 | - | 5.94 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Galante-Sempere, D.; Khemchandani, S.L.; del Pino, J. A 2-V 1.4-dB NF GaAs MMIC LNA for K-Band Applications. Sensors 2023, 23, 867. https://doi.org/10.3390/s23020867

Galante-Sempere D, Khemchandani SL, del Pino J. A 2-V 1.4-dB NF GaAs MMIC LNA for K-Band Applications. Sensors. 2023; 23(2):867. https://doi.org/10.3390/s23020867

Chicago/Turabian StyleGalante-Sempere, David, Sunil Lalchand Khemchandani, and Javier del Pino. 2023. "A 2-V 1.4-dB NF GaAs MMIC LNA for K-Band Applications" Sensors 23, no. 2: 867. https://doi.org/10.3390/s23020867

APA StyleGalante-Sempere, D., Khemchandani, S. L., & del Pino, J. (2023). A 2-V 1.4-dB NF GaAs MMIC LNA for K-Band Applications. Sensors, 23(2), 867. https://doi.org/10.3390/s23020867