A 14-Bit Hybrid Analog-to-Digital Converter for Infrared Focal Plane Array Digital Readout Integrated Circuit

Abstract

:1. Introduction

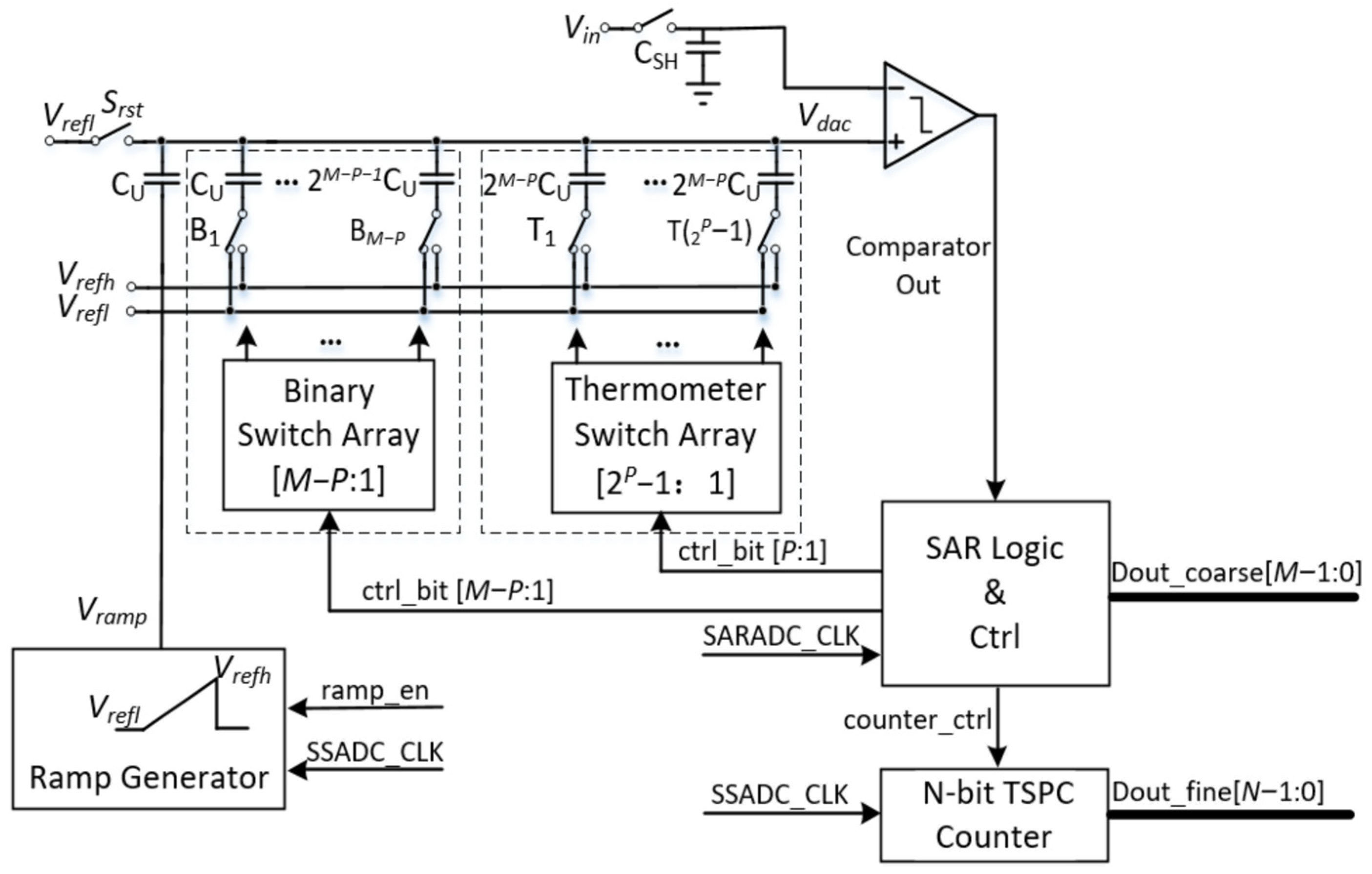

2. Architecture of the Proposed ADC

2.1. Block Diagram

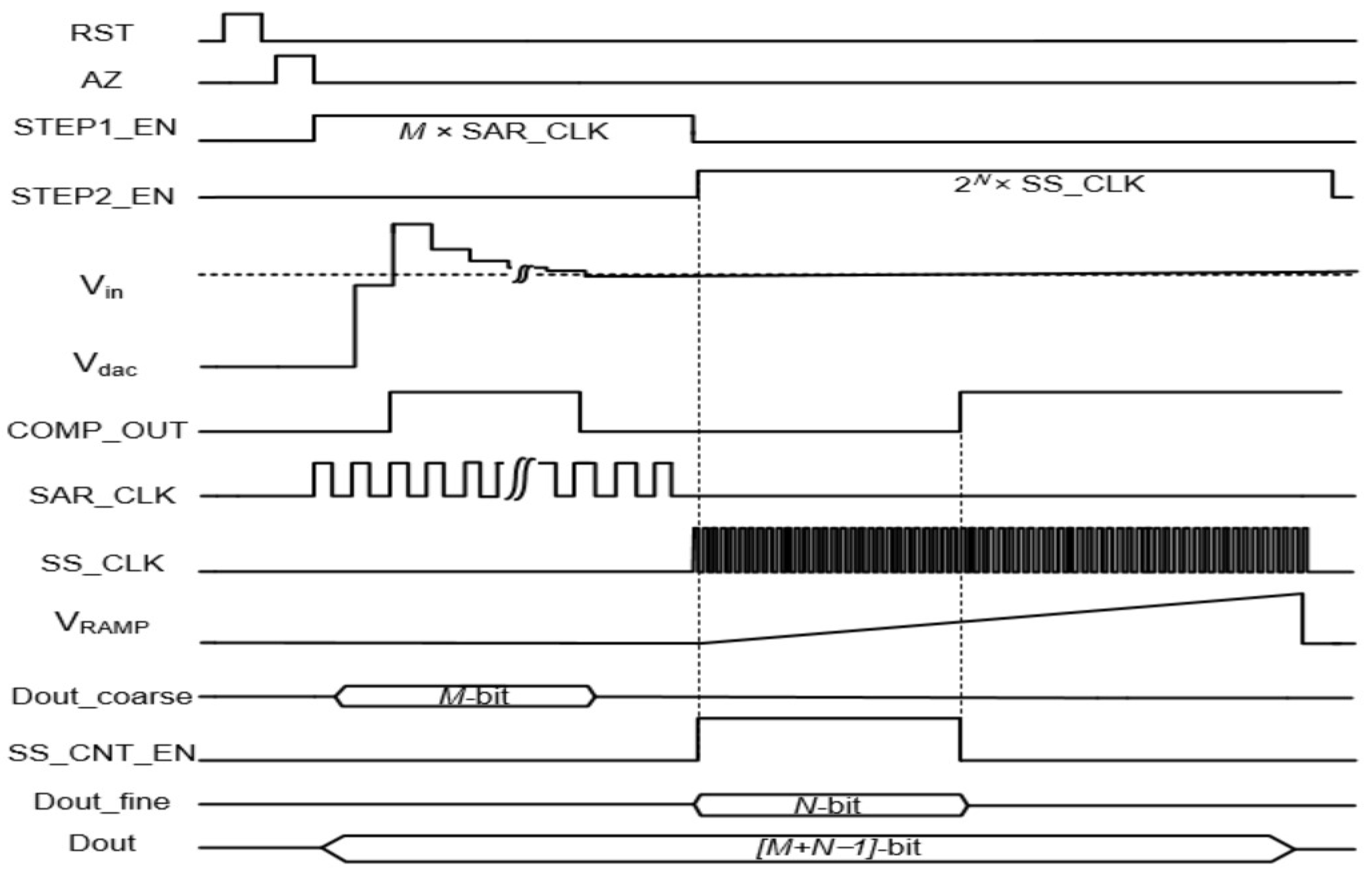

2.2. The Operating Principle of the Proposed Hybrid ADC

3. The Design of the Proposed Hybrid ADC

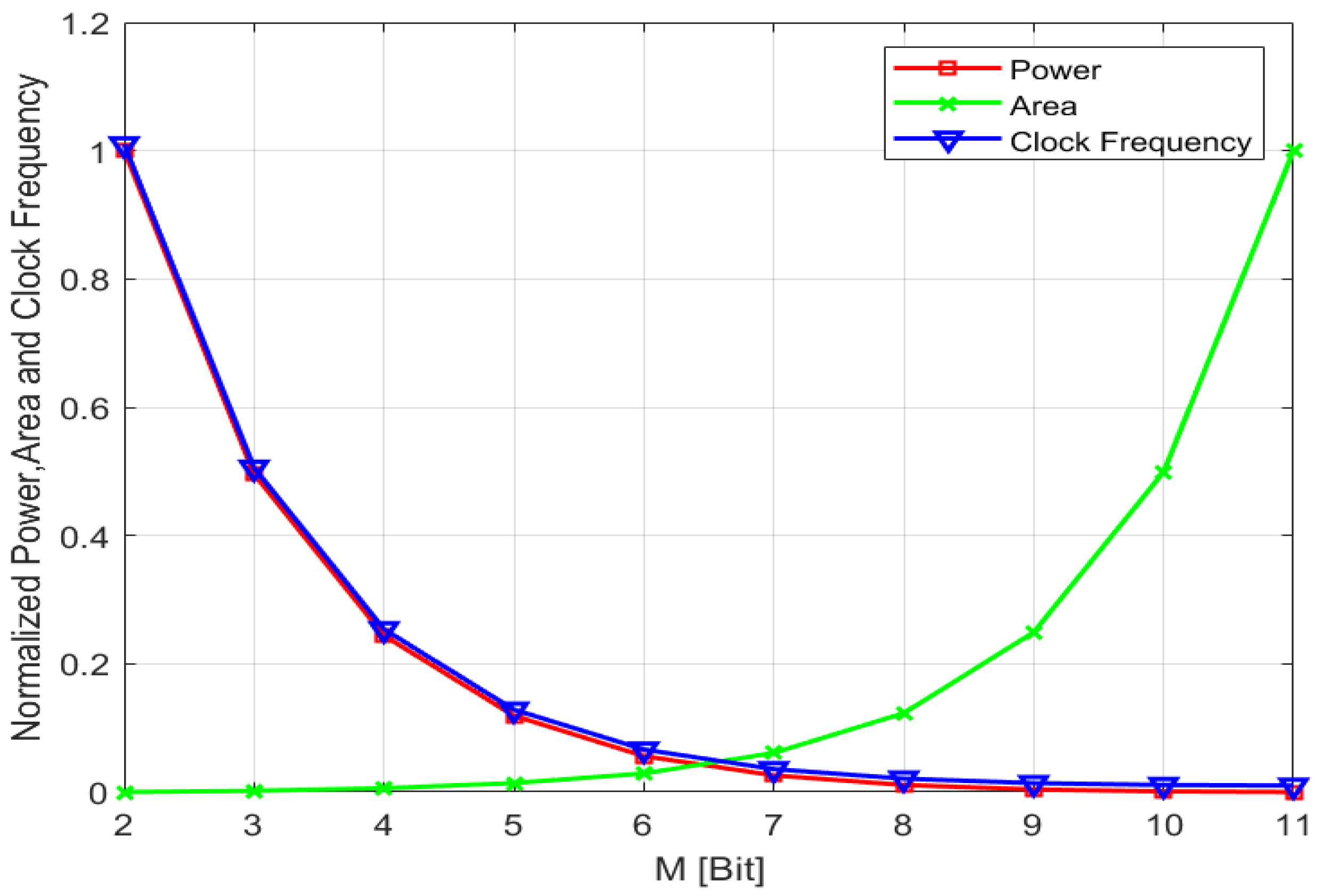

3.1. The Trade-off between the SAR and SS ADC

3.2. Comparator

3.3. Ramp

3.4. Layout

4. Measurement Results and Discussion

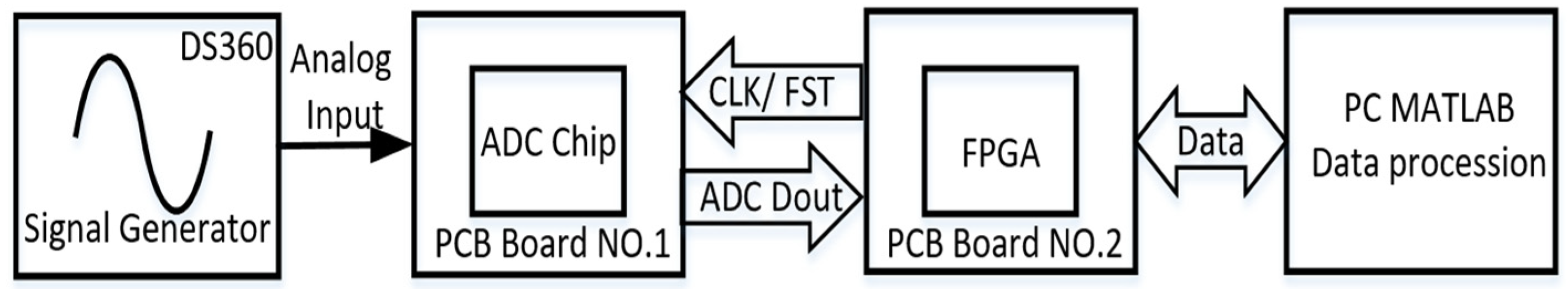

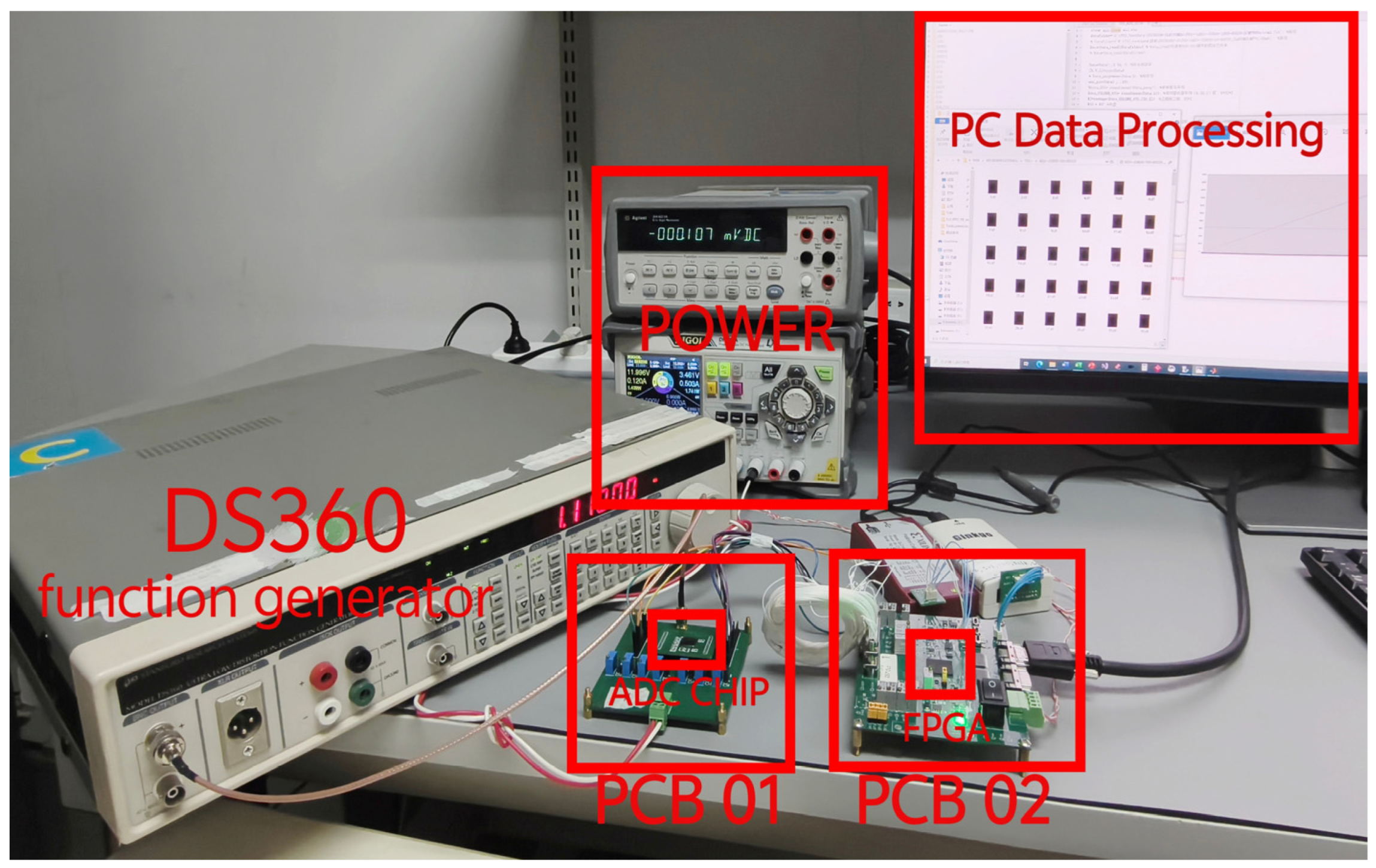

4.1. Measurement Setup

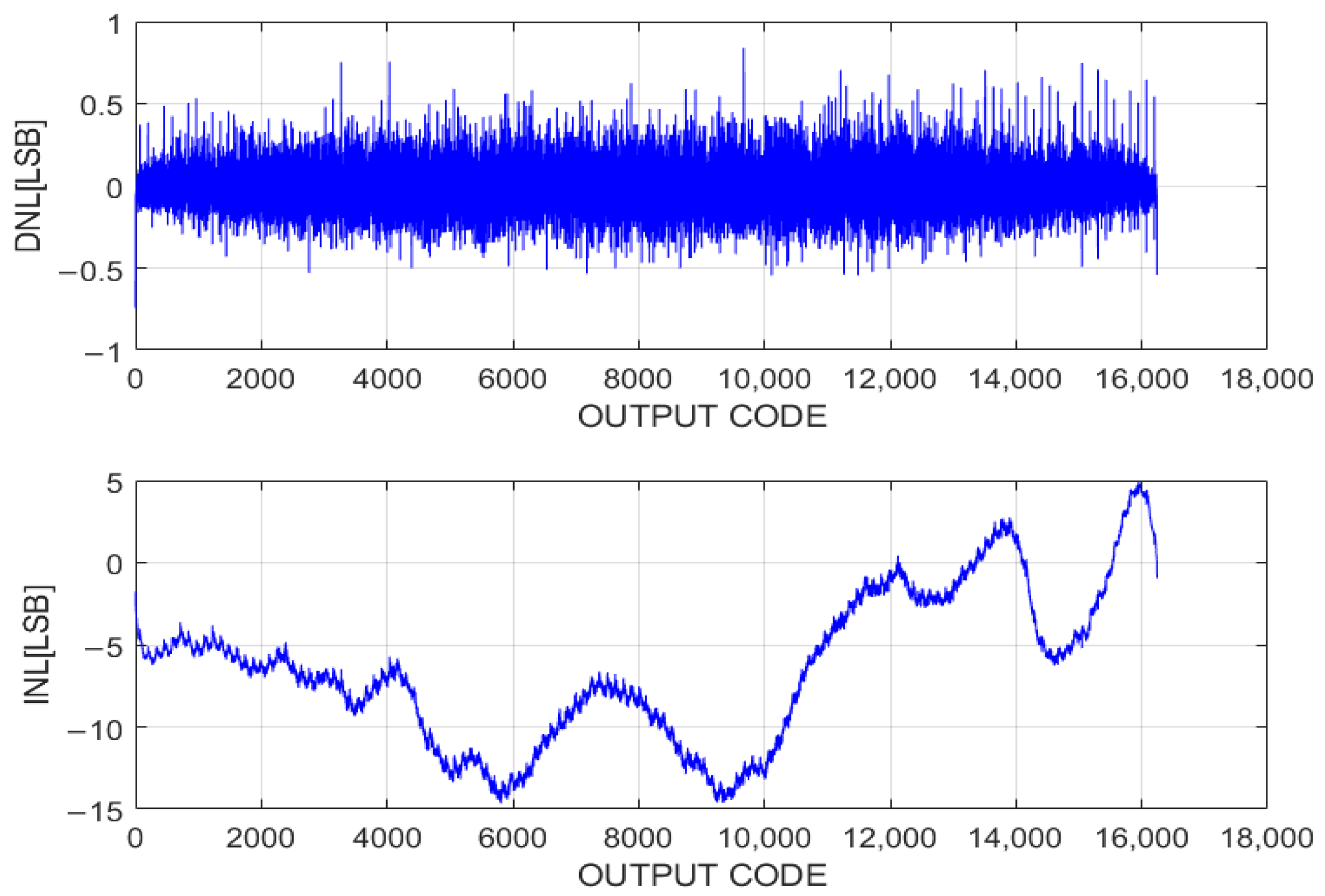

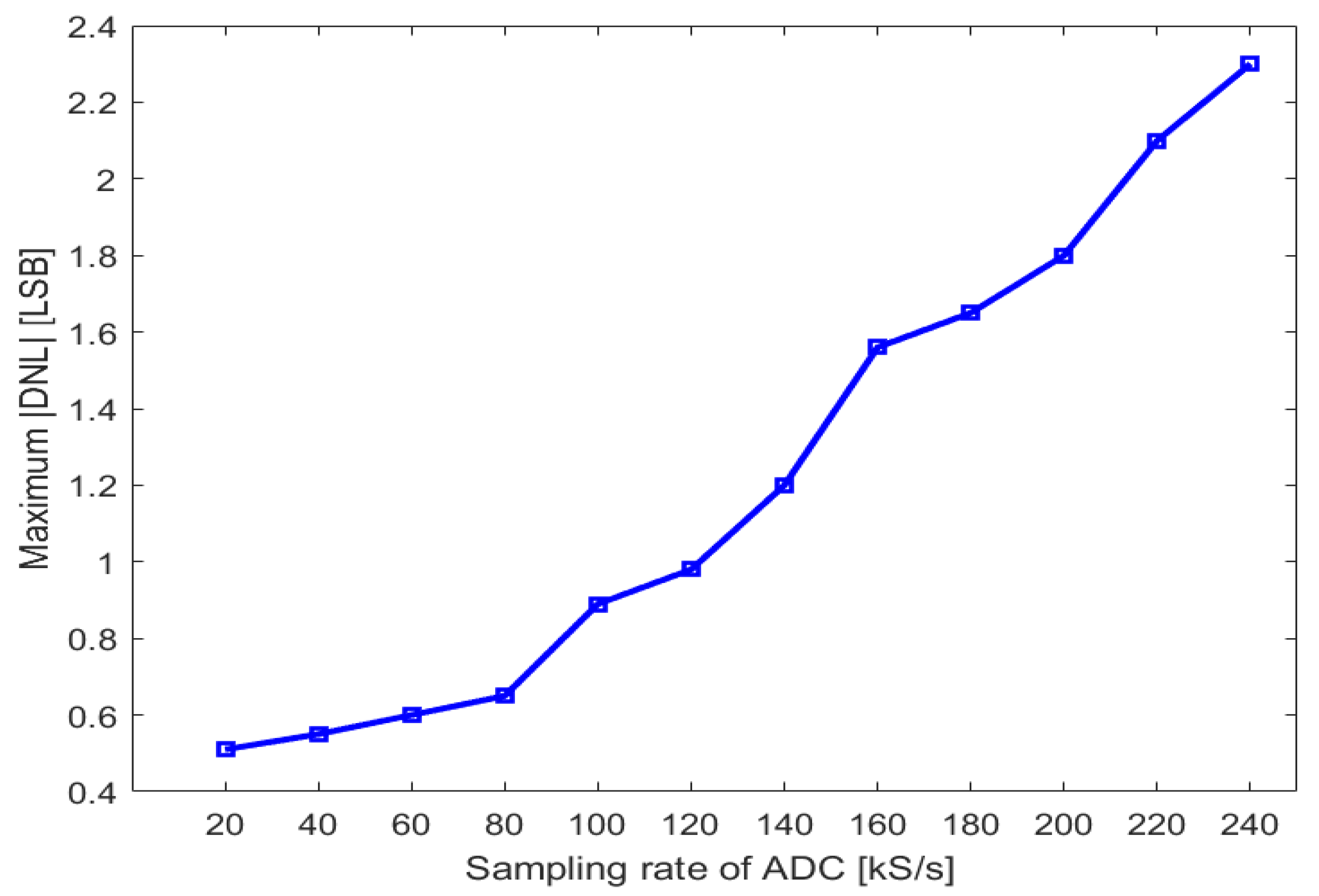

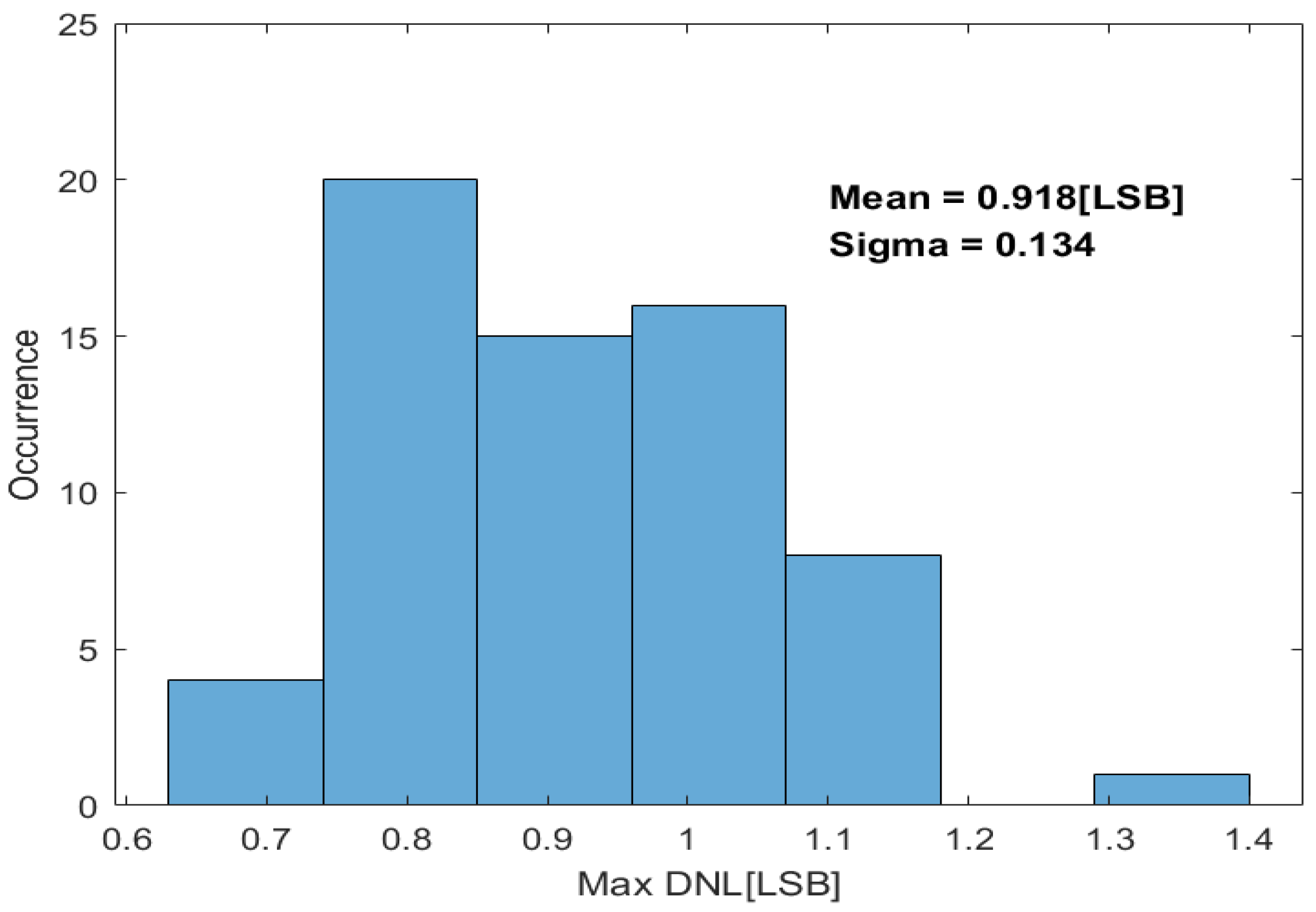

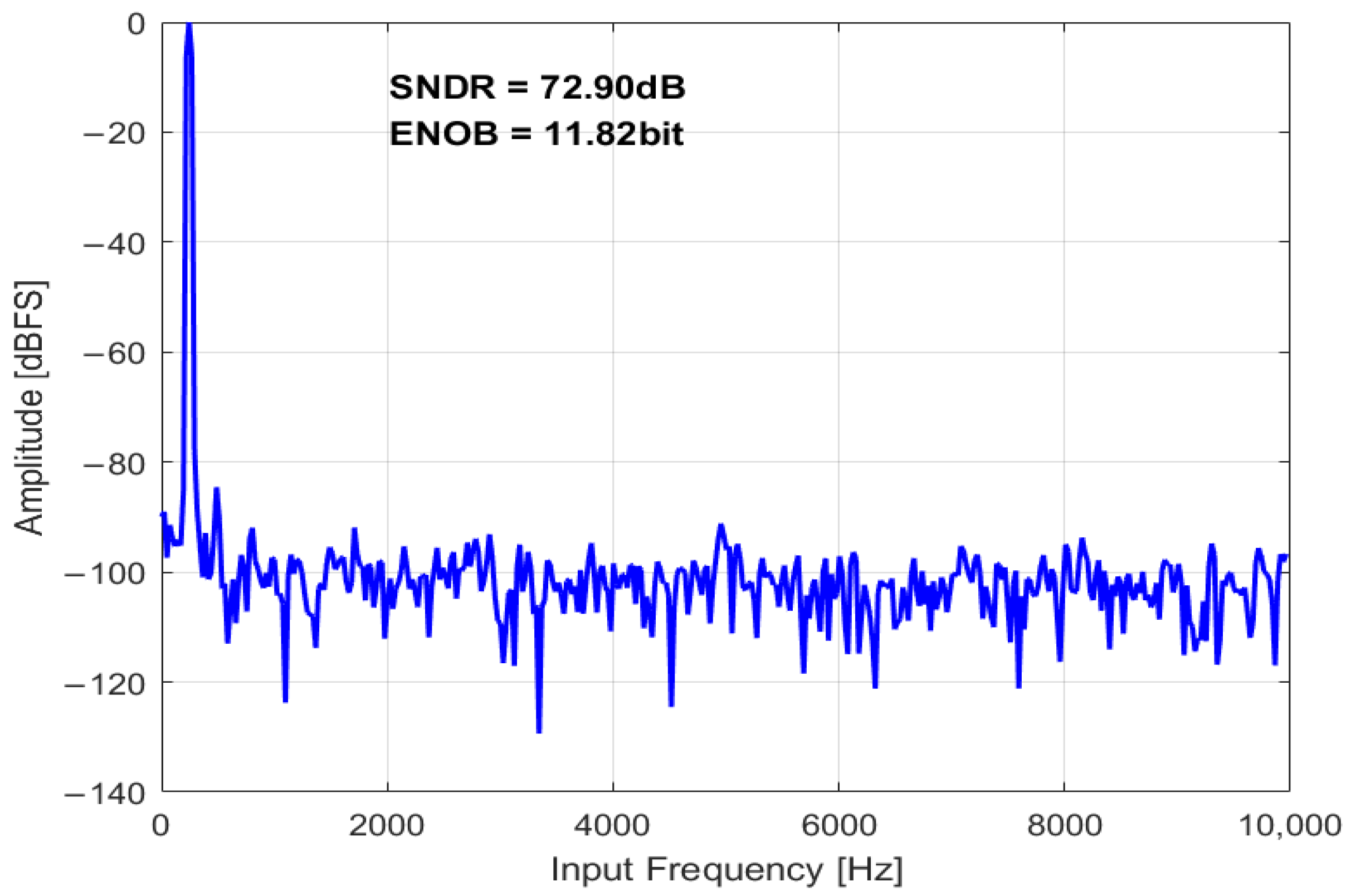

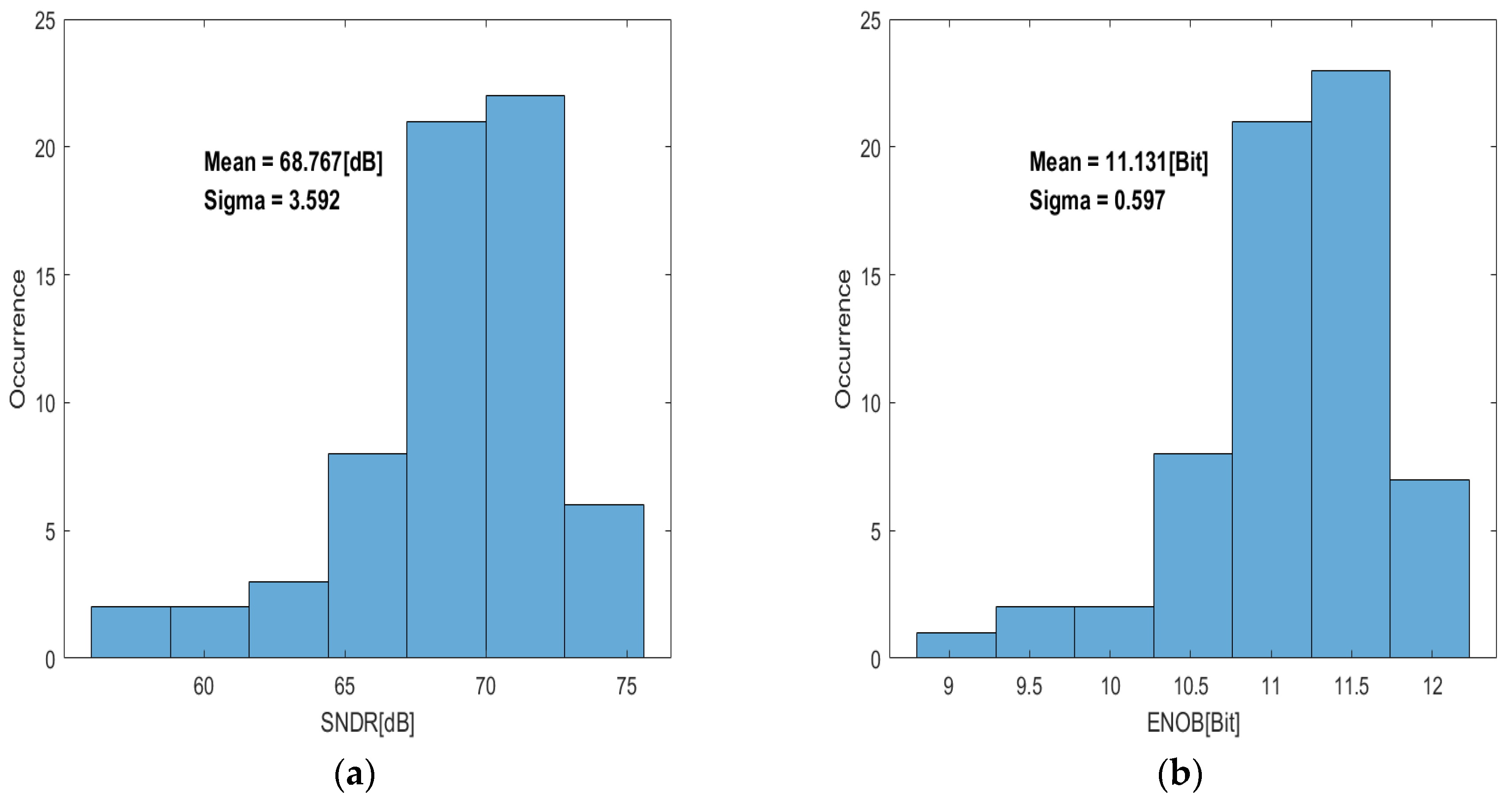

4.2. Measurement Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Reibel, Y.; Pere-Laperne, N.; Augey, T.; Rubaldo, L.; Decaens, G.; Bourqui, M.L.; Manissadjian, A.; Billon-Lanfrey, D.; Bisotto, S.; Gravrand, O.; et al. Getting Small, new 10 µm pixel pitch cooled infrared products. Infrared Technol. Appl. XL 2014, 9070, 886–895. [Google Scholar] [CrossRef]

- Hood, A.D.; Huang, E.K.; Yang, K.; Hibberd, D.; Loung, V.; Oleson, M.; Lott, R.; Pratt, C.; Thomas, J.; Costolo, M.; et al. Small pixel pitch, high-definition MWIR, and dual band SWIR/MWIR imaging sensors for SWaP-constrained applications. Infrared Technol. Appl. XLIX 2023, 12534, 140–148. [Google Scholar] [CrossRef]

- Billon-Lanfrey, D.; Trinolet, P.; Pistone, F.; Rubaldo, L.; Huet, H. New IR detectors with small pixel pitch and high operating temperature. Infrared Millim. Wave Terahertz Technol. 2010, 7854, 128–138. [Google Scholar] [CrossRef]

- Reibel, Y.; Péré-Laperne, N.; Rubaldo, L.; Augey, T.; Decaens, G.; Badet, V.; Badet, V.; Baud, L.; Roumegoux, J.; Kessler, A.; et al. Update on 10µm pixel pitch MCT-based focal plane array with enhanced functionalities. Infrared Technol. Appl. XLI 2015, 9451, 639–653. [Google Scholar] [CrossRef]

- Caulfield, J.T.; Curzan, J.P.; Norton, A.; Terterian, S.; Sharifi, H. Small pixel HD MWIR camera technology. Infrared Technol. Appl. XLVIII 2022, 12107, 443–449. [Google Scholar] [CrossRef]

- Poonnen, T.; McCotter, S.; Esparza, K.; Veeder, K. Digital readout integrated circuit for high dynamic range infrared imaging. Infrared Technol. Appl. XLIX 2021, 11740, 29–33. [Google Scholar] [CrossRef]

- Baier, N.; Gravrand, O.; Le Goff, T.; Lobre, C.; Rabaud, W.; Rochette, F.; Brunner, A.; Grezes, C.; Morisset, N.; Rubaldo, L. Small pixel pitch MCT P on N MWIR photodiodes at DEFIR: Towards 7.5um and beyond with very high image quality. Infrared Technol. Appl. XLIX 2023, 12534, 246–254. [Google Scholar] [CrossRef]

- Caulfield, J.T.; Curzan, J.P.; Sharifi, H.; Terterian, S.; Veeder, K.; Dhawan, N. High-definition and ultra-high-definition IR camera technology. Infrared Technol. Appl. XLIX 2023, 12534, 205–212. [Google Scholar] [CrossRef]

- Huang, E.; Thomas, J.; Hibberd, D.; Luong, V.; Lott, R.; Oleson, M.; Hood, A.; MacDougal, M.H. Small pixel MWIR sensors for low SWaP applications. Infrared Technol. Appl. XLVII 2021, 11741, 123–129. [Google Scholar] [CrossRef]

- Zeng, Y.; Yang, S.; Liu, Y.; Bao, R.; Zhu, Z.; Lin, J.; Zhou, X.; Chen, Y.; Yin, J.; Mak, P.I. A Digital Readout Integrated Circuit Based on Pixel-level ADC Incorporating On-chip Image Algorithm Calibration for IRFPA. IEEE Sens. J. 2023, 23, 21747–21756. [Google Scholar] [CrossRef]

- Abbasi, S.; Ceylan, O.; Gurbuz, Y. A DROIC based on PFM ADCs employing over-integration for error shaping. IEEE Trans. Circuits Syst. I Regul. Papers 2019, 66, 3713–3722. [Google Scholar] [CrossRef]

- Zeng, Y.; Yang, S.; Liu, Y.; Li, Z.; Huang, W.; Huang, X.; Zhou, X.; Liu, J.; Li, Q. A 640× 512 30μm Pixel Pitch 1.8 mK-NETD 90.1 dB-SNR Digital Read-out Integrated Circuit with Fully on-Chip Image Algorithm Pixel-Level Calibration. In Proceedings of the 2021 IEEE Asian Solid-State Circuits Conference (A-SSCC), Busan, Republic of Korea, 7–10 November 2021; pp. 1–3. [Google Scholar] [CrossRef]

- Lu, H.; Zhou, Y.; Lu, W.; Zhang, Y.; Chen, Z. High Frame Rate High Precision ROIC with Pixel-Level CCO-Based ADC for Infrared FPAs. In Proceedings of the 2023 IEEE 15th International Conference on ASIC (ASICON), Nanjing, China, 24–27 October 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Nie, K.; Zha, W.; Shi, X.; Li, J.; Xu, J.; Ma, J. A single slope ADC with row-wise noise reduction technique for CMOS image sensor. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 2873–2882. [Google Scholar] [CrossRef]

- Kim, H.J. 11-bit column-parallel single-slope ADC with first-step half-reference ramping scheme for high-speed CMOS image sensors. IEEE J. Solid-State Circuits 2021, 56, 2132–2141. [Google Scholar] [CrossRef]

- Ding, M.; Harpe, P.; Liu, Y.H.; Busze, B.; Philips, K.; De Groot, H. A 46 µW 13 b 6.4 MS/s SAR ADC with background mismatch and offset calibration. IEEE J. Solid-State Circuits 2016, 52, 423–432. [Google Scholar] [CrossRef]

- Lim, S.; Lee, J.; Kim, D.; Han, G. A high-speed CMOS image sensor with column-parallel two-step single-slope ADCs. IEEE Trans. Electron Devices 2009, 56, 393–398. [Google Scholar] [CrossRef]

- Snoeij, M.F.; Theuwissen, A.J.; Makinwa, K.A.; Huijsing, J.H. Multiple-ramp column-parallel ADC architectures for CMOS image sensors. IEEE J. Solid-State Circuits 2007, 42, 2968–2977. [Google Scholar] [CrossRef]

- Tang, F.; Chen, D.G.; Wang, B.; Bermak, A. Low-power CMOS image sensor based on column-parallel single-slope/SAR quantization scheme. IEEE Trans. Electron Devices 2013, 60, 2561–2566. [Google Scholar] [CrossRef]

- Park, H.; Yu, C.; Kim, H.; Roh, Y.; Burm, J. Low power CMOS image sensors using two step single slope ADC with bandwidth-limited comparators & voltage range extended ramp generator for battery-limited application. IEEE Sens. J. 2019, 20, 2831–2838. [Google Scholar] [CrossRef]

- Kim, M.K.; Hong, S.K.; Kwon, O.K. An area-efficient and low-power 12-b SAR/single-slope ADC without calibration method for CMOS image sensors. IEEE Trans. Electron Devices 2016, 63, 3599–3604. [Google Scholar] [CrossRef]

- Zhang, Q.; Ning, N.; Zhang, Z.; Li, J.; Wu, K.; Yu, Q. A 12-bit two-step single-slope ADC with a constant input-common-mode level resistor ramp generator. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2022, 30, 644–655. [Google Scholar] [CrossRef]

- Dai, S.; Hu, K.; Rosenstein, J.K. A segmented SAR/SS ADC with digital error correction and programmable resolution for column-parallel sensor arrays. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Lin, C.H.; Bult, K. A 10-b, 500-MSample/s CMOS DAC in 0.6 mm/sup 2. IEEE J. Solid-State Circuits 1998, 33, 1948–1958. [Google Scholar] [CrossRef]

- Van Elzakker, M.; van Tuijl, E.; Geraedts, P.; Schinkel, D.; Klumperink, E.A.; Nauta, B. A 10-bit Charge-Redistribution ADC Consuming 1.9µW at 1 MS/s. IEEE J. Solid-State Circuits 2010, 45, 1007–1015. [Google Scholar] [CrossRef]

- Liu, C.C.; Huang, M.C.; Tu, Y.H. A 12 bit 100 MS/s SAR-assisted digital-slope ADC. IEEE J. Solid-State Circuits 2016, 51, 2941–2950. [Google Scholar] [CrossRef]

- Liu, C.C.; Kuo, C.H.; Lin, Y.Z. A 10 bit 320 MS/s low-cost SAR ADC for IEEE 802.11 ac applications in 20 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2645–2654. [Google Scholar] [CrossRef]

- Wang, Z.; Liu, X.; Wan, P.; Chen, Z. Design of a column-parallel SAR/SS two-step hybrid ADC for sensor arrays. In Proceedings of the 2021 IEEE 15th International Conference on Anti-Counterfeiting, Security, and Identification (ASID), Xiamen, China, 29–31 October 2021; pp. 172–176. [Google Scholar] [CrossRef]

- McCreary, J.L.; Gray, P.R. All-MOS charge redistribution analog-to-digital conversion techniques. I. IEEE J. Solid-State Circuits 1975, 10, 371–379. [Google Scholar] [CrossRef]

- Promitzer, G. 12 bit low power fully differential switched capacitor non-calibrating successive approximation ADC with 1MS/s. In Proceedings of the 26th European Solid-State Circuits Conference, Stockholm, Sweden, 19–21 September 2000; pp. 176–179. [Google Scholar]

- Matsuo, S.; Bales, T.J.; Shoda, M.; Osawa, S.; Kawamura, K.; Andersson, A.; Haque, M.; Honda, H.; Almond, B.; Mo, Y.; et al. 8.9-megapixel video image sensor with 14-b column-parallel SA-ADC. IEEE Trans. Electron Devices 2009, 56, 2380–2389. [Google Scholar] [CrossRef]

- Kim, J.B.; Hong, S.K.; Kwon, O.K. A low-power CMOS image sensor with area-efficient 14-bit two-step SA ADCs using pseudomultiple sampling method. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 451–455. [Google Scholar] [CrossRef]

- Zhang, Q.; Ning, N.; Li, J.; Yu, Q.; Zhang, Z.; Wu, K. A high area-efficiency 14-bit SAR ADC with hybrid capacitor DAC for array sensors. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 4396–4408. [Google Scholar] [CrossRef]

- Moon, C.W.; Yoon, K.S.; Lee, J. A 12~14-Bit SAR-SS Hybrid ADC with SS Bit Shifting Resolution Reconfigurable Method for Bio-Signal Processing. Electronics 2023, 12, 4916. [Google Scholar] [CrossRef]

| [21] TED 2016 | [22] VLSI 2022 | [20] Sensor J 2020 | [23] ISCAS 2020 | [34] Electron 2022 | This Work | |

|---|---|---|---|---|---|---|

| Process | 90 nm | 130 nm | 180 nm | 180 nm | 28 nm | 180 nm |

| Supply voltage (V) | 2.8/1.2 | 3.3/1.2 | 2.8/1.5 | 1.8 | N/A | 3.3/1.8 |

| Architecture | SAR/SS | TS SS | TS SS | SAR/SS | SAR/SS | SAR/SS |

| Resolution (bit) | 12 | 12 | 12 | 10 | 14 | 14 |

| ENOB (bit) | N/A | 9.8 | 9.13 | 9.1 | 10.81 | 11.82 |

| Conversion time (μs) | 2.7 | 10 | 39.7 | 0.8 | 2.8 | 8.3 |

| Power (μW) | 56 | 62 | 6.53 | 36 | 34 | 71 |

| DNL (LSB) | −0.45/+0.84 | −1/+0.83 | −1/+4.25 | −0.61/+0.6 | −1/+2.5 | −0.61/+0.84 |

| INL (LSB) | −1.5/+0.74 | −3.31/+4.78 | −7.3/+5.73 | −0.89/+0.82 | −3.3/+3.6 | −14.5/+4.8 |

| * FoM1 (fJ/conv) | 36.9 | 151.3 | 1.75 | 87.89 | 5.8 | 43.3 |

| ** FoM2 (fJ/conv) | N/A | 695.5 | 447 | 52.5 | 53 | 196.3 |

| *** FoMS (dB) | N/A | 149.6 | 149.4 | 158.8 | 163.8 | 162 |

| Area(μm2) | 2.24 × 998 | 7.5 × 675 | 5.6 × 1007 | 60 × 200 | 550 × 1180 | 20 × 1100 |

| **** AE(μm2/code) | N/A | 5.68 | 10.6 | 21.8 | 361 | 6.08 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hu, D.; Yao, L.; Chen, N.; Zhang, J.; Zhong, S.; Mao, W.; Zhu, F.; Zhang, J. A 14-Bit Hybrid Analog-to-Digital Converter for Infrared Focal Plane Array Digital Readout Integrated Circuit. Sensors 2024, 24, 3653. https://doi.org/10.3390/s24113653

Hu D, Yao L, Chen N, Zhang J, Zhong S, Mao W, Zhu F, Zhang J. A 14-Bit Hybrid Analog-to-Digital Converter for Infrared Focal Plane Array Digital Readout Integrated Circuit. Sensors. 2024; 24(11):3653. https://doi.org/10.3390/s24113653

Chicago/Turabian StyleHu, Douming, Libin Yao, Nan Chen, Jiqing Zhang, Shengyou Zhong, Wenbiao Mao, Fang Zhu, and Juan Zhang. 2024. "A 14-Bit Hybrid Analog-to-Digital Converter for Infrared Focal Plane Array Digital Readout Integrated Circuit" Sensors 24, no. 11: 3653. https://doi.org/10.3390/s24113653