Abstract

In this article, a generalized control scheme is proposed to extend the operating range of three-phase hybrid cascaded H-bridge (HCHB) inverters into various voltage levels without necessitating alterations to the core structure or the integration of additional H-bridge submodules. This study addresses a critical challenge related to capacitor voltage drift at various modulation indices and power factors, which is a serious impediment to various applications. To overcome this challenge, a novel balancing control scheme has been developed based on the injection of two independent offset voltages to simultaneously control the DC-link and flying capacitors. A distinctive aspect of the proposed technique involves adjusting the common reference voltage to attain the nearest level in the same cluster, thereby mitigating the insufficiency of redundant switching states. The effectiveness of the proposed technique to regulate the capacitor voltages at various operating conditions has been verified through simulation and experimental results.

1. Introduction

Over the past few decades, extensive studies have been widely carried out to meet the increased market demand for high-power conversion systems, such as industrial motor drives, high-voltage direct-current (HVDC) transmission, grid-tied energy storage, uninterruptible power supplies (UPS), and renewable energy systems [1,2,3,4,5,6,7,8]. Multilevel converters have emerged as the preferred choice in systems spanning medium to high voltage ratings due to the inherent advantages, such as lower voltage stress at switch devices, reduced harmonic distortion, higher power quality, improved scalability, fault tolerability, and diminished electro-magnetic interference (EMI) compared to two-level counterparts [2,9]. Nevertheless, the number of components in the classical multilevel topologies, such as diode-clamped inverters, flying capacitor inverters, cascaded H-bridge inverters, T-type inverters, generalized P2 inverters, and multilevel active-clamped inverters, increases in proportion to the number of levels [4,10,11,12,13,14,15,16,17,18,19,20,21,22,23].

In order to reduce the number of semiconductor switches, several topologies have been proposed with multiple isolated DC voltage sources, which provide a modular and scalable approach to designing power converters for various voltage levels [24,25,26]. However, these isolated DC voltage sources are provided through the integration of additional transformers in conjunction with front-end rectifiers. These additional components are often deemed less favorable in light of the heightened complexity, augmented cost, and substantial challenges in terms of control and reliability, thereby contributing to the limited acceptance of these configurations. Consequently, the quest for converters which are capable of mitigating these drawbacks while maintaining a low device count has led to the development of numerous recent topologies.

One of the most established and extensively researched topologies is the five-level hybrid active neutral-point-clamped (5L-ANPC) inverter, which is an extension of the three-level (3L-ANPC) inverter with an additional flying capacitor (FC) unit at each phase [27,28,29]. This topology provides sufficient redundant switching states, which ease the capacitor voltage control and improve the output voltage quality compared to the three-level predecessors. However, the necessity for additional FC units for voltage level extension results in an increase in converter volume.

Another variant of the ANPC family is the four-level hybrid-clamped (4L-HC) inverter. This topology stems from the aforementioned 5L-ANPC inverter with an additional middle DC-link capacitor. This structure provides a number of benefits such as uniform voltage rating at each switch and uniform voltages at the split DC-link and flying capacitors. In addition, the five-level and six-level variants of this topology, namely hybrid flying capacitor (HFC) inverters, have also been developed with resembling structures [30,31,32,33,34]. However, despite the improvement of voltage quality, all of these inverters still exhibit the aforementioned drawback, i.e., they require additional components upon voltage level extension.

Other hybrid topologies such as nested multilevel converters and stacked multi-cell converters have become alternatives to the ANPC family. These topologies have proven to enhance voltage quality by incorporating one or two additional voltage levels in each phase. This is accomplished by introducing commutation cells between the primary inverter structure and the DC-bus capacitors. However, these voltage level extensions come at the cost of either a significantly increased device count or more complicated capacitor balancing control [35,36,37,38,39,40,41,42,43].

The integration of switched-capacitor (SC) circuits into multilevel inverters has also gained prominence in the last decade. These circuits employ capacitors, power switches, and/or diodes to convert a fixed DC-link voltage into multilevel voltage, enabling inductorless and transformerless operation with voltage-boosting capabilities and inherent capacitor self-voltage balancing. Although SC integration in DC-DC converters has been extensively studied and commercialized, the application to multilevel AC-voltage generation is still a growing area of research [44,45,46,47,48]. There are considerations related to component count, complexity, and the large value of current stress imposed by the input DC source which limit the expected power range of these converters.

Lately, there has been a surge of hybrid topologies stemming from diverse multilevel structures and cascaded H-bridge (CHB) submodules, where the primary goal is to generate seven or more levels at each phase leg [3,49,50]. These inverters possess the versatility to scale up to higher voltage levels by modifying the core multilevel structures or by incorporating additional CHB submodules. For instance, a nine-level inverter can be obtained from the combination of a 3L-ANPC inverter with two H-bridge submodules and the combination of a 5L-ANPC with one H-bridge submodule. However, it is important to note that these voltage-level extensions come with an increase in switches and capacitor count, and thus lead to a substantial uptick in the overall volume.

In order to maintain structure simplicity, a more streamlined approach has been taken by combining a three-level cascaded inverter and a CHB submodule at each phase leg [51,52,53]. Through the selective design of DC-bus and flying capacitor voltages, this hybrid cascaded H-bridge (HCHB) structure eliminates the necessity of modifying the core structure or adding more H-bridge submodules for synthesizing a higher voltage level. However, this approach minimizes the device count at the cost of a constrained operating range, where capacitor voltage drifts are expected to take place at various modulation indices and power factors. This issue has hampered the competitiveness of these topologies and become an impediment to widespread adoption across various applications.

In this article, a novel control scheme is presented to overcome operational constraints in various HCHB inverters. The key components which affect capacitor voltage drifts have been analyzed to construct a generalized operating scheme for inverters with various numbers of levels. Analogous to conventional approaches, a proportional offset is injected to the reference voltages to counter the voltage deviation at DC-link capacitors. In order to maintain voltage balance at each flying capacitor and compensate for the lack of redundant switching states, the proposed technique forces the common reference voltage to attain the nearest level within the same cluster which possesses the opposite charging characteristic. With this method, each HCHB inverter can be operated across the complete spectrum of modulation indices and power factors. The effectiveness of the proposed technique is verified through various simulation results and validated in experiments with a downscaled prototype.

2. Overview of HCHB Inverters

In this section, the topological properties and basic operating scheme of HCHB inverters with various number of levels are discussed.

2.1. Circuit Configuration

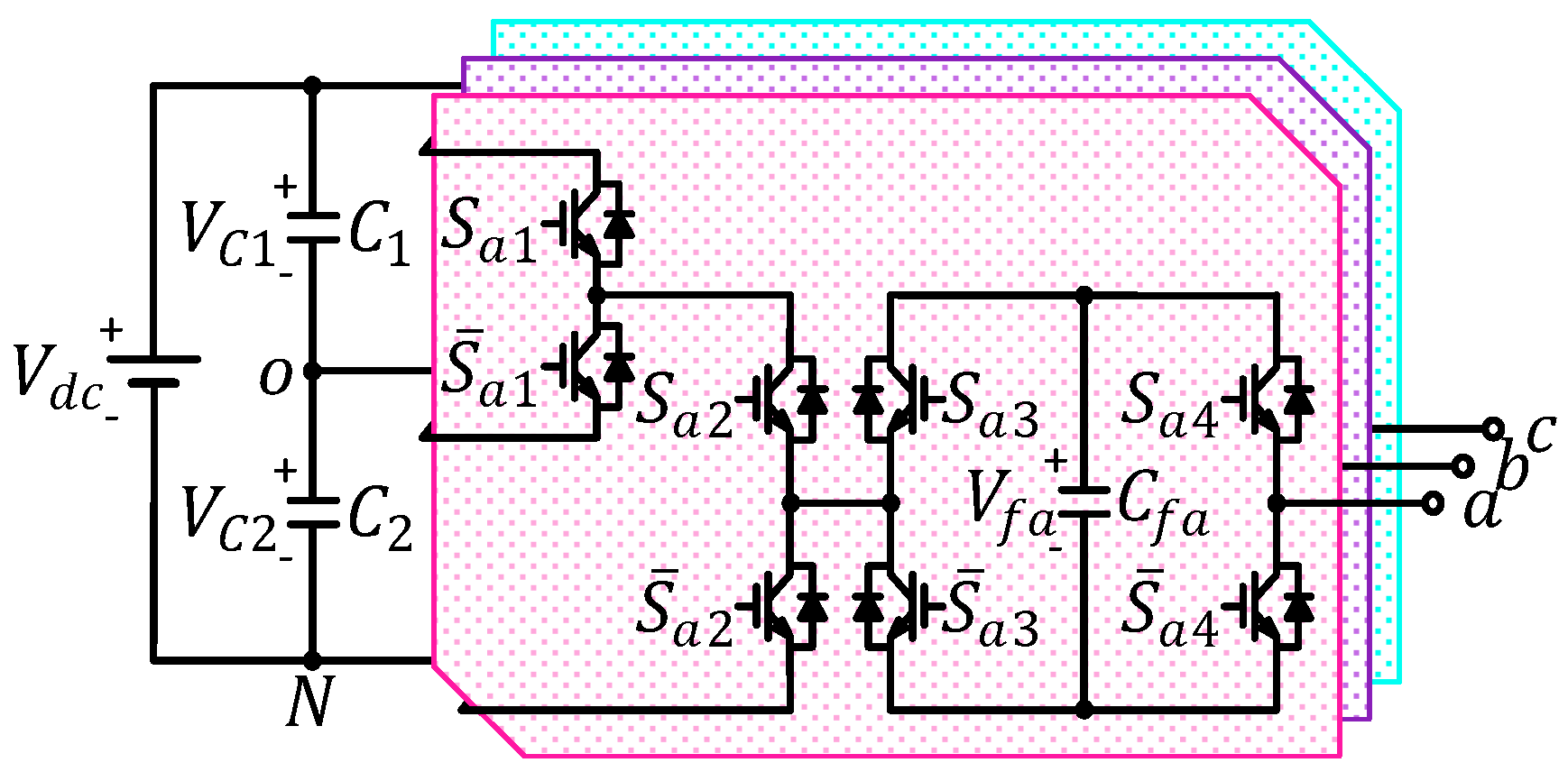

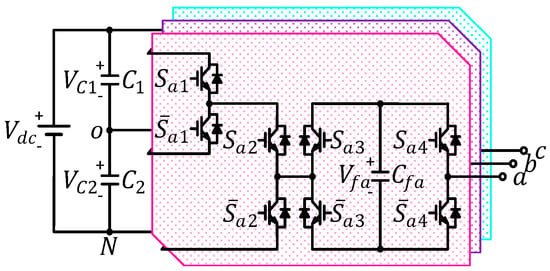

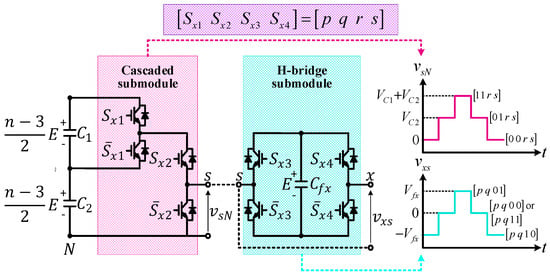

The generalized structure of three-phase hybrid cascaded H-bridge (HCHB) inverters is illustrated in Figure 1. This topology consists of two split DC-link capacitors ( and ), one flying capacitor (), and four pairs of complementary switches at each phase leg (: , , or ).

Figure 1.

Generalized structure of three−phase HCHB inverters.

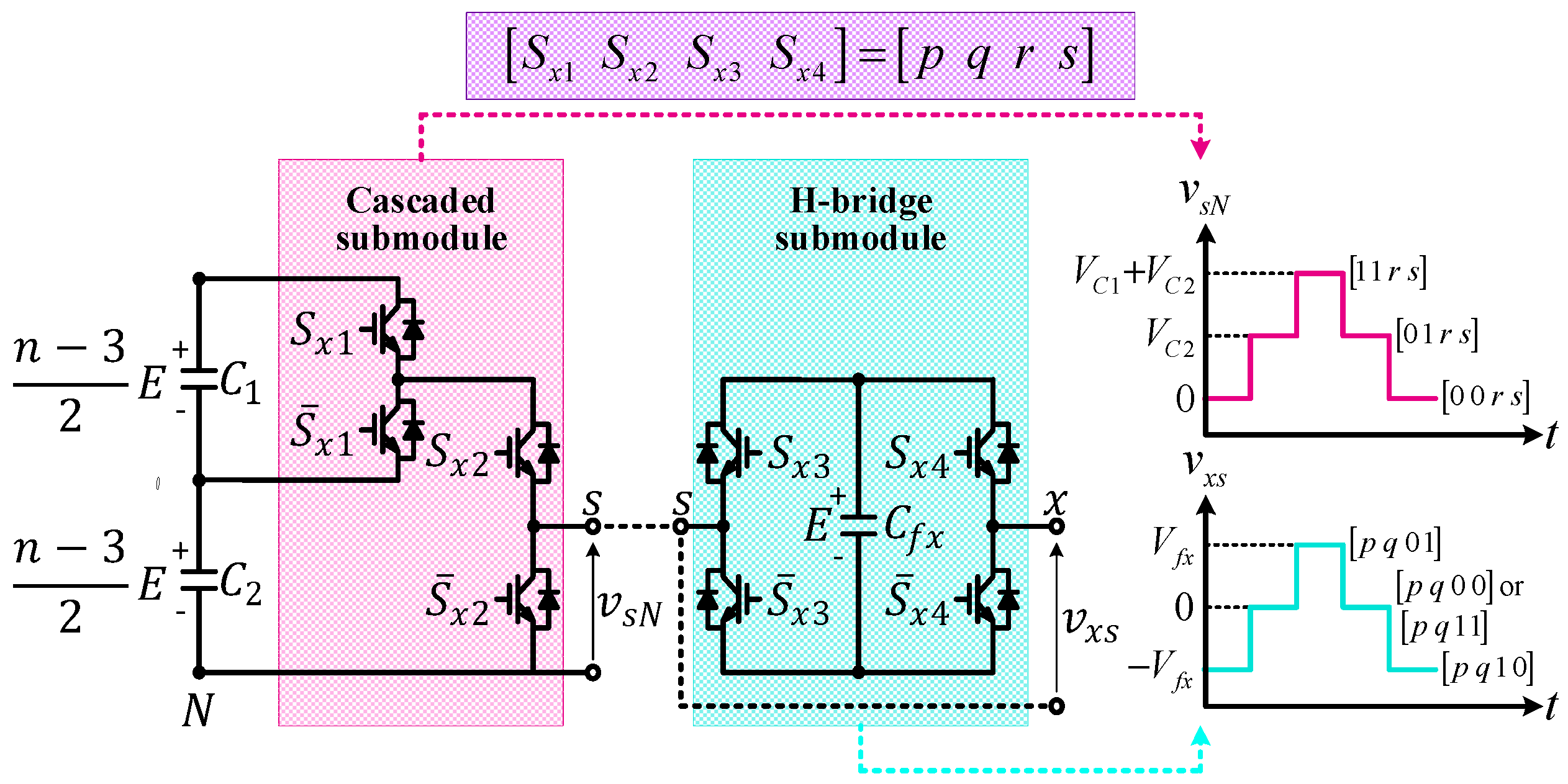

When each phase leg is seen as the combination of one cascaded submodule and one H-bridge submodule, as depicted in Figure 2, the synthesis of output voltage at every phase is defined as follows:

where , , , , and denote the output voltage at each phase leg and the switching status of every semiconductor at phase leg.

Figure 2.

Voltage synthesis for n−level HCHB inverters according to switching patterns at cascaded and H-bridge submodules.

2.2. Generalized Switching Pattern

The combination of both cascaded inverter and H-bridge submodules generates up to 12 switching states, as listed in Table 1, where the direction of current flowing through each of the split DC-link and flying capacitors (, , and ) varies according the polarity of the output current (). Since each of the submodule output voltages, namely and , generates three levels of voltage, the maximum and minimum numbers of levels generated at each phase leg are nine and five, respectively.

Table 1.

Generalized switching states pattern for HCHB inverters.

2.2.1. Voltage Synthesis for Five-Level Inverter

In order to generate five-level output voltage at every phase, the capacitor voltages should be configured in such a way that switching events at H-bridge submodules only contribute two additional switching states to the available three switching states generated by cascaded submodules. This is achieved by constructing the capacitor voltages as follows:

where , , , , and are the voltages of split DC-link capacitors and flying capacitor, the DC-bus voltage, and base voltage of the inverter. Therefore, the maximum amplitude of pole voltage () is or , which is two times as high as that of the conventional buck inverters (). Meanwhile, every switch sustains the same voltage stress at .

2.2.2. Voltage Synthesis for Seven-Level Inverter

Synthesis of a higher number of levels requires an adjustment of the split DC-link capacitor voltages, whereas those of the flying capacitors are maintained at the base voltage to keep the total capacitor voltages low. In order to achieve seven-level output voltage at every phase, the capacitor voltages should be controlled as follows:

The maximum amplitude of pole voltage is or , which is 1.5 times as high as that of the conventional buck inverters. Meanwhile, the switches at the cascaded and H-bridge submodules should sustain the voltage stress at and , respectively.

2.2.3. Voltage Synthesis for Nine-Level Inverter

In order to achieve nine-level output voltage, which is the maximum level available for this inverter structure, the capacitor voltages should be regulated in such a way that all switching states should be designed to generate unique without any overlapping voltages. Therefore, the capacitor voltages are arranged as follows:

With this configuration, the maximum amplitude of pole voltage is or , which is 1.33 times as high as that of the conventional buck inverters. The voltage stresses of switches at the cascaded and H-bridge submodules are and , respectively.

2.2.4. Generalized Voltage Synthesis for HCHB Inverters

Each of the HCHB configurations discussed above generates odd-level output voltage. As a general pattern, the capacitor voltages are formulated as follows:

where denotes the number of levels. For odd-level inverters, the value of each split DC-link capacitor is always an integer which is multiplied with the base voltage. Meanwhile, the multiplier value for even-level inverters is always a non-integer, which results in non-uniform voltage steps at the staircase waveforms. To address this issue, the values of both and should be rounded up and down to the nearest integers in such a way that the sum is still equal to . Therefore, each of these even-level inverters can be constructed with two configuration options, as given in Table 2. Note that the pole voltages of even-level inverters exhibit asymmetric waveforms due to the uneven voltage distribution at the split DC-link capacitors.

Table 2.

Comparison of various HCHB inverters.

Since the voltages of split DC-link capacitors of most HCHB inverters are higher than those of the flying capacitors, the voltage stress of each switch in the cascaded submodule is also higher than those of the H-bridge submodule. In addition to producing lower voltage steps () at each phase leg, the inverters with a higher number of levels also exhibit lower total standing voltages (TSV) due to the lower voltage stress at H-bridge submodules, as listed in Table 2.

2.3. Operating Range Limits

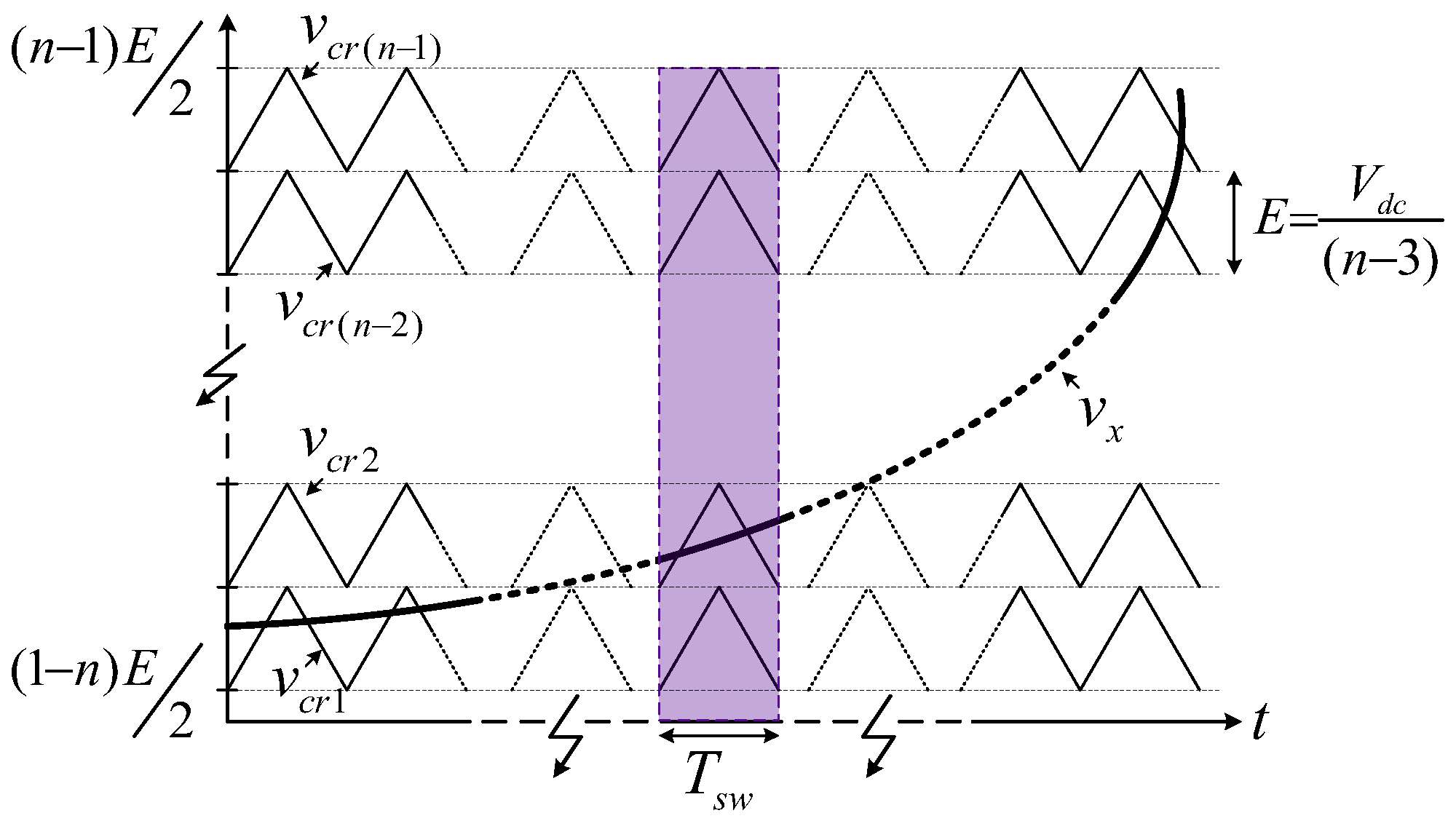

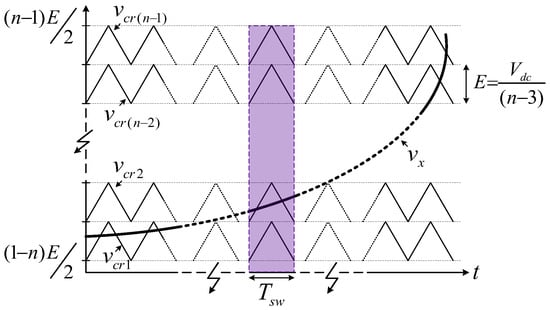

In the previous study [52], a three-phase 7L-HCHB inverter was developed and operated with an in-phase disposition level-shifted multicarrier PWM (IPD-LSPWM), as illustrated in Figure 3. In this technique, the voltage reference at each phase leg is compared with the carrier waveforms () to determine the switching of each device [54].

Figure 3.

In-phase disposition level-shifted multicarrier PWM (IPD-LSPWM) for n-level HCHB inverters.

Suppose that the voltage and current at each phase leg for various -level inverters, which are denoted by and , are defined as follows:

where , ,, , , , , and denote the amplitudes of pole voltage and output current, operating frequency, amplitude and frequency modulation indices, fundamental angular frequency, initial phase angle, and the phase angle between and , respectively.

Since the staircase voltages are formed by the DC-link and flying capacitor voltages, the voltage balance of each capacitor needs to be maintained. The operating range limitation in seven-level inverters has been analyzed by deducing the accumulated charge variation in each flying capacitor during half of the fundamental cycle, where it has been concluded that these topologies can be operated only at . Meanwhile, the split DC-link capacitor voltages are theoretically capable of self-balancing due to the symmetry in the polarity of phase current over one fundamental cycle. Nevertheless, the implementation of closed-loop control for voltage balancing is necessary to mitigate voltage drifts in the real environment with dynamic conditions [50,51,52].

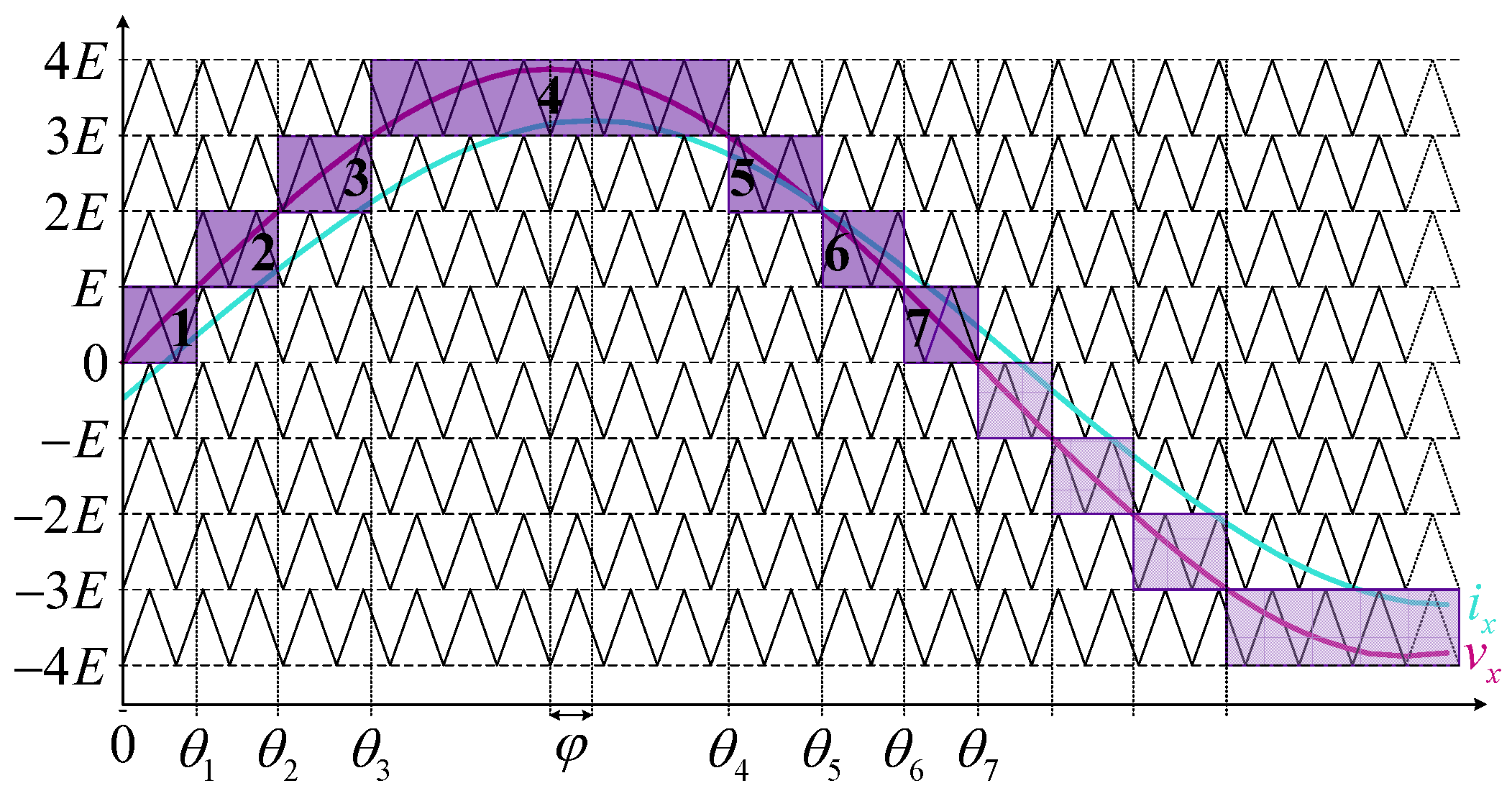

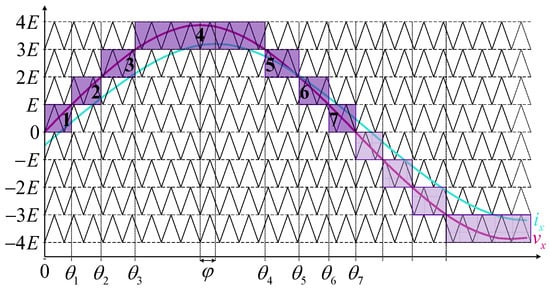

A similar approach can be applied to analyze the balancing capability of any -level HCHB inverter. For instance, the output voltage and current of a 9L-HCHB inverter are illustrated in Figure 4, where the staircase waveform during half of the fundamental cycle can be divided into seven areas. The demarcation angle for each area can be calculated based on the geometrical correlation as follows:

where and denote the final demarcation angle of area and the period of fundamental wave, respectively.

Figure 4.

Output voltage and current at each phase leg of 9L-HCHB inverter during a half of the fundamental cycle.

The accumulated charge variation in each area can be calculated as follows:

where , , and denote the charge variation at area , total charge variation during half of the fundamental cycle, and the average current that flows into the flying capacitor at area . The value of is calculated according to the conduction path in area in correlation with the output current. For instance, charge variations in 9L-HCHB inverter are obtained as follows:

A conclusion regarding the capacitor balancing capability can be obtained by summing up the entire charge variations, where must be positive to maintain the capacitor charge balance under IPD-LSPWM.

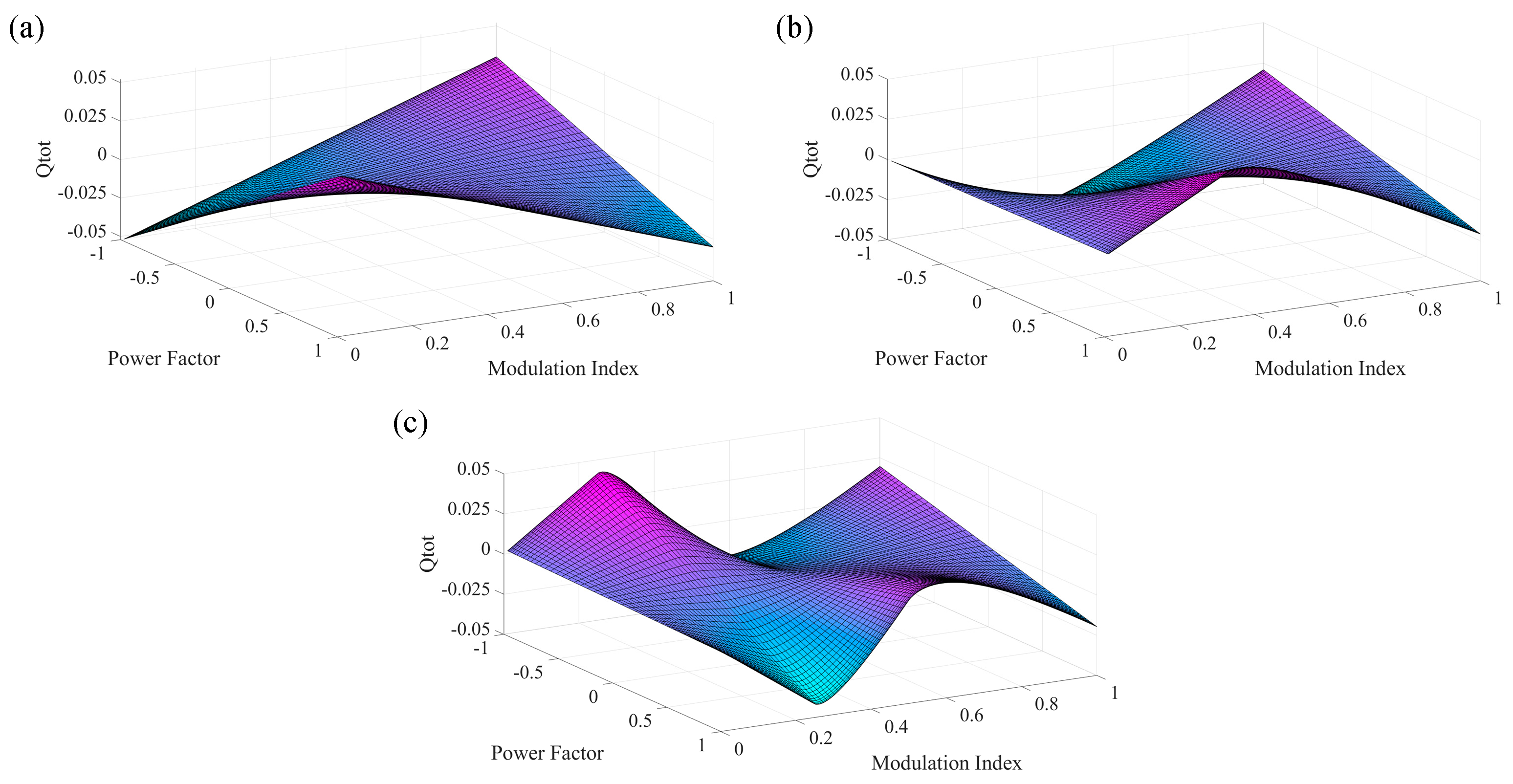

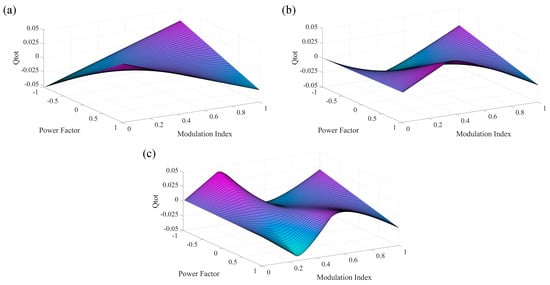

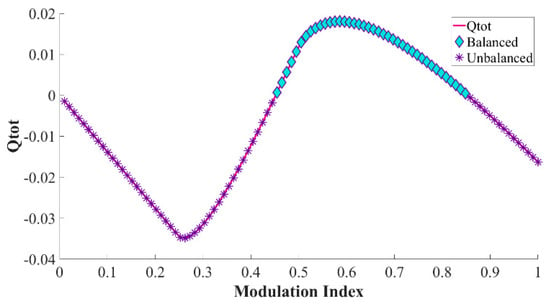

In order to observe the operating range limit of various HCHB inverters, the values of have been calculated and plotted in Figure 5 by assuming that the fundamental operating frequency and output current amplitude are set at = 60 Hz and = 10 A.

Figure 5.

Accumulated charge variation in each flying capacitor during half of the fundamental cycle at various modulation indices and power factors. (a) 5L−HCHB. (b) 7L−HCHB. (c) 9L−HCHB.

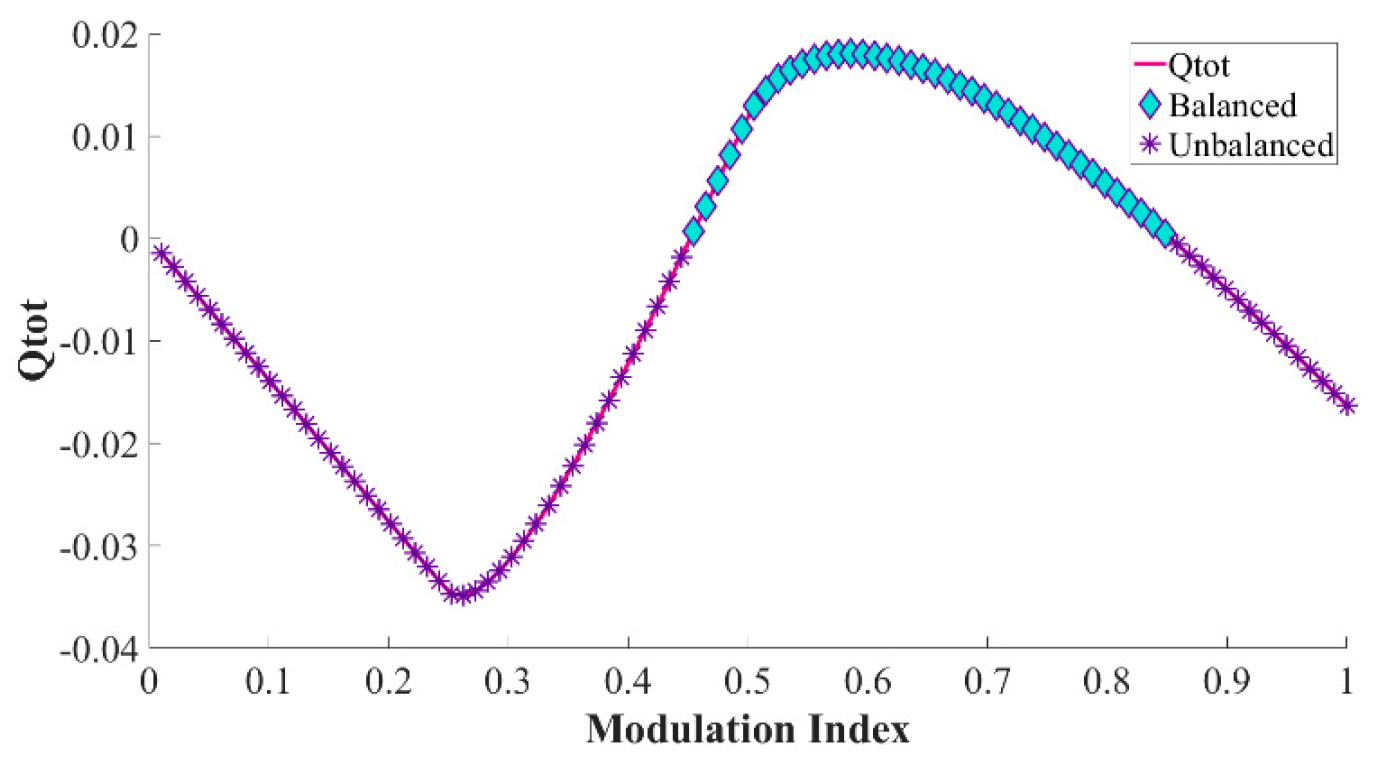

Note that only determines the amplitude of , whereas the polarity remains identical. Since the value of in each graph is not always positive, voltage drifts are expected to take place in any -level HCHB inverter when it is operated at various modulation indices and power factors. For instance, consider the charge variation in the flying capacitors of 9L-HCHB inverter for cos () = 0.83, as illustrated in Figure 6. In this case, the value of is negative at 0.45 and 0.84, where voltage imbalance is expected to occur. Such operating range limits adversely negate the benefit this structure offers, i.e., flexibility to increase the number of levels, and thus diminish the competitiveness of this topology.

Figure 6.

Accumulated charge variation in each flying capacitor of 9L−HCHB inverter at PF = 0.83.

A number of control balancing techniques that are commonly used in various multilevel inverters have been listed in Table 3. Despite the effectiveness, none of these techniques satisfy the requirement of capacitor voltage balancing in the HCHB inverters without adversely affecting the output voltage quality, increasing the computational burden, or increasing the device count of the inverter.

Table 3.

Common capacitor voltage balancing methods for multilevel inverters.

3. Proposed Balancing Control Scheme

In the previous section, the problem with operating range limit has been discussed. In order to solve this issue, a novel control is proposed by injecting two separate offsets into the reference voltage at each phase ().

3.1. Control of DC-Link Capacitor Voltages

The structure of HCHB inverters position the DC-link capacitor voltages as significant contributors to the formation of pole voltage at each phase leg. Since the values of and should be regulated at for odd-level inverters and the nearest integers for even-level inverters, a simple control scheme has been modified to maintain the error of either or within the allowable range. Table 1 shows how the switching states in any -level HCHB inverter provide similar conduction paths to discharge the voltages of and as the reference voltage is controlled at certain levels. In order to control these capacitor voltages, a proportional offset voltage is injected to as follows:

where and denote the actual and reference voltage error between and , whereas , , and denote the offset voltage, proportional control gain, and the maximum allowable error percentage. Typically, adhering to a general guideline, the peak-to-peak capacitor voltage ripple should be kept within 10% of the corresponding reference [61,62].

3.2. Control of Flying Capacitor Voltages

As mentioned above, each flying capacitor voltage should be regulated at the base voltage (). Since voltage drift is expected to occur at certain modulation indices and power factors, a controller is needed to counter the deviation. Suppose that the voltage error is defined as follows:

where denotes the calculated error between actual and reference flying capacitor voltages.

Table 1 shows the topological characteristic of HCHB inverters, where the polarity of flying capacitor current varies within half of the fundamental cycle. Since the switching state redundancy is not sufficient to correct the voltage drifts at certain modulation indices and power factors, a common offset voltage, namely , should be injected to force to the nearest switching states with the opposite current polarity. Since is commonly shared among the reference voltages at all phase legs, a number of common parameters should be defined as follows:

where the value of , which is obtained by sorting the absolute values of voltage errors across all phase legs, is also used to determine the common output current () and the common voltage reference (). The value of is classified into several clusters, each of which consists of at least two points which correspond to with opposite charging or discharging characteristics, namely and , respectively. If the maximum allowable error percentage for every flying capacitor voltage is denoted by , the offset voltage should be generated whenever exceeds , as follows:

An example of how is obtained for a 9L-HCHB inverter is given in Table 4, where is classified into four clusters. The value of in cluster I corresponds to three voltage levels at , i.e., , , and , where and . If the capacitor voltage is overcharged during positive , the reference voltage of the phase with the highest error is forced to reach to discharge the capacitor. Contrarily, the reference should be forced to reach to restore the voltage of an undercharged capacitor. Note that the actions should be reversed during negative . The same principle is applied to the other clusters and other -level CHCB inverters.

Table 4.

Offset injection for regulating flying capacitor voltages in 9L-HCHB inverter.

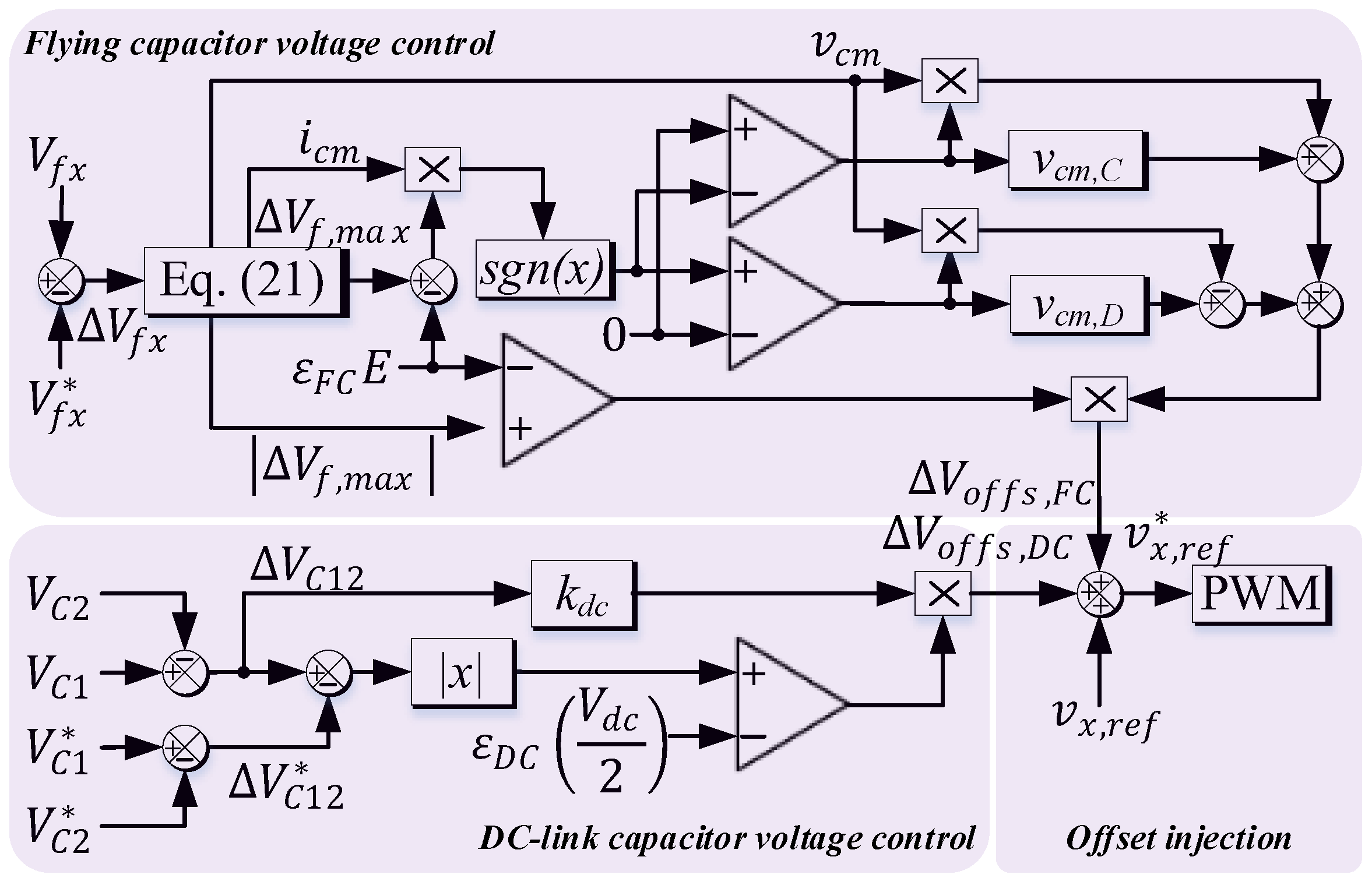

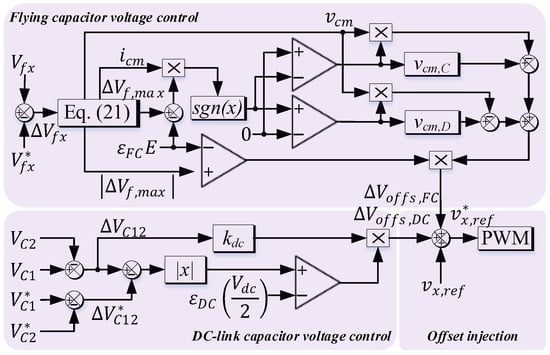

3.3. Summary of Proposed Balancing Scheme

From the previous section, it can be concluded that two independent offset voltages should be generated to regulate the split DC-link and flying capacitor voltages as follows:

where the new voltage reference at each phase leg is denoted by . This new reference is compared with the normalized carrier waveforms () under the IPD-LSPWM technique to generate the switching signals of all devices according to the corresponding switching states in Table 1. Figure 7 shows the control block diagram of split DC-link and flying capacitor voltages. With this generalized control scheme, all capacitor voltages are regulated at the corresponding references, and thus keep the voltage THD low, particularly at HCHB inverters with a higher number of levels [63,64,65,66].

Figure 7.

Control block diagram of HCHB inverters.

4. Simulation Results

In order to verify the effectiveness of this balancing control technique for various HCHB inverters, a number of simulations have been carried out for five-level, seven-level, and nine-level HCHB inverters. The parameters used for this simulation are listed in Table 5. The peak voltage ripple of each capacitor is controlled within 10% of the reference.

Table 5.

Parameters for simulation.

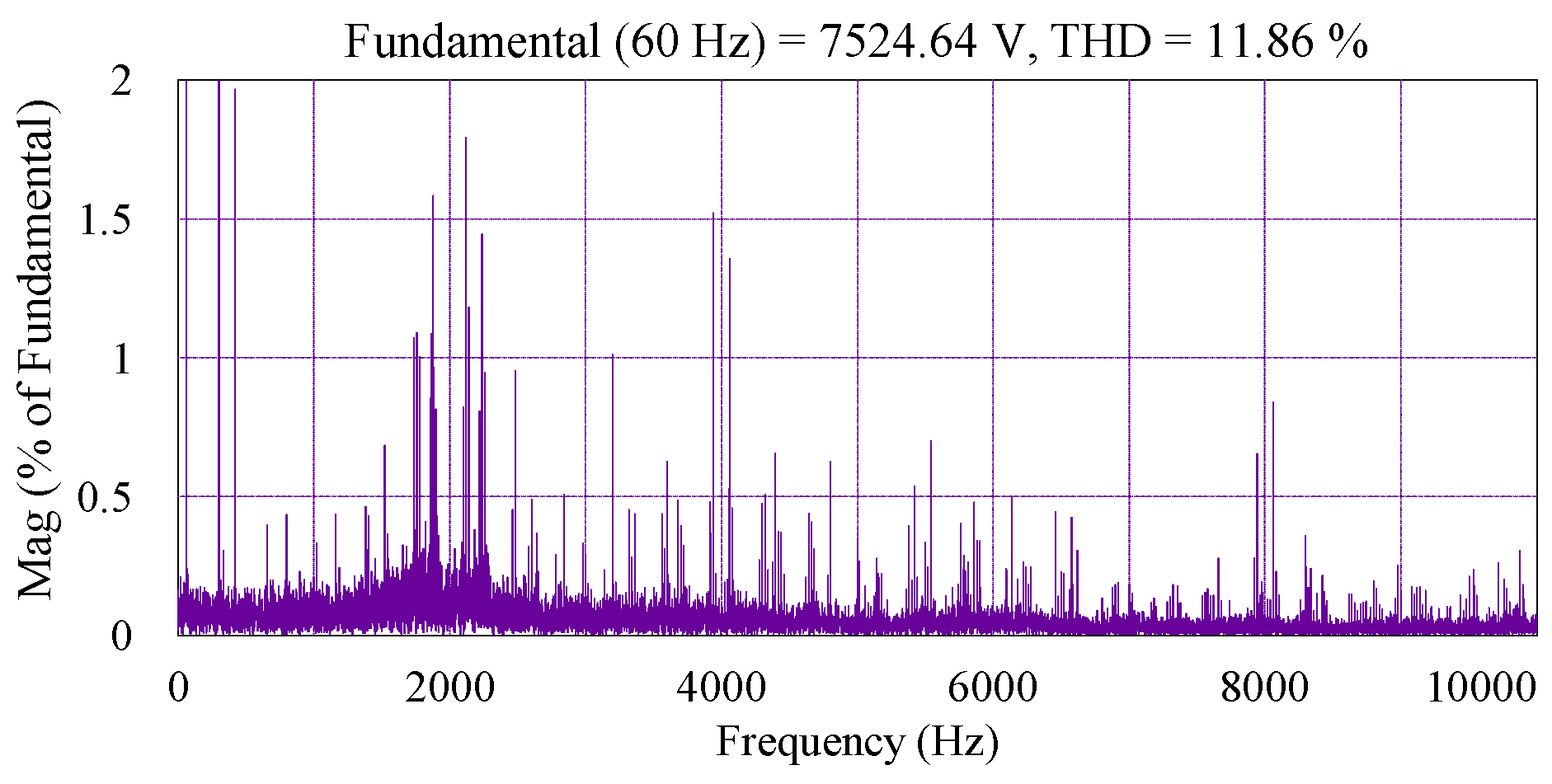

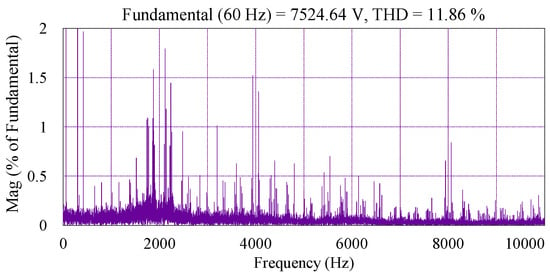

The performance of a 9L-HCHB inverter during a steady state in the unity modulation index is shown in Figure 8, where both pole and line voltages exhibit the maximum number of levels. In order to maintain the capacitor voltages, the reference voltage at each phase leg () is injected with the offset voltage (), and thus results in the generation of a new reference voltage (). DC-link and flying capacitor voltages are regulated at 3500 V and 1166.67 V, respectively, where the maximum ripples are 2.37% and 5.07% of the references, respectively. The harmonic spectrum of line voltage is shown in Figure 9, where the THD is 11.86%.

Figure 8.

Performance of 9L-HCHB inverter at unity modulation index. (a) Reference voltages. (b) Offset voltage. (c) Pole voltage. (d) Line voltage. (e) Split DC-link capacitor voltages. (f) Flying capacitor voltages. (g) Output currents.

Figure 9.

Harmonic spectrum of line voltage of 9L-HCHB inverter at unity modulation index.

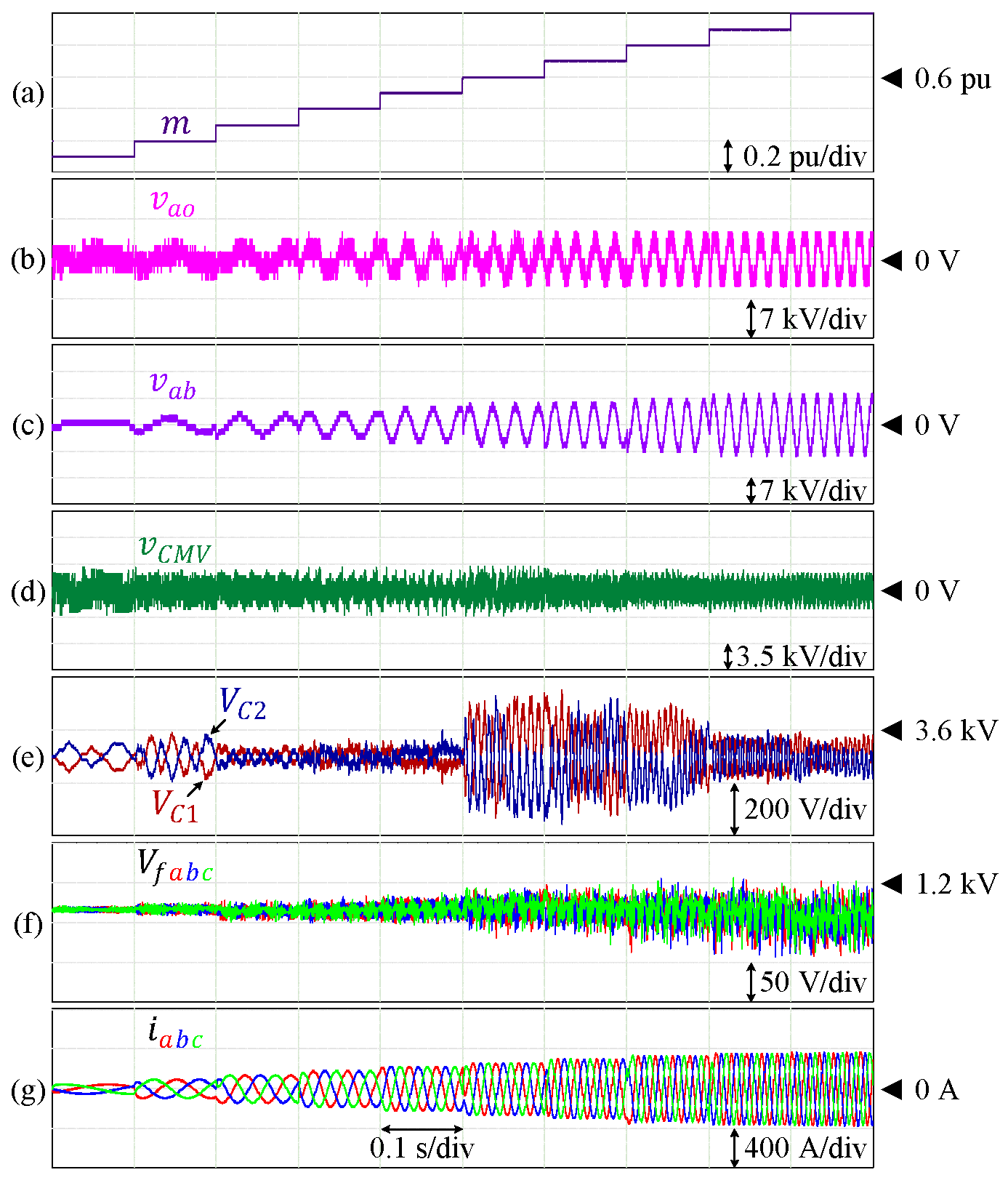

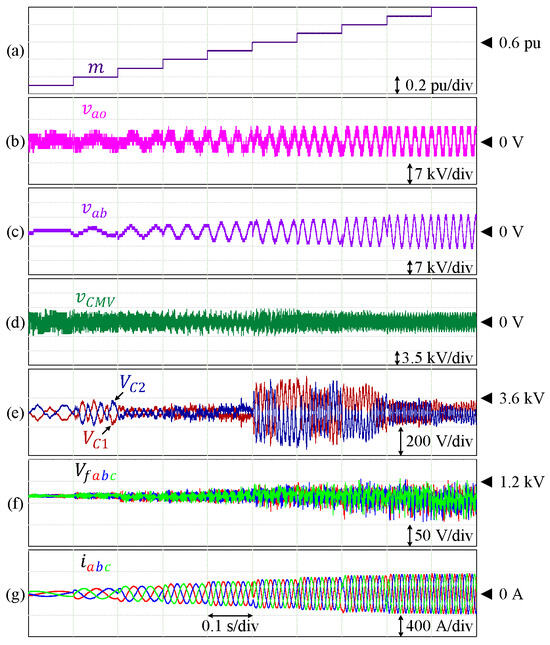

As discussed earlier, the flying capacitor voltages are expected to drift at certain modulation indices under the conventional scheme. Figure 10 shows the performance of this 9L-HCHB inverter at various amplitude and frequency modulation indices ( = = ) under the proposed balancing control. Each of the DC-link and flying capacitors is regulated at the corresponding reference, where the maximum voltage ripples are 7.21% and 5.06% of the references, respectively.

Figure 10.

Performance of 9L-HCHB inverter at various modulation indices. (a) Modulation index. (b) Pole voltage. (c) Line voltage. (d) Common-mode voltage. (e) Split DC-link capacitor voltages. (f) Flying capacitor voltages. (g) Output currents.

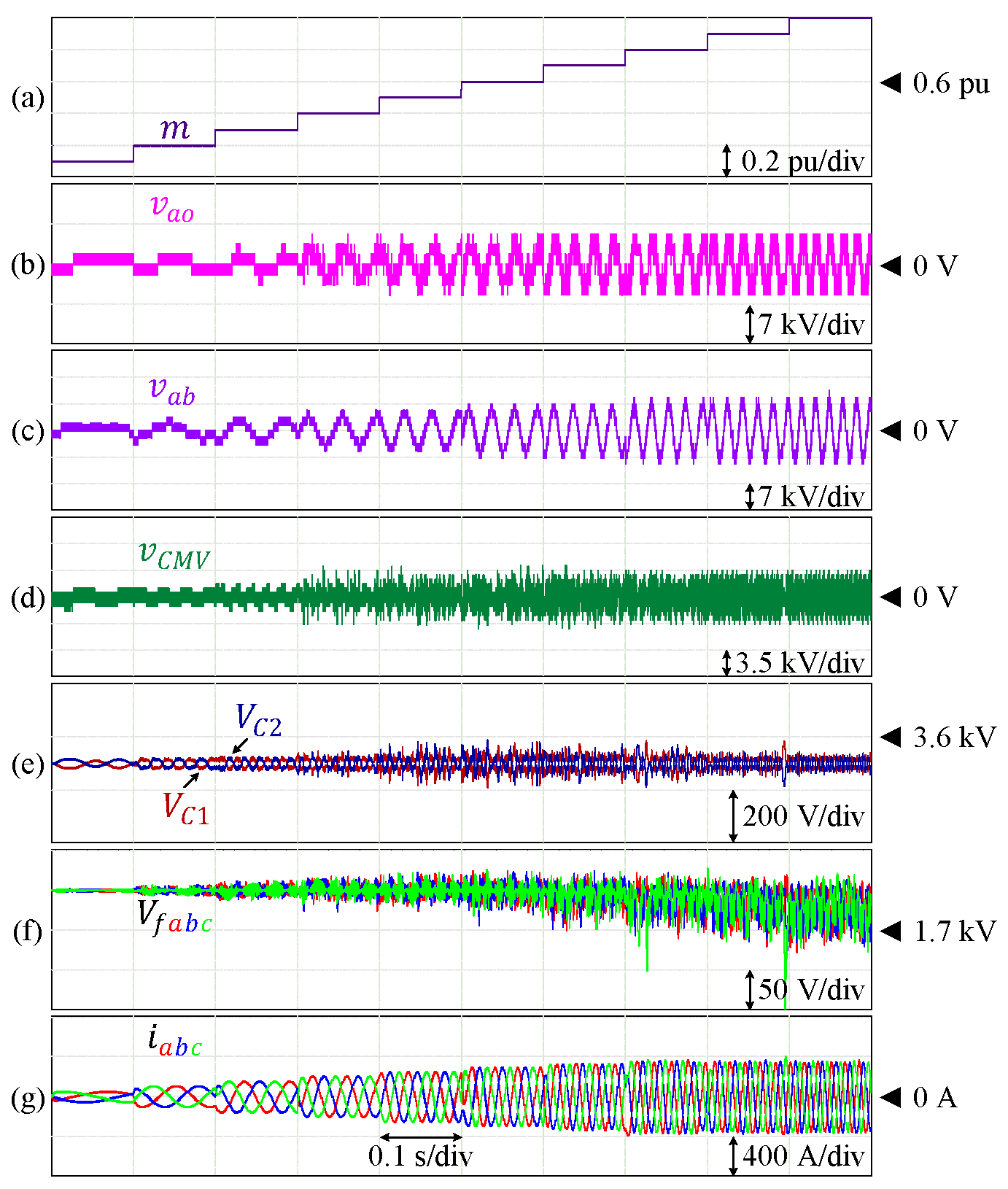

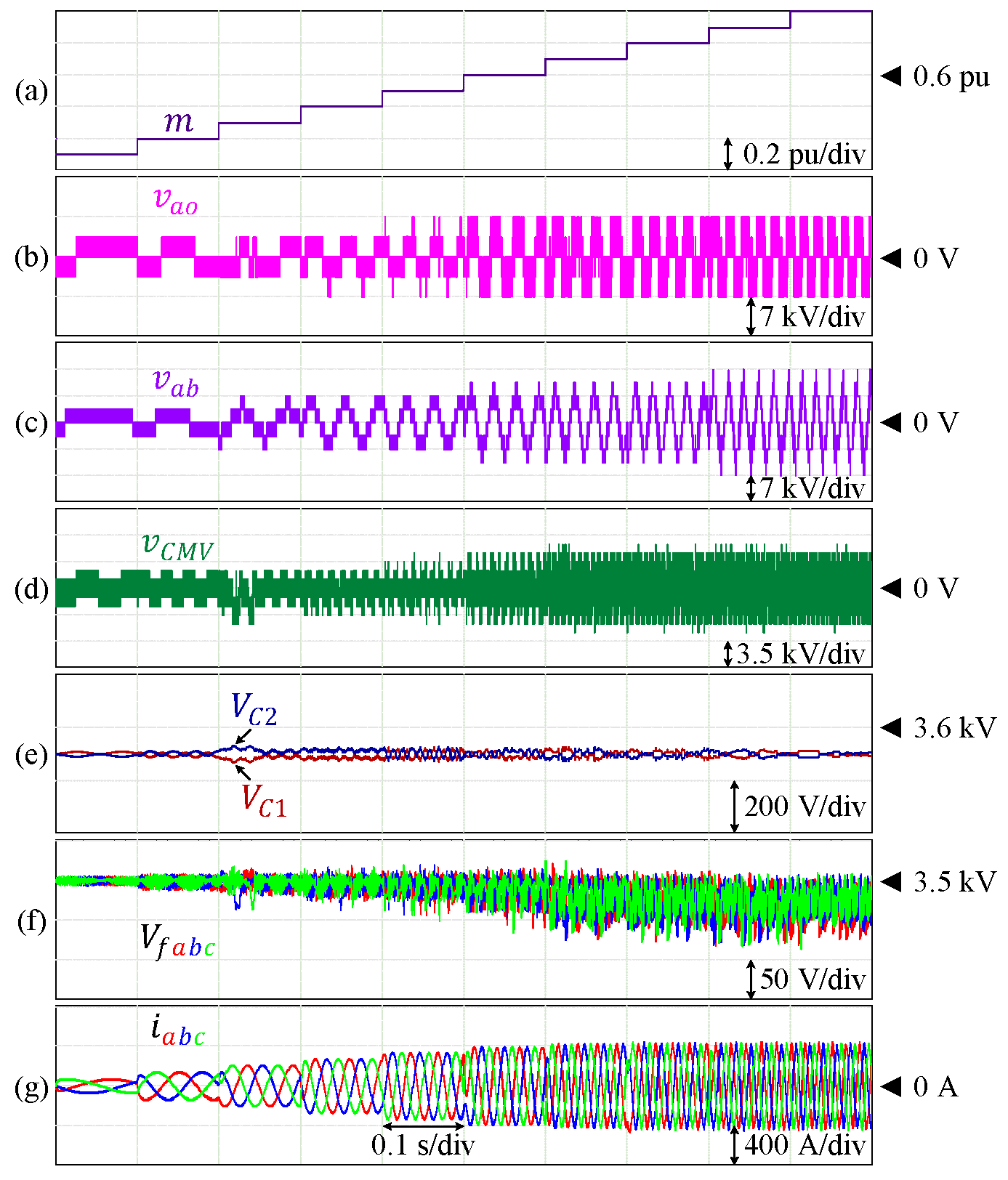

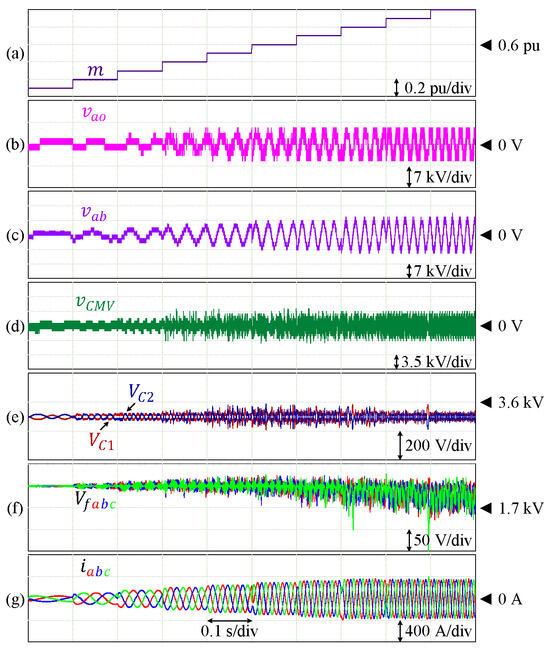

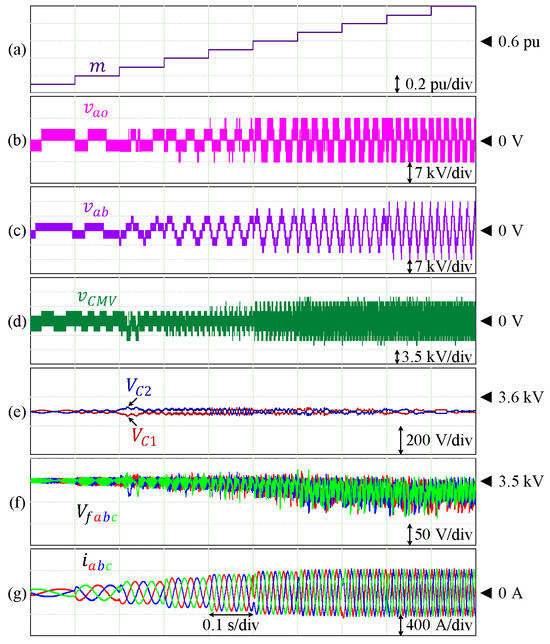

The effectiveness of this control technique has also been verified for other HCHB inverters with a lower number of levels. Figure 11 shows the performance of a 7L-HCHB inverter under various modulation indices, where the voltages of the DC-link and flying capacitors are maintained at 3500 V and 1750 V, respectively. The maximum voltage ripples of the DC-link capacitors are 2.49% of the reference, whereas those of the flying capacitors are 8.62% of the reference, respectively. A similar simulation has also been conducted for a 5L-HCHB inverter as shown in Figure 12, where each capacitor voltage is maintained at 3500 V. The maximum voltage ripples at the DC-link and flying capacitors are 0.93% and 2.33% of the references, respectively.

Figure 11.

Performance of 7L-HCHB inverter at various modulation indices. (a) Modulation index. (b) Pole voltage. (c) Line voltage. (d) Common-mode voltage. (e) Split DC-link capacitor voltages. (f) Flying capacitor voltages. (g) Output currents.

Figure 12.

Performance of 5L-HCHB inverter at various modulation indices. (a) Modulation index. (b) Pole voltage. (c) Line voltage. (d) Common-mode voltage. (e) Split DC-link capacitor voltages. (f) Flying capacitor voltages. (g) Output currents.

The common-mode voltages () at HCHB inverters with a lower number of levels are higher due to the higher amplitude of pole voltages and voltage steps (). The fluctuation of in 9L-HCHB, 7L-HCHB, and 5L-HCHB inverters are presented in Figure 10d–Figure 12d, where the amplitudes are 46.40%, 58.71%, and 83.29% of , respectively. Meanwhile, the root-mean-square (RMS) values are 16.74%, 20.25%, and 36.02% of , respectively.

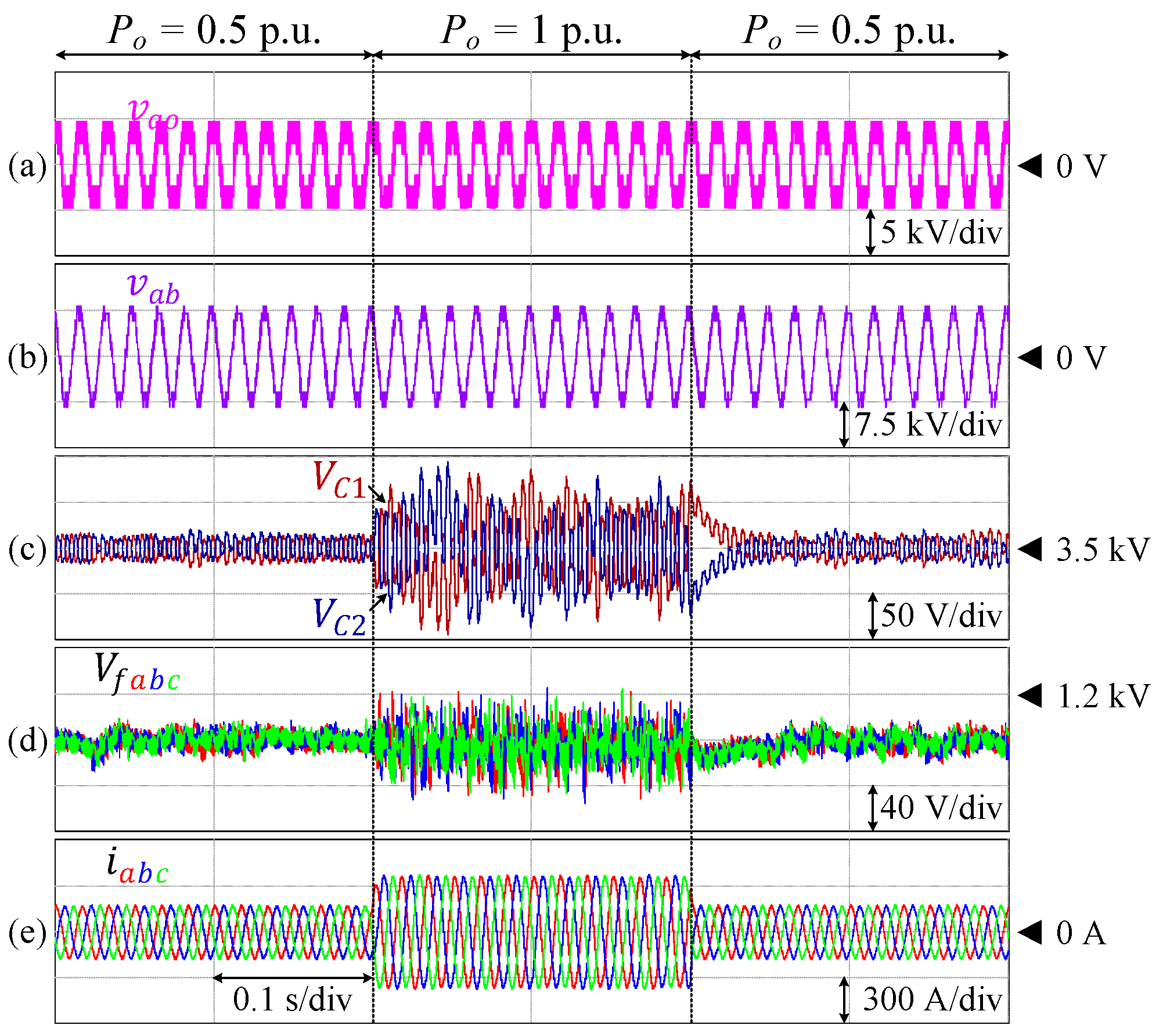

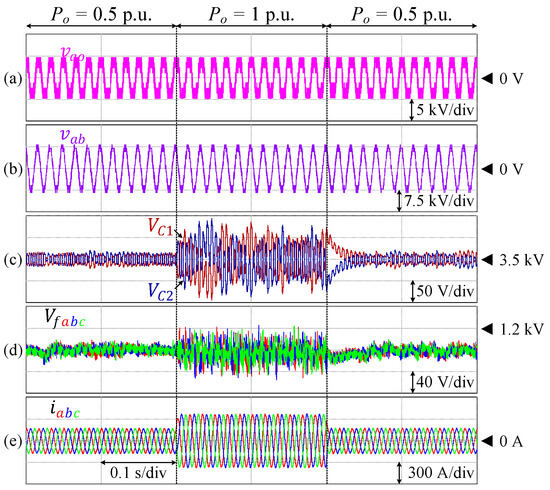

The proposed control technique has also been verified for operation under dynamic load changes, as presented in Figure 13. In this case, the load of a 9L-HCHB inverter varies between 50% of the rated load ( = 0.53 p.u. = 1.03 MW) and the rated load ( = 1 p.u. = 1.94 MW). Each of the DC-link and flying capacitor voltages manage to be controlled with low fluctuation, where the maximum voltage ripples are 2.67% and 4.90% of the references, respectively.

Figure 13.

Performance of 9L-HCHB inverter under dynamic load changes. (a) Pole voltage. (b) Line voltage. (c) Split DC-link capacitor voltages. (d) Flying capacitor voltages. (e) Output currents.

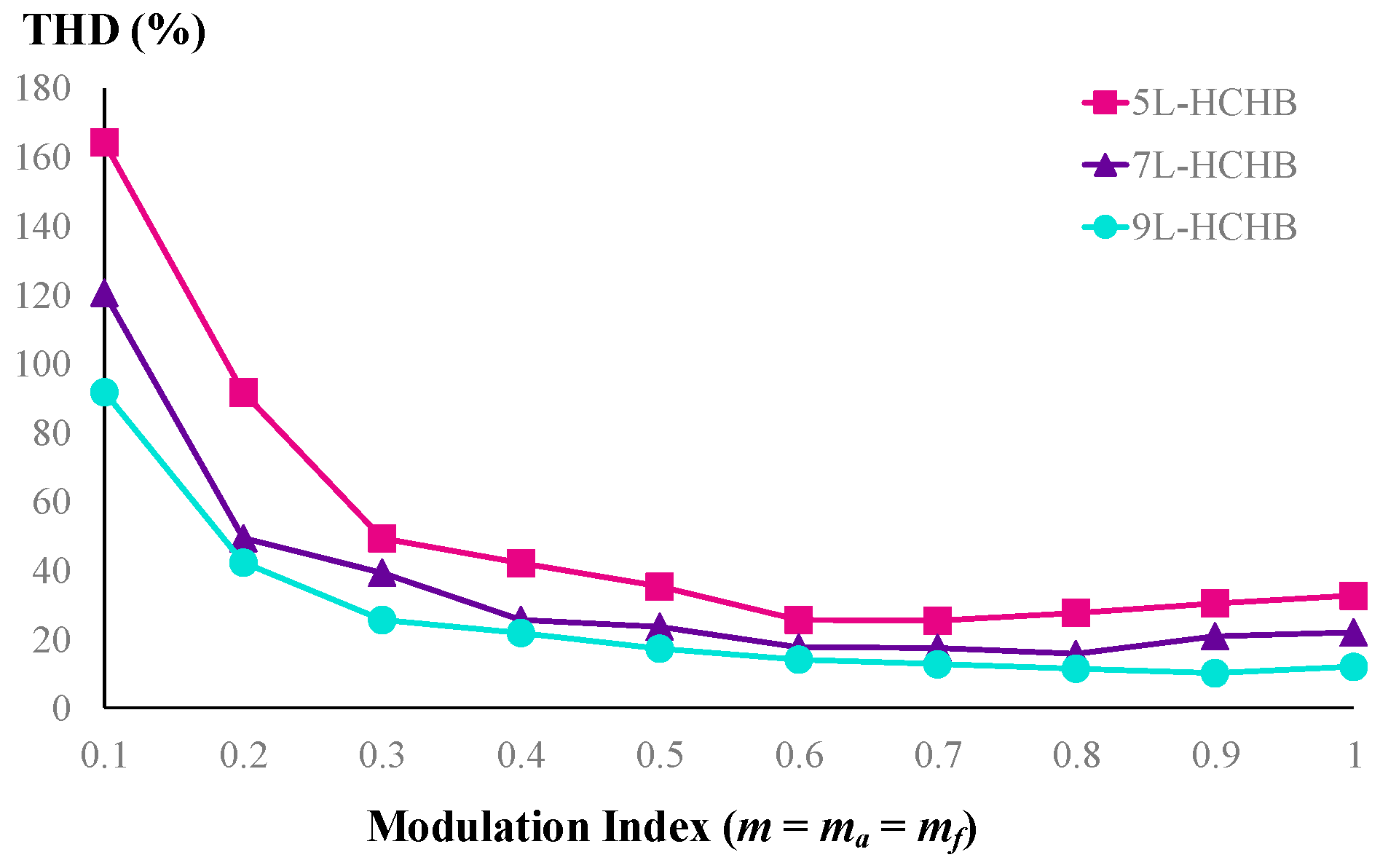

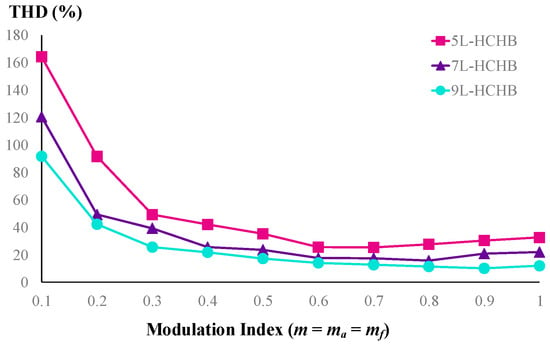

A comparison of the THD values of line-to-line voltages at these odd-level HCHB inverters under various modulation indices is depicted in Figure 14. Since the inverter with a higher number of levels generates lower and more sinusoidal voltage, the THD values are also lower at all modulation indices. For instance, the THD of five-level, seven-level, and nine-level HCHB inverters under unity modulation index are 32.51%, 21.89%, and 11.86%, respectively.

Figure 14.

THD of line voltages at odd-level HCHB inverters.

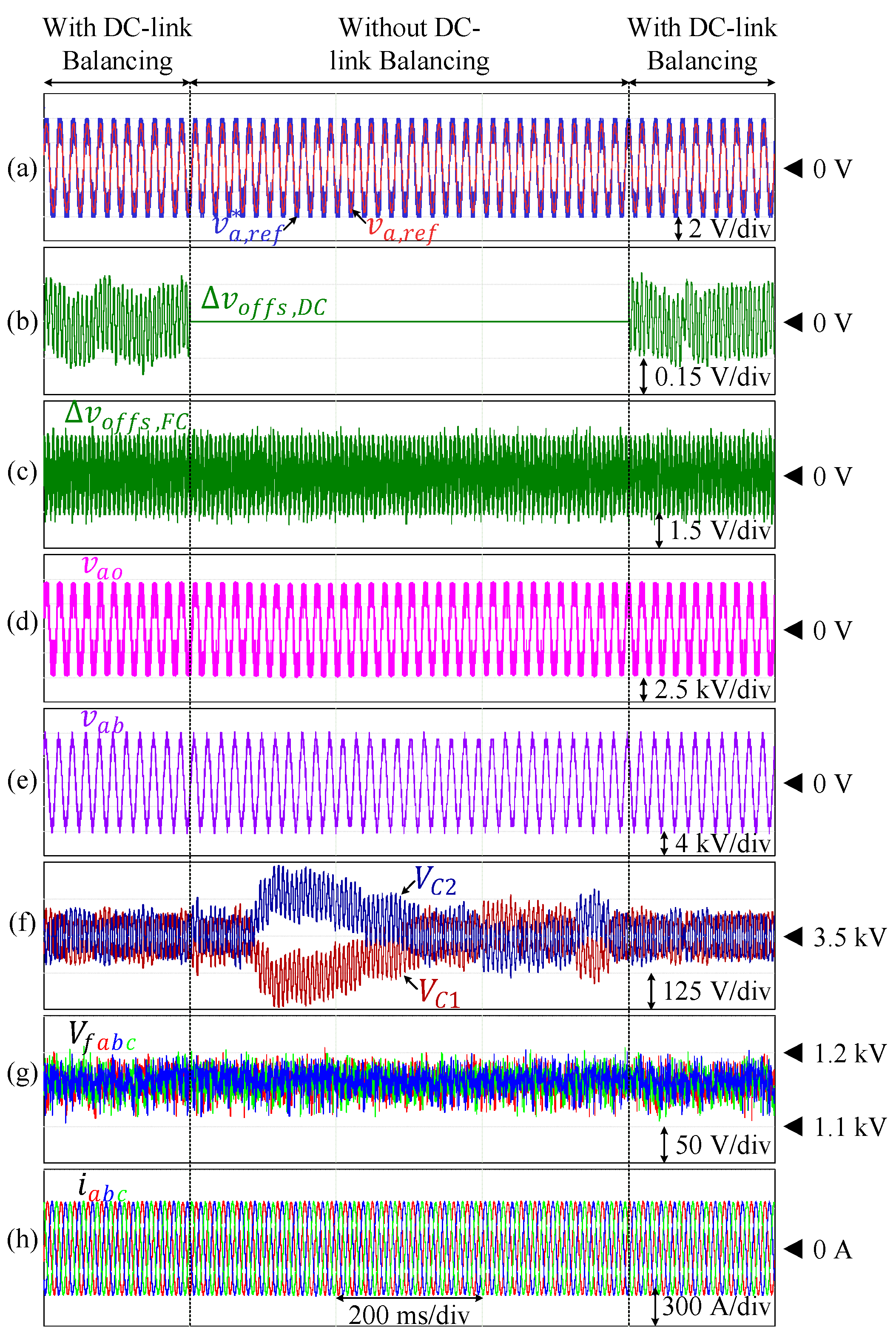

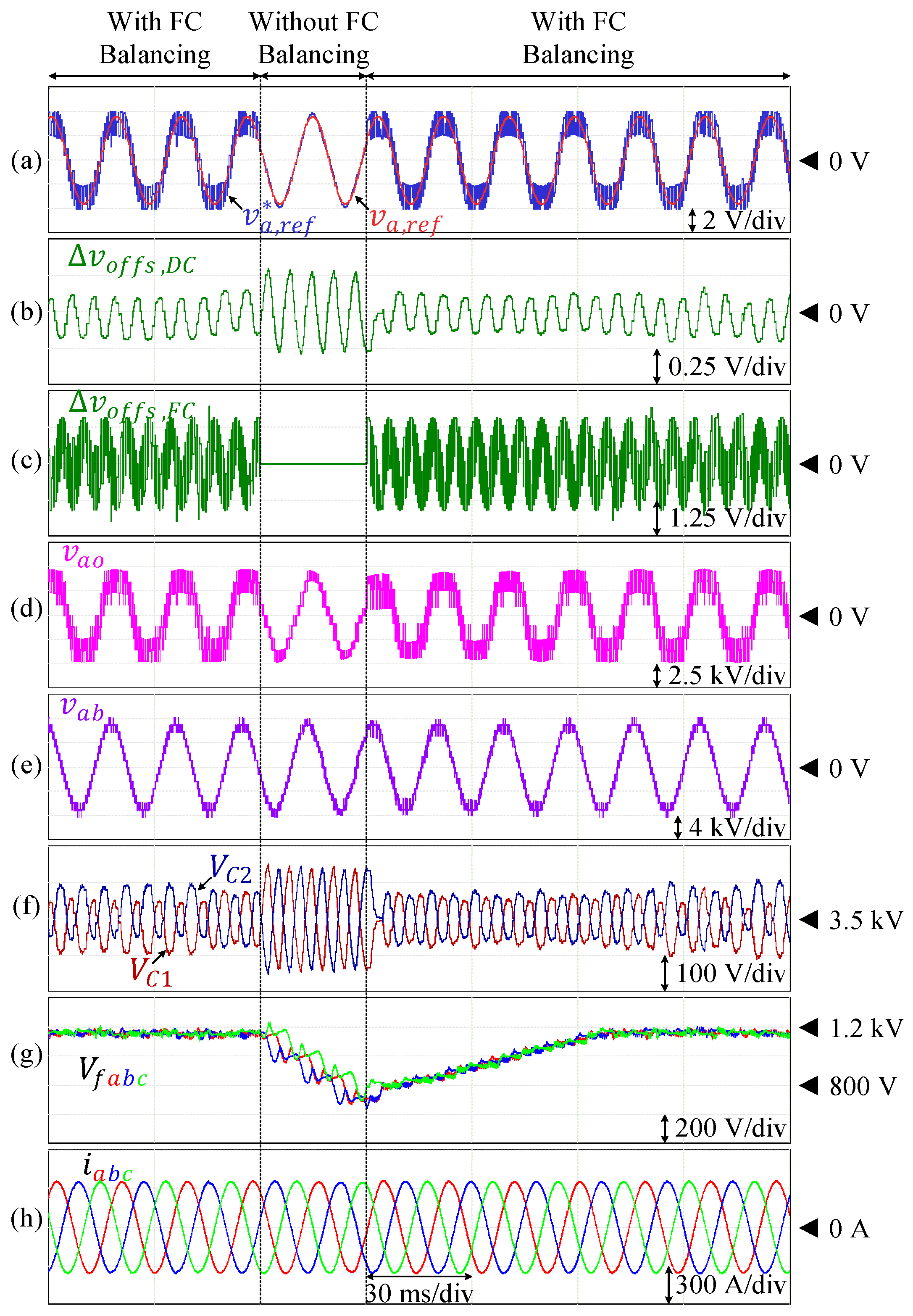

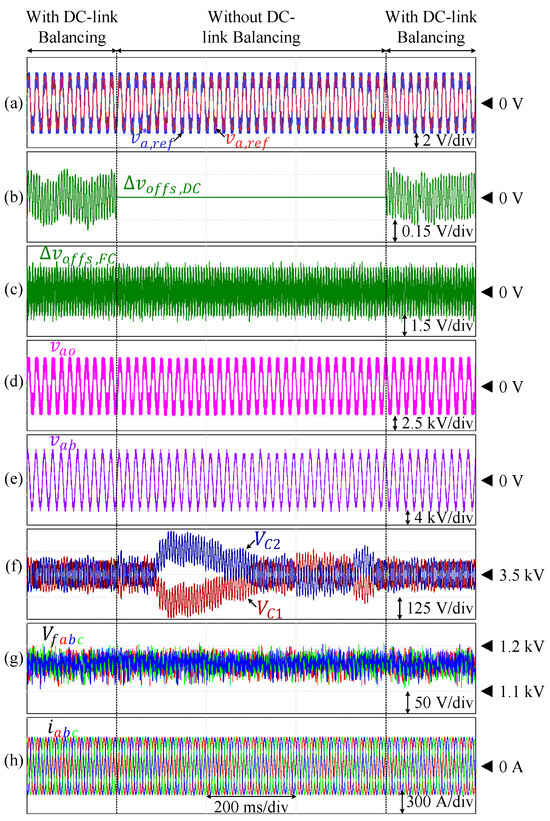

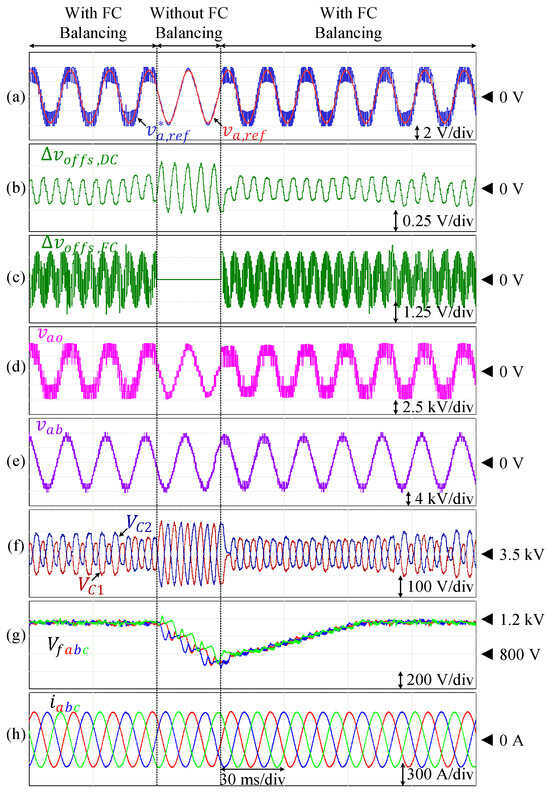

As discussed earlier, the split DC-link capacitor voltages are theoretically capable of self-balancing due to the symmetry in the polarity of phase current over one fundamental cycle. As a result, deactivating the corresponding voltage control () does not significantly affect the voltage balance of and , as demonstrated in Figure 15, where the DC-link capacitor voltages are naturally balanced. Nevertheless, the implementation of this closed-loop control is still applied to mitigate voltage drifts in the real environment with dynamic conditions. On the other hand, when the flying capacitor voltage balancing is deactivated () during an operation in an unbalanced area, each of the flying capacitor voltages deviates from the reference value. This is demonstrated in Figure 16, where the inverter is operated at PF = 0.83 and . Deactivation of the corresponding offset voltage leads to deviation of each flying capacitor voltage from the reference value. These capacitor voltages are restored back to the reference value as soon as the offset voltage is reintroduced to the modulation voltage reference.

Figure 15.

Performance of the inverter under the conventional scheme without offset injection for split DC-link voltage balancing and under the proposed scheme. (a) Reference voltages. (b) Injected offset for split DC-link voltage control. (c) Injected offset for FC voltage control. (d) Pole voltage. (e) Line-to-line voltage. (f) Split DC-link capacitor voltages. (g) Flying capacitor voltages. (h) Output currents.

Figure 16.

Performance of the inverter under the conventional scheme without offset injection for flying capacitor voltage balancing and under the proposed scheme. (a) Reference voltages. (b) Injected offset for split DC-link voltage control. (c) Injected offset for FC voltage control. (d) Pole voltage. (e) Line-to-line voltage. (f) Split DC-link capacitor voltages. (g) Flying capacitor voltages. (h) Output currents.

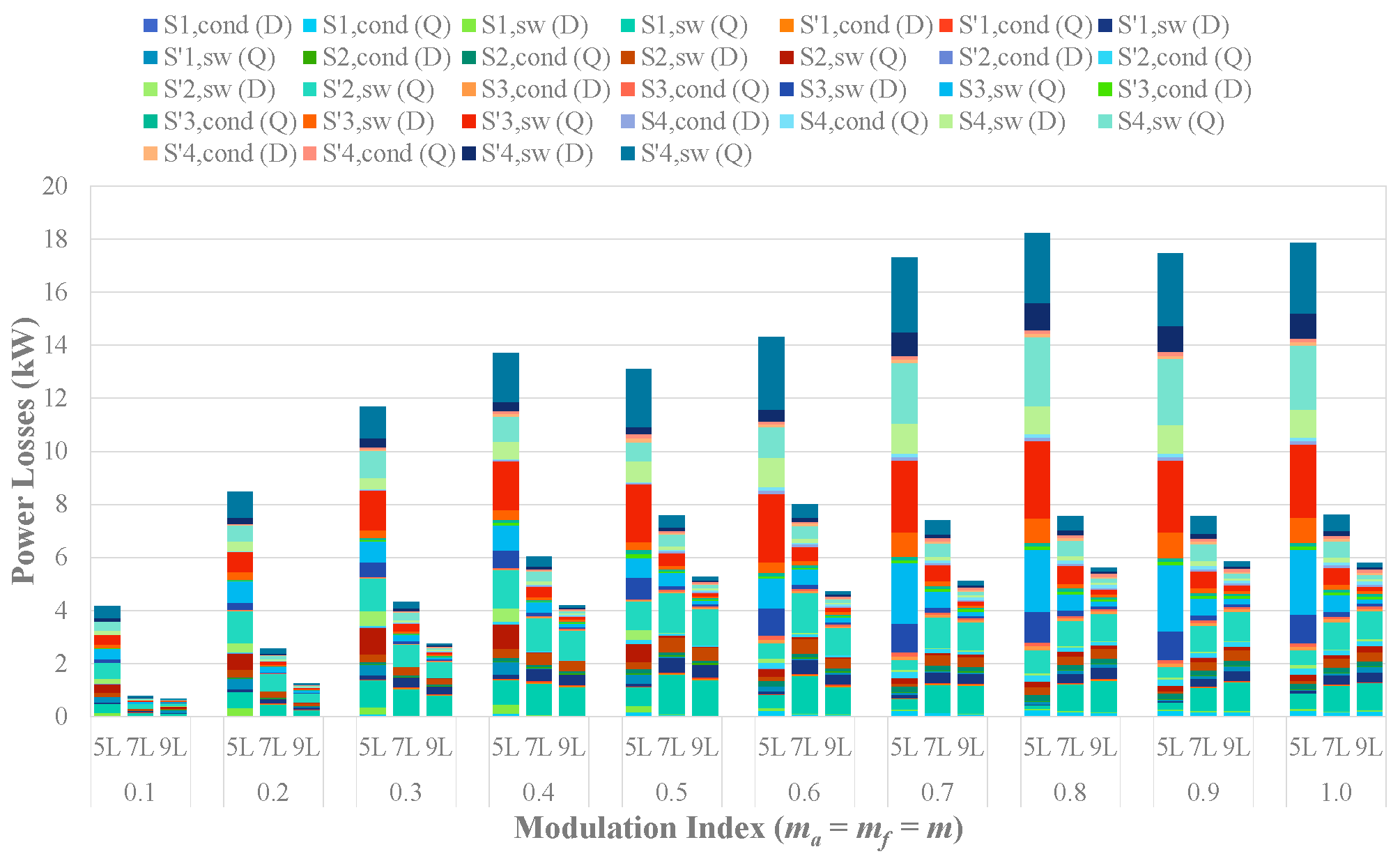

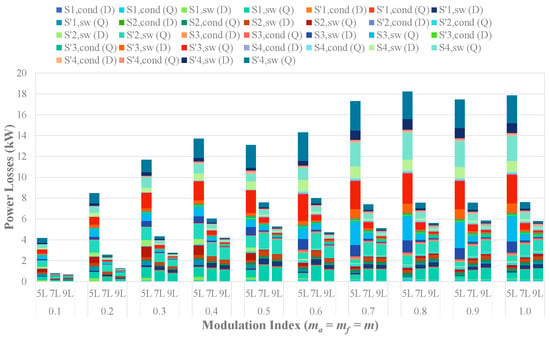

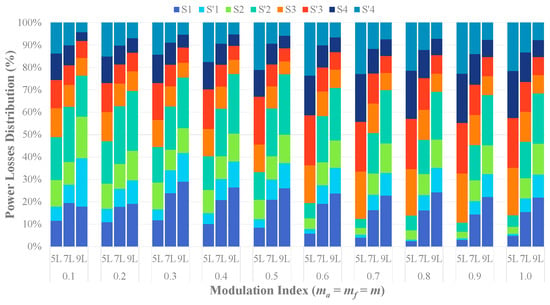

To analyze the switching and conduction losses across the power switches at various modulation indices, a series of simulations have been conducted using thermal modules in PSIM. The DIM800XSM45-TS001 modules (4500 V/800 A) (Manufacturer: Dynex Semiconductor Ltd. City, Country: Doddington Road, Lincoln, Lincolnshire, LN6 3LF, United Kingdom.)have been employed to simulate devices within all cascaded submodules of each HCHB inverter and the H-bridge submodules of the 5L-HCHB inverter. Simultaneously, the switches in the H-bridge submodules of 9L-HCHB and 7L-HCHB inverters have been modeled using DIM800XSM33-F000 (3300 V/800 A) and DIM800FSM17-A000 (1700 V/800 A), respectively.

Figure 17 illustrates the switching loss (“sw”) and conduction loss (“cond”) at the transistor (“Q”) and anti-parallel diode (“D”) of each power switch. The results reveal that lower switching and conduction losses are dissipated in inverters with a higher number of levels. At the unity modulation index, the power losses for the 5L-HCHB, 7L-HCHB, and 9L-HCHB inverters are 17.9 kW, 7.6 kW, and 5.8 kW, respectively.

Figure 17.

Switching and conduction losses across the power switches at various modulation indices.

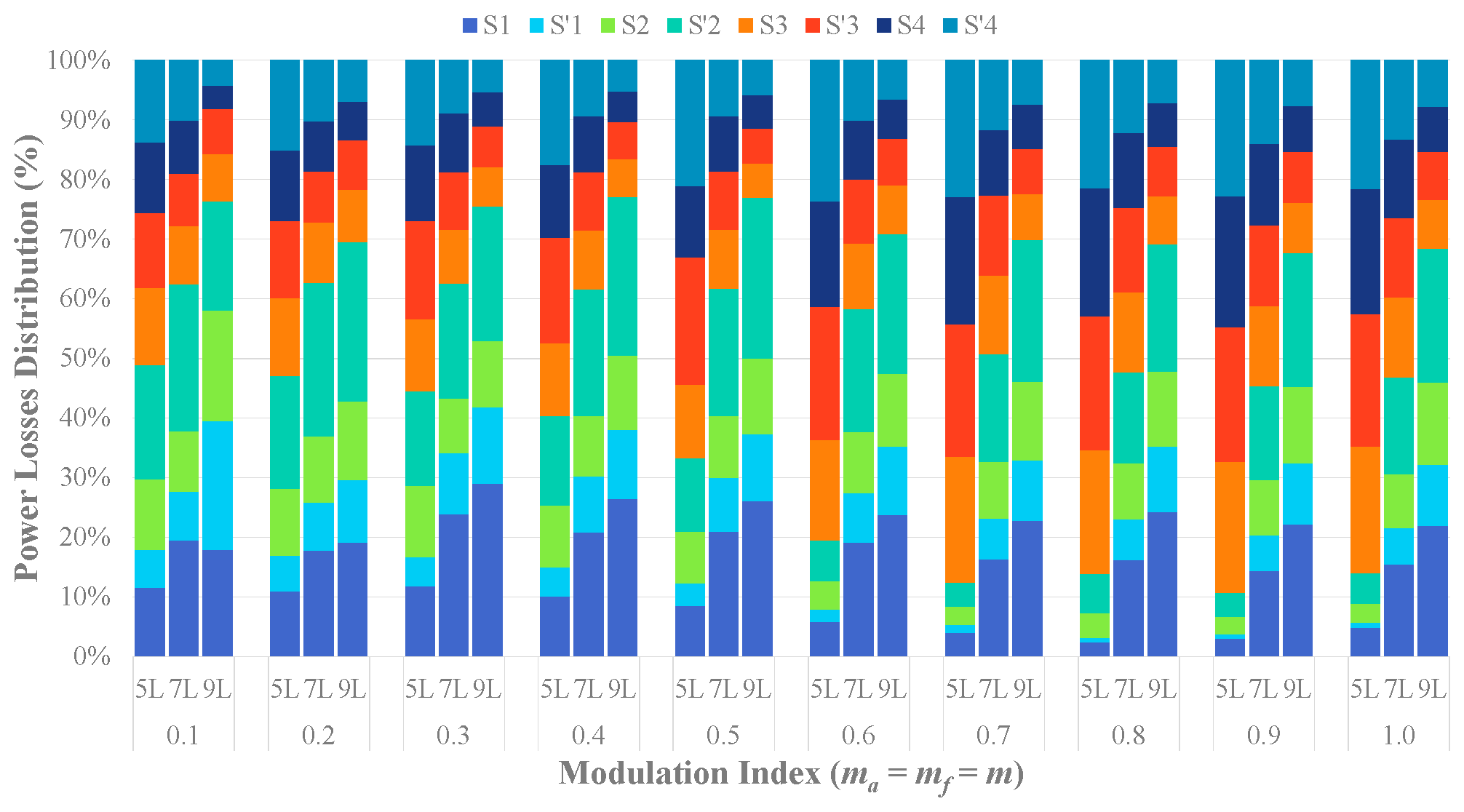

Figure 18 illustrates the power loss distribution across the switches. In the 5L-HCHB inverter, the highest power dissipations are contributed by the H-bridge submodules, which contribute up to 89% of the total power losses. The opposite trend is exhibited in the 9L-HCHB inverter at all modulation indices, where the cascaded submodules contribute up to 77% of the total power losses. Meanwhile, the power losses in the 7L-HCHB inverters are more evenly distributed between both submodules at high modulation indices and uniformly distributed across the switches in the H-bridge submodules.

Figure 18.

Power losses distribution across the switches.

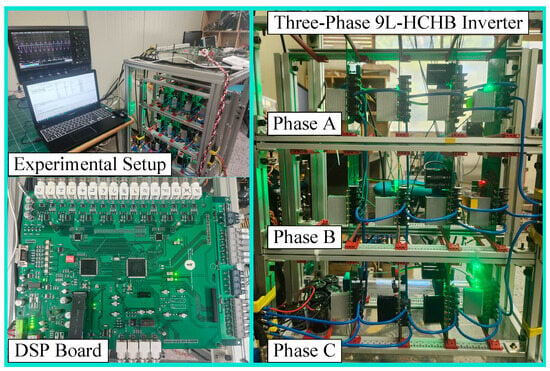

5. Experimental Verifications

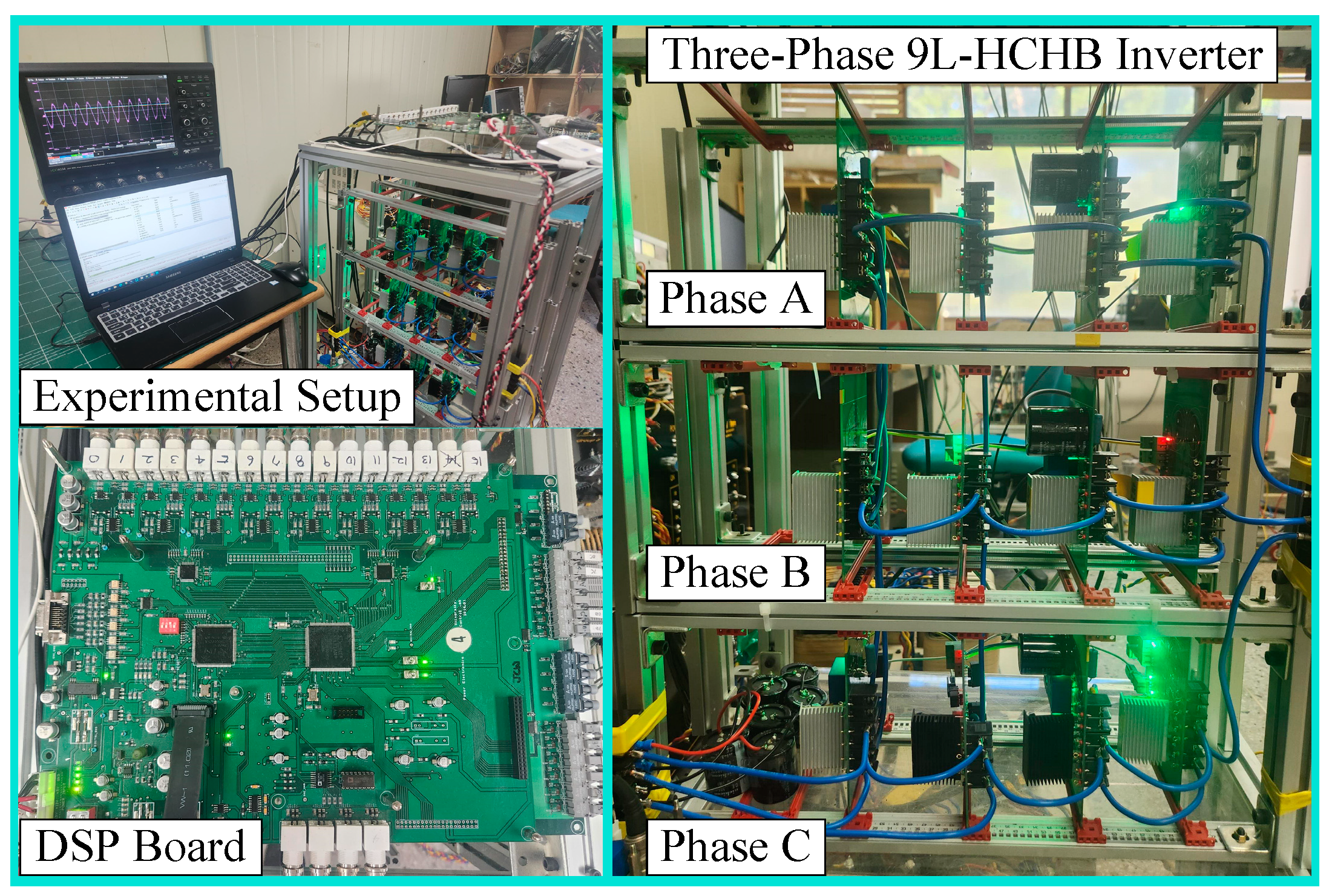

In order to further validate the proposed operating scheme, a down-scaled three-phase 9L-HCHB inverter has been developed and operated with the parameters listed in Table 6. This prototype is controlled with a DSP chip (TMS320F28335)( Manufacturer: Texas Instruments Incorporated City, country: 12500 TI Blvd., Dallas, Texas 75243 USA) and a field-programmable gate array (Xilinx XC3S400) (Manufacturer: Xilinx, Inc., City, country: San Jose, CA, USA), as shown in Figure 19.

Table 6.

Parameters for experiment.

Figure 19.

Experimental prototype of 9L-HCHB inverter.

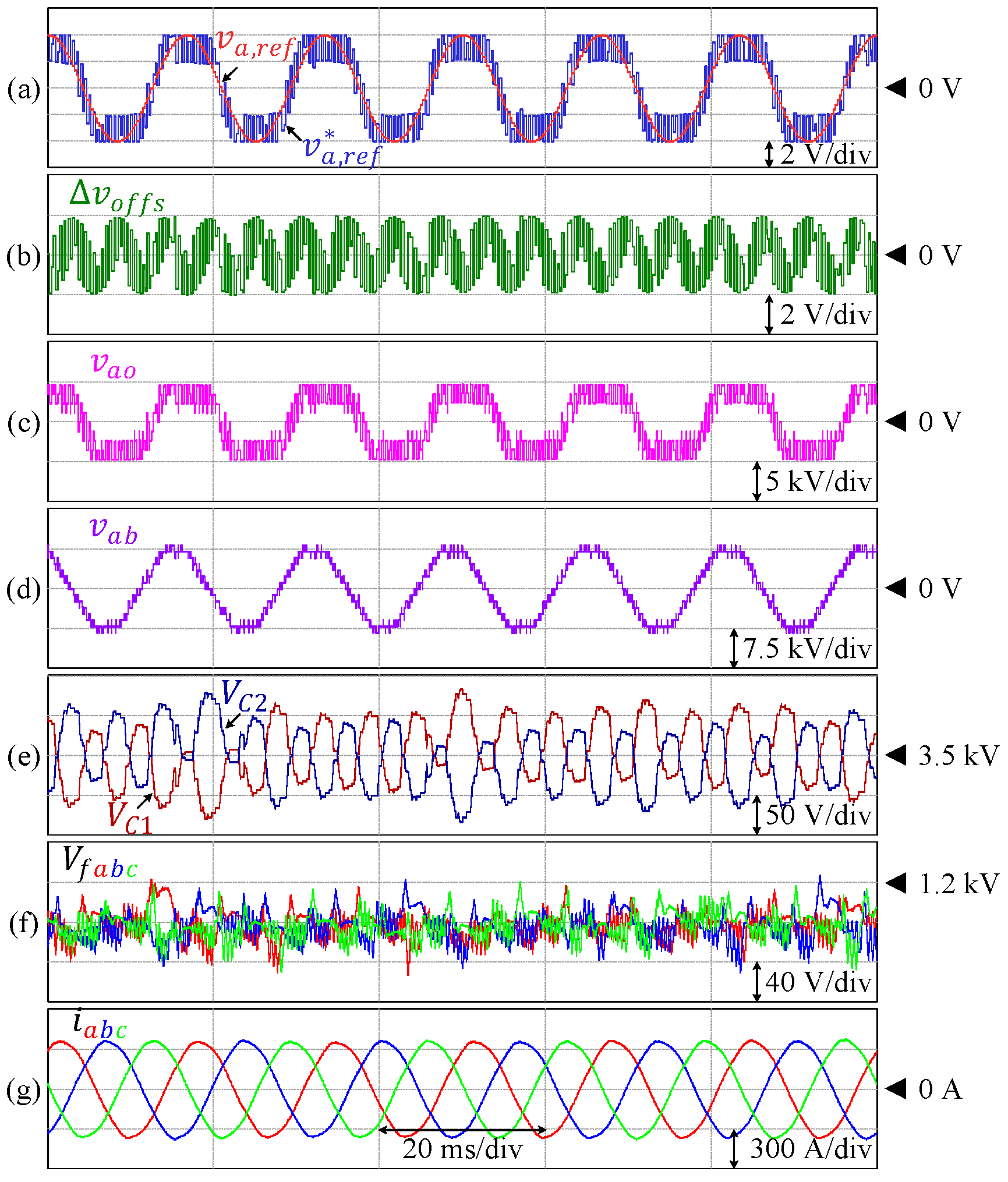

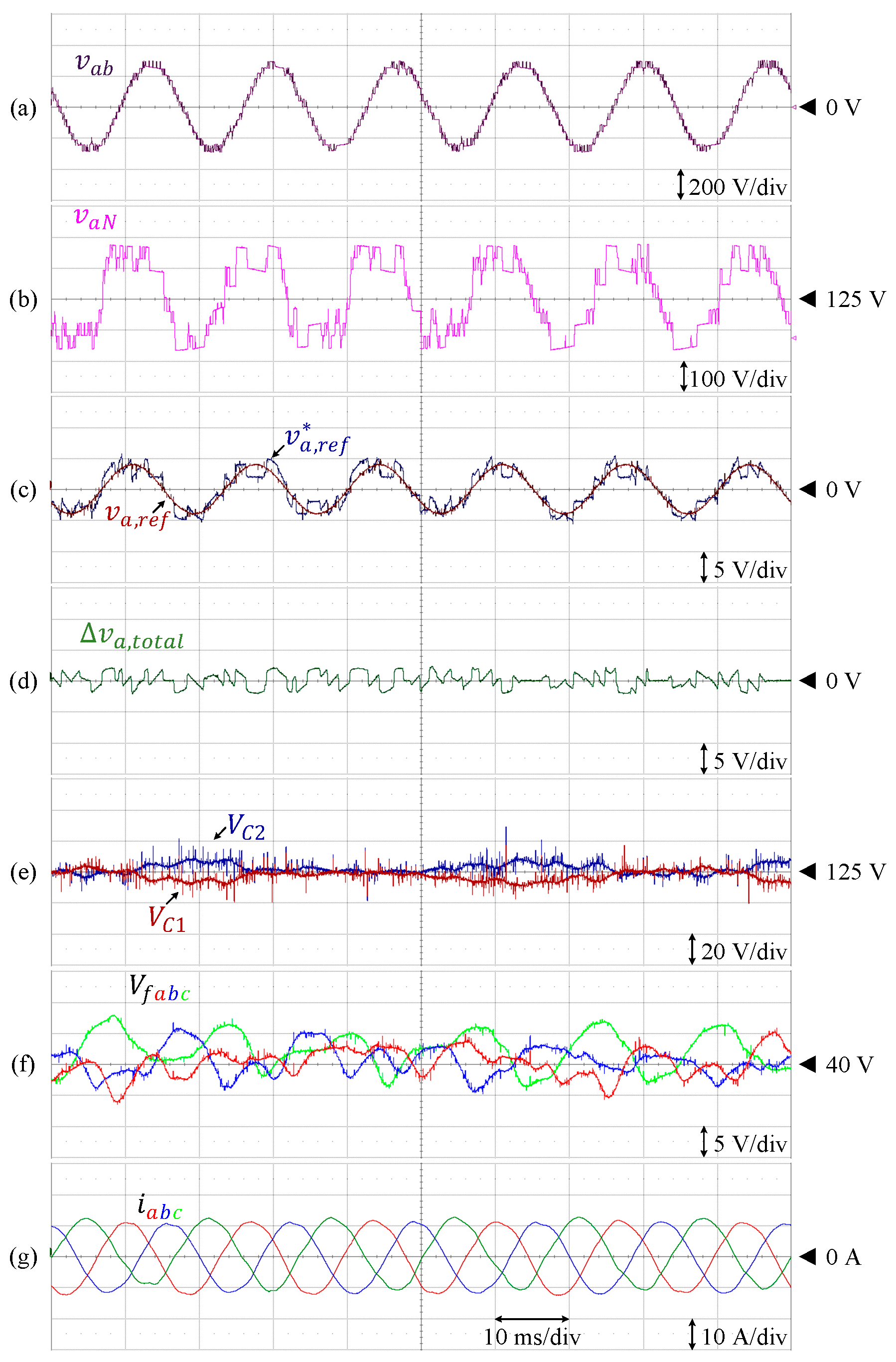

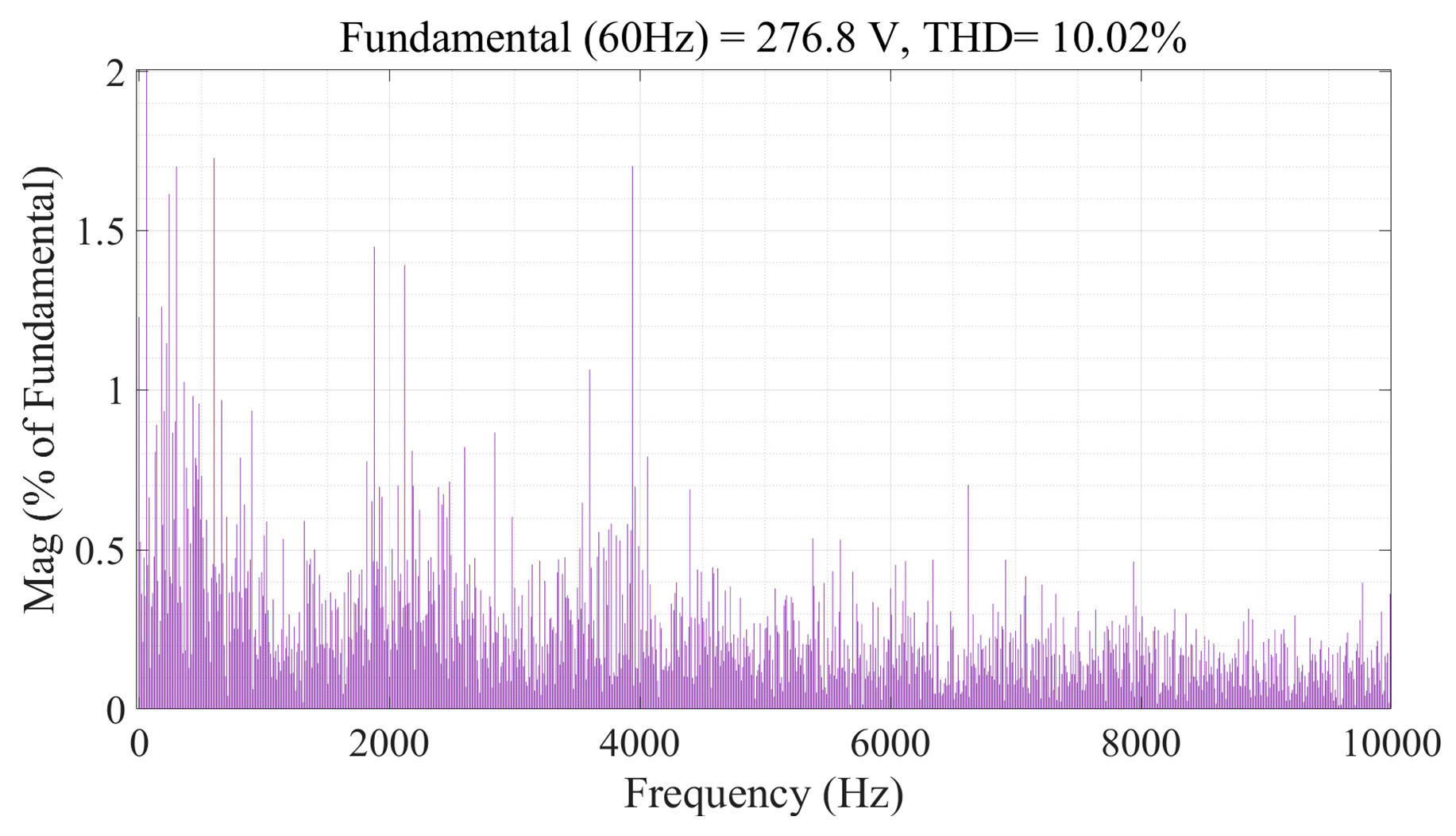

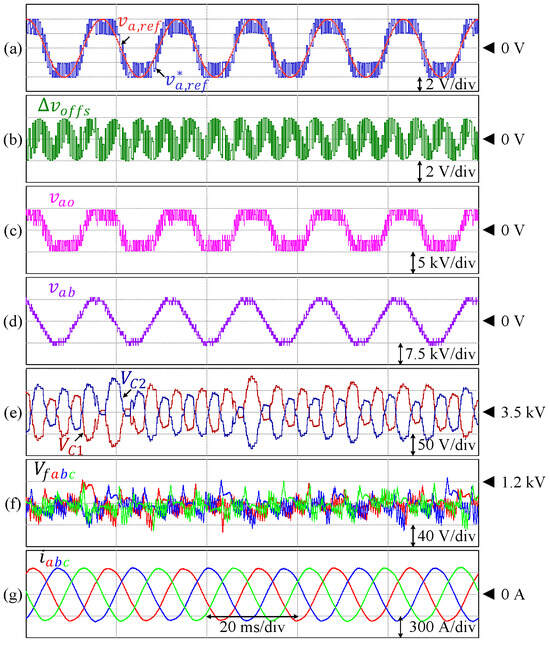

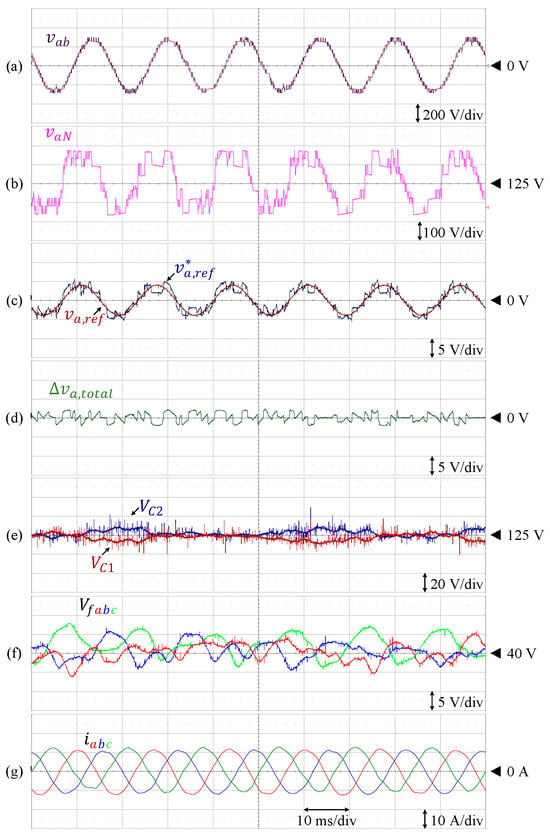

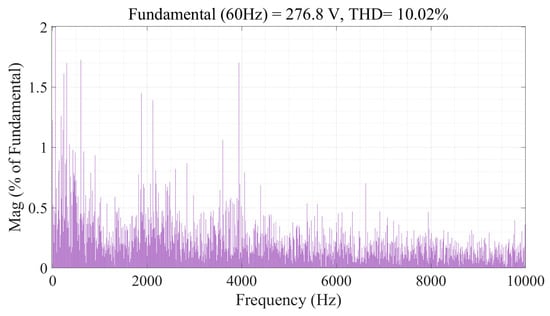

The steady-state performance of this inverter at unity modulation index is presented in Figure 20. The DC-link and flying capacitor voltages are controlled at 125 V and 41.67 V, respectively, where the peak-to-peak voltage ripples are kept within the allowable range, i.e., 20% of the corresponding references. The harmonic spectrum of the line-to-line voltage is depicted in Figure 21, where the THD is 10.02%. The harmonic components constituting this voltage also resemble that of the simulation.

Figure 20.

Performance of 9L-HCHB inverter prototype at unity modulation index. (a) Line voltage. (b) Pole voltage. (c) Reference voltages. (d) Injected offset voltage. (e) Split DC-link capacitor voltages. (f) Flying capacitor voltages. (g) Output currents.

Figure 21.

Harmonic spectrum of line voltage of 9L-HCHB inverter prototype at unity modulation index.

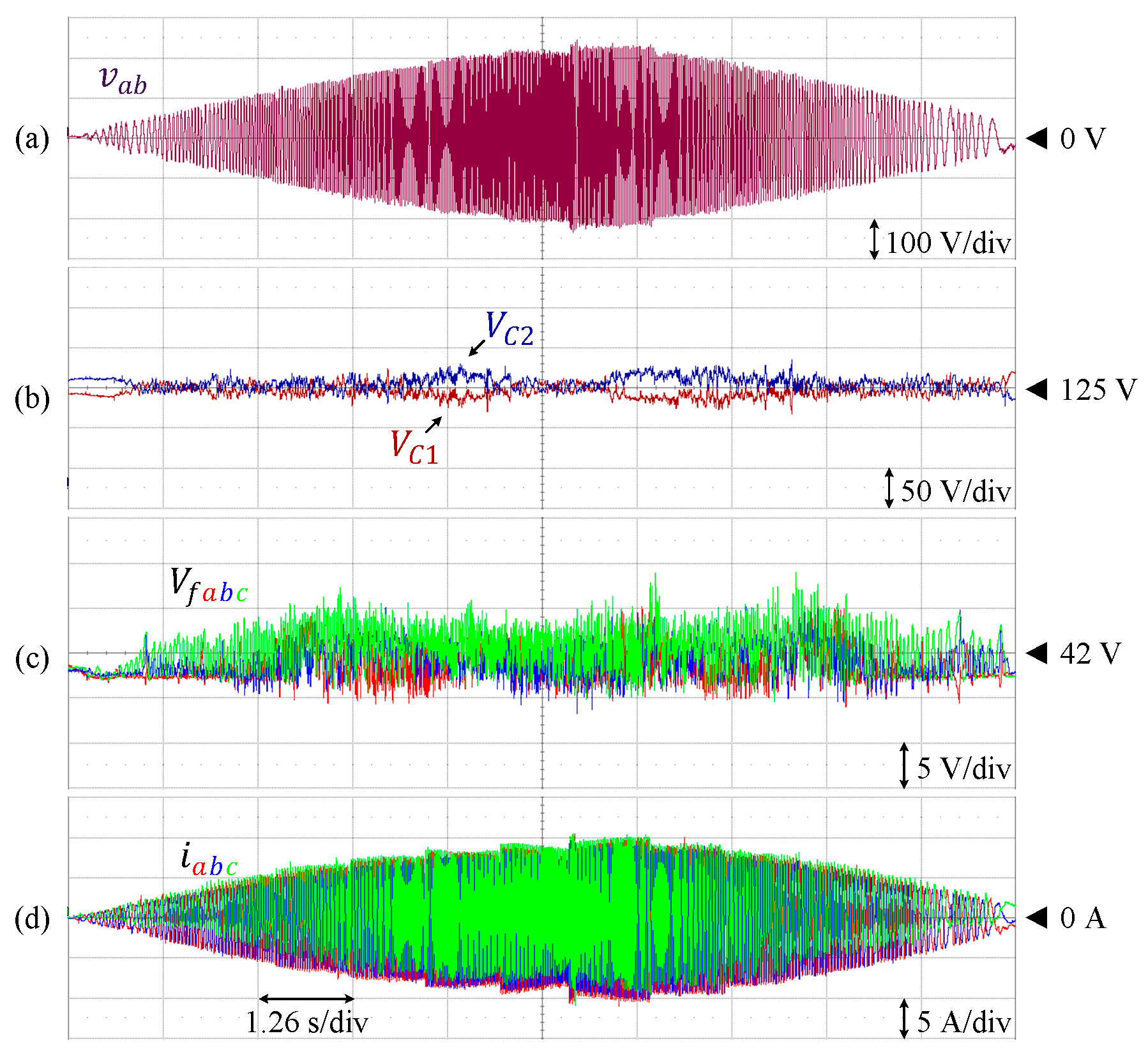

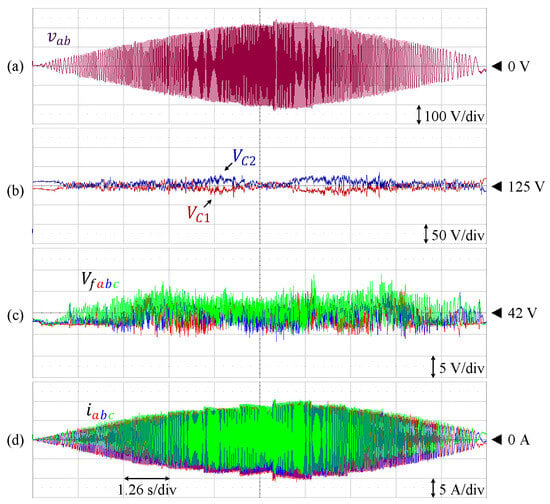

The proposed control technique is also effective to maintain each of the DC-link and flying capacitor voltages at various modulation indices, as shown in Figure 22. Both the amplitude and modulation indices are gradually increased from = 0 to = 1 before both parameters are reduced back to = 0. In this case, each of the DC-link and flying capacitor voltages are controlled at the references, and the fluctuations are kept within the allowable range.

Figure 22.

Performance of 9L-HCHB inverter prototype at various modulation indices. (a) Line voltage. (b) Split DC-link capacitor voltages. (c) Flying capacitor voltages. (d) Output currents.

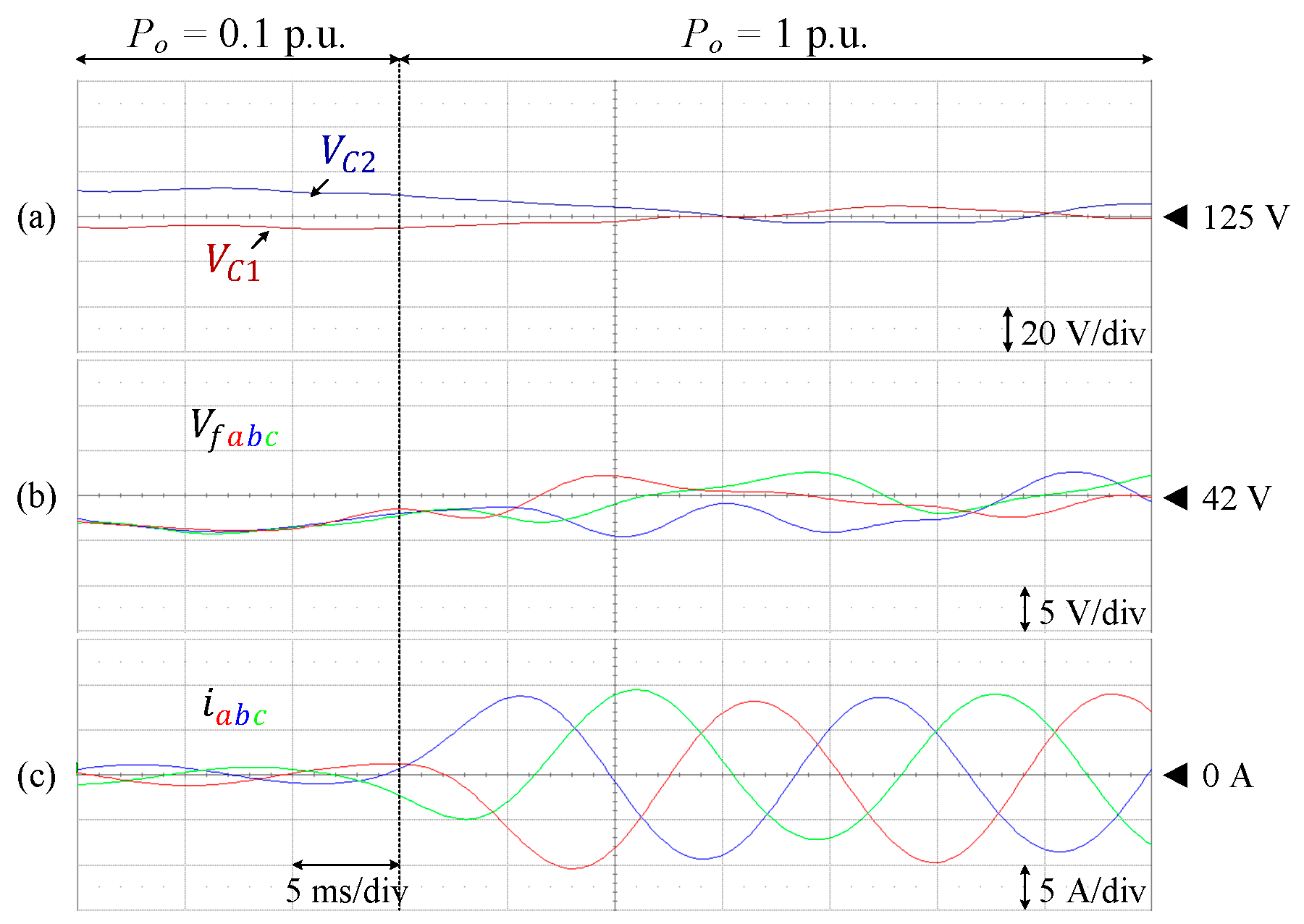

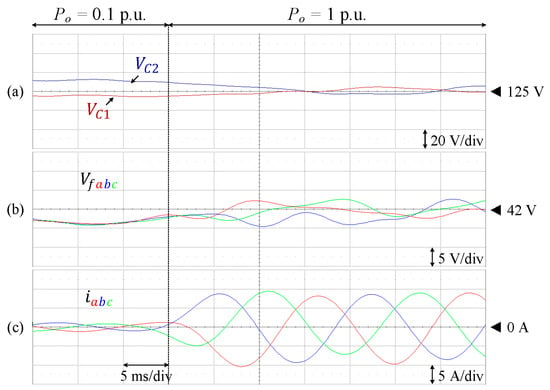

Figure 23 shows the transient state responses for load variation, where the load is increased from 12.7% ( = 318 W) to 100% of the rated value ( = 2.5 kW). Each of the DC-link and flying capacitor voltages is also maintained at the corresponding reference.

Figure 23.

Performance of 9L-HCHB inverter prototype for step load changes. (a) Split DC-link capacitor voltages. (b) Flying capacitor voltages. (c) Output currents.

6. Conclusions

In this paper, a novel control scheme has been proposed to generalize the operating technique of hybrid cascaded H-bridge (HCHB) inverters and counter the capacitor voltage drifts at certain modulation indices. This is achieved by injecting two independent offset voltages to the modulation voltage references. The first offset voltage is obtained through a proportional control based on the deviation at the DC-link capacitor voltages. Meanwhile, the second offset voltage is generated by forcing the common reference to the nearest levels in the same cluster with opposing charging characteristics that compensate for the lack of switching state redundancy for balancing each flying capacitor voltage. The effectiveness of the proposed technique in simultaneously maintaining all capacitor voltages at the full range of operating conditions and within the allowable fluctuation range has been verified through simulation and experimental results.

Author Contributions

Conceptualization, A.T.; methodology, A.T., J.P. and M.-S.K.; software, A.T., J.P. and M.-S.K.; validation, J.P. and M.-S.K.; formal analysis, A.T., J.P. and M.-S.K.; investigation, A.T and J.P.; resources, J.P., M.-S.K. and D.-C.L.; data curation, J.P. and M.-S.K.; writing—original draft preparation, A.T., J.P. and M.-S.K.; writing—review and editing, J.P., M.-S.K. and D.-C.L.; visualization, A.T., J.P. and M.-S.K.; supervision, D.-C.L.; project administration, D.-C.L.; funding acquisition, D.-C.L. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported by the 2021 Yeungnam University Research Grant.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Data are contained within the article.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- Poorfakhraei, A.; Narimani, M.; Emadi, A. A Review of Multilevel Inverter Topologies in Electric Vehicles: Current Status and Future Trends. IEEE Open J. Power Electron. 2021, 2, 155–170. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Pérez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Li, J.; Bhattacharya, S.; Huang, A.Q. A New Nine-Level Active NPC (ANPC) Converter for Grid Connection of Large Wind Turbines for Distributed Generation. IEEE Trans. Power Electron. 2011, 26, 961–972. [Google Scholar] [CrossRef]

- Ozdemir, E.; Ozdemir, S.; Tolbert, L.M. Fundamental-Frequency-Modulated Six-Level Diode-Clamped Multilevel Inverter for Three-Phase Stand-Alone Photovoltaic System. IEEE Trans. Ind. Electron. 2009, 56, 4407–4415. [Google Scholar] [CrossRef]

- Elsanabary, A.I.; Konstantinou, G.; Mekhilef, S.; Townsend, C.D.; Seyedmahmoudian, M.; Stojcevski, A. Medium Voltage Large-Scale Grid-Connected Photovoltaic Systems Using Cascaded h-Bridge and Modular Multilevel Converters: A Review. IEEE Access 2020, 8, 223686–223699. [Google Scholar] [CrossRef]

- Da Silva, I.R.F.M.P.; Jacobina, C.B.; Oliveira, A.C.; De Almeida Carlos, G.A.; De Rossiter Correa, M.B. Hybrid Modular Multilevel DSCC Inverter for Open-End Winding Induction Motor Drives. IEEE Trans. Ind. Appl. 2017, 53, 1232–1242. [Google Scholar] [CrossRef]

- Dhanamjayulu, C.; Padmanaban, S.; Ramachandaramurthy, V.K.; Holm-Nielsen, J.B.; Blaabjerg, F. Design and Implementation of Multilevel Inverters for Electric Vehicles. IEEE Access 2021, 9, 317–338. [Google Scholar] [CrossRef]

- Huang, Q.; Huang, A.Q.; Yu, R. Dual-Mode Cascaded Buck—Boost Multilevel Transformerless PV Inverter with GaN AC Switches. IEEE Trans. Power Electron. 2019, 34, 7474–7488. [Google Scholar] [CrossRef]

- Rodríguez, J.; Lai, J.S.; Peng, F.Z. Multilevel Inverters: A Survey of Topologies, Controls, and Applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Busquets-monge, S.; Nicolas-apruzzese, J. A Multilevel Active-Clamped Converter Topology—Operating Principle. IEEE Trans. Ind. Electron. 2011, 58, 3868–3878. [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, J.W. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Hammond, P.W. A New Approach to Enhance Power Quality for Medium Voltage AC Drives. IEEE Trans. Ind. Appl. 1997, 33, 202–208. [Google Scholar] [CrossRef]

- Candan, E.; Brooks, N.C.; Stillwell, A.; Abramson, R.A.; Strydom, J.; Pilawa-Podgurski, R.C.N. A Six-Level Flying Capacitor Multilevel Converter for Single-Phase Buck-Type Power Factor Correction. IEEE Trans. Power Electron. 2022, 37, 6335–6348. [Google Scholar] [CrossRef]

- Yan, B.; Huang, H.; Wang, H. Robust Phase-Shifted Model Predictive Control for Cascaded H-Bridge Power Supplies Using Linear Matrix Inequality. J. Power Electron. 2022, 22, 1496–1507. [Google Scholar] [CrossRef]

- Wang, L.; Chen, X.; Zhang, Z.; Guo, X. Voltage Equalization Control of Three-Phase Cascaded H-Bridge Multilevel Rectifiers. J. Power Electron. 2022, 23, 230–240. [Google Scholar] [CrossRef]

- Lee, E.-J.; Lee, K.-B. Performance Improvement of Cascaded H-Bridge Multilevel Inverters with Modified Modulation Scheme. J. Power Electron. 2021, 21, 541–552. [Google Scholar] [CrossRef]

- Khajehoddin, S.A.; Bakhshai, A.; Jain, P.K. A Simple Voltage Balancing Scheme for M-Level Diode-Clamped Multilevel Converters Based on a Generalized Current Flow Model. IEEE Trans. Power Electron. 2008, 23, 2248–2259. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Xu, L.; Li, Y. A Generalized Carrier-Overlapped PWM Method for Neutral-Point-Clamped Multilevel Converters. IEEE Trans. Power Electron. 2020, 35, 9095–9106. [Google Scholar] [CrossRef]

- Harbi, I.; Rodriguez, J.; Poorfakhraei, A.; Vahedi, H.; Guse, M.; Trabelsi, M.; Abdelrahem, M.; Ahmed, M.; Fahad, M.; Lin, C.H.; et al. Common DC-Link Multilevel Converters: Topologies, Control and Industrial Applications. IEEE Open J. Power Electron. 2023, 4, 512–538. [Google Scholar] [CrossRef]

- Kampitsis, G.; Batzelis, E.I.; Kolokasis, A.; Matioli, E.; Pal, B.C. A Generalized Phase-Shift Pwm Extension for Improved Natural and Active Balancing of Flying Capacitor Multilevel Inverters. IEEE Open J. Power Electron. 2022, 3, 621–634. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H. Multi-Level Conversion: High Voltage Choppers and Voltage-Source Inverters. In Proceedings of the PESC ‘92 Record, 23rd Annual IEEE Power Electronics Specialists Conference, Toledo, Spain, 29 June–3 July 1992; pp. 397–403. [Google Scholar]

- Peng, F.Z. A Generalized Multilevel Inverter Topology with Self Voltage Balancing. IEEE Trans. Ind. Appl. 2001, 37, 611–618. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA, 225–230. [Google Scholar] [CrossRef]

- Dutra, A.D.E.; Vitorino, M.A.; Correa, M.B.D.R. A Survey on Multilevel Rectifiers with Reduced Switch Count. IEEE Access 2023, 11, 56098–56141. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, Z.; Liu, W.; Zhang, Y.; Wang, K.; Liang, J. Step-up Switched-Capacitor Multilevel Inverter Employing Multiple Inputs with Reduced Switches. J. Power Electron. 2021, 21, 986–997. [Google Scholar] [CrossRef]

- Salem, A.; Van Khang, H.; Robbersmyr, K.G.; Norambuena, M.; Rodriguez, J. Voltage Source Multilevel Inverters with Reduced Device Count: Topological Review and Novel Comparative Factors. IEEE Trans. Power Electron. 2021, 36, 2720–2747. [Google Scholar] [CrossRef]

- Brückner, T.; Bernet, S.; Güldner, H. The Active NPC Converter and Its Loss-Balancing Control. IEEE Trans. Ind. Electron. 2005, 52, 855–868. [Google Scholar] [CrossRef]

- Barbosa, P.; Steimer, P.; Steinke, J.; Meysenc, L.; Winkelnkemper, M.; Celanovic, N. Active Neutral-Point-Clamped Multilevel Converters. In Proceedings of the 2005 IEEE 36th Power Electronics Specialists Conference, Dresden, Germany, 16 June 2005; pp. 2296–2301. [Google Scholar]

- Barbosa, P.; Steimer, P.; Steinke, J.; Winkelnkemper, M.; Celanovic, N. Active-Neutral-Point-Clamped (ANPC) Multilevel Converter Technology. In Proceedings of the 2005 European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005. [Google Scholar]

- Le, Q.A.; Lee, D.C. A Novel Six-Level Inverter Topology for Medium-Voltage Applications. IEEE Trans. Ind. Electron. 2016, 63, 7195–7203. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Xu, L.; Li, Y. Topology and Control of a Five-Level Hybrid-Clamped Converter for Medium-Voltage High-Power Conversions. IEEE Trans. Power Electron. 2018, 33, 4690–4702. [Google Scholar] [CrossRef]

- Dao, N.D.; Lee, D.-C. Operation and Control Scheme of a Five-Level Hybrid Inverter for Medium-Voltage Motor Drives. IEEE Trans. Power Electron. 2018, 33, 10178–10187. [Google Scholar] [CrossRef]

- Wang, Z.; Gao, C.; Chen, C.; Xiong, J.; Zhang, K. Ripple Analysis and Capacitor Voltage Balancing of Five-Level Hybrid Clamped Inverter (5L-HC) for Medium-Voltage Applications. IEEE Access 2019, 7, 86077–86089. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Xu, L.; Li, Y. A Four-Level Hybrid-Clamped Converter with Natural Capacitor Voltage Balancing Ability. IEEE Trans. Power Electron. 2014, 29, 1152–1162. [Google Scholar] [CrossRef]

- Gateau, G.; Meynard, T.A.; Foch, H. Stacked Multicell Converter (SMC): Properties and Design. PESC Rec. IEEE Annu. Power Electron. Spec. Conf. 2001, 3, 1583–1588. [Google Scholar] [CrossRef]

- Yuan, X. Ultimate Generalized Multilevel Converter Topology. IEEE Trans. Power Electron. 2021, 36, 8634–8639. [Google Scholar] [CrossRef]

- Keshmiri, N.; Narimani, M. A New 7-Level Voltage Source Converter for Medium-Voltage Application. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–3 October 2019; pp. 3649–3654. [Google Scholar] [CrossRef]

- Narimani, M.; Wu, B.; Cheng, Z.; Zargari, N.R. A New Nested Neutral Point-Clamped (NNPC) Converter for Medium-Voltage (MV) Power Conversion. IEEE Trans. Power Electron. 2014, 29, 6375–6382. [Google Scholar] [CrossRef]

- Narimani, M.; Wu, B.; Zargari, N.R. A Novel Seven-Level Voltage Source Converter for Medium-Voltage (MV) Applications. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 4277–4282. [Google Scholar] [CrossRef]

- Dekka, A.; Narimani, M. Capacitor Voltage Balancing and Current Control of a Five-Level Nested Neutral-Point-Clamped Converter. IEEE Trans. Power Electron. 2018, 33, 10169–10177. [Google Scholar] [CrossRef]

- Narimani, M.; Wu, B.; Zargari, N.R. A Novel Five-Level Voltage Source Inverter with Sinusoidal Pulse Width Modulator for Medium-Voltage Applications. IEEE Trans. Power Electron. 2016, 31, 1959–1967. [Google Scholar] [CrossRef]

- Deng, Z.; Liu, J.; Du, S. A Novel Medium Voltage Five-Level Converter with Minimized Volume. J. Power Electron. 2022, 22, 1676–1686. [Google Scholar] [CrossRef]

- Ebrahimi, J.; Karshenas, H. A New Single DC Source Six-Level Flying Capacitor Based Converter with Wide Operating Range. IEEE Trans. Power Electron. 2019, 34, 2149–2158. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Forouzesh, M.; Lee, S.S.; Blaabjerg, F.; Siwakoti, Y.P. Switched-Capacitor Multilevel Inverters: A Comprehensive Review. IEEE Trans. Power Electron. 2022, 37, 11209–11243. [Google Scholar] [CrossRef]

- Ye, Y.; Chen, S.; Sun, R.; Wang, X.; Yi, Y. Three-Phase Step-up Multilevel Inverter with Self-Balanced Switched-Capacitor. IEEE Trans. Power Electron. 2021, 36, 7652–7664. [Google Scholar] [CrossRef]

- Chen, S.; Ye, Y.; Chen, S.; Hua, T.; Wang, X. Three-Phase Boost Multilevel Inverter Based on Coupled-Structure Switched-Capacitor and V2SVM. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 679–690. [Google Scholar] [CrossRef]

- Ye, Y.; Zhang, Y.; Wang, X.; Cheng, K.W.E. Quasi-Z-Source-Fed Switched-Capacitor Multilevel Inverters without Inrush Charging Current. IEEE Trans. Ind. Electron. 2023, 70, 1115–1125. [Google Scholar] [CrossRef]

- Lee, S.S.; Bak, Y.; Kim, S.-M.; Joseph, A.; Lee, K.-B. New Family of Boost Switched-Capacitor Seven-Level Inverters (BSC7LI). IEEE Trans. Power Electron. 2019, 34, 10471–10479. [Google Scholar] [CrossRef]

- Davis, T.T.; Dey, A. Enhanced Floating Capacitor Voltage Balancing Schemes for Single-Source Seven-Level Inverters with Capacitor Fed H-Bridge Units. IEEE Trans. Ind. Electron. 2020, 67, 6227–6236. [Google Scholar] [CrossRef]

- Diao, F.; Li, Y.; Du, X.; Zhao, Y. An Active Hybrid Modulation Strategy for a Si/SiC Hybrid Multilevel Converter. IEEE Open J. Power Electron. 2021, 2, 401–413. [Google Scholar] [CrossRef]

- Yu, H.; Chen, B.; Yao, W.; Lu, Z. Hybrid Seven-Level Converter Based on T-Type Converter and H-Bridge Cascaded under SPWM and SVM. IEEE Trans. Power Electron. 2018, 33, 689–702. [Google Scholar] [CrossRef]

- Abhilash, T.; Annamalai, K.; Tirumala, S.V. A Seven-Level VSI with a Front-End Cascaded Three-Level Inverter and Flying-Capacitor-Fed H-Bridge. IEEE Trans. Ind. Appl. 2019, 55, 6073–6088. [Google Scholar] [CrossRef]

- Tirupathi, A.; Lee, D.-C. A 3-Phase Nine-Level Inverter Topology with Improved Capacitor Voltage Balancing Method. In Proceedings of the 2021 24th International Conference on Electrical Machines and Systems (ICEMS), Gyeongju, Republic of Korea, 31 October–3 November 2021; pp. 223–227. [Google Scholar] [CrossRef]

- Chokkalingam, B.; Bhaskar, M.S.; Padmanaban, S.; Ramachandaramurthy, V.K.; Iqbal, A. Investigations of Multi-Carrier Pulse Width Modulation Schemes for Diode Free Neutral Point Clamped Multilevel Inverters. J. Power Electron. 2019, 19, 702–713. [Google Scholar]

- Ghias, A.M.Y.M.; Pou, J.; Agelidis, V.G. An Active Voltage-Balancing Method Based on Phase-Shifted PWM for Stacked Multicell Converters. IEEE Trans. Power Electron. 2016, 31, 1921–1930. [Google Scholar] [CrossRef]

- Gobburi, H.B.; Borghate, V.B.; Meshram, P.M. A Level Enhanced Nearest Level Control for Modular Multilevel Converter without Using Sensors. IEEE Trans. Ind. Appl. 2023, 59, 4364–4374. [Google Scholar] [CrossRef]

- Chen, H.C.; Wu, P.H.; Lee, C.T.; Wang, C.W.; Yang, C.H.; Cheng, P.T. Zero-Sequence Voltage Injection for DC Capacitor Voltage Balancing Control of the Star-Connected Cascaded H-Bridge PWM Converter under Unbalanced Grid. IEEE Trans. Ind. Appl. 2015, 51, 4584–4594. [Google Scholar] [CrossRef]

- Wu, M.; Li, Y.W.; Konstantinou, G. A Comprehensive Review of Capacitor Voltage Balancing Strategies for Multilevel Converters under Selective Harmonic Elimination Pwm. IEEE Trans. Power Electron. 2021, 36, 2748–2767. [Google Scholar] [CrossRef]

- Mora, A.; Urrutia, M.; Cardenas, R.; Angulo, A.; Espinoza, M.; Diaz, M.; Lezana, P. Model-Predictive-Control-Based Capacitor Voltage Balancing Strategies for Modular Multilevel Converters. IEEE Trans. Ind. Electron. 2019, 66, 2432–2443. [Google Scholar] [CrossRef]

- Ramli, Z.; Jamaludin, J.; Rahim, N.A.; Azzuhri, S.R. Capacitor Voltage Balancing with Online Controller Performance-Based Tuning for a Switch-Sharing-Based Multilevel Inverter. Appl. Sci. 2021, 11, 4428. [Google Scholar] [CrossRef]

- Merlin, M.M.C.; Green, T.C. Cell Capacitor Sizing in Multilevel Converters: Cases of the Modular Multilevel Converter and Alternate Arm Converter. IET Power Electron. 2015, 8, 350–360. [Google Scholar] [CrossRef]

- Le, D.D.; Lee, D.-C. Reduction of Half-Arm Current Stresses and Flying-Capacitor Voltage Ripples of Flying-Capacitor MMCs. IEEE Access 2020, 8, 180076–180086. [Google Scholar]

- Krishnamoorthy, U.; Pitchaikani, U.; Rusu, E.; Fayek, H.H. Performance Analysis of Harmonic-Reduced Modified PUC Multi-Level Inverter Based on an MPC Algorithm. Inventions 2023, 8, 90. [Google Scholar] [CrossRef]

- Saeedian, M.; Pouresmaeil, E.; Samadaei, E.; Godinho Rodrigues, E.M.; Godina, R.; Marzband, M. An Innovative Dual-Boost Nine-Level Inverter with Low-Voltage Rating Switches. Energies 2019, 12, 207. [Google Scholar] [CrossRef]

- El Gadari, A.; El Ouardi, H.; Ounejjar, Y.; Al-haddad, K. Novel Three-Phase Nine-Level Inverter and Its Control Strategies. Electronics 2022, 11, 3348. [Google Scholar] [CrossRef]

- Al-Samawi, A.A.; Trabelsi, H. New Nine-Level Cascade Multilevel Inverter with a Minimum Number of Switches for PV Systems. Energies 2022, 15, 5857. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).