Novel Class-AB Operational Amplifier for Compact and Energy-Efficient Wake-Up Sensor Systems

Abstract

:1. Introduction

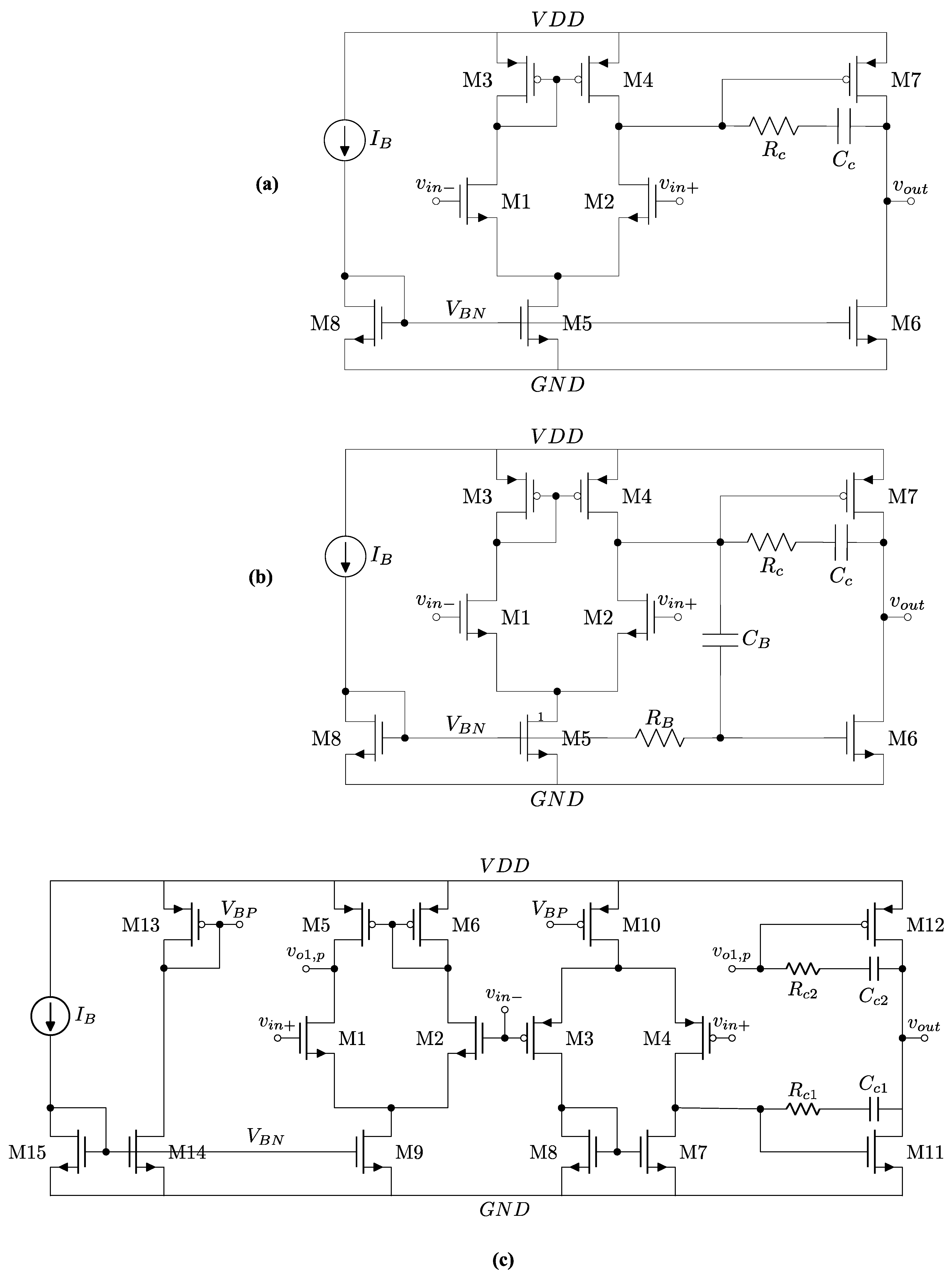

2. Circuit Analysis of the Proposed Class-AB Op-Amp

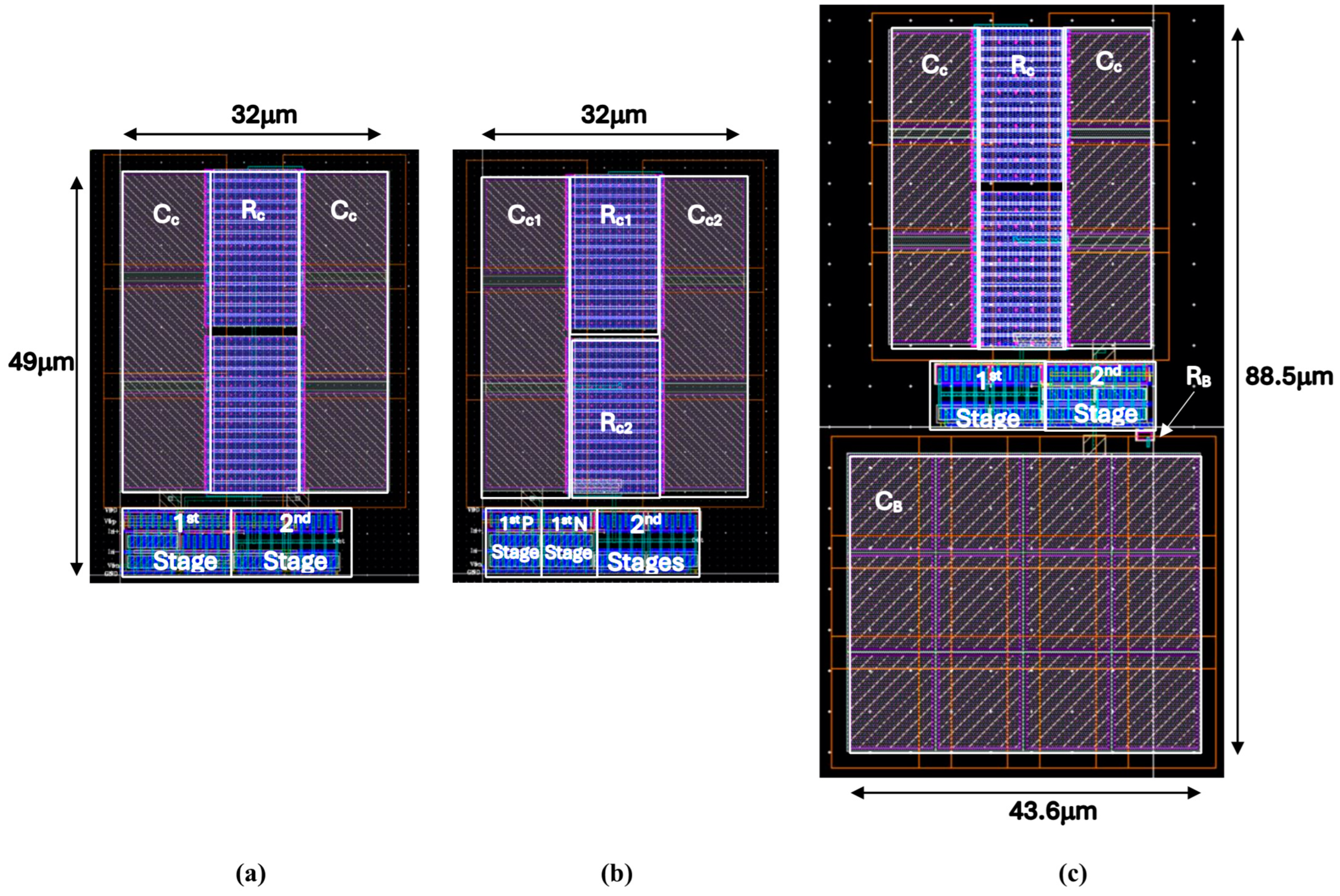

3. Proposed Design Details

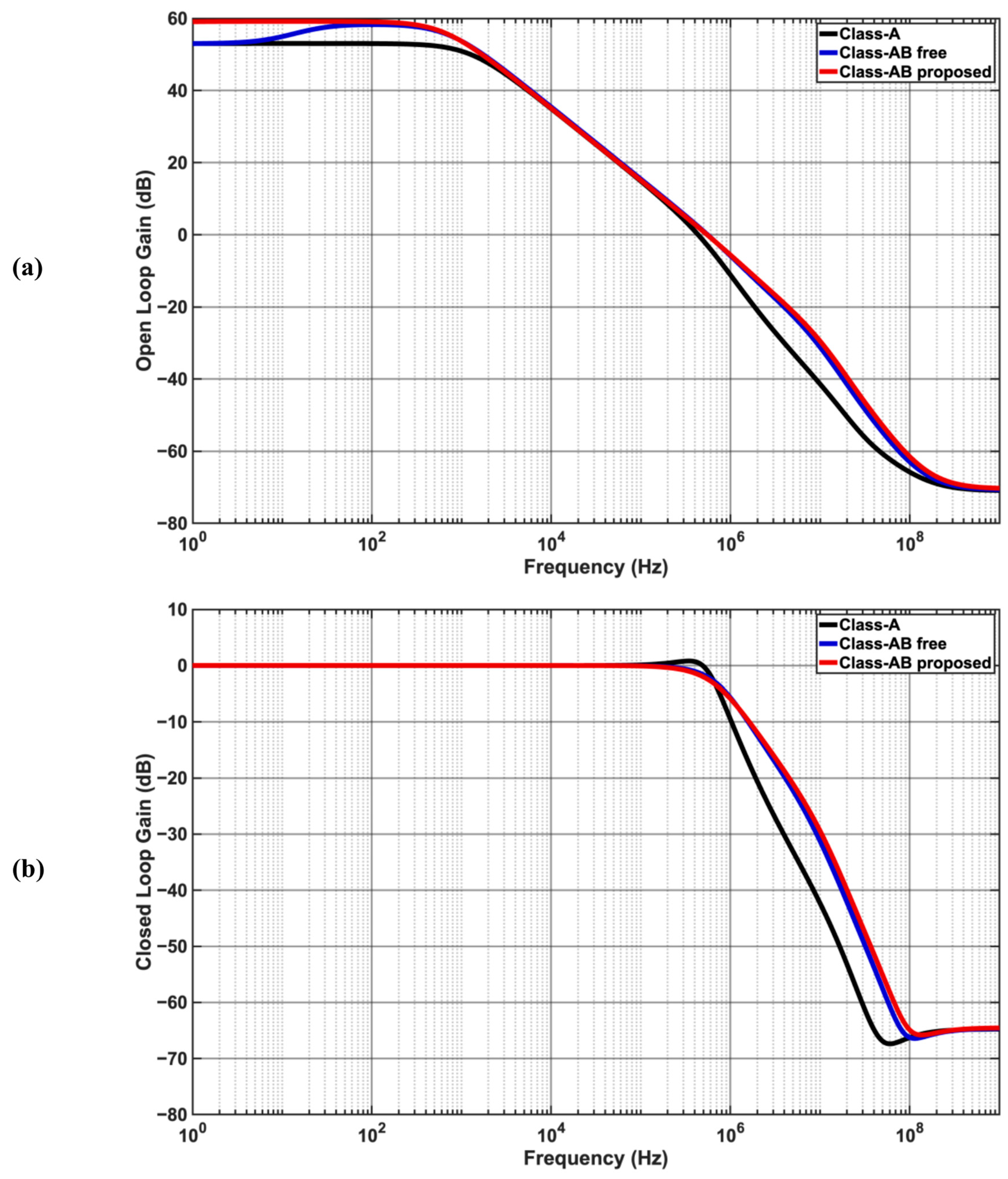

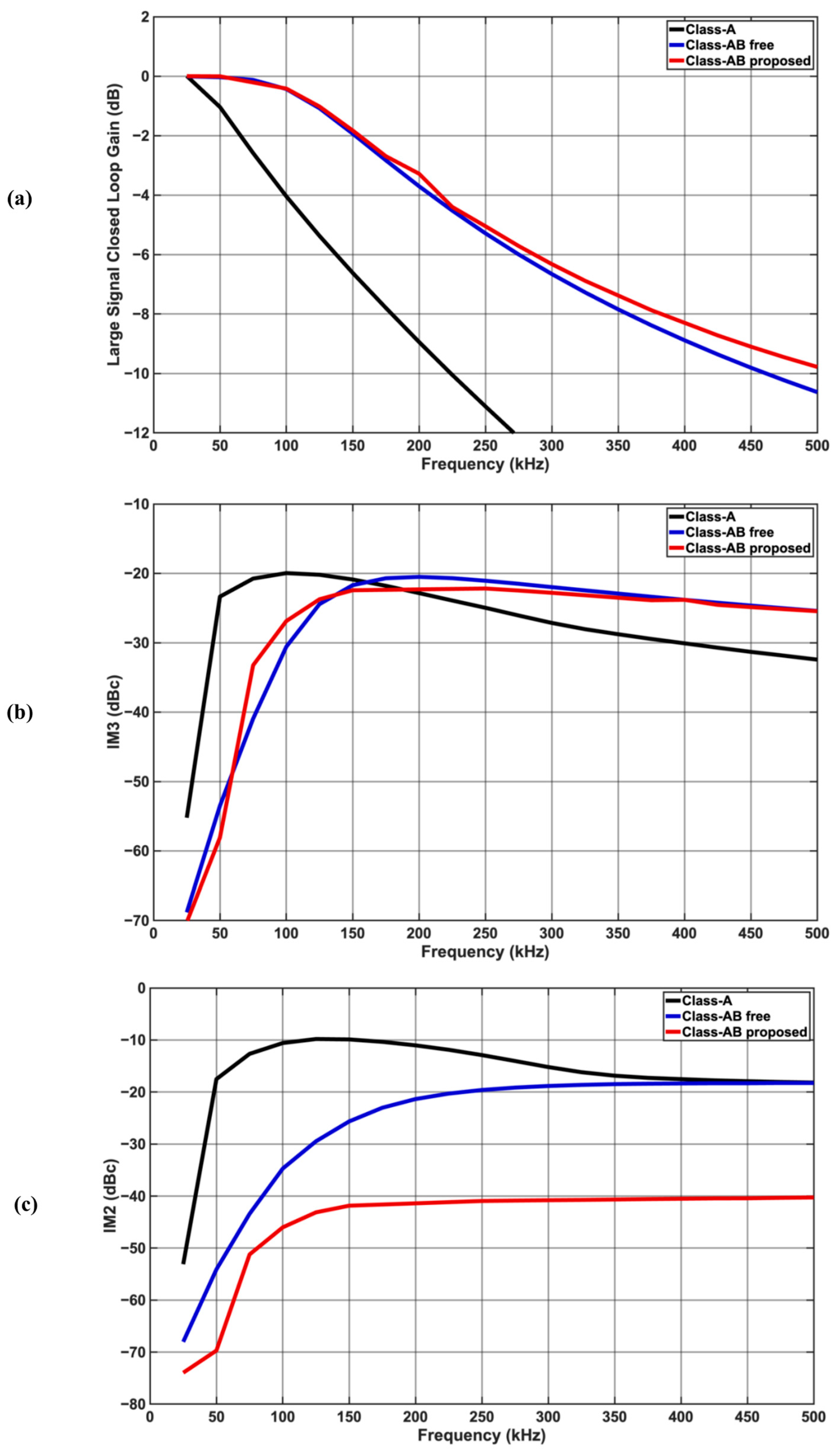

4. Simulation Results and Discussion

5. Conclusions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Hogervorst, R.; Tero, J.P.; Eschauzier, R.G.H.; Huijsing, J.H. A compact power-efficient 3 V CMOS rail-to-rail input/output operational amplifier for VLSI cell libraries. IEEE J. Solid-State Circuits 1994, 29, 1505–1513. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Carvajal, R.G.; Galan, J.A.; Lopez-Martin, A. A free but efficient low-voltage class-AB two-stage operational amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2006, 53, 568–571. [Google Scholar] [CrossRef]

- Paul, A.; Ramírez-Angulo, J.; Sánchez, A.D.; López-Martín, A.J.; Carvajal, R.G.; Li, F.X. An Enhanced Gain-Bandwidth Class-AB Miller op-amp with 23,800 MHz·pF/mW FOM, 11-16 Current Efficiency and Wide Range of Resistive and Capacitive Loads Driving Capability. IEEE Access 2021, 9, 69783–69797. [Google Scholar] [CrossRef]

- Pourashraf, S.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; González-Carvajal, R. A Highly Efficient Composite Class-AB–AB Miller Op-Amp with High Gain and Stable From 15 pF Up to Very Large Capacitive Loads. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 2061–2072. [Google Scholar] [CrossRef]

- Grasso, A.D.; Pennisi, S.; Scotti, G.; Trifiletti, A. 0.9-V Class-AB Miller OTA in 0.35- μm CMOS With Threshold-Lowered Non-Tailed Differential Pair. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 1740–1747. [Google Scholar] [CrossRef]

- Kuo, P.-Y.; Tsai, S.-D. An enhanced scheme of multi-stage amplifier with high-speed high-gain blocks and recycling frequency cascode circuitry to improve gain-bandwidth and slew rate. IEEE Access 2019, 7, 130820–130829. [Google Scholar] [CrossRef]

- An, C.-H.; Kong, B.-S. High-Speed Rail-to-Rail Class-AB Buffer Amplifier with Compact, Adaptive Biasing for FPD Applications. Electronics 2020, 9, 2018. [Google Scholar] [CrossRef]

- Djurić, R.; Popović-Božović, J. A CMOS Rail-to-Rail Class AB Second-Generation Voltage Conveyor and Its Application in a Relaxation Oscillator. Electronics 2024, 13, 3511. [Google Scholar] [CrossRef]

- Esparza-Alfaro, F.; Pennisi, S.; Palumbo, G.; Lopez-Martin, A.J. Low-Power Class-AB CMOS Voltage Feedback Current Operational Amplifier with Tunable Gain and Bandwidth. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 574–578. [Google Scholar] [CrossRef]

- Chen, X.; Mo, T.; Wu, P.; Wu, B. A Capacitive-Feedback Amplifier with 0.1% THD and 1.18 μVrms Noise for ECG Recording. Electronics 2024, 13, 378. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Baswa, S.; Ramirez-Angulo, J.; Carvajal, R.G. Low-Voltage Super class AB CMOS OTA cells with very high slew rate and power efficiency. IEEE J. Solid-State Circuits 2005, 40, 1068–1077. [Google Scholar] [CrossRef]

- Centurelli, F.; Monsurrò, P.; Parisi, G.; Tommasino, P.; Trifiletti, A. A Topology of Fully Differential Class-AB Symmetrical OTA With Improved CMRR. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1504–1508. [Google Scholar] [CrossRef]

- Beloso-Legarra, J.; De La Cruz-Blas, C.A.; Lopez-Martin, A.J. Power-Efficient Single-Stage Class-AB OTA Based on Non-Linear Nested Current Mirrors. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 1566–1579. [Google Scholar] [CrossRef]

- Serrano-Reyes, A.; Sanz-Pascual, M.T.; Calvo-López, B. Three-Stage CMOS LDO with Optimized Power and Dynamic Performance for Portable Devices. Electronics 2023, 12, 4638. [Google Scholar] [CrossRef]

- Fan, X.; Gao, F.; Chan, P.K. Design of a 0.5 V Chopper-Stabilized Differential Difference Amplifier for Analog Signal Processing Applications. Sensors 2023, 23, 9808. [Google Scholar] [CrossRef] [PubMed]

- Andrews, C.; Molnar, A.C. A Passive Mixer-First Receiver with Digitally Controlled and Widely Tunable RF Interface. IEEE J. Solid-State Circuits 2010, 45, 2696–2708. [Google Scholar] [CrossRef]

- Hamza, A.; Nagulu, A.; AlShammary, H.; Hill, C.; Lam, E.; Krishnaswamy, H.; Buckwalter, J.F. A Full-Duplex Transceiver with CMOS RF Circulation and Code-Domain Signal Processing for 104 dB Self-Interference Rejection and Watt Level TX Power Handling. In Proceedings of the 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 4–6 August 2020; pp. 1207–1210. [Google Scholar] [CrossRef]

- Hamza, A.; Nagulu, A.; Davidson, A.F.; Tao, J.; Hill, C.; AlShammary, H.; Krishnaswamy, H.; Buckwalter, J. A Code-Domain, In-Band, Full-Duplex Wireless Communication Link with Greater Than 100-dB Rejection. IEEE Trans. Microw. Theory Tech. 2021, 69, 955–968. [Google Scholar] [CrossRef]

- Hamza, A.; AlShammary, H.; Hill, C.; Buckwalter, J.F. A Full-Duplex Rake Receiver Using RF Code-Domain Signal Processing for Multipath Environments. IEEE J. Solid-State Circuits 2021, 56, 3094–3108. [Google Scholar] [CrossRef]

- Li, X.; Zheng, Y.; Kong, X.; Liu, Y.; Tang, D. Research on High-Resolution Miniaturized MEMS Accelerometer Interface ASIC. Sensors 2020, 20, 7280. [Google Scholar] [CrossRef]

- Qiao, Z.; Boom, B.A.; Annema, A.-J.; Wiegerink, R.J.; Nauta, B. On Frequency-Based Interface Circuits for Capacitive MEMS Accelerometers. Micromachines 2018, 9, 488. [Google Scholar] [CrossRef] [PubMed]

| Specification [Units] | Requirement |

|---|---|

| Bandwidth [kHz] | ≥10 |

| Unity gain frequency [kHz] | ≥200 |

| Phase margin [°] | ≥50 |

| Input signal [mV] | 0.5–10 |

| ADC input full-scale [Vpp] | 0.5 |

| Integrated input-referred noise [μVrms] | ≤50 |

| Max gain [dB] | 51 |

| CMRR@10 Hz [dB] | ≥40 |

| PSRR@10 Hz [dB] | ≥40 |

| Power consumption [μW] | ≤2 |

| Slew rate [V/μs] | ≥0.3 |

| CL [pF] (ADC load, pads etc.) | 5 |

| CIN [pF] (Amp load, pads etc.) | ≤1 |

| Inrush current [μA] | ≤10 |

| IM3, IM2 at 1 Vpp [dBc] | ≤−21 (each) |

| SNDR [dB] | ≥20 |

| Class-A | Free Class-AB | Proposed Class-AB |

|---|---|---|

| (W/L)7 = 2(W/L)3 = 2(W/L)4 = 4(6 μm/0.18 μm) | (W/L)7 = 2(W/L)3 = 2(W/L)4 = 4(6 μm/0.18 μm) | (W/L)12 = 2(W/L)10 = 4(W/L)5 = 4(W/L)6 = 4(6 μm/0.18 μm) |

| (W/L)6 = | (W/L)6 = | (W/L)11 = |

| (W/L)5 = 4(W/L)8 = 4(6 μm/0.18 μm) | (W/L)5 = 4(W/L)8 = 4(6 μm/0.18 μm) | 4(W/L)7 = 4(W/L)8 = 2(W/L)9 = 4(W/L)14 = 4(W/L)15 = 4(6 μm/0.18 μm) |

| (W/L)1 = | (W/L)1 = | (W/L)1 = |

| (W/L)2 = | (W/L)2 = | (W/L)2 = |

| 2(6 μm/0.18 μm) | 2(6 μm/0.18 μm) | (W/L)3 = (W/L)4 = 6 μm/0.18 μm |

| Cc = 1.5 pF | Cc = 1.5 pF | Cc1 = 0.75 pF |

| CB = 3 pF | Cc2 = 0.75 pF | |

| RB: 1.5 μm/0.18 μm (MOSFET) |

| Specification [Units] | Class-A | Free Class-AB | Proposed Class-AB |

|---|---|---|---|

| DC small-signal open-loop gain [dB] | 53 | 53 | 59 |

| Unity gain frequency [kHz] | 435.8 | 556.3 | 550.1 |

| Phase margin [°] | 57.4 | 78.8 | 82.5 |

| Closed loop gain −3 dB BW [kHz] | 664 | 683.5 | 631.7 |

| Total integrated input noise [μVrms] | 44.4 | 44.3 | 45.3 |

| Power consumption * [μW] | 1.95 | 1.95 | 2.05 |

| Active area [μm2] | 1568 | 3312 | 1568 |

| PSRR@100 Hz/PSRR worst [dB] | 53.6/1.4 | 46.6/8.3 | 46.2/8.5 |

| PSRR BW [kHz] | 1.54 | 37.3 | 34.3 |

| CMRR@100 Hz/CMRR worst [dB] | 45.9/30.6 | 49.9 | 52.0/37.9 |

| CMRR BW [kHz] | 39.8 | 54.5 | 52.3 |

| Specification [Units] | Class-A | Free Class-AB | Proposed Class-AB |

|---|---|---|---|

| Closed-loop gain 3 dB BW [kHz] | 80 | 175 | 175 |

| Worst IM3 within 3 dB BW [dBc] | −20.7 | −20.7 | −22.4 |

| Worst IM2 within 3 dB BW [dBc] | −12.4 | −29.5 | −43.3 |

| Worst slew rate [V/μs] | 0.08 | 0.24 | 0.33 |

| Steady-state error @ 300 μs [mV] | 0.1 | 15 | 0.1 |

| Inrush current [μA] | 1 | 7 | 1004 |

| Estimated SNDR at 1 Vpp operation [dB] | 11.9 | 20.1 | 22.3 |

| Specification [Units] | Class-A | Free Class-AB | Proposed Class-AB |

|---|---|---|---|

| Input referred offset voltage [mV] | 0.16/0.12 | 0.16/0.12 | 0.07/0.01 |

| Phase margin [°] | 47.3/1.5 | 74/1.8 | 78.8/3.2 |

| DC gain [dB] | 58.8/1.6 | 62.6/2 | 64.9/1.6 |

| Unity gain frequency [kHz] | 733.4/35.9 | 1082/79.8 | 1120/107.4 |

| IM3 @ 50 kHz [dBc] | −25/0.97 | −58.24 | −60.55/0.78 |

| IM2 @ 50 kHz [dBc] | −20.2/1.1 | −59.2/0.67 | −80.8/5.8 |

| CMRR@100 Hz [dB] | 51.8/1.6 | 51.7/1.6 | 54.9/1.6 |

| Specification [Units] (T = 27 °C, VDD = 1.8 V) | TTTT | SSSS | FFFF | ||||||

|---|---|---|---|---|---|---|---|---|---|

| Standard | Free | Proposed | Standard | Free | Proposed | Standard | Free | Proposed | |

| Class-A | Class-AB | Class-AB | Class-A | Class-AB | Class-AB | Class-A | Class-AB | Class-AB | |

| DC gain [dB] | 53.0 | 53.0 | 59.0 | 59.5 | 59.5 | 64.8 | 48.4 | 48.4 | 54.8 |

| Unity gain frequency [MHz] | 0.44 | 0.56 | 0.55 | 0.30 | 0.48 | 0.49 | 0.51 | 0.68 | 0.67 |

| Phase margin [°] | 57.4 | 78.8 | 82.5 | 53.6 | 75.1 | 75.3 | 60.7 | 83.8 | 91.7 |

| Power [μW] | 1.95 | 1.95 | 2.05 | 1.75 | 1.75 | 1.90 | 2.20 | 2.20 | 2.70 |

| PSRR@100 Hz [dB] | 53.6 | 46.6 | 46.2 | 48.4 | 46.6 | 46.2 | 60.9 | 46.6 | 46.2 |

| CMRR@100 Hz [dB] | 46.9 | 49.9 | 52.0 | 45.1 | 49.9 | 52.0 | 49.9 | 49.9 | 52.0 |

| Worst slew rate (SR) [V/μs] | 0.08 | 0.24 | 0.33 | 0.08 | 0.23 | 0.27 | 0.10 | 0.26 | 0.38 |

| IM3 @ 50 kHz [dBc] | −23.4 | −53.4 | −58.1 | −21.4 | −51.3 | −53.3 | −26.9 | −56.9 | −59.9 |

| IM2 @ 50 kHz [dBc] | −17.7 | −53.9 | −69.7 | −15.4 | −53.4 | −75.6 | −20.7 | −55.1 | −89.7 |

| Integrated noise [μVrms] | 44.4 | 44.3 | 45.3 | 43.8 | 43.8 | 43.5 | 45.1 | 45.2 | 47.3 |

| Specification [Units] (TTTT, T = 27 °C) | VDD = 1.62 V | VDD = 1.8 V | VDD = 1.98 V | ||||||

| Standard | Free | Proposed | Standard | Free | Proposed | Standard | Free | Proposed | |

| Class-A | Class-AB | Class-AB | Class-A | Class-AB | Class-AB | Class-A | Class-AB | Class-AB | |

| DC gain [dB] | 52.8 | 52.8 | 58.8 | 53.0 | 53.0 | 59.0 | 53.1 | 53.2 | 59.3 |

| Unity gain frequency [MHz] | 0.41 | 0.52 | 0.49 | 0.44 | 0.56 | 0.55 | 0.46 | 0.59 | 0.61 |

| Phase margin [°] | 56.3 | 77.6 | 79.3 | 57.4 | 78.8 | 82.5 | 58.4 | 80.0 | 85.8 |

| Power [μW] | 1.66 | 1.67 | 1.79 | 1.95 | 1.95 | 2.05 | 2.26 | 2.26 | 2.39 |

| PSRR@100 Hz [dB] | 54.1 | 46.8 | 46.3 | 53.6 | 46.6 | 46.2 | 53.1 | 46.33 | 46.1 |

| CMRR@100 Hz [dB] | 46.7 | 49.7 | 49.6 | 46.9 | 49.9 | 52.0 | 47.2 | 50.2 | 51.9 |

| Worst slew rate (SR) [V/μs] | 0.08 | 0.23 | 0.29 | 0.08 | 0.24 | 0.33 | 0.09 | 0.26 | 0.35 |

| IM3 @ 50 kHz [dBc] | −22.9 | −51.2 | −52.9 | −23.4 | −53.4 | −58.1 | −24.0 | −55.3 | −58.7 |

| IM2 @ 50 kHz [dBc] | −17.0 | −52.8 | −77.7 | −17.7 | −53.9 | −69.7 | −18.5 | −55.0 | −86.2 |

| Integrated noise [μVrms] | 44.5 | 44.4 | 45.4 | 44.4 | 44.3 | 45.3 | 44.4 | 44.3 | 45.3 |

| Specification [Units] (TTTT, VDD = 1.8 V) | T = −20 °C | T = 27 °C | T = 80 °C | ||||||

| Standard | Free | Proposed | Standard | Free | Proposed | Standard | Free | Proposed | |

| Class-A | Class-AB | Class-AB | Class-A | Class-AB | Class-AB | Class-A | Class-AB | Class-AB | |

| DC gain [dB] | 54.0 | 56.6 | 60.3 | 53.0 | 53.0 | 59.0 | 51.8 | 51.8 | 57.7 |

| Unity gain frequency [MHz] | 0.49 | 0.64 | 0.60 | 0.44 | 0.56 | 0.55 | 0.39 | 0.49 | 0.51 |

| Phase margin [°] | 62.2 | 84.0 | 85.3 | 57.4 | 78.8 | 82.5 | 53.0 | 74.3 | 80.4 |

| Power [μW] | 1.88 | 1.88 | 2.04 | 1.95 | 1.95 | 2.05 | 2.03 | 2.04 | 2.34 |

| PSRR@100 Hz [dB] | 53.2 | 46.3 | 47.9 | 53.6 | 46.6 | 46.2 | 41.7 | 50.7 | 45.3 |

| CMRR@100 Hz [dB] | 48.6 | 52.7 | 54.4 | 46.9 | 49.9 | 52.0 | 45.2 | 45.2 | 52.6 |

| Worst slew rate (SR) [V/μs] | 0.80 | 0.24 | 0.30 | 0.08 | 0.24 | 0.33 | 0.83 | 0.26 | 0.34 |

| IM3 @ 50 kHz [dBc] | −22.7 | −52.3 | −54.4 | −23.4 | −53.4 | −58.1 | −24.0 | −54.5 | −57.6 |

| IM2 @ 50 kHz [dBc] | −18.3 | −53.5 | −78.1 | −17.7 | −53.9 | −69.7 | −17.7 | −54.5 | −83.9 |

| Integrated noise [μVrms] | 41.4 | 41.3 | 42.5 | 44.4 | 44.3 | 45.3 | 47.7 | 47.5 | 48.5 |

| Specification [Units] | Proposed Work | [3] (2021) | [4] (2018) | [5] (2017) | [6] (2019) | [15] (2023) |

|---|---|---|---|---|---|---|

| CMOS process [μm] | 0.18 | 0.13 | 0.18 | 0.35 | 0.18 | 0.04 |

| Verification | Simulation | Measured | Measured | Measured | Measured | Simulation |

| Supply [V] | 1.8 | ±0.6 | ±0.9 | 0.9 | 1.8 | 0.5 |

| Capacitive load (CL) [pF] | 5 | 300 | 25 | 10 | 5 | 50 |

| Slew rate (SR) [V/μs] | 0.33 | 5.4 | 28 | 0.25 | 13.25 | 0.055 |

| DC gain [dB] | 59 | 87.8 | 90.8 | 65 | 105.5 | 89 |

| 184.7@10 kHz | 20@1 MHz | 27@1 MHz | 65@100 kHz | 194,224@1 Hz–10 MHz | 245@1 kHz | |

| Phase margin [°] | 82.5 | 54 | 58.4 | 65 | 53 | 63.6 |

| Power [μW] | 2.05 | 126 | 80 | 24.9 | 850 | 0.72 |

| Inrush current [μA] | 7 | NA | NA | NA | NA | NA |

| Active area [mm2] | 0.0016 | 0.025 | 0.021 | 1,568 | 0.45 | NA |

| PSRR@10 Hz [dB] | 59.6 | 86 | 64 | 50 | NA | 79 |

| CMRR@10 Hz [dB] | 59.2 | 92 | 68 | 80 | NA | 101 |

| Unity gain frequency (fu) [MHz] | 0.55 | 10 | 12.5 | 1 | 231.7 | 0.174 |

| μW·mm2] | 503 | 514 | 419 | 7.2 | 0.17 | NA |

| μW·mm2] | 838.4 | 952.4 | 186 | 28.7 | 3 | NA |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

AlShammary, H. Novel Class-AB Operational Amplifier for Compact and Energy-Efficient Wake-Up Sensor Systems. Sensors 2025, 25, 316. https://doi.org/10.3390/s25020316

AlShammary H. Novel Class-AB Operational Amplifier for Compact and Energy-Efficient Wake-Up Sensor Systems. Sensors. 2025; 25(2):316. https://doi.org/10.3390/s25020316

Chicago/Turabian StyleAlShammary, Hussam. 2025. "Novel Class-AB Operational Amplifier for Compact and Energy-Efficient Wake-Up Sensor Systems" Sensors 25, no. 2: 316. https://doi.org/10.3390/s25020316

APA StyleAlShammary, H. (2025). Novel Class-AB Operational Amplifier for Compact and Energy-Efficient Wake-Up Sensor Systems. Sensors, 25(2), 316. https://doi.org/10.3390/s25020316