Thermo-Mechanical Reliability Study of Through Glass Vias in 3D Interconnection

Abstract

:1. Introduction

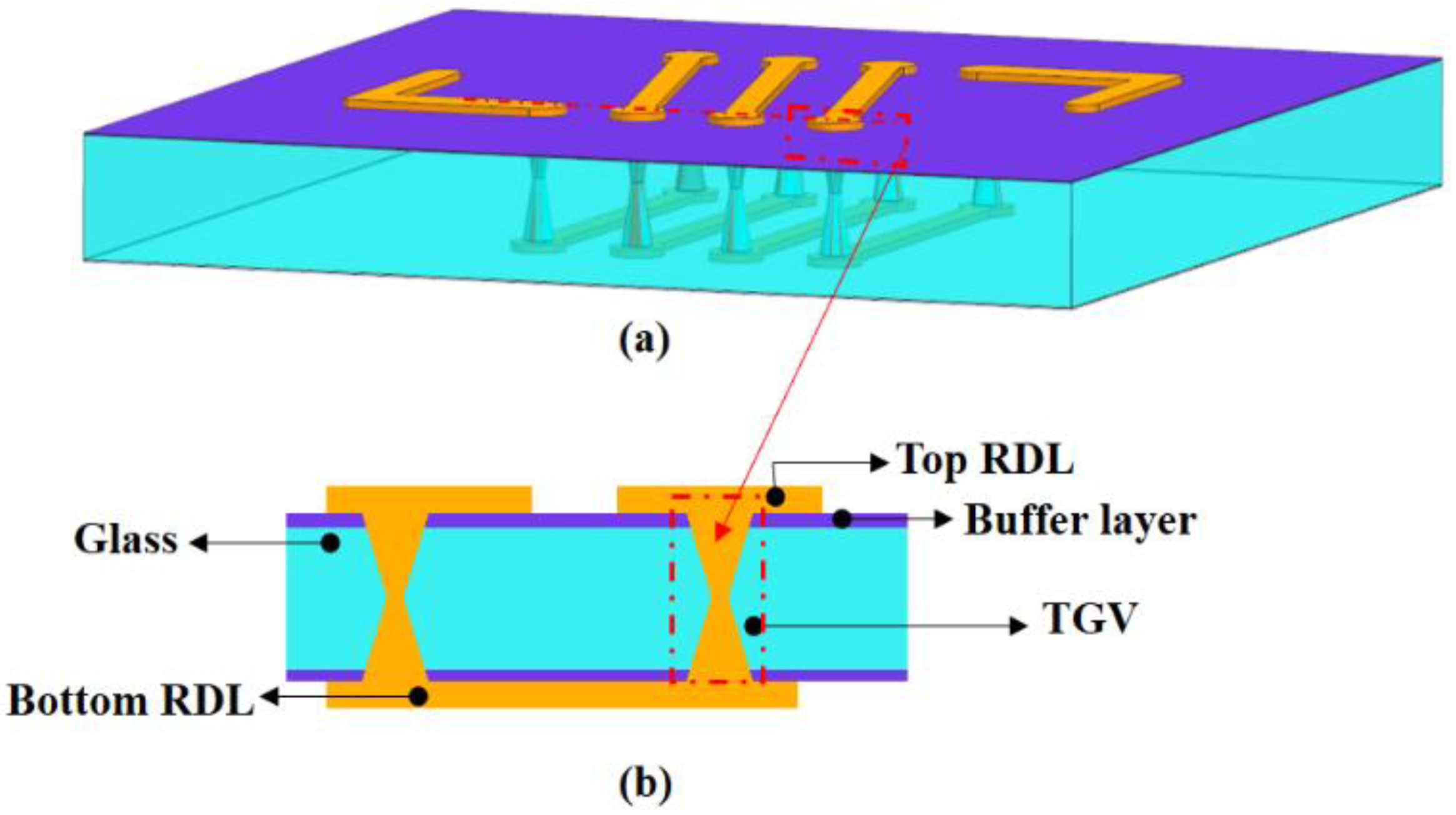

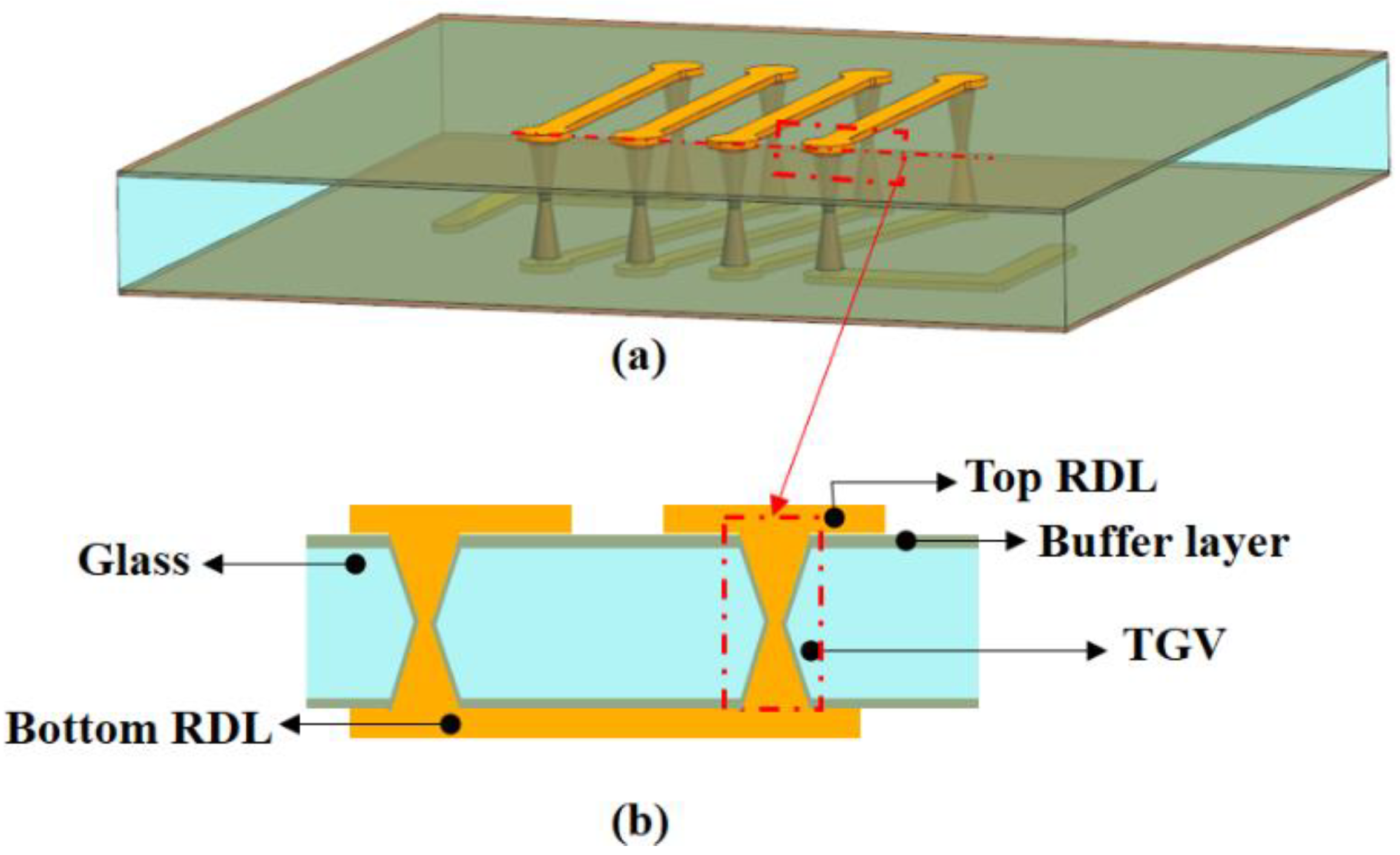

2. TGV Interconnection Structure Packaging Design

2.1. 3D Interconnection Structure for TGVs

2.2. Stress Analysis of TGV–Cu Structures

3. Effect of Geometric Parameters and Material on Wafer Reliability

3.1. Effect of Cu Plating Thickness in the Via

3.2. Effect of Buffer Layers

3.3. Effect of Material Parameters

4. Improved Process Flow and Stress Optimization for 3D Interconnection

4.1. Formation of Interconnection Vias

4.2. TGV Full Filling Preparation and RDL Formation

4.3. TGV Conformal Filling Formation

4.4. TGV Interconnection Structure Formation with a Buffer Layer

5. Conclusions

- (1)

- The copper percentage in the via, the thickness of the surface RDL, and the addition of the buffer layer all affect the stress distribution in the TGV structure. For the 3D-TGV interconnect structure, the stress increases with the increase in the copper percentage inside the hole, and the maximum stress value is concentrated inside the via. As the thickness of RDL increases, the stress maximum points are mainly distributed at the edges of TGV and RDL, and this part becomes the dangerous point of failure.

- (2)

- The CTE of different types of glass has the most significant effect on the stress in the interconnect structure, and it was found that reducing the value of thermal mismatch strain between glass and copper is one way to reduce the stress.

- (3)

- Adding a buffer layer between the glass and RDL can significantly improve stress-related reliability issues.

- (4)

- Reducing the surface RDL thickness or the hanging wall thickness in the via is an efficient technique to improve reliability in the actual process.

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Samanta, K.K. Cost-Effective Technologies for Next-Generation System on Package: Multilayer Transmission Lines and Interconnects for 5G and Millimeter-Wave. IEEE Microw. Mag. 2022, 23, 50–65. [Google Scholar] [CrossRef]

- Yi, H.; Ozturk, E.; Koelink, M.; Krimmling, J.; Damian, A.A.; Debski, W.; van Zeijl, H.W.; Zhang, G.; Poelma, R.H. Antenna-in-Package (AiP) Using Through-Polymer Vias (TPVs) for a 122-GHz Radar Chip. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 893–901. [Google Scholar] [CrossRef]

- Chen, Z.; Yu, D.; Jiang, F. Development of 3-D Wafer Level Packaging for SAW Filters Using Thin Glass Capping Technology. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 375–381. [Google Scholar] [CrossRef]

- Chien, C.H.; Lee, C.K.; Yu, H.; Liu, C.C.; Chen, P.S.; Chien, H.C.; Cheng, J.H.; Liao, L.L.; Dai, M.J.; Lin, Y.M.; et al. Performance and Process Comparison between Glass and Si Interposer for 3D-IC Integration. Int. Symp. Microelectron. 2013, 2013, 000618–000624. [Google Scholar] [CrossRef]

- Töpper, M.; Ndip, I.; Erxleben, R.; Brusberg, L.; Nissen, N.; Schröder, H.; Yamamoto, H.; Todt, G.; Reichl, H. 3-D Thin film interposer based on TGV (Through Glass Vias): An alternative to Si-interposer. In Proceedings of the 2010 Proceedings 60th Electronic Components & Technology Conference, Las Vegas, NV, USA, 1–4 June 2010. [Google Scholar]

- Sukumaran, V.; Chen, Q.; Liu, F.; Kumbhat, N.; Bandyopadhyay, T.; Chan, H.; Min, S.; Nopper, C.; Sundaram, V.; Tummala, R. Through-package-via formation and metallization of glass interposers. In Proceedings of the 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 557–563. [Google Scholar] [CrossRef]

- Sridharan, V.; Min, S.; Sundaram, V.; Sukumaran, V.; Hwang, S.; Chan, H.; Liu, F.; Nopper, C.; Tummala, R. Design and fabrication of bandpass filters in glass interposer with through-package-vias (TPV). In Proceedings of the 2010 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 530–535. [Google Scholar] [CrossRef]

- Shorey, A.; Pollard, S.; Streltsov, A.; Piech, G.; Wagner, R. Development of substrates for through glass vias (TGV) for 3DS-IC integration. In Proceedings of the 2012 IEEE 62nd Electronic Components and Technology Conference, San Diego, CA, USA, 29 May–1 June 2012; pp. 289–291. [Google Scholar] [CrossRef]

- Wang, B.K.; Chen, Y.-A.; Shorey, A.; Piech, G. Thin glass substrates development and integration for through glass vias (TGV) with copper (Cu) interconnects. In Proceedings of the 2012 7th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), Taipei, China, 24–26 October 2012; pp. 247–250. [Google Scholar] [CrossRef]

- Demir, K.; Ogawa, T.; Sundaram, V.; Raj, P.M.; Tummala, R.R. Reliability of Through-Package-Vias From via-First Processing With Ultra-Thin Glass. IEEE Trans. Device Mater. Reliab. 2017, 17, 683–691. [Google Scholar] [CrossRef]

- Lu, K.H.; Ryu, S.K.; Zhao, Q.; Zhang, X.; Im, J.; Huang, R.; Ho, P.S. Thermal stress induced delamination of through silicon vias in 3-D interconnects. In Proceedings of the 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 40–45. [Google Scholar]

- Sato, Y.; Imajyo, N.; Ishikawa, K.; Tummala, R.; Hori, M. Laser-drilling formation of through-glass-via (TGV) on polymer-laminated glass. J. Mater. Sci. Mater. Electron. 2019, 30, 10183–10190. [Google Scholar] [CrossRef]

- Demir, K.; Armutlulu, A.; Sundaram, V.; Raj, P.M.; Tummala, R.R. Reliability of Copper Through-Package Vias in Bare Glass Interposers. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 829–837. [Google Scholar] [CrossRef]

- Ahmed, O.; Jalilvand, G.; Pollard, S.; Okoro, C.; Jiang, T. The interfacial reliability of through-glass vias for 2.5D integrated circuits. Microelectron. Int. 2020, 37, 181–188. [Google Scholar] [CrossRef]

- Ryu, S.-K.; Lu, K.-H.; Zhang, X.; Im, J.-H.; Ho, P.S.; Huang, R. Impact of Near-Surface Thermal Stresses on Interfacial Reliability of Through-Silicon Vias for 3-D Interconnects. IEEE Trans. Device Mater. Reliab. 2011, 11, 35–43. [Google Scholar] [CrossRef] [Green Version]

- Tang, T.; Yuan, Y.; Yalikun, Y.; Hosokawa, Y.; Li, M.; Tanaka, Y. Glass based Micro Total Analysis Systems: Materials, Fabrication methods, and Applications. Sens. Actuators B Chem. 2021, 339, 129859. [Google Scholar] [CrossRef]

- Chen, Z.; Yu, D.; Zhang, M.; Jiang, F. Development and Reliability Study of 3-D Wafer Level Packaging for SAW Filter Using Thin Film Capping. IEEE Trans. Compon. Packag. Manuf. Technol. 2021, 11, 1047–1054. [Google Scholar] [CrossRef]

| Material | Elasticity Modules (GPa) | Poisson’s Ratio | CTE (ppm/°C) | Tg (°C) |

|---|---|---|---|---|

| Cu | 120 | 0.3 | 16.4 | |

| Glass1 | 72.7 | 0.16 | 0.57 | |

| Glass2 | 74.8 | 0.238 | 3.2 | 717 |

| Glass3 | 64 | 0.2 | 3.25 | 525 |

| Glass4 | 72.9 | 0.208 | 7.2 | 557 |

| Glass5 | 69.3 | 0.212 | 7.58 | |

| Glass6 | 71 | 0.2 | 9.4 | 542 |

| Material | Elasticity Modules (GPa) | Poisson’s Ratio | CTE (ppm/°C) | Tensile Strength (MPa) |

|---|---|---|---|---|

| HD4100 | 3.5 | 0.3 | 35 | 200 |

| BCB4000 | 2.9 | 0.34 | 42 | 87 |

| SU-8 | 4.1 | 0.28 | 50 | NA |

| HD8820 | 2.3 | 0.25 | 60 | 170 |

| SiO2 | 69 | 0.17 | 0.6 | 45 |

| Si3N4 | 300 | 0.26 | 3.5 | NA |

| Items | Structure A | Structure B | ||

|---|---|---|---|---|

| Material | SiO2 | Si3N4 | SiO2 | Si3N4 |

| The stress of the TGV edge (MPa) | 259.92 | 257.63 | 132.64 | 140.82 |

| Shear stress in the side of the via (MPa) | 256.35 | 256.03 | 132.74 | 127.58 |

| The stress of the RDL edge (MPa) | 141.72 | 157.21 | 117.16 | 100.49 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, J.; Chen, Z.; Qin, F.; Yu, D. Thermo-Mechanical Reliability Study of Through Glass Vias in 3D Interconnection. Micromachines 2022, 13, 1799. https://doi.org/10.3390/mi13101799

Zhao J, Chen Z, Qin F, Yu D. Thermo-Mechanical Reliability Study of Through Glass Vias in 3D Interconnection. Micromachines. 2022; 13(10):1799. https://doi.org/10.3390/mi13101799

Chicago/Turabian StyleZhao, Jin, Zuohuan Chen, Fei Qin, and Daquan Yu. 2022. "Thermo-Mechanical Reliability Study of Through Glass Vias in 3D Interconnection" Micromachines 13, no. 10: 1799. https://doi.org/10.3390/mi13101799

APA StyleZhao, J., Chen, Z., Qin, F., & Yu, D. (2022). Thermo-Mechanical Reliability Study of Through Glass Vias in 3D Interconnection. Micromachines, 13(10), 1799. https://doi.org/10.3390/mi13101799