Manufacturability and Stress Issues in 3D Silicon Detector Technology at IMB-CNM

Abstract

1. Introduction

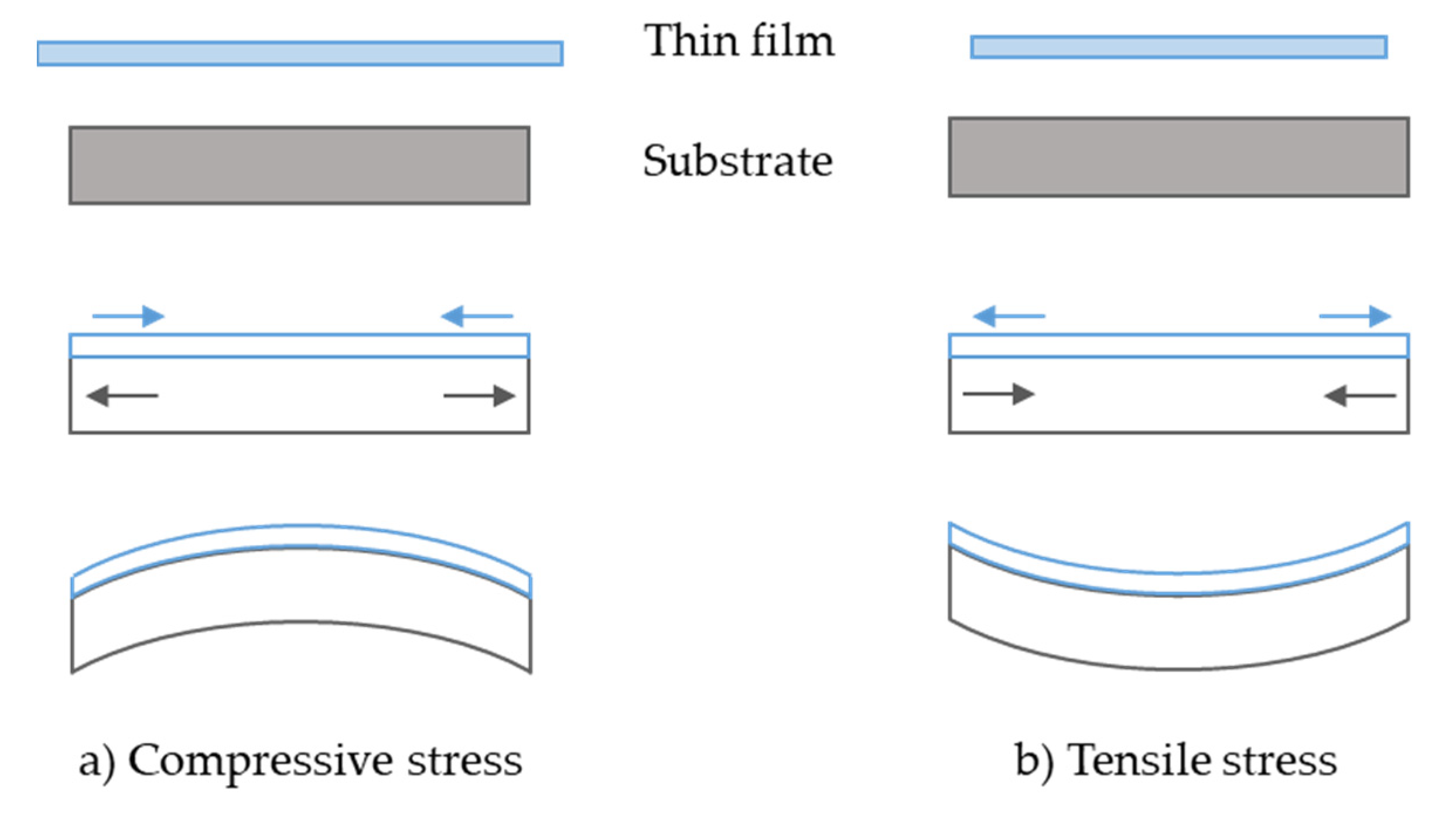

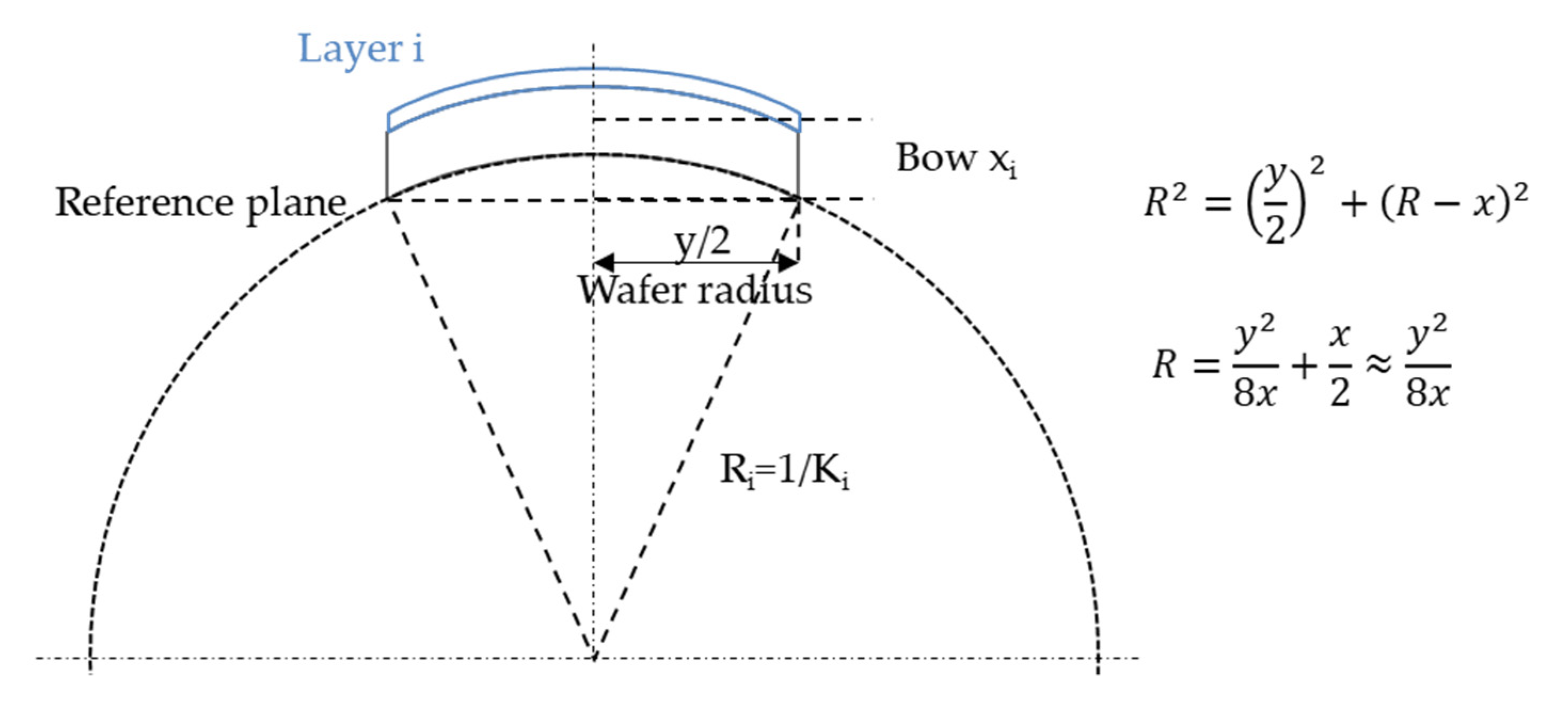

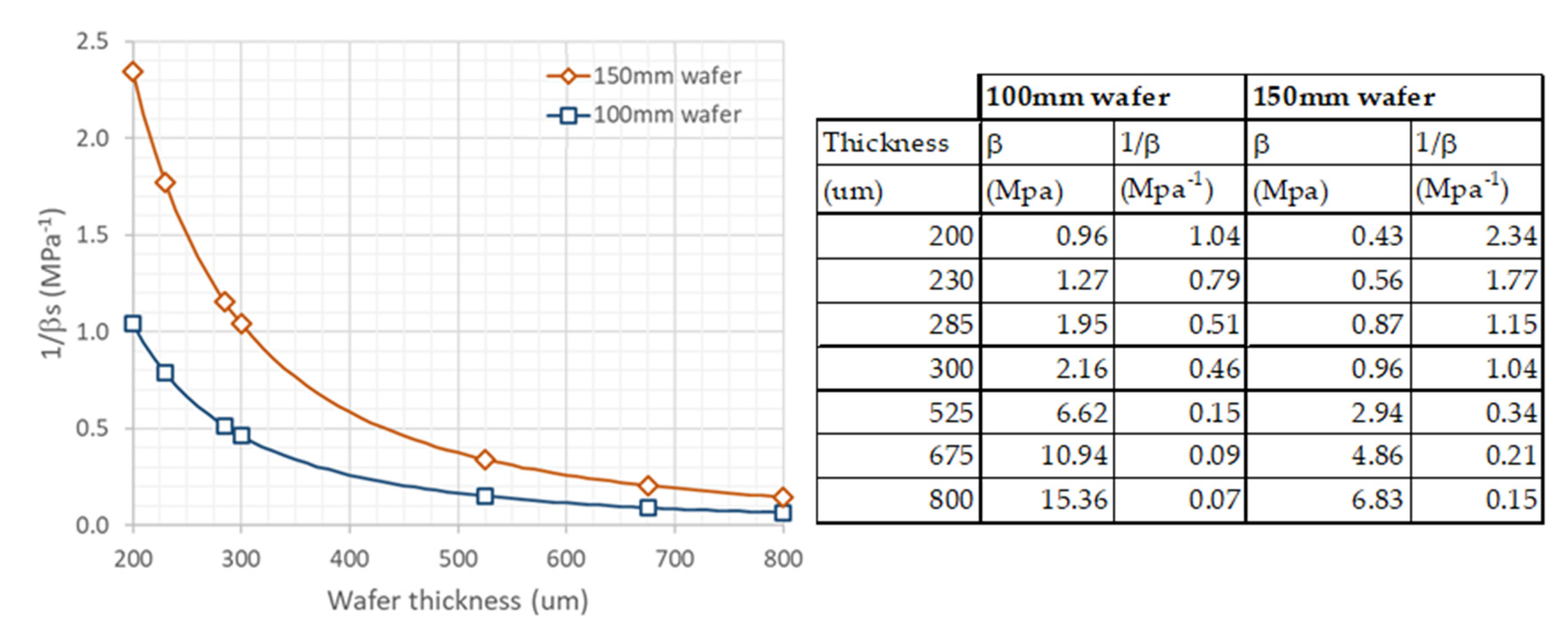

2. Stress and Wafer Bow in Silicon Manufacturing

2.1. Basics of Stress in Semiconductor Manufacturing

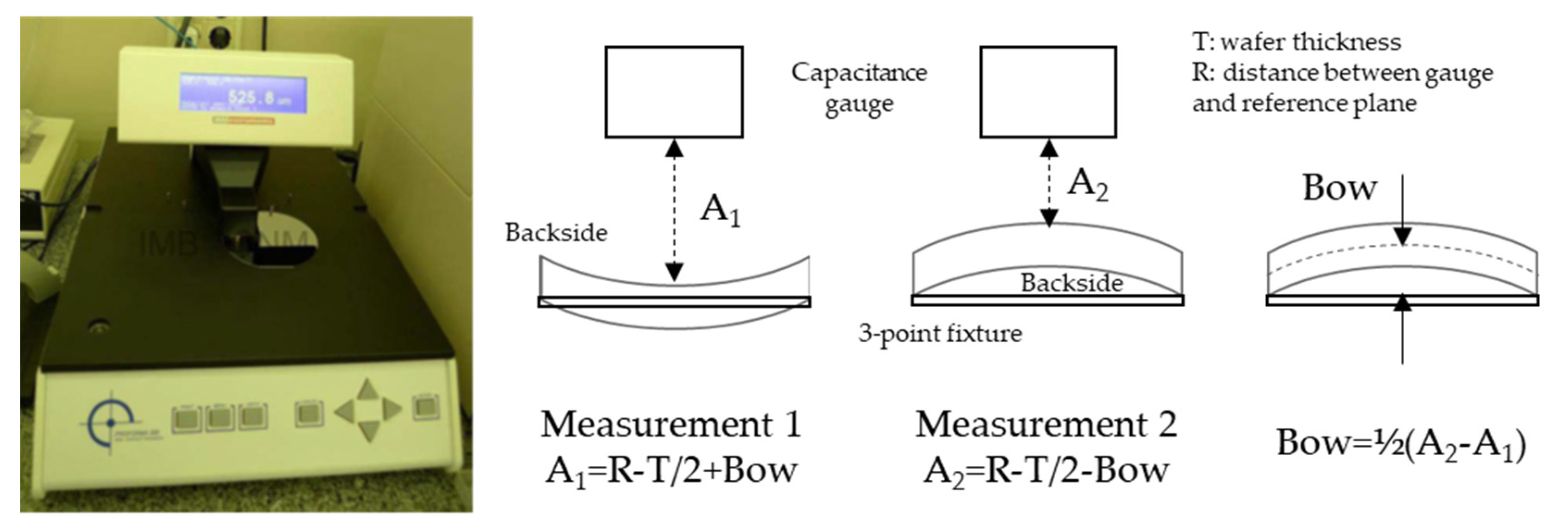

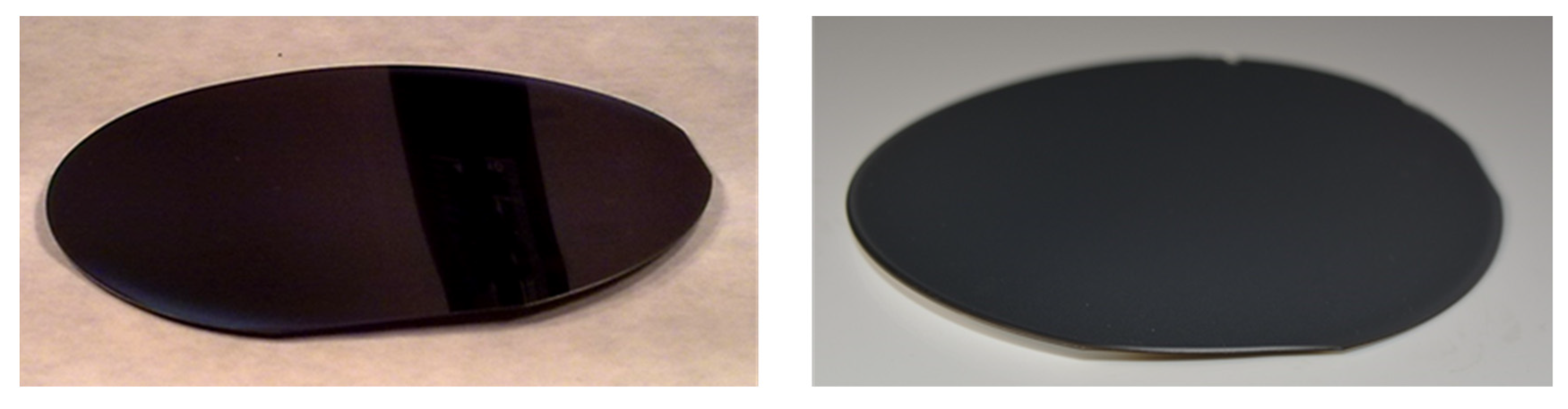

2.2. Bow Measurement at Microelectronics Institute of Barcelona (IMB-CNM)

3. Consequences of Bow on Manufacturability

3.1. Photolithography

3.2. Stress and Wafer Breakage

3.3. Application to Planar Process: Toy Model

4. Overview of Fabrication Technologies for 3D Detectors

4.1. Parker’s Proposal and First Productions at Stanford and SINTEF

- Deep reactive ion etching (DRIE) for the etching of high aspect ratio electrodes within the silicon volume.

- Polysilicon deposited by low pressure chemical vapor deposition (LPCVD) to ensure a conformal coating on electrode sidewalls and bottom, and a homogeneous dopant diffusion along the electrodes, due the high diffusion coefficient of dopants in polysilicon compared to silicon.

- Diffusion doping of p+ and n+ electrodes: these “old” processes are key to 3D technology since implantation is unable to provide a uniform doping in the high aspect ratio electrodes.

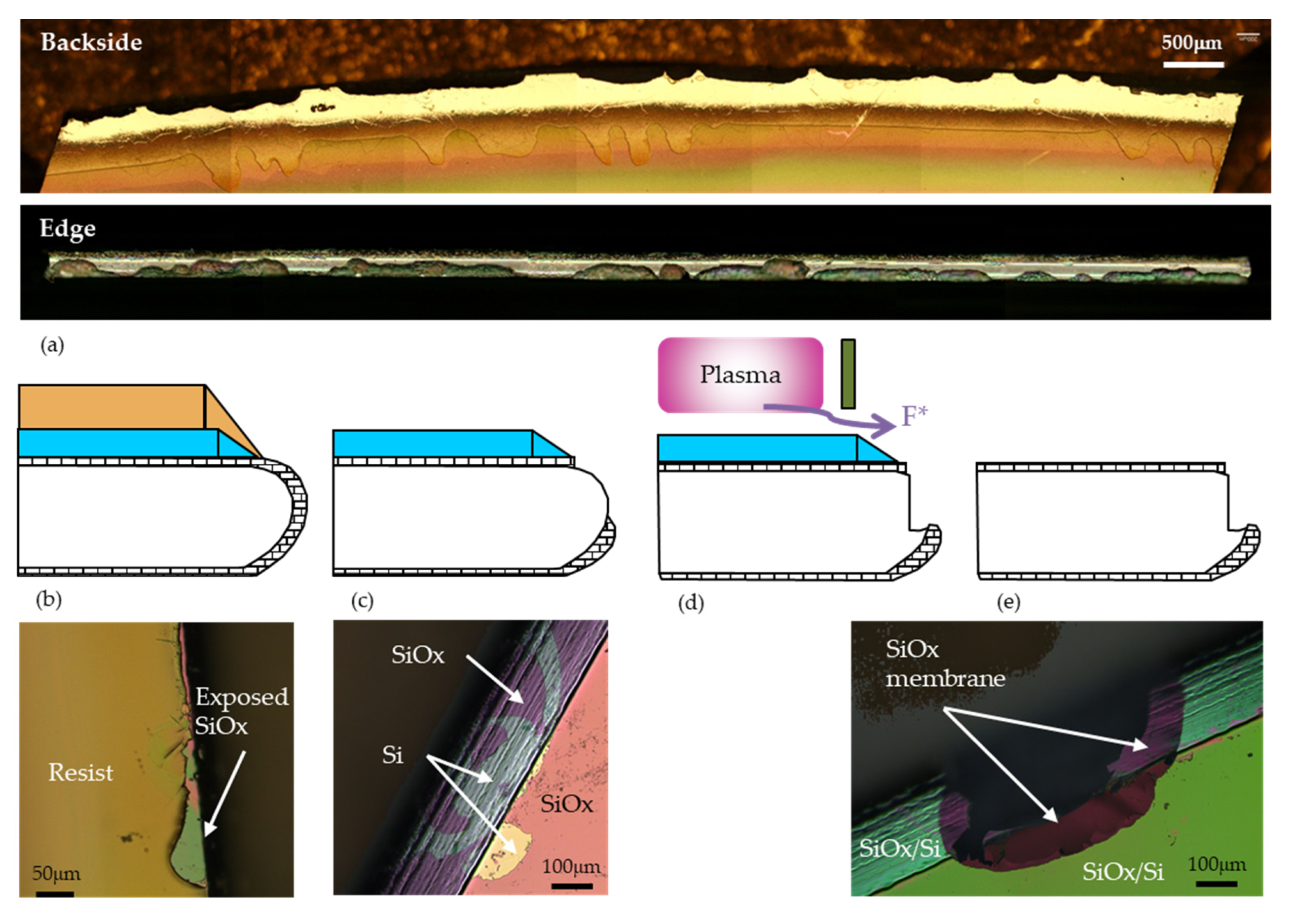

- DRIE mask: Aluminum was substituted for thick resist, as neither resist nor silicon oxide offered sufficient selectivity for the long high aspect ratio etching [32];

- When the n-type electrodes were doped and filled, they were capped with a protection oxide of 300 nm. Note that polysilicon filling was still performed at Stanford Nanofabrication Facility because of limitations in the polysilicon process at SINTEF MiNaLab.

- A final passivation of 500 nm silicon oxide and 250 nm silicon nitride was deposited by plasma-enhanced chemical vapor deposition (PECVD) to guarantee protection from scratches, humidity, and contamination from outer world.

- Different oxide thickness between front and backsides of the wafers, leading to a bow around −130 μm [31]. Silicon nitride was deposited to avoid this asymmetry, and bow was reduced to +20 μm [33]. In both cases, wafer thickness was not directly specified, but if it was measured on the wafer mentioned in those papers (process wafer of 250 μm bonded on a 350 μm support wafer) these bow values imply really a large amount of stress, insuperable on thinner wafer, or after grinding of the support wafer;

- Polysilicon filling of the electrodes also induced a large stress, but this was mitigated by careful handling and planning [33].

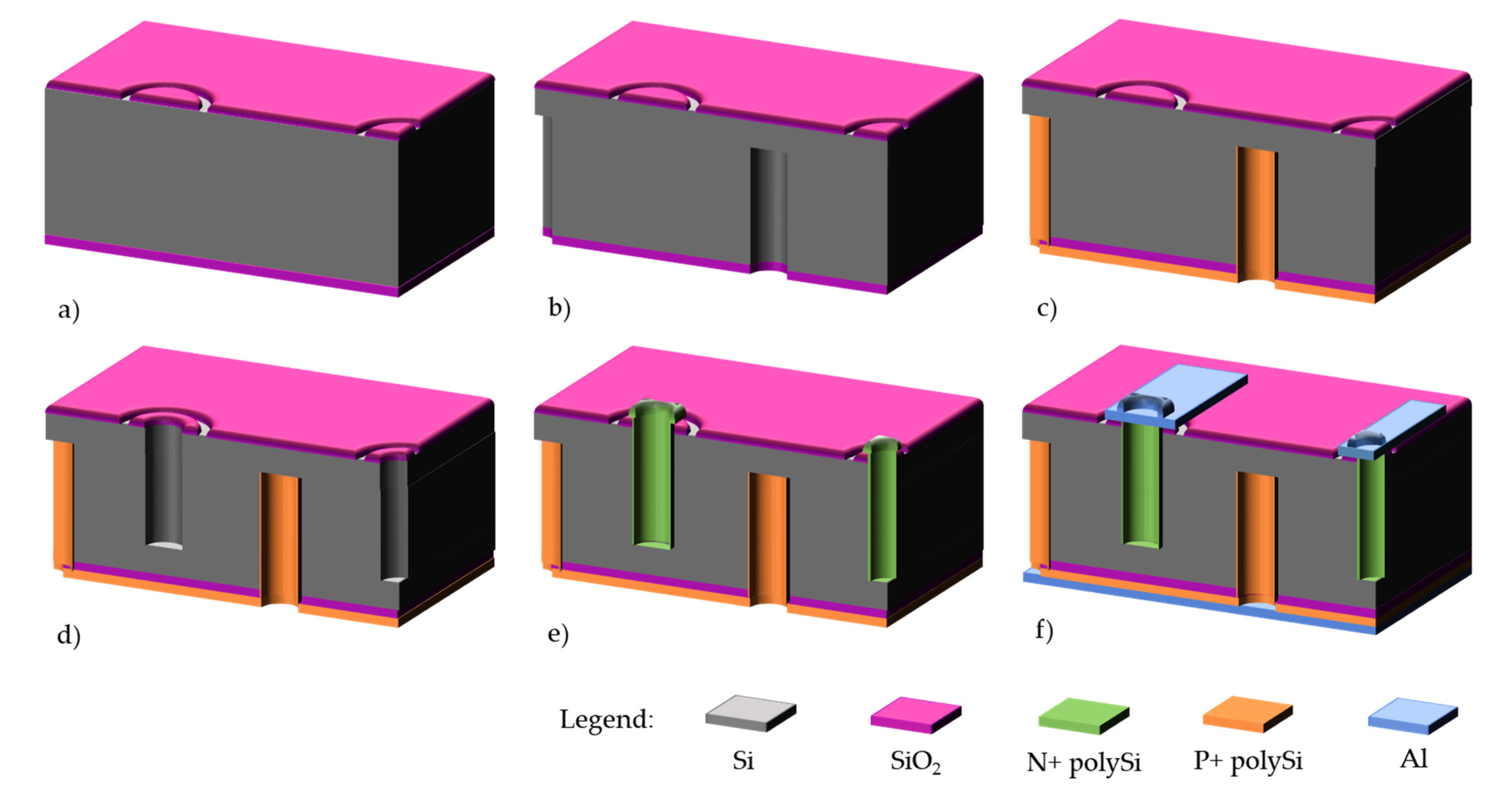

4.2. Double Side Process (IMB-CNM, FBK)

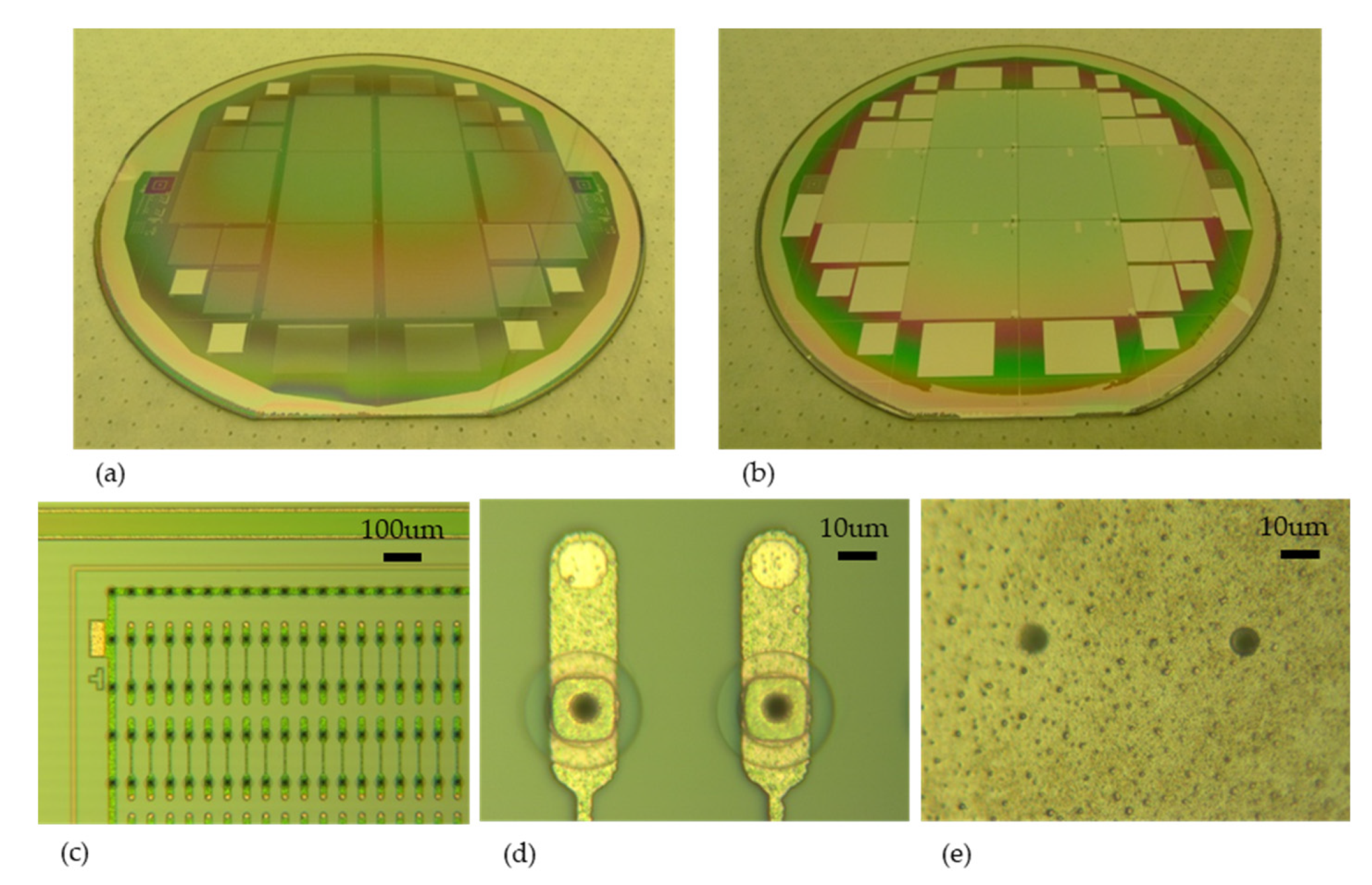

4.3. 3D-SOI Technology at IMB-CNM

- The p+ electrodes are not filled, but sealed, to minimize the amount of polysilicon deposited, and limit the wafer bow (see discussion below).

- The n+ electrodes are not filled: there is no further DRIE, so no risk of further etching; and the resist spins perfectly over the open narrow contacts, so that photolithography can be performed normally.

- The n+ electrodes are not etched down to the buried oxide, but 30 μm from it.

- The p+ electrodes are not accessed from the front side, but from the backside via a potassium hydroxide (KOH) etching of the support wafer and subsequent backside metallization.

- Contrary to process on standard wafers, field oxidation contributes consequently to bow. A SOI wafer is not a perfectly strain-relaxed system, but a complex balance of compressive stress in the buried oxide and tensile stress in silicon [41]. Moreover, low to null initial bow in our wafers is achieved because of a ~1 μm backside oxide. Field oxidation at high temperature might relax part of the strain and break the initial balance.

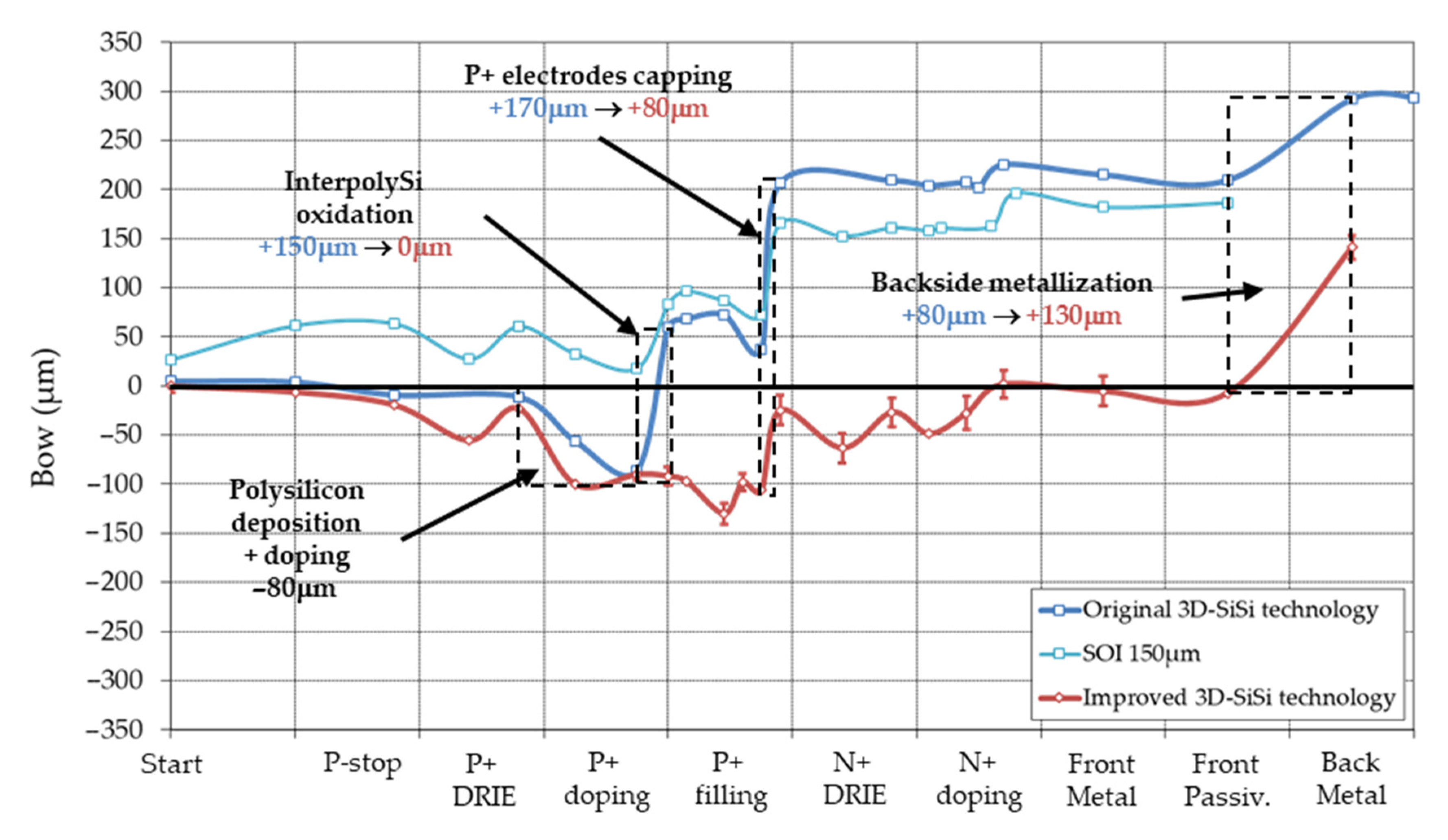

- As in 3D-DS technology, a 200 nm oxide is thermally grown on the p+ doped polysilicon. It serves as an etch-stop for the undoped polysilicon etching (inter-polysilicon oxidation). It adds, depending on wafers, from +50 to +70 μm bow, which is slightly lower than measured on 3D-DS technology in the same conditions (−100 μm; the opposite sign comes from the opposite side of the contacts).

- Finally, the p+ pads are capped with a 500 nm thermal oxide to protect them from further etching and processes, and also to improve the voltage breakdown strength with nearby n+ metal pads. This step induces a bow of 35 to 90 μm depending on SOI wafers.

4.4. 3D-SiSi Technology for High Luminosity LHC (HL-LHC)

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Parker, S.; Kenney, C.; Segal, J. 3D—A proposed new architecture for solid-state radiation detectors. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 1997, 395, 328–343. [Google Scholar] [CrossRef]

- Da Vià, C.; Dalla Betta, G.F.; Parker, S. Radiation Sensors with 3D Electrodes; CRC Press: Boca Raton, FL, USA; Taylor and Francis: Oxfordshire, UK, 2019. [Google Scholar]

- ATLAS IBL Collaboration. Prototype ATLAS IBL modules using the FE-I4 front-end readout chip. J. Instrum. 2012, 7, P11010. [Google Scholar] [CrossRef]

- Grinstein, S.; Cavallaro, E.; Chmeissani, M.; Dorholt, O.; Förster, F.; Lange, J.; Paz, I.L.; Manna, M.; Pellegrini, G.; Quirion, D.; et al. Module production of the one-arm AFP 3D pixel tracker. J. Instrum. 2017, 12, C01086. [Google Scholar] [CrossRef][Green Version]

- Ravera, F. The CT-PPS Project Detector Hardware and Operational Experience. In Proceedings of the 26th International Workshop On Vertex Detectors, Las Caldas, Spain, 10–15 September 2017; p. 015. [Google Scholar]

- Technical Design Report for the ATLAS Inner Tracker Pixel Detector. Available online: https://cds.cern.ch/record/2285585 (accessed on 17 December 2020).

- CMS Collaboration. he Phase-2 Upgrade of the CMS Outer Tracker. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2020, 979, 164432. [Google Scholar] [CrossRef]

- Kramberger, G.; Baselga, M.; Cindro, V.; Fernandez-Martinez, P.; Flores, D.; Galloway, Z.; Gorišek, A.; Greco, V.; Hidalgo, S.; Fadeyev, V.; et al. Radiation effects in Low Gain Avalanche Detectors after hadron irradiations. J. Instrum. 2015, 10, P07006. [Google Scholar] [CrossRef]

- Kramberger, G.; Cindro, V.; Flores, D.; Hidalgo, S.; Hiti, B.; Manna, M.; Mandić, I.; Mikuž, M.; Quirion, D.; Pellegrini, G.; et al. Timing performance of small cell 3D silicon detectors. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2019, 934, 26–32. [Google Scholar] [CrossRef]

- ATLAS Insertable B-Layer Technical Design Report. Available online: https://cds.cern.ch/record/1291633/files/ATLAS-TDR-019.pdf (accessed on 17 December 2020).

- Doerner, M.F.; Nix, W.D. Stresses and deformation processes in thin films on substrates. Crit. Rev. Solid State Mater. Sci. 1988, 14, 225–268. [Google Scholar] [CrossRef]

- Thornton, J.A.; Hoffman, D. Stress-related effects in thin films. Thin Solid Films 1989, 171, 5–31. [Google Scholar] [CrossRef]

- Townsend, P.H.; Barnett, D.M.; Brunner, T.A. Elastic relationships in layered composite media with approximation for the case of thin films on a thick substrate. J. Appl. Phys. 1987, 62, 4438–4444. [Google Scholar] [CrossRef]

- Hopcroft, M.; Nix, W.D.; Kenny, T.W. What is the Young’s Modulus of Silicon? J. Microelectromechanical Syst. 2010, 19, 229–238. [Google Scholar] [CrossRef]

- Stoney, G.G. The tension of metallic films deposited by electrolysis. Proc. R. Soc. Lond. Ser. A Math. Phys. Sci. 1909, 82, 172–175. [Google Scholar] [CrossRef]

- Available online: https://www.mtiinstruments.com/products/metrology-systems/semiconductor-metrology-system/ (accessed on 17 December 2020).

- Stallhofer, P. Why Are Silicon Wafers as Thick as They Are? In Ultra-thin Chip Technology and Applications; Springer Science and Business Media LLC: Berlin/Heidelberg, Germany, 2010; pp. 3–12. [Google Scholar]

- Baylies, W. A review of flatness effects in microlithographic technology. Microelectron. Reliab. 1981, 21, 757. [Google Scholar] [CrossRef]

- Turner, K.T.; Veeraraghavan, S.; Sinha, J.K. Relationship between localized wafer shape changes induced by residual stress and overlay errors. J. Micro Nanolithography MEMS MOEMS 2012, 11, 013001. [Google Scholar] [CrossRef]

- Brunner, T.A.; Menon, V.C.; Wong, C.W.; Gluschenkov, O.; Belyansky, M.P.; Felix, N.M.; Ausschnitt, C.P.; Vukkadala, P.; Veeraraghavan, S.; Sinha, J.K. Characterization of wafer geometry and overlay error on silicon wafers with nonuniform stress. J. Micro Nanolithography MEMS MOEMS 2013, 12, 043002. [Google Scholar] [CrossRef]

- Petersen, K.E. Silicon as a mechanical material. Proc. IEEE 1982, 70, 420–457. [Google Scholar] [CrossRef]

- Flamm, D.L.; Donnelly, V.M.; Mucha, J.A. The reaction of fluorine atoms with silicon. J. Appl. Phys. 1981, 52, 3633–3639. [Google Scholar] [CrossRef]

- Kok, A.; Hansen, T.; Hansen, T.; Lieater, N.; Mielnik, M.; Storas, P.; da Via, C.; Hasi, J.; Kenney, C.; Parker, S. 3D Detector Activities at SINTEF Minalab—Wafer Bonding and Deep Reactive Ion Etching. Available online: https://sintef.brage.unit.no/sintef-xmlui/bitstream/handle/11250/2429994/SINTEF+S7626.pdf?sequence=1 (accessed on 17 December 2020).

- Charavel, R.; Roig, J.; Altamirano-Sanchez, E.; Van Aelst, J.; Devriendt, K.; Van Wichelen, K.; Gassot, P.; Coppens, P.; De Backer, E. Wafer Bevel Protection During Deep Reactive Ion Etching. IEEE Trans. Semicond. Manuf. 2011, 24, 358–365. [Google Scholar] [CrossRef]

- Landsberger, L.M.; Tiller, W.A. Refractive index, relaxation times and the viscoelastic model in dry-grown SiO2 films on Si. Appl. Phys. Lett. 1987, 51, 1416–1418. [Google Scholar] [CrossRef]

- Wilson, R.; Weiss, B. A review of the properties of aluminium alloy films used during silicon device fabrication. Vacuum 1991, 42, 719–729. [Google Scholar] [CrossRef]

- Hearn, E.; Werner, D.; Doney, D. Film-Induced Stress Model. J. Electrochem. Soc. 1986, 133, 1749–1751. [Google Scholar] [CrossRef]

- Kenney, C.; Parker, S.; Segal, J.; Storment, C. Silicon detectors with 3-D electrode arrays: Fabrication and initial test results. IEEE Trans. Nucl. Sci. 1999, 46, 1224–1236. [Google Scholar] [CrossRef]

- Laermer, F.; Schilp, A. Method of Anisotropically Etching Silicon. US Patent 5,501,893, 5 August 1994. [Google Scholar]

- Morse, J.; Kenney, C.; Westbrook, E.; Naday, I.; Parker, S. 3DX: A micro-machined silicon crystallographic X-ray detector. Proc. SPIE 2002, 4784, 365–374. [Google Scholar]

- Hansen, T.-E.; Kok, A.; Hansen, T.; Lietaer, N.; Mielnik, M.; Storås, P.; da Via, C.; Hasi, J.; Kenney, C.; Parker, S. First fabrication of full 3D-detectors at SINTEF. J. Instrum. 2009, 4, P03010. [Google Scholar] [CrossRef]

- Kok, A.; Hansen, T.-E.; Hansen, T.; Jensen, G.U.; Lietaer, N.; Mielnik, M.; Storås, P. High aspect ratio deep RIE for novel 3D radiation sensors in high energy physics applications. In Proceedings of the 2009 IEEE Nuclear Science Symposium Conference Record (NSS/MIC), Orlando, FL, USA, 24 October–1 November 2009; pp. 1623–1627. [Google Scholar] [CrossRef]

- Kok, A.; Hansen, T.-E.; Hansen, T.; Lietaer, N.; Summanwar, A.; Kenney, C.; Hasi, J.; da Via, C.; Parker, S. Fabrication of 3D Silicon Sensors. 2010. Available online: https://www.osti.gov/biblio/1042666 (accessed on 17 December 2020).

- Fleta, C.; Pennicard, D.; Bates, R.; Parkes, C.; Pellegrini, G.; Lozano, M.; Wright, V.; Boscardin, M.; Betta, G.D.; Piemonte, C.; et al. Simulation and test of 3D silicon radiation detectors. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2007, 579, 642–647. [Google Scholar] [CrossRef]

- Pellegrini, G.; Lozano, M.; Ullan, M.; Bates, R.; Fleta, C.; Pennicard, D. First double-sided 3-D detectors fabricated at CNM-IMB. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2008, 592, 38–43. [Google Scholar] [CrossRef]

- Betta, G.D.; Boscardin, M.; Bosisio, L.; Piemonte, C.; Ronchin, S.; Zoboli, A.; Zorzi, N. New developments on 3D detectors at IRST. In Proceedings of the 2007 IEEE Nuclear Science Symposium Conference Record, Honolulu, HI, USA, 27 October–3 November 2007; Volume 2, pp. 983–987. [Google Scholar] [CrossRef]

- Adamczewska, J.; Budzynski, T. Stress in chemically vapour-deposited silicon films. Thin Solid Films 1984, 113, 271–285. [Google Scholar] [CrossRef]

- Melliar-Smith, C. Crystal Defects in Silicon Integrated Circuits—Their Cause and Effects. In Treatrise on Materials Science and Technology; Academic Press: Cambridge, MA, USA, 1977; pp. 47–149. [Google Scholar]

- Pellegrini, G.; Manna, M.; Quirion, D. 3D-Si single sided sensors for the innermost layer of the ATLAS pixel upgrade. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2019, 924, 69–72. [Google Scholar] [CrossRef]

- Terzo, S.; Chmeissani, M.; Giannini, G.; Grinstein, S.; Manna, M.; Pellegrini, G.; Quirion, D.; Furelos, D.V. Performance of Irradiated RD53A 3D Pixel Sensors. J. Instrum. 2019, 14, P06005. [Google Scholar] [CrossRef]

- Camassel, J.; Falkovsky, L.A.; Planes, N. Strain effect in silicon-on-insulator materials: Investigation with optical phonons. Phys. Rev. B 2000, 63, 035309. [Google Scholar] [CrossRef]

- Betta, G.D.; Boscardin, M.; Mendicino, R.; Ronchin, S.; Sultan, D.; Zorzi, N. Development of new 3D pixel sensors for phase 2 upgrades at LHC. In Proceedings of the 2015 IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), San Diego, CA, USA, 31 October–7 November 2015; Volume 10, pp. 1–4. [Google Scholar] [CrossRef]

- Hughes, D. Silicon-silicon direct wafer bonding. In Proceedings of the 2nd International Symposium on Semiconductor Wafer Bonding: Science, Technology, and Applications; Baumgart, H., Hunt, C.E., Schmidt, M., Abe, T., Eds.; Electrochemical Society: Pennington, NJ, USA, 1993; pp. 17–31. [Google Scholar]

- Gambino, J.P.; Adderly, S.A.; Knickerbocker, J.U. An overview of through-silicon-via technology and manufacturing challenges. Microelectron. Eng. 2015, 135, 73–106. [Google Scholar] [CrossRef]

- Lu, K.H.; Zhang, X.; Ryu, S.-K.; Im, J.; Huang, R.; Ho, P.S. Thermo-mechanical reliability of 3-D ICs containing through silicon vias. In Proceedings of the 2009 59th Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009; pp. 630–634. [Google Scholar] [CrossRef]

- Ryu, S.-K.; Jiang, T.; Lu, K.H.; Im, J.; Son, H.-Y.; Byun, K.-Y.; Huang, R.; Ho, P.S. Characterization of thermal stresses in through-silicon vias for three-dimensional interconnects by bending beam technique. Appl. Phys. Lett. 2012, 100, 041901. [Google Scholar] [CrossRef]

- Che, F.; Li, H.Y.; Zhang, X.; Gao, S.; Teo, K.H. Development of Wafer-Level Warpage and Stress Modeling Methodology and Its Application in Process Optimization for TSV Wafers. IEEE Trans. Compon. Packag. Manuf. Technol. 2012, 2, 944–955. [Google Scholar] [CrossRef]

- Parès, G.; Bresson, N.; Moreau, S.; Lapras, V.; Henry, D.; Sillon, N. Effects of stress in polysilicon VIA—First TSV technology. In Proceedings of the 2010 12th Electronics Packaging Technology Conference, Singapore, 8–10 December 2010; pp. 333–337. [Google Scholar]

- Garcia, F.; Pellegrini, G.; Balbuena, J.; Lozano, M.; Orava, R.; Ullan, M. A novel ultra-thin 3D detector for plasma diagnositcs at JET and ITER tokamaks. Nucl. Instr. Meth. Phys. Res. 2009, 607, 57–60. [Google Scholar] [CrossRef]

- Esteban, S.; Fleta, C.; Guardiola, C.; Jumilla, C.; Pellegrini, G.; Quirion, D.; Rodriguez, J.; Lozano, M. Microstructured silicon neutron detectors for security applications. J. Instrum. 2014, 9, C12006. [Google Scholar] [CrossRef]

- Martinéz, P.F.; Flores, D.; Villena, S.H.; Jorda, X.; Perpina, X.; Quirion, D.; Ré, L.; Ullán, M.; Vellvehi, M. A New Vertical JFET Power Device for Harsh Radiation Environments. Energies 2017, 10, 256. [Google Scholar] [CrossRef]

- Guardiola, C.; Quirion, D.; Pellegrini, G.; Fleta, C.; Esteban, S.; Cortes-Giraldo, M.; Gomez, F.; Solberg, T.; Carabe, A.; Lozano, M. Silicon-based three-dimensionak microstructures for radiation dosimetry in hadrontherapy. Appl. Phys. Lett. 2015, 107, 023505. [Google Scholar] [CrossRef]

| Materials | CET | B | Ref |

|---|---|---|---|

| 10−6K−1 | GPa | ||

| Silicon | 2.5 | 180 | [Hopcroft10] |

| Thermal SiO2 | 0.5 | 164 | [Sinha78] |

| LPCVD Si3N4 | 2.8 | 3500 | [Sinha78] |

| Aluminium | 23.2 | 84 | [Jamting97] |

| Step | Layer | Covered Area | Stress (Mpa) | ∆Bow | ||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Material | Thickn. | Temp. | CTE | B | Front | Back | Front | Back | (µm) | |

| (nm) | (°C) | (10−6K−1) | (GPa) | |||||||

| Process start | Silicon | 2.5 | 0.0 | 0.0 | 0.0 | |||||

| Field oxidation | Silicon oxide | 800 | 1100 | 0.5 | 164 | 100% | 100% | 354.2 | 354.2 | 0.0 |

| Contact definition | Silicon oxide | 800 | 1100 | 0.5 | 164 | 64% | 0% | 354.2 | 0..0 | 141.9 |

| Front metallization | Aluminium | 1000 | 100 | 23.2 | 84 | 100% | 0% | −139.1 | 0.0 | −109.5 |

| Front metal etching | Aluminium | 1000 | 100 | 23.2 | 84 | 37% | 0% | −139.1 | 0.0 | 40.3 |

| Backside metallization | Aluminium | 1000 | 100 | 23.2 | 84 | 0% | 100% | 0.0 | −139.1 | 164.3 |

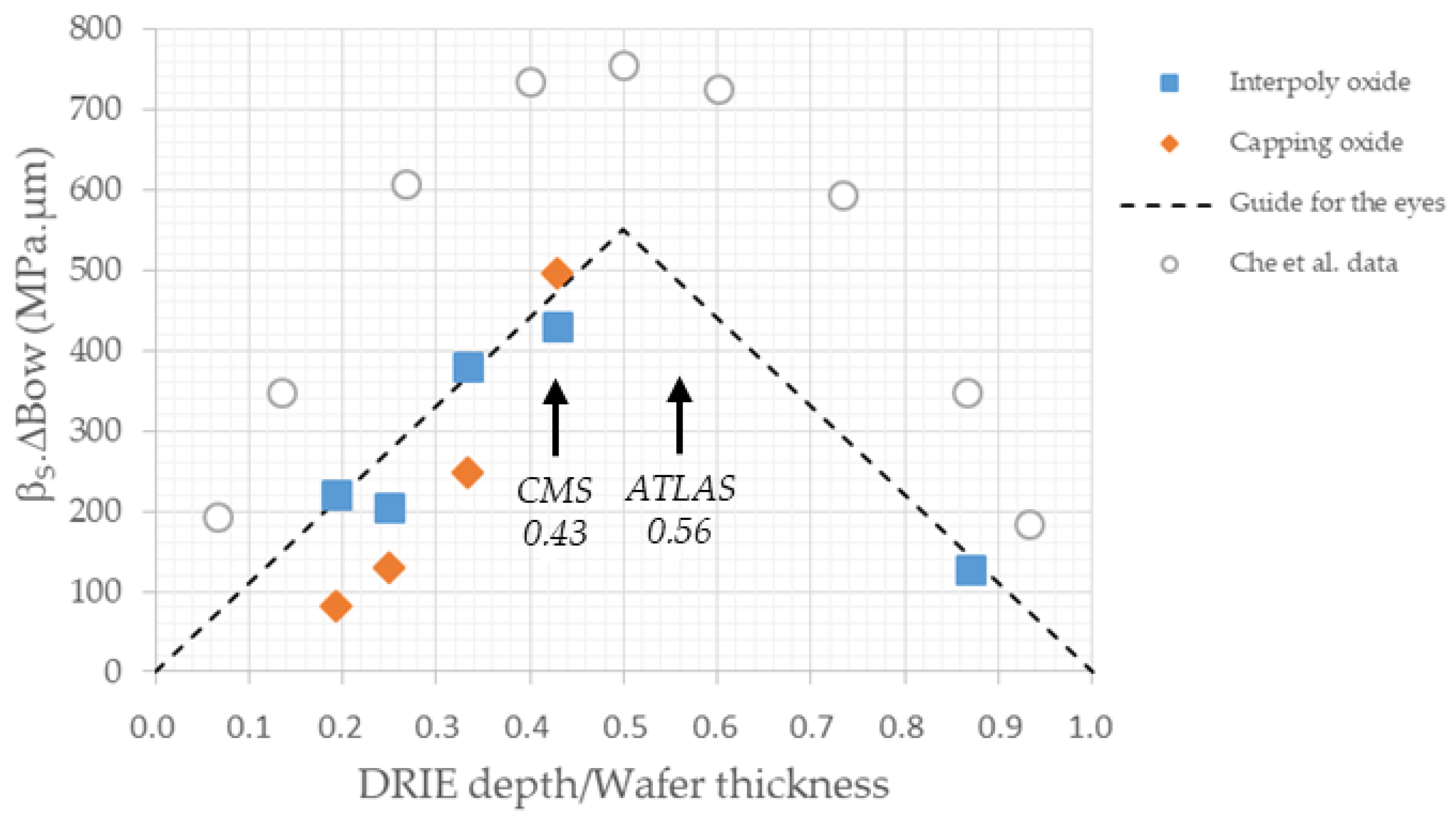

| InterPolySi Oxide | Capping Oxide | |||||||

|---|---|---|---|---|---|---|---|---|

| Technology | Wafer Total Thickness (µm) | 3D P+ Column Depth (µm) | Ratio | Βs (MPa) | ∆Bow (µm) | Βs. ∆Bow (Mpa. µm) | ∆Bow (µm) | Βs. ∆Bow (Mpa. µm) |

| 3D-DS improved | 230 | 200 | 0.87 | 1.27 | 101.1 | 128.4 | ||

| 3D-SOI 150mm | 450 | 150 | 0.33 | 4.86 | 78.4 | 380.9 | 88.1 | 428.3 |

| 3D-SOI 100mm | 400 | 100 | 0.25 | 3.84 | 53.1 | 203.9 | 33.7 | 129.4 |

| 3D-SOI 72mm | 372 | 72 | 0.19 | 3.32 | 66.2 | 219.7 | 25.0 | 83.0 |

| 3D-SOI original | 350 | 150 | 0.43 | 2.94 | 146.0 | 429.2 | 168.8 | 496.3 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Quirion, D.; Manna, M.; Hidalgo, S.; Pellegrini, G. Manufacturability and Stress Issues in 3D Silicon Detector Technology at IMB-CNM. Micromachines 2020, 11, 1126. https://doi.org/10.3390/mi11121126

Quirion D, Manna M, Hidalgo S, Pellegrini G. Manufacturability and Stress Issues in 3D Silicon Detector Technology at IMB-CNM. Micromachines. 2020; 11(12):1126. https://doi.org/10.3390/mi11121126

Chicago/Turabian StyleQuirion, David, Maria Manna, Salvador Hidalgo, and Giulio Pellegrini. 2020. "Manufacturability and Stress Issues in 3D Silicon Detector Technology at IMB-CNM" Micromachines 11, no. 12: 1126. https://doi.org/10.3390/mi11121126

APA StyleQuirion, D., Manna, M., Hidalgo, S., & Pellegrini, G. (2020). Manufacturability and Stress Issues in 3D Silicon Detector Technology at IMB-CNM. Micromachines, 11(12), 1126. https://doi.org/10.3390/mi11121126