3D AND-Type Stacked Array for Neuromorphic Systems

Abstract

1. Introduction

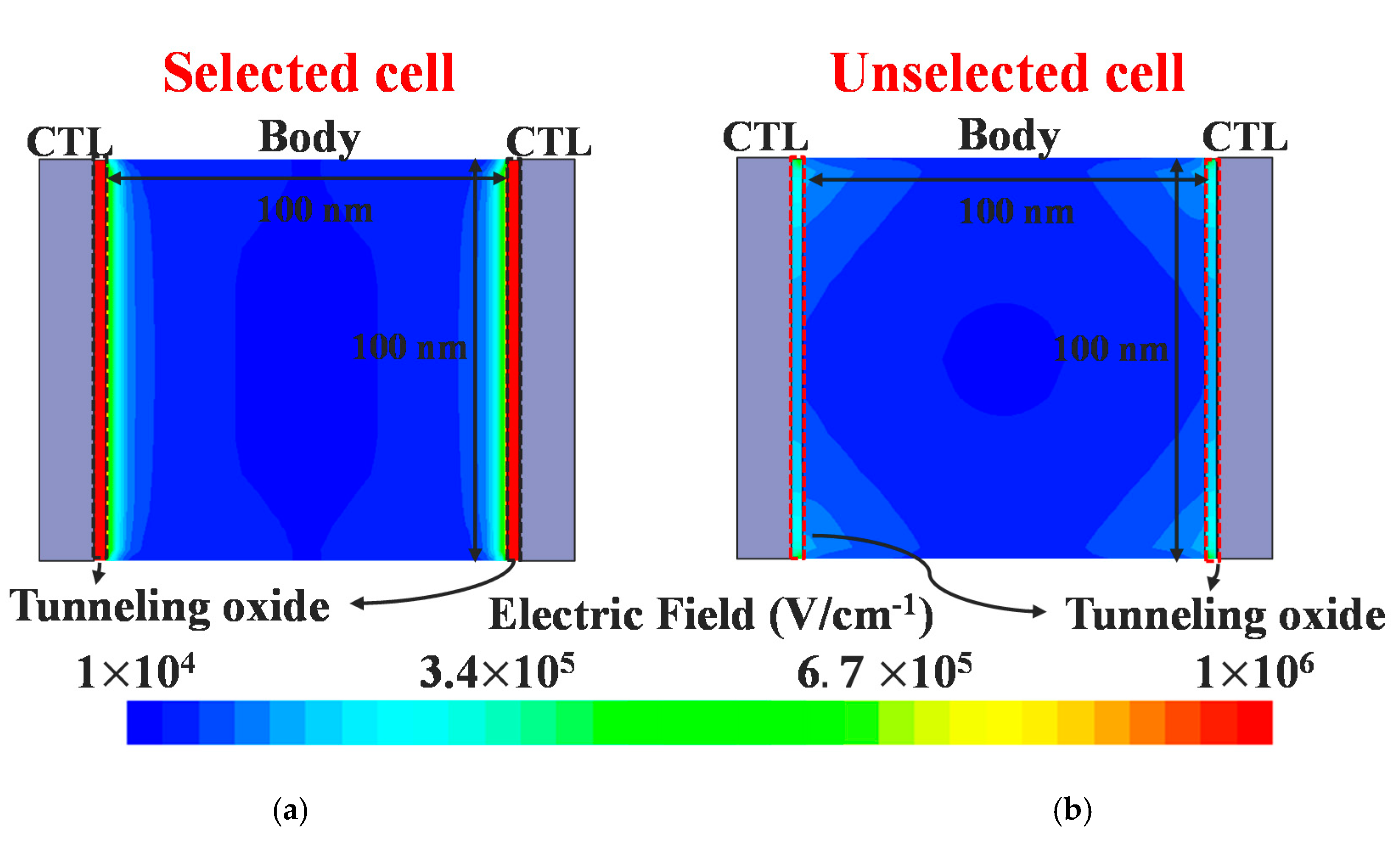

2. Characteristics of the AND-type Synapse Array

3. Results

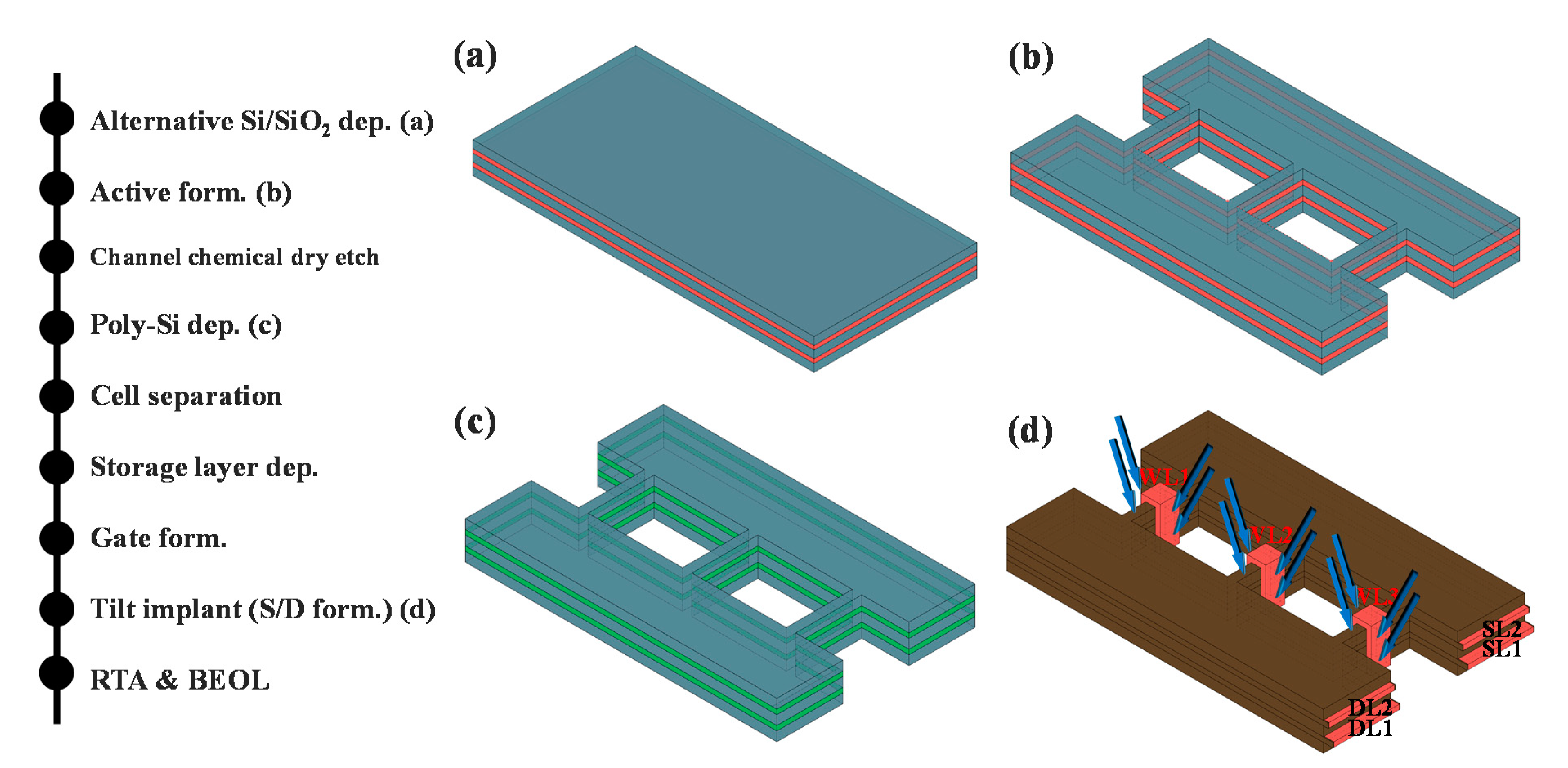

3.1. Process Flow of the 3D AND-type Synapse Array

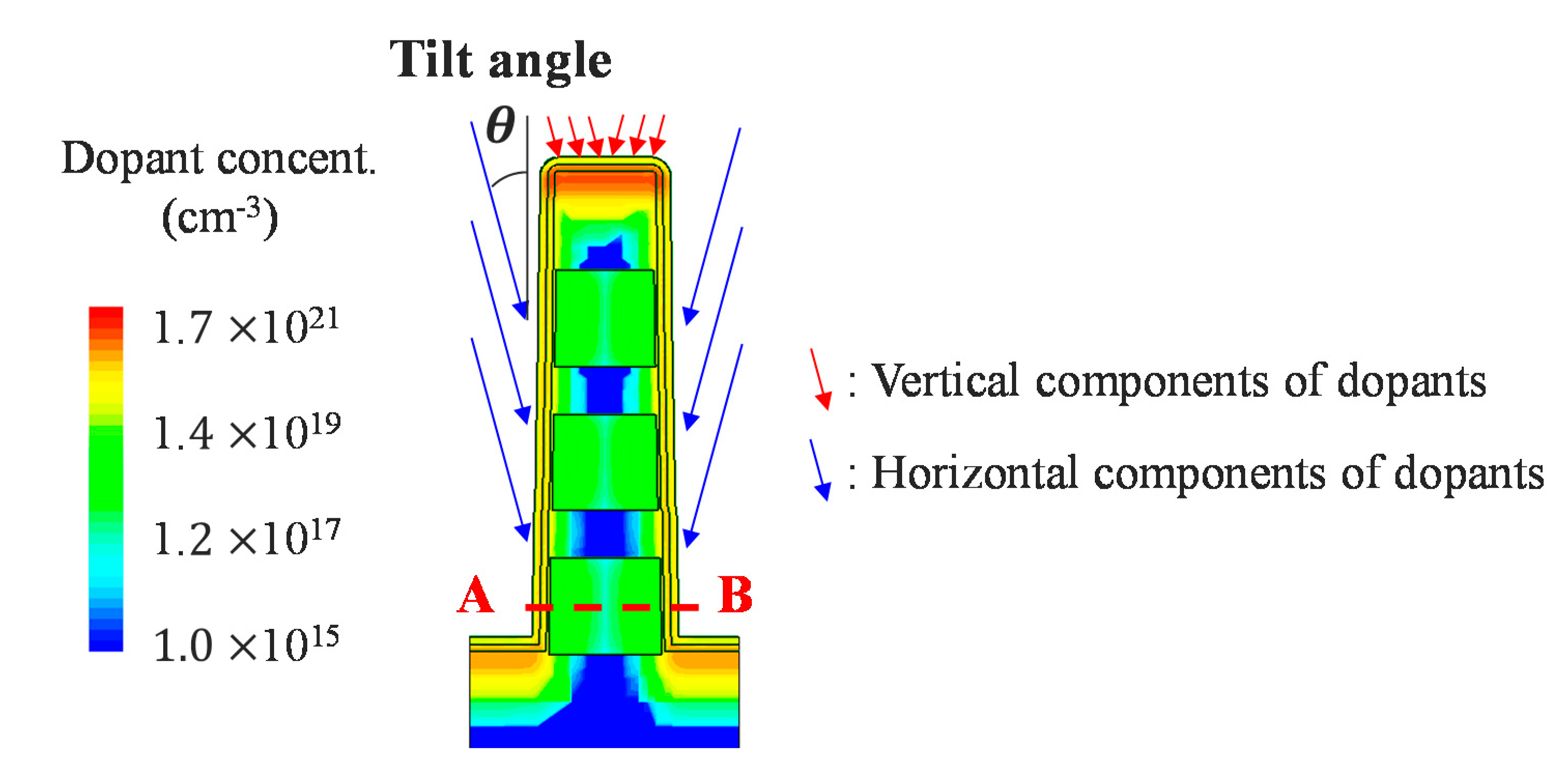

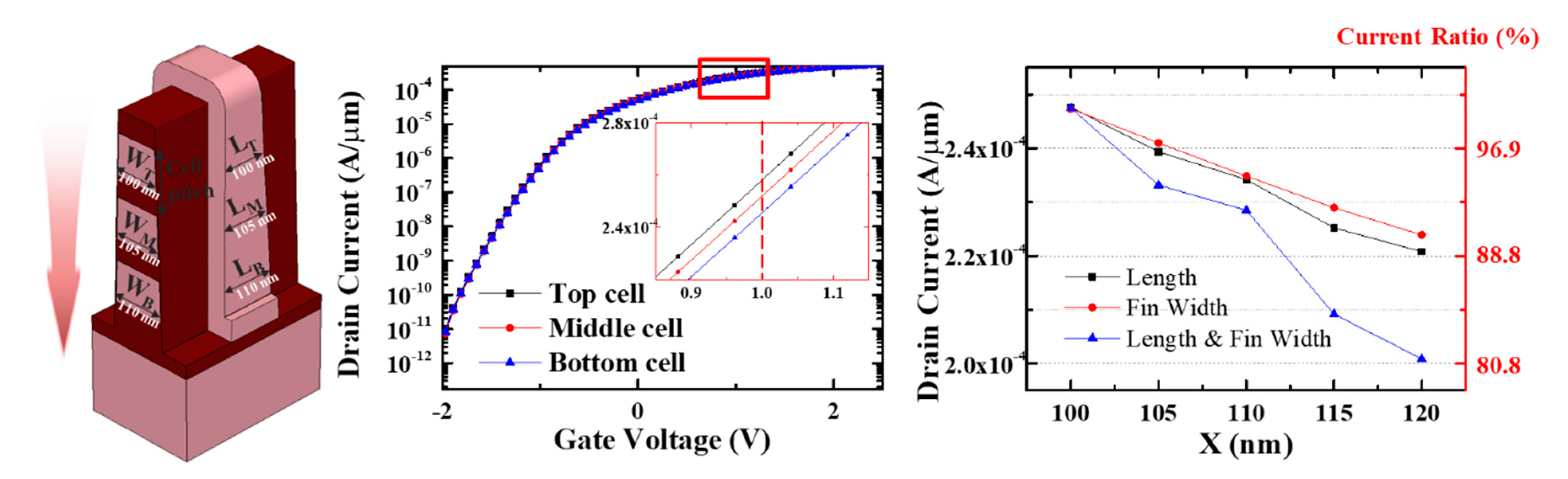

3.2. Cell-to-Cell Variation due to the Etch Slope

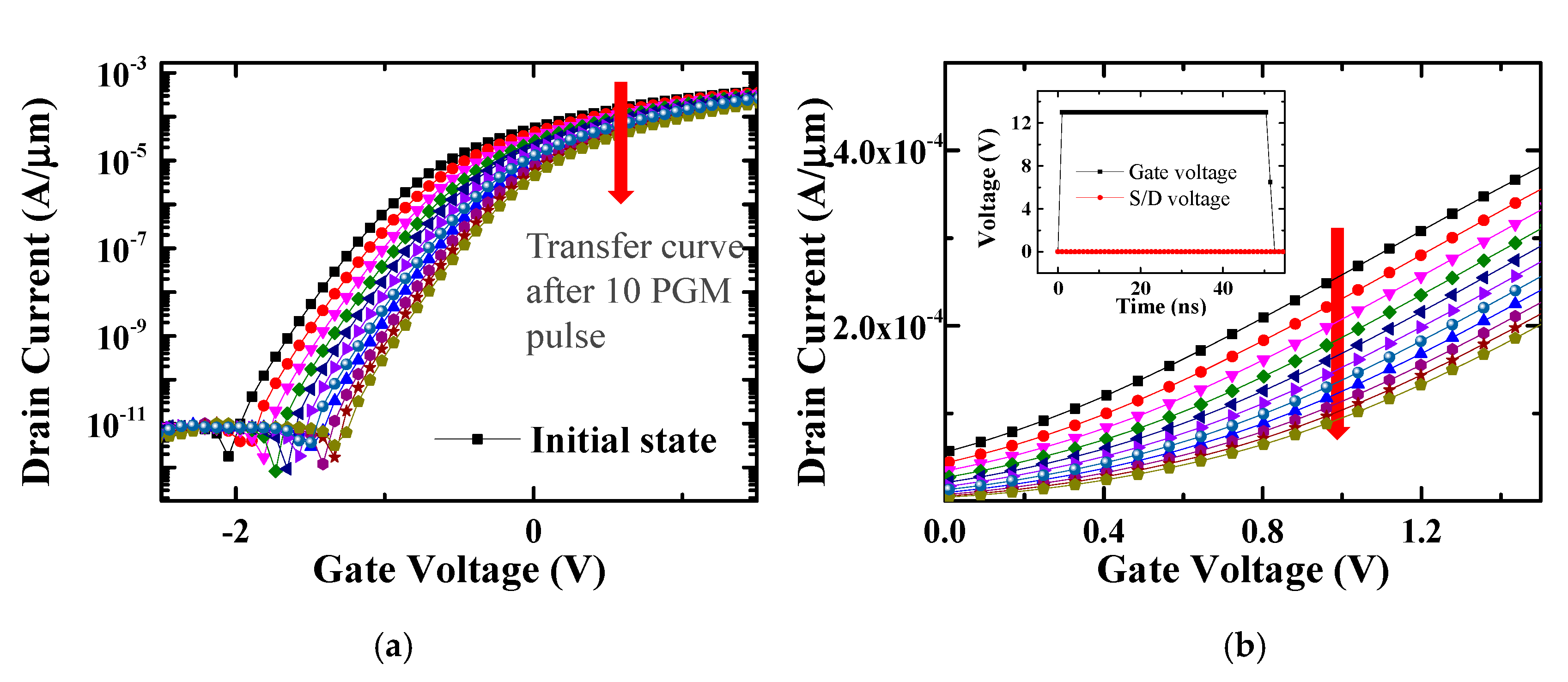

3.3. Electrical Characteristics of Synapse Array

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Yu, S.; Wu, Y.; Jeyasingh, R.; Kuzum, D.; Philip Wong, H.-S. An electronic synapse device based on metal oxide resistive switching memory for neuromorphic computation. IEEE Trans. Electron. Devices 2011, 58, 2729–2737. [Google Scholar] [CrossRef]

- Milo, V.; Pedretti, G.; Carboni, R.; Calderoni, A.; Ramaswamy, N.; Ambrogio, S.; Ielmini, D. Demonstration of hybrid CMOS/RRAM neural networks with spike time/rate-dependent plasticity. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Ambrogio, S.; Balatti, S.; Milo, V.; Carboni, R.; Wang, Z.-Q.; Caldernoi, A.; Ramaswamy, N.; Ielmini, D. Neuromorphic Learning and Recognition with One-Transistor-One-Resistor Synapses and Bistable Metal Oxide RRAM. IEEE Trans. Electron. Devices 2016, 63, 1508–1515. [Google Scholar] [CrossRef]

- Tosson, A.M.S.; Yu, S.; Anis, M.H.; Wei, L. A Study of the Effect of RRAM Reliability Soft Errors on the Performance of RRAM-Based Neuromorphic Systems. IEEE Trans. Very Large Scale Intergr. Vlsi Syst. 2017, 25, 3125–3137. [Google Scholar] [CrossRef]

- Kuzum, D.; Jeyasingh, R.G.D.; Lee, B.; Philip Wong, H.-S. Nanoelectronic Programmable Synapses Based on Phase Change Materials for Brain-Inspired Computing. Nano Lett. 2011, 12, 2179–2186. [Google Scholar] [CrossRef] [PubMed]

- Tan, S.H.; Lin, P.; Yeon, S.; Choi, S.; Park, Y.; Kim, J. Perspective: Uniform switching of artificial synapses for large-scale neuromorphic arrays. Appl. Phys. Lett. 2018, 6, 120901. [Google Scholar] [CrossRef]

- Hoffer, B.; Rana, V.; Menzel, S.; Waser, R.; Kvatinsky, S. Experimental Demonstration of Memristor-Aided Logic (MAGIC) Using Valence Change Memory (VCM. IEEE Trans. Electron. Devices 2020, 67, 3115–3122. [Google Scholar] [CrossRef]

- Liao, Y.; Wu, H.; Wan, W.; Zhang, W.; Gao, B.; Philip Wong, H.-S.; Qian, H. Novel In-Memory Matrix-Matrix Multiplication with Resistive Cross-Point Arrays. In Proceedings of the 2018 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 18–22 June 2018; pp. 31–32. [Google Scholar] [CrossRef]

- Huang, P.; Zhou, Y.; Xiang, Y.; Han, R.; Liu, L.; Liu, X.; Kang, J. Hardware implementation of RRAM based binarized neural networks. APL Mater. 2019, 7, 081105. [Google Scholar] [CrossRef]

- Kang, S.; Lee, J.; Kang, M.; Song, Y. Achievement of Gradual Conductance Characteristics Based on Interfacial Phase-Change Memory for Artificial Synapse Applications. Electronics 2020, 9, 1268. [Google Scholar] [CrossRef]

- Malavena, G.; Filippi, M.; Spinelli, A.S.; Compagnoni, C.M. Unsupervised Learning by Spike-Timing-Dependent Plasticity in a Mainstream NOR Flash Memory Array—Part I: Cell Operation. IEEE Trans. Electron. Devices 2019, 66, 4727–4732. [Google Scholar] [CrossRef]

- Malavena, G.; Filippi, M.; Spinelli, A.S.; Compagnoni, C.M. Unsupervised Learning by Spike-Timing-Dependent Plasticity in a Mainstream NOR Flash Memory Array—Part II: Array Learning. IEEE Trans. Electron. Devices 2019, 66, 4733–4738. [Google Scholar] [CrossRef]

- Guo, X.; Merrikh Bayat, F.; Prezioso, M.; Chen, Y.; Nguyen, B.; Do, N.; Strukov, D.B. Temperature-insensitive analog vector-by-matrix multiplier based on 55 nm NOR flash memory cells. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 30 April–3 May 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Malavena, G.; Spinelli, A.S.; Monzio Compagnoni, C. Implementing Spike-Timing-Dependent Plasticity and Unsupervised Learning in a Mainstream NOR Flash Memory Array. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Kim, C.-H.; Lee, S.; Woo, S.Y.; Kang, W.-M.; Lim, S.; Bae, J.-H.; Kim, J.; Lee, J.-H. Demonstration of Unsupervised Learning with Spike-Timing-Dependent Plasticity Using a TFT-Type NOR Flash Memory Array. IEEE Trans. Electron. Devices 2018, 65, 1774–1780. [Google Scholar] [CrossRef]

- Guo, X.; Merrikh Bayat, F.; Bavandpour, M.; Klachko, M.; Mahmoodi, M.R.; Prezioso, M.; Likharev, K.K.; Strukov, D.B. Fast, Energy-Efficient, Robust, and Reproducible Mixed-Signal Neuromorphic Classifier Based on Embedded NOR Flash Memory Technology. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Noh, Y.; Seo, Y.; Park, B.-G.; Lee, J.-H. Synaptic Devices Based on 3-D AND Flash Memory Architecture for Neuromorphic Computing. In Proceedings of the International Memory Workshop (IMW), Monterey, CA, USA, 12–15 May 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Malavena, G.; Petro, S.; Spinelli, A.S.; Monzio Compagnoni, C. Impact of Program Accuracy and Random Telegraph Noise on the Performance of a NOR Flash-based Neuromorphic Classifier. In Proceedings of the ESSDERC 2019—49th European Solid-State Device Research Conference (ESSDERC), Cracow, Poland, 23–26 September 2019; pp. 122–125. [Google Scholar] [CrossRef]

- Wang, Y.; Zhao, Y.; Khan, B.M.; Doherty, C.L.; Krayer, J.D.; White, M.H. A novel SONOS nonvolatile flash memory device using substrate hot-hole injection for write and gate tunneling for erase. Solid State Electron. 2004, 48, 2031–2034. [Google Scholar] [CrossRef]

- Kim, H.; Park, J.; Kwon, M.-W.; Lee, J.-H.; Park, B.-G. Silicon-Based floating-body synaptic transistor with frequency-dependent short- and long-term memories. IEEE Electron. Device Lett. 2016, 37, 249–252. [Google Scholar] [CrossRef]

- Baek, M.-H.; Jang, T.; Kim, H.; Park, J.; Kwon, M.-W.; Hwang, S.; Kim, S.; Lee, J.-J.; Park, B.-G. Grain boundary induced short-term memory effect in fully depleted thin-polysilicon devices. Jpn. J. Appl. Phys. 2019, 58, 1–5. [Google Scholar] [CrossRef]

- Mody, J.; Duffy, R.; Eyben, P.; Goossens, J.; Moussa, A.; Polspoel, W.; Berghmans, B.; Dal, M.J.H.V.; Pawlak, B.J.; Kaiser, M.; et al. Experimental studies of dose retention and activation in fin field-effect-transistor-based structures. J. Vac. Sci. Technol. B 2010, 28, C1H5. [Google Scholar] [CrossRef]

- Wang, L.; Brown, A.R.; Cheng, B.; Asenov, A. Simulation of 3D FinFET Doping Profiles by Ion Implantation. In Proceedings of the American Institute of Physics (AIP) Conference Proceedings, Valladolid, Spain, 25–29 June 2012; pp. 217–220. [Google Scholar] [CrossRef]

- Duffy, R.; Curatola, G.; Pawlak, B.J.; Doornbos, G.; Tak, K.V.D.; Breimer, P.; van Berkum, J.G.M.; Roozeboom, F. Doping fin field-effect transistor sidewalls: Impurity dose retention in silicon due to high angle incident ion implants and the impact on device performance. J. Vac. Sci. Technol. B 2008, 26, 402–407. [Google Scholar] [CrossRef]

- Cho, S.; Li, D.H.; Kim, D.-H.; Cho, I.H.; Park, B.-G. Channel Doping Concentration and Fin Width Effects on Self-Boosting in NAND-Type SONOS Flash Memory Array Based on Bulk-FinFETs. In Proceedings of the Nanotechnology Materials and Devices Conference (NMDC), Traverse City, Michigan, USA, 2–5 June 2009; pp. 251–254. [Google Scholar] [CrossRef]

- Liu, Y.; Matsukawa, T.; Endo, K.; O’uchi, S.; Sakamoto, K.; Tsukada, J.; Ishikawa, Y.; Yamauchi, H.; Masahara, M. Investigation of Low-Energy Tilted Ion Implantation for Fin-Type Double-Gate Metal–Oxide–Semiconductor Field-Effect Transistor Extension Doping. Jpn. J. Appl. Phys. 2010, 49, 04DC18. [Google Scholar] [CrossRef]

- Lenoble, D.; Doornbos, G.; de Keersgieter, A.; Pawlak, B.; Vandervorst, W.; Skotnicki, T. The junction challenges in the FinFETs device. In Proceedings of the International Workshop on Junction Technology, Shanghai, China, 15–16 May 2006; pp. 78–83. [Google Scholar] [CrossRef]

- Chang, R.-D.; Lin, P.-H. Simulation Study of Implantation Angle Variation and Its Impact on Device Performance. In Proceedings of the International Conference on Ion Implantation Technology (IIT), Tainan, Taiwan, 26–30 September 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Witters, L.; Son, N.J.; San, T.; Singanamalla, R.; Kerner, C.; Collaert, N.; De Meyer, K.; Jurczak, M. Treshold voltage modulation in FinFET devices through Arsenic Ion Implantation into TiN/HfSiON gate stack. In Proceedings of the IEEE International SOI Conference, Indian Wells, CA, USA, 1–4 October 2007; p. 32. [Google Scholar] [CrossRef]

- Mody, J.; Kambham, A.K.; Zschatzsch, G.; Schatzer, P.; Chiarella, T.; Collaert, N.; Witters, L.; Jurczak, M.; Horiguchi, N.; Gilbert, M.; et al. Dopant and carrier profiling in FinFET-based devices with sub-nanometer resolution. In Proceedings of the 2010 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 15–17 June 2010; pp. 195–196. [Google Scholar] [CrossRef]

- Gossmann, H.-J.L.; Agarwal, A.; Parrill, T.; Rubin, L.M.; Poate, J.M. On the FinFET extension implant energy. IEEE Trans. Nanotechnol. 2003, 2, 285–290. [Google Scholar] [CrossRef]

- Kedzierski, J.; Ieong, M.; Nowak, E.; Kanarsky, T.S.; Zhang, Y.; Roy, R.; Boyd, D.; Fired, D.; Wong, H.-S.P. Extension and source/drain design for high-performance FinFET devices. IEEE Trans. Electron. Devices 2003, 50, 952–958. [Google Scholar] [CrossRef]

- Zschatzsch, G.; Sasaki, Y.; Hayashi, S.; Togo, M.; Chiarella, T.; Kambham, A.K.; Mody, J.; Douhard, B.; Horiguchi, N.; Mizuno, B.; et al. High performance n-MOS finFET by damage-free, conformal extension doping. In Proceedings of the International Electron Device Meeting (IEDM), Wasington, DC, USA, 5–7 December 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Lue, H.-T.; Hsu, T.-H.; Wang, S.-Y.; Lai, E.-K.; Hsieh, K.-Y.; Liu, R.; Lu, C.-Y. Study of incremental step pulse programming (ISPP) and STI edge effect of BE-SONOS NAND Flash. In Proceedings of the IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 27 April–1 May 2008; pp. 693–694. [Google Scholar] [CrossRef]

- Kim, M.; Kim, S.; Shin, H. A Compact Model for ISPP of 3-D Charge-Trap NAND Flash Memories. IEEE Trans. Electron. Devices 2020, 67, 3095–3101. [Google Scholar] [CrossRef]

- Chen, W.-C.; Lue, H.-T.; Hsiao, Y.-H.; Hsu, T.-H.; Lin, X.-W.; Lu, C.-Y. Charge storage efficiency (CSE) effect in modeling the incremental step pulse programming (ISPP) in charge-trapping 3D NAND flash devices. In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Maconi, A.; Monzio Compagnoni, C.; Amoroso, S.M.; Mascellino, E.; Ghidotti, M.; Padovini, G.; Spinelli, A.S.; Lacaita, A.L.; Mauri, A.; Ghidini, G.; et al. Investigation of the ISPP dynamics and of the programming efficiency of charge-trap memories. In Proceedings of the European Solid State Device Research Conference, Sevilla, Spain, 14–16 September 2010; pp. 444–447. [Google Scholar] [CrossRef]

- Liu, S.; Zou, X. QLC NAND study and enhanced Gray coding methods for sixteen-level-based program algorithms. Microelectron. J. 2017, 66, 58–66. [Google Scholar] [CrossRef]

- Kim, S.; Baek, M.-H.; Hwang, S.; Jang, T.; Park, K.; Park, B.-G. A Novel Vector-matrix Multiplication (VMM) Architecture based on NAND Memory Array. J. Semicond. Tech. Sci. 2020, 20, 242–248. [Google Scholar] [CrossRef]

- Lee, S.-T.; Lim, S.; Choi, N.Y.; Bae, J.-H.; Kwon, D.; Park, B.-G.; Lee, J.-H. Operation Scheme of Multi-Layer Neural Networks Using NAND Flash Memory as High-Density Synaptic Devices. IEEE J. Electron. Devices Soc. 2019, 7, 1085–1093. [Google Scholar] [CrossRef]

- Lee, S.-T.; Kim, H.; Bae, J.-H.; Yoo, H.; Choi, N.Y.; Kwon, D.; Lim, S.; Park, B.-G.; Lee, J.-H. High-Density and Highly-Reliable Binary Neural Networks Using NAND Flash Memory Cells as Synaptic Devices. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Kim, M.; Song, J.; Kim, C.H. Reliability Characterization of Logic-Compatible NAND Flash Memory based Synapses with 3-bit per Cell Weights and 1μA Current Steps. In Proceedings of the International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28–30 April 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Wang, P.; Xu, F.; Wang, B.; Gao, B.; Wu, H.; Qian, H.; Yu, S. Three-Dimensional NAND Flash for Vector–Matrix Multiplication. IEEE Trans. Very Large Scale Intergr. Vlsi Syst. 2019, 27, 988–991. [Google Scholar] [CrossRef]

- Minucci, U.; Santis, L.D.; Vali, T.; Irrera, F. A Neural Network implemented on NAND memory. In Proceedings of the 2020 IEEE International Memory Workshop (IMW), Dresden, Germany, 17–20 May 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Lue, H.-T.; Lai, S.-C.; Hsu, T.-H.; Du, P.-Y.; Wang, S.-Y.; Hsieh, K.-Y.; Liu, R.; Lu, C.-Y. Understanding barrier engineered charge-trapping NAND flash devices with and without high-K dielectric. In Proceedings of the IEEE International Reliability Physics Symposium, Montreal, QC, Canada, 26–30 April 2009; pp. 874–882. [Google Scholar] [CrossRef]

- Kang, M.; Park, K.-T.; Song, Y.; Hwang, S.; Choi, B.Y.; Song, Y.; Lee, Y.-T.; Kim, C. Improving Read Disturb Characteristics by Self-Boosting Read Scheme for Multilevel NAND Flash Memories. Jpn. J. Appl. Phys. 2009, 48, 04C062. [Google Scholar] [CrossRef]

- Lue, H.-T.; Hsu, P.-K.; Wang, K.-C.; Lu, C.-Y. Introduction of Non-Volatile Computing in Memory (nvCIM) by 3D NAND Flash for Inference Accelerator of Deep Neural Network (DNN) and the Read Disturb Reliability Evaluation. In Proceedings of the IEEE International Reliability Physics Symposium, Dallas, TX, USA, 28–30 May 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Kobayashi, A.; Tokutomi, T.; Takeuchi, K. Versatile TLC NAND flash memory control to reduce read disturb errors by 85% and extend read cycles by 6.7-times of Read-Hot and Cold data for cloud data centers. In Proceedings of the 2016 Symposium on VLSI Technology (VLSIT), Honolulu, Hawaii, 15–17 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Zhang, Y.; Jin, L.; Jiang, D.; Zou, X.; Liu, H.; Huo, Z. A Novel Read Scheme for Read Disturbance Suppression in 3D NAND Flash Memory. IEEE Electron. Device Lett. 2017, 12, 1669–1672. [Google Scholar] [CrossRef]

- Della Marca, V.; Postel-Pellerin, J.; Just, G.; Canet, P.; Ogier, J.-L. Impact of endurance degradation on the programming efficiency and the energy consumption of NOR flash memories. Microelectron. Reliab. 2014, 54, 2262–2265. [Google Scholar] [CrossRef]

- Driussi, F.; Esseni, D.; Selmi, L. Performance, degradation monitors, and reliability of the CHISEL injection regime. IEEE Trans. Device Mater. Reliab. 2004, 4, 327–334. [Google Scholar] [CrossRef]

- Postel-Pellerin, J.; Chiquet, P.; Della Marca, V.; Wakrim, T.; Just, G.; Ogier, J.L. Improving Flash memory endurance and consumption with ultra-short channel-hot-electron programming pulses. In Proceedings of the International Semiconductor Conference (CAS), Sinaia, Romania, 13–15 October 2014; pp. 197–200. [Google Scholar] [CrossRef]

- Park, M.; Park, S.; Lee, D.-K.; Jeong, Y.; Hong, C.; Lee, H.S.; Cho, M.K.; Ahn, K.-O.; Koh, Y. NAND Flash reliability degradation induced by HCI in boosted channel potential. In Proceedings of the IEEE International Reliability Physics Symposium, Anaheim, CA, USA, 2–6 May 2010; p. MY.7.1-2. [Google Scholar]

| Program | Erase | |

|---|---|---|

| Selected WL | 13 V | −19 V |

| Unselected WL | 0 V | 0 V |

| Selected SL/DL | 0 V | 0 V |

| Unselected SL/DL | Floating or Vpgm/2 | Floating or Ver/2 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jang, T.; Kim, S.; Chang, J.; Min, K.K.; Hwang, S.; Park, K.; Lee, J.-H.; Park, B.-G. 3D AND-Type Stacked Array for Neuromorphic Systems. Micromachines 2020, 11, 829. https://doi.org/10.3390/mi11090829

Jang T, Kim S, Chang J, Min KK, Hwang S, Park K, Lee J-H, Park B-G. 3D AND-Type Stacked Array for Neuromorphic Systems. Micromachines. 2020; 11(9):829. https://doi.org/10.3390/mi11090829

Chicago/Turabian StyleJang, Taejin, Suhyeon Kim, Jeesoo Chang, Kyung Kyu Min, Sungmin Hwang, Kyungchul Park, Jong-Ho Lee, and Byung-Gook Park. 2020. "3D AND-Type Stacked Array for Neuromorphic Systems" Micromachines 11, no. 9: 829. https://doi.org/10.3390/mi11090829

APA StyleJang, T., Kim, S., Chang, J., Min, K. K., Hwang, S., Park, K., Lee, J.-H., & Park, B.-G. (2020). 3D AND-Type Stacked Array for Neuromorphic Systems. Micromachines, 11(9), 829. https://doi.org/10.3390/mi11090829