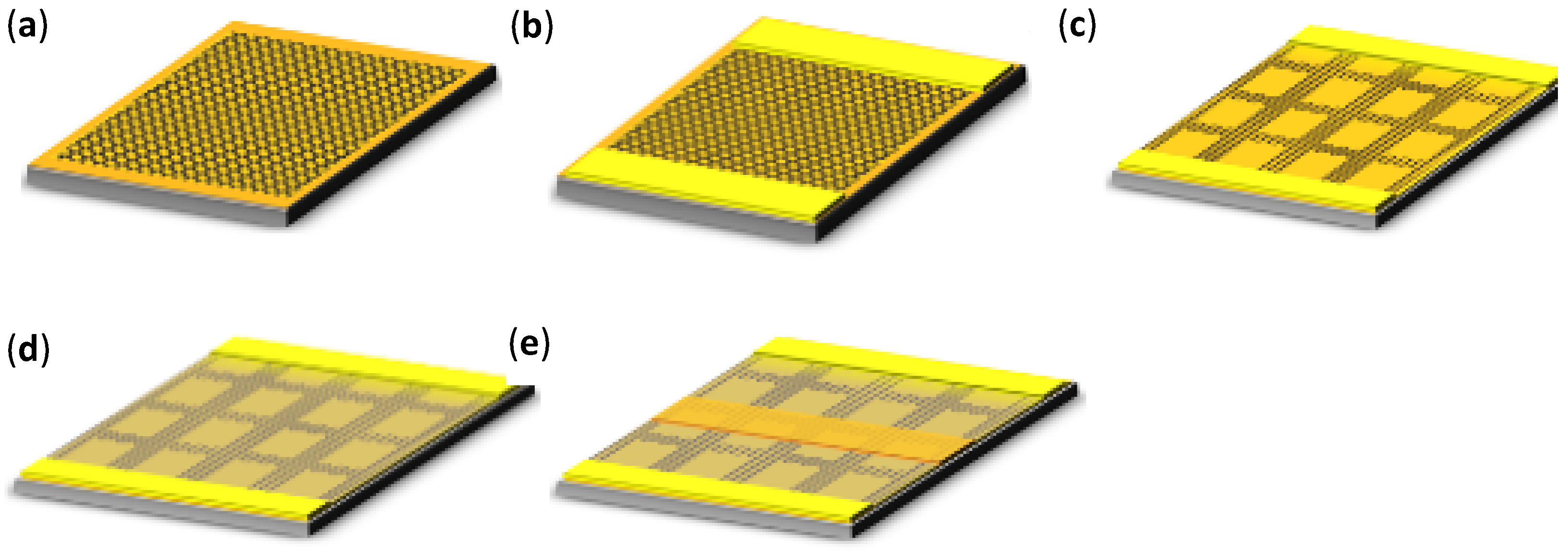

According to the device structure we designed, and the micro–nano processing platform of the National Center for Nanoscience and Technology of China, the overall fabrication process of the device is divided into the following five steps as shown in

Figure 1.

2.1. Chemical Vapor Deposition (CVD) and Transfer of Graphene

Graphene film is prepared on copper foil (2 cm × 2 cm × 25 μm in volume) by CVD [

4,

15,

16], and then transferred to the prepared Si/SiO

2 substrate. Firstly, the desired copper foil substrate was obtained with the method of chemical immersion cleaning combined with electrochemical polishing. Then, graphene crystals were grown in a single-temperature-zone CVD tube furnace. The temperature was raised in a low-pressure environment (the pressure was set at 600–800 mTorr), and H

2 was introduced when the temperature was raised. Under the condition of 1050 °C, the copper foil substrate was annealed for 1.5 h and maintained at this temperature, and H

2 (catalyst) and CH

4 (carbon source) were introduced for chemical reaction preparation. The reaction time was controlled within half an hour. After the graphene film was formed, the PMMA was coated as the protective layer. The thickness of the PMMA is about 200 nm when the spin speed is 4000 RPM and the concentration of the PMMA is 6%. Ferric chloride and hydrochloric acid were used as etching solutions to soak the copper foil substrate and some inorganic impurities. After copper foil etching, the PMMA/graphene was cleaned with deionized water. The selected substrate is a highly doped p-type silicon with a thickness of 525 μm. The thickness of the oxide layer above the silicon wafer is 285 nm. Before the transfer, the substrate was cleaned with deionized water and then dried with nitrogen. The PMMA/graphene was directly transferred to the substrate. At last, the PMMA was dissolved and removed in an acetone solution. In order to prevent graphene damage and avoid using ultrasound, the PMMA was removed by 80 °C water bath heating.

2.2. Fabrication of the Source and Drain Electrodes

Graphene film is essentially a single layer of carbon atoms. During the process design of the device, graphene damage should be avoided as far as possible. Therefore, the stripping process is chosen for electrode evaporation in order to avoid damage to the graphene caused by strong acid etching solutions in the electrode manufacturing process.

However, the metal pattern formed on graphene by the stripping process is easy to fall off. The main reason is that the bonding between graphene and substrate is very low due to the van der Waals force. When the metal film is evaporated on graphene, the metal does not directly make contact with the substrate, and graphene may also act as a “stripping adhesive” in the stripping process to strip the metal directly. The phenomenon of metal peeling is observed obviously, especially in the location of the large-area metal pad as shown in

Figure 2.

In order to solve this problem, a process of etching graphene is added on the basis of the conventional stripping process, and then the metal evaporation stripping process is carried out twice. The optimized process is shown in

Figure 3.

Before spin-coating, the graphene substrate is pretreated and soaked in acetone at room temperature for half an hour. After that, the graphene substrate is cleaned with isopropanol and deionized water, and dried with nitrogen successively. Next, the pre-baking temperature for the substrate is set to 120 °C and the heating time is 3 min. Then, a 4% concentration of PMMA (950 k) is selected as the positive glue to spin onto the substrate with a spin-coating speed of 5000 RPM. After spin-coating, the substrate is post-baked at 150 °C for 2 min, as shown in

Figure 3a.

Figure 3b shows that the positive photoresist stripping process is used to expose the pattern of the metal wire and pad, in which the graphene would be removed, excluding the part of the source and drain electrodes located in the central part framed in the red dotted line.

Figure 4 shows the layout pattern for electron-beam direct writing with an exposure dose of 850 μC/cm

2. In order to improve the exposure efficiency, the electron-beam step is set at 50 nm.

Figure 3c shows the result of the positive photoresist development. The developer was a mixture of MIBK: IPA = 1:3. After 100 s of developing time, the substrate was then soaked in isopropanol for 50 s. In order to avoid the stripping effect of graphene upon the metal, oxygen plasma was used to etch the graphene with an etching time of 8 s and an etching power of 150 W under a pressure of 5 Pa. The development result is shown in

Figure 3d. Then, the first evaporated metal of 8 nm/40 nm Ti/Au, shown in

Figure 3e, could make contact with the SiO

2/Si substrate to enhance the adhesion force. Meanwhile, the useless graphene easily fell off. Therefore, water bath heating and longer soaking time can be used to enhance the stripping effect without using ultrasound. The stripping result is shown in

Figure 3f.

The same PMMA positive photoresist was used for spin-coating again. The peeling effect of the subsequent process could be enhanced by appropriately increasing the thickness of the spin-coating, as shown in

Figure 3g. The source and drain electrodes are designed and shown in the enlarged picture in

Figure 5. This scheme causes the metal to directly make contact with the substrate to enhance the adhesion of the metal, and it can also reduce the contact resistance by making the source and drain electrodes directly make contact with graphene, as shown in

Figure 3h. The parameters of electron-beam exposure are the same as those of the first exposure.

The evaporated metal is Au with a thickness of 100 nm as shown in

Figure 3i, including the patterns of wire and pad, and source and drain electrodes. In order to ensure the continuity of the whole metal pattern, the evaporation thickness is required to exceed the first overall thickness.

Figure 3j shows the source and drain electrodes and metal pads obtained by the same stripping method presented above.

2.3. Fabrication of Graphene Nanomesh by EBL and OPE

In order to obtain the large-area and uniform graphene nanogrid, the micro–nano fabrication method of electron-beam lithography (EBL) and oxygen plasma etching (OPE) was used to obtain the corresponding size of graphene nanogrid structure materials. Firstly, a large-area single-layer graphene was grown by chemical vapor deposition on a copper substrate. It was then transferred onto heavily doped p-type Si substrates with a 285 nm SiO2 layer using polymethyl methacrylate (PMMA)-assisted wet-transfer techniques. The silicon wafer (substrate size 1.2 cm × 1.2 cm) with the transferred graphene film was soaked in an acetone solution for 12 h, then soaked in isopropanol, slightly washed with deionized water, and finally dried (<80 °C). Then, the PMMA with a concentration of 4% was used as a resist, and the spin-coating speed was set at 5000–6000 RPM (the corresponding coating thickness was about 200 nm). For different structures and sizes of GNM, the corresponding exposure dose was determined and selected for electron-beam exposure. At last, a graphene nanomesh structure was fabricated by oxygen plasma etching. The layout of the graphene channel between the source and drain electrodes is shown in

Figure 6a, which was processed by EBL [

17]. The exploration of the graphene nanomesh is shown in the right image of

Figure 6b. After the electron-beam direct writing exposure process is completed, the channel image of the device is obtained and shown on the left of

Figure 6b.

SEM images of the graphene nanomesh structure after oxygen plasma etching are shown in

Figure 7. It can be seen that the fabricated graphene nanogrid can maintain the integrity of the periodic structure in the large-area.

2.4. CVD Deposition of the Dielectric Layer

As the device will work in THz frequency bands, the dielectric constant of the gate dielectric layer under the gate electrode should be as large as possible. For graphene that has been processed into nanostructure, the bonding ability with the dielectric layer on the surface of graphene and the question of easy damage should be considered carefully in the subsequent processes.

Therefore, plasma-enhanced chemical vapor deposition (PECVD) was chosen to deposit Si

3N

4 on the surface of the graphene nanomesh as the dielectric layer. Because the combination of Si

3N

4 and graphene is much better than that of a silicon oxide dielectric layer created by the thermal oxidation process, the dielectric constant of Si

3N

4 (ε = 6.6) is much higher than that of silicon oxide (ε = 3.9), and Si

3N

4 has a higher polarized photo–phonon frequency, which can reduce the phonon scattering of the graphene conductive channel and is conducive to the photoelectric application of graphene [

18]. Simultaneously, the PECVD process worked at a low-temperature environment, which could effectively prevent the damage of graphene. The gas source of Si

3N

4 CVD was the inert gas of N

2 and NH

3. In addition, the power source was a low-density plasma with a power of only 40 W. These factors could ensure that the damage to graphene is minimized in the manufacturing process of the dielectric layer.

The growth process of the Si

3N

4 dielectric layer is shown in

Figure 8. The result of spin-coating positive photoresist is shown in

Figure 8a. The rotation speed was set at 4000–5000 RPM to spin-coat with the PMMA 950 k positive photoresist and control the photoresist thickness above 200 nm. The pre-baking and post-baking time are 1–2 and 2 min, respectively. The pre-baking and post-baking temperatures are 120 and 150 °C, respectively. As the pattern of the dielectric layer is simple and the requirement of dimensional accuracy is low, only accurate alignment is required for electron-beam direct writing. The exposure dose of electron beam was 850 μC/cm

2, and the step setting was 50 nm. The fabrication of EBL is shown in

Figure 8b. The mixture of MIBK and IPA (1:3) was used as developer. The positive photoresist development time was 100 s, and isopropanol was used for fixing for 30 s. After the development was obtained, as shown in

Figure 8c, the Si

3N

4 was grown by using the Si 500 D PECVD equipment (SENTECH). SiH

4/N

2 and NH

3 were used as the gas source, and the reaction equation is:

While the RF power, temperature, pressure and deposition time are set to 40 W, 55 °C, 50 Pa and 1 h, respectively, the thickness of the Si

3N

4 film would be about 60 nm, as shown in

Figure 8d. The last step of the dielectric layer deposition is stripping, which used an acetone solution to remove the PMMA, and the result is shown in

Figure 8e.

2.5. Fabrication of the Gate Electrode

After the fabrication of the dielectric layer Si

3N

4, the graphene nanomesh was covered by silicon nitride, and the possibility of damage was reduced, as shown in

Figure 9. Therefore, the conventional metal evaporation stripping process can be used for the fabrication of different gate electrodes. The specific process flow is shown in

Figure 10.

Figure 10a shows the spin-coating result, among which PMMA (950 k) stock solution was used for spin-coating, the spin-coating speed was 4500 RPM, and the thickness of the adhesive was controlled above 200 nm. The pre-baking and post-baking time both were 100 s, and the temperatures were set to 80 and 150 °C, respectively. While the electron-beam exposure dose was set at 900 μC/cm

2 and the step was set at 50 nm, the overlay precision could be ensured for the electron-beam direct writing exposure of the gate electrode pattern. The EBL result is shown in

Figure 10b. The positive development still used the mixture of MIBK and IPA (1:3) as developer in

Figure 10c. The development time was 100 s and then isopropanol was used for fixing. The thickness of the evaporated gate metal should be as thin as possible, as shown in

Figure 10d. Therefore, we evaporated 10/50 nm thick Ti/Au metal, which is conducive to complete stripping. The PMMA adhesive was removed by immersing the substrate in an acetone solution to complete the stripping process, as shown in

Figure 10e. A water bath with long-time soaking was used to ensure complete stripping, because due to the narrow metal spacing it was easy to cause incomplete stripping.

Using the above process, we fabricated an r-GNM FET THz device with a graphene nanomesh size of 14 nm × 60 nm, which is shown in

Figure 11.