Sensing Circuit Design Techniques for RRAM in Advanced CMOS Technology Nodes

Abstract

:1. Introduction

2. The Design Challenges of RRAM

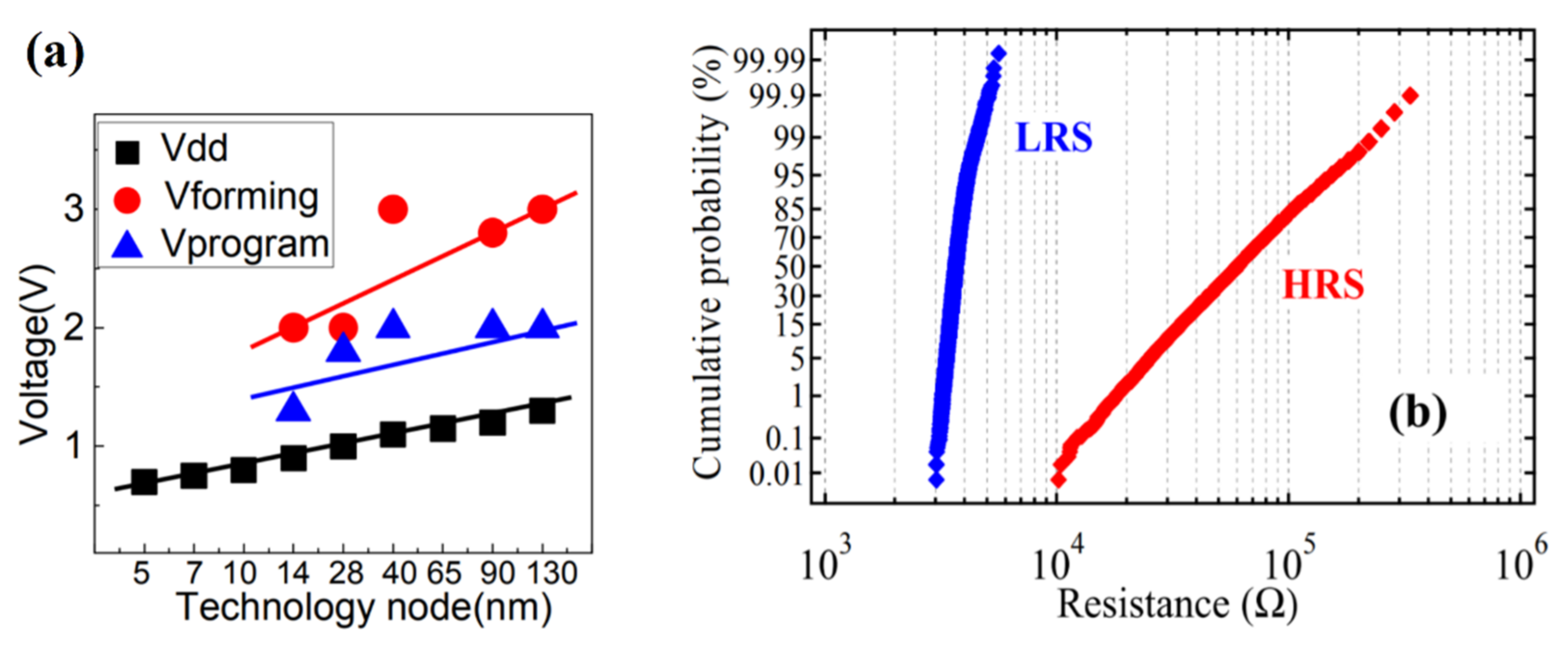

2.1. The Working Voltage Decreases as Technology Shrink

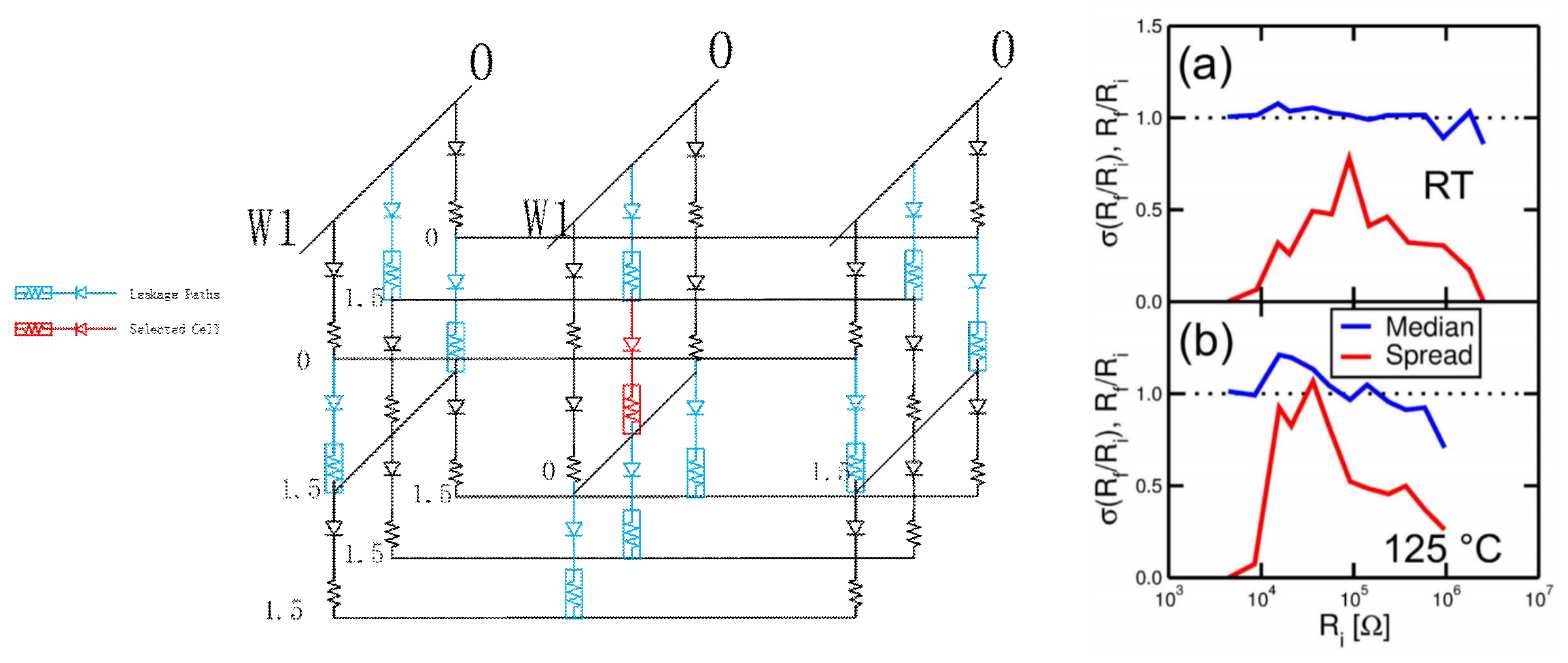

2.2. Sneak Current Issues

2.3. IR Drop Issues

2.4. Resistance Variability Issues

2.5. Temperature Dependence of RRAM Cell

2.6. Read Disturb

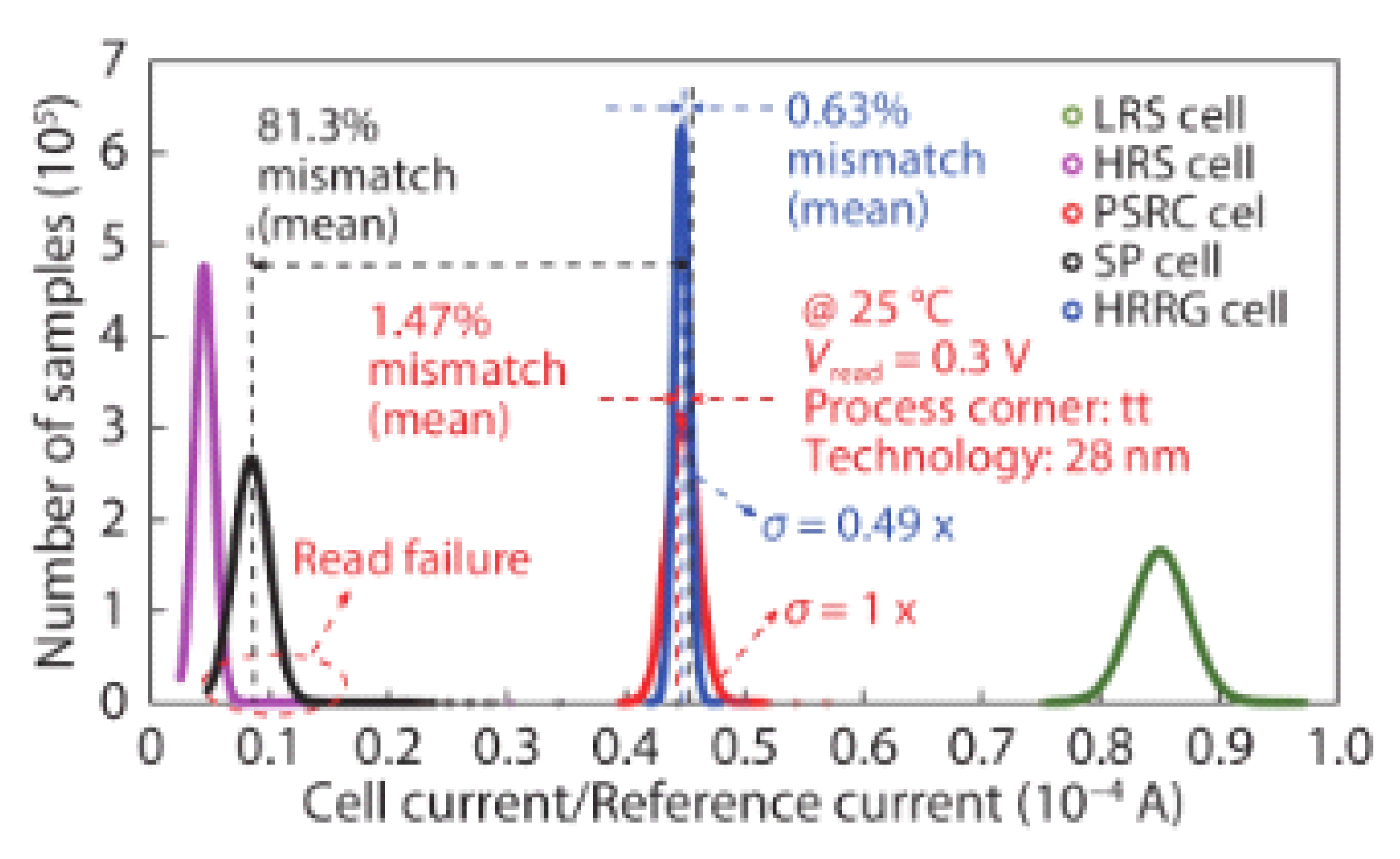

2.7. Sensing Margin Degradation

2.8. The Offset Current Increases in the Sense Circuit

3. Sensing Circuit Design Techniques for RRAM

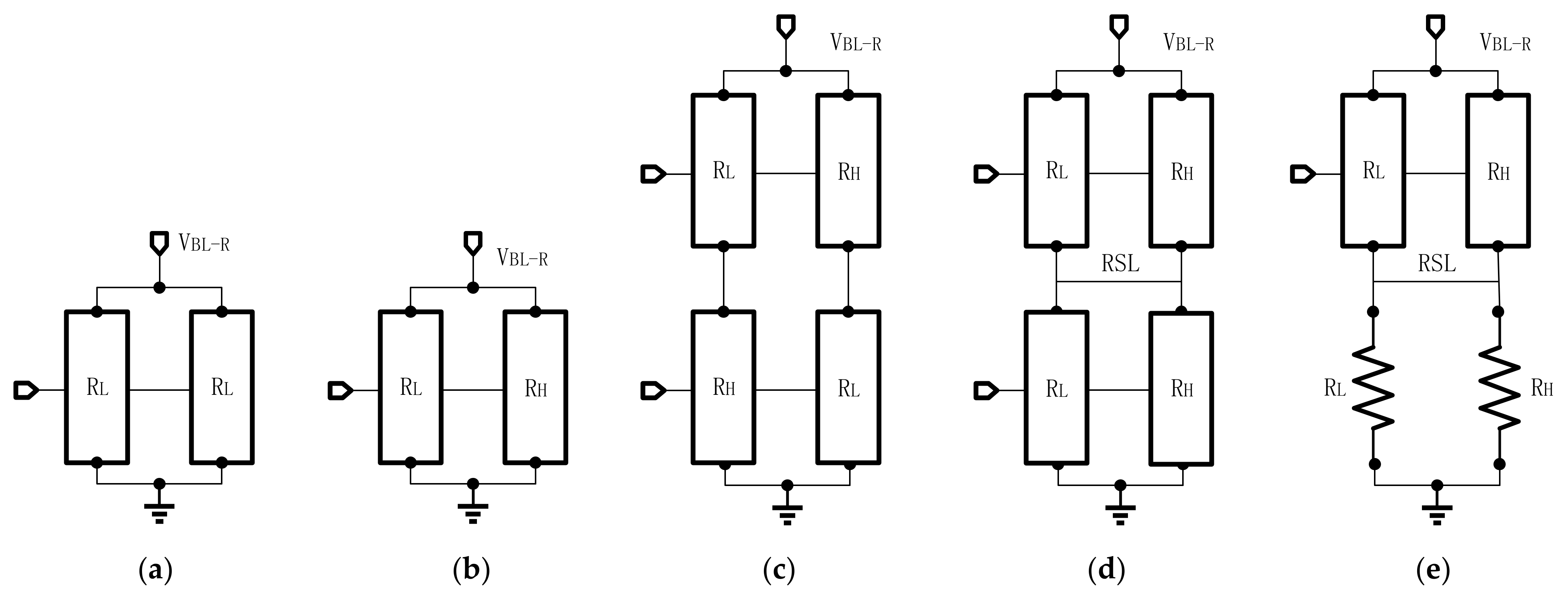

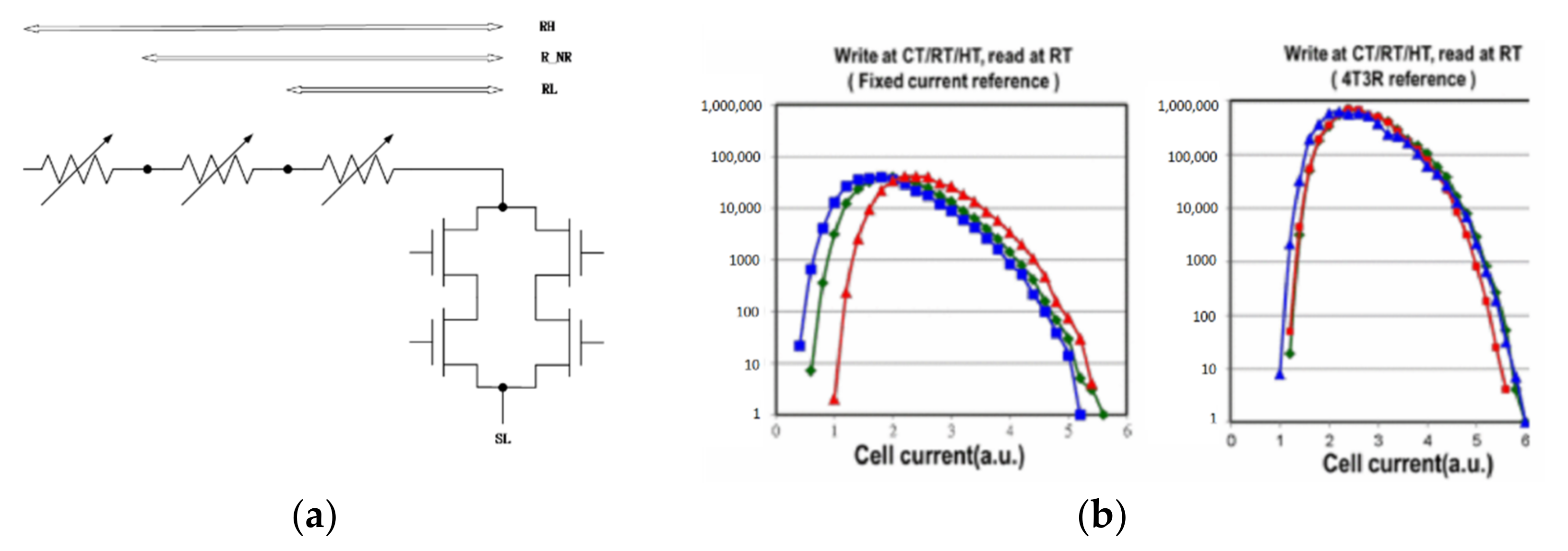

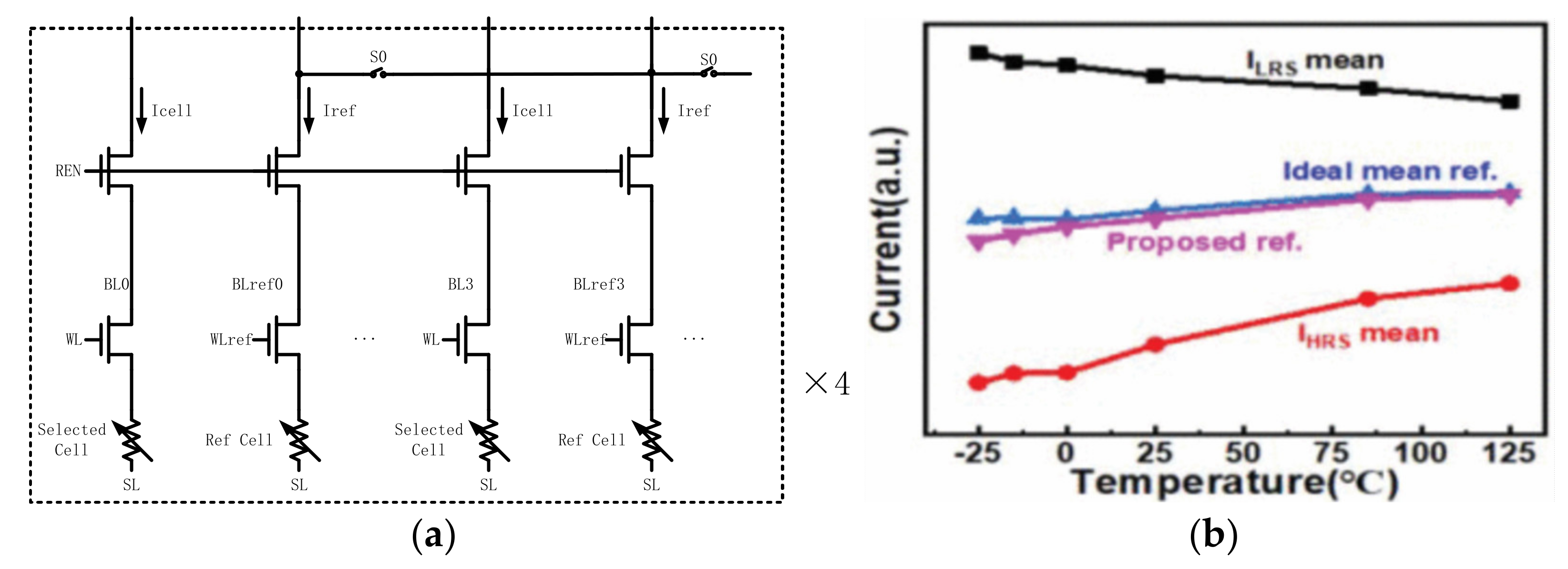

3.1. Reference Schemes

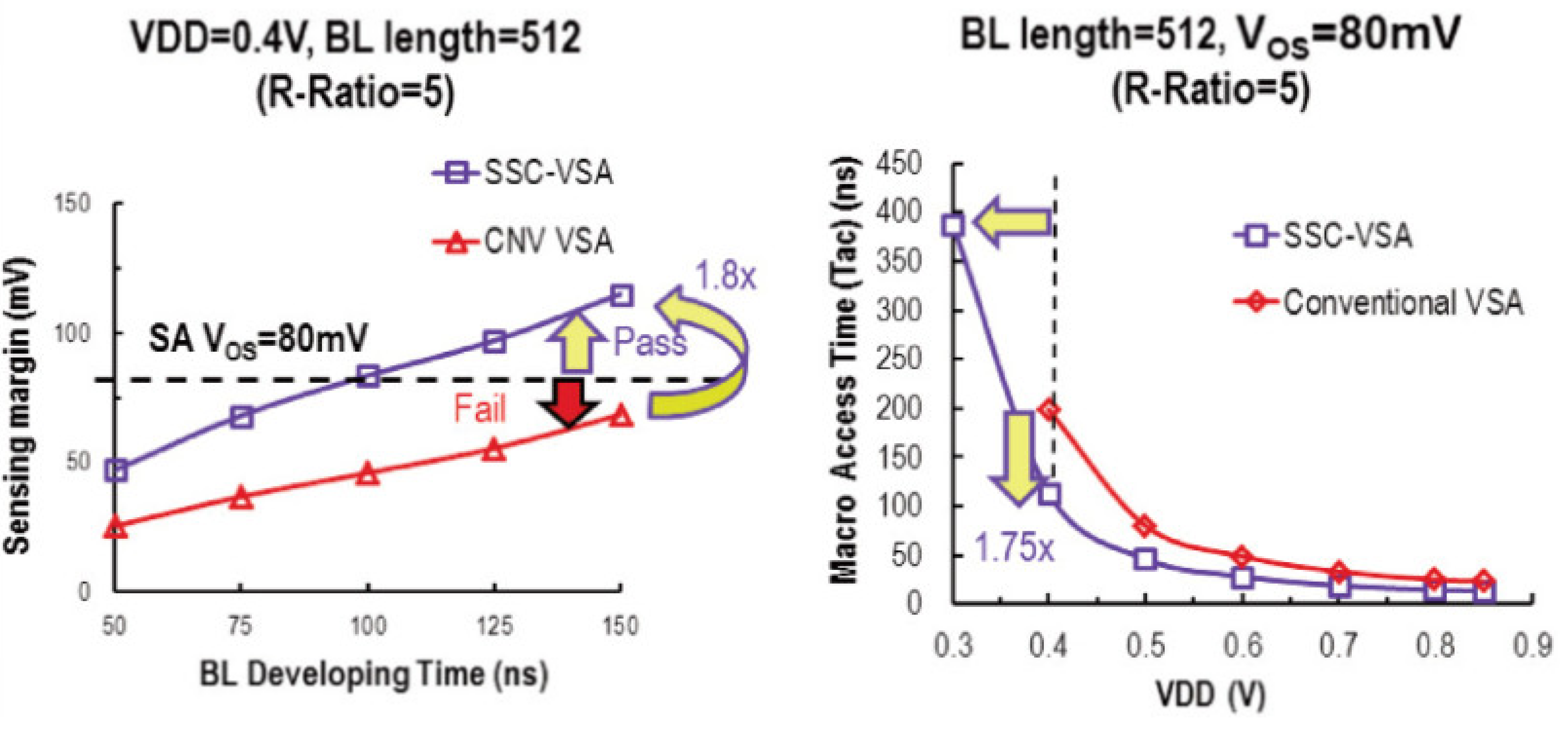

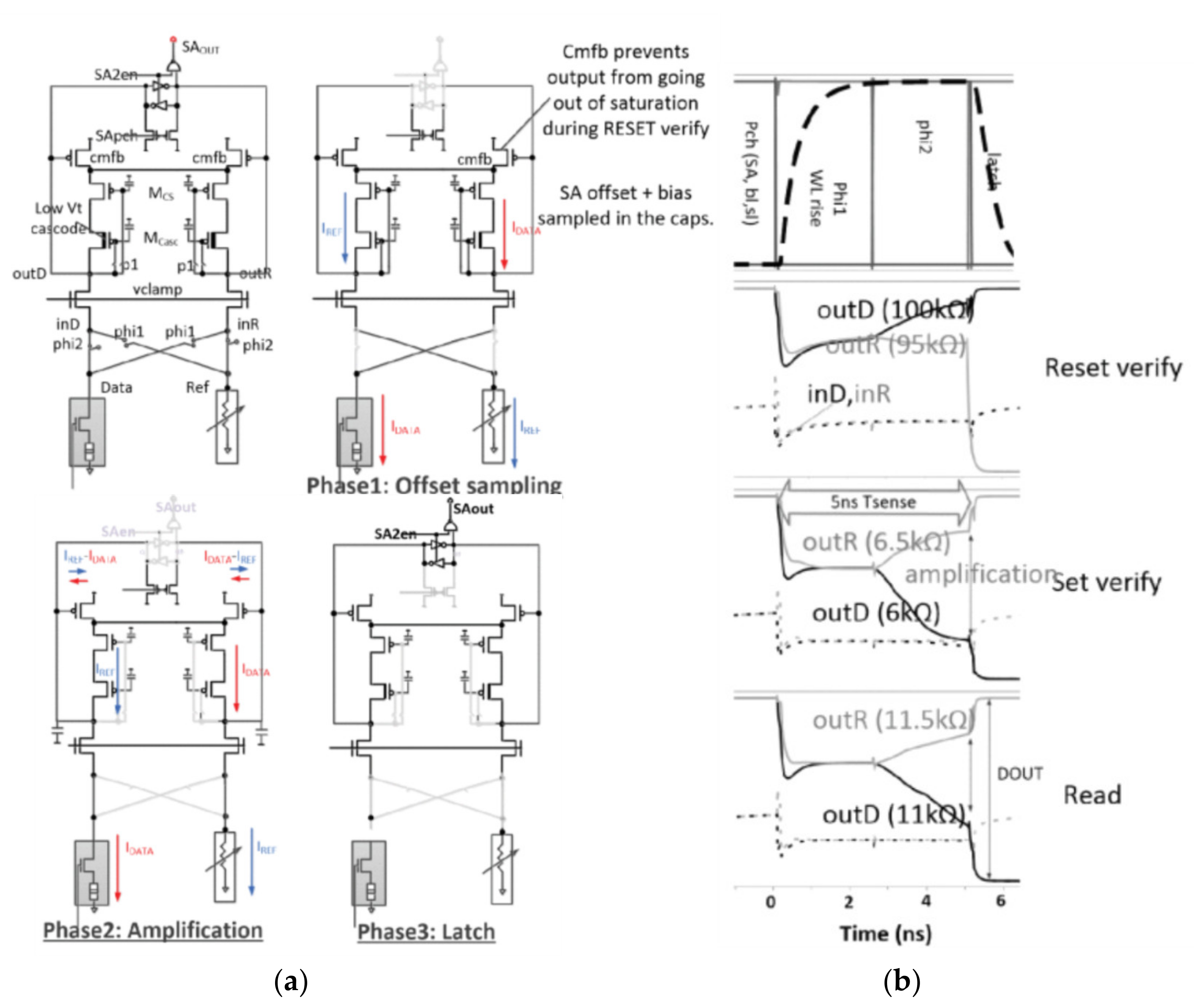

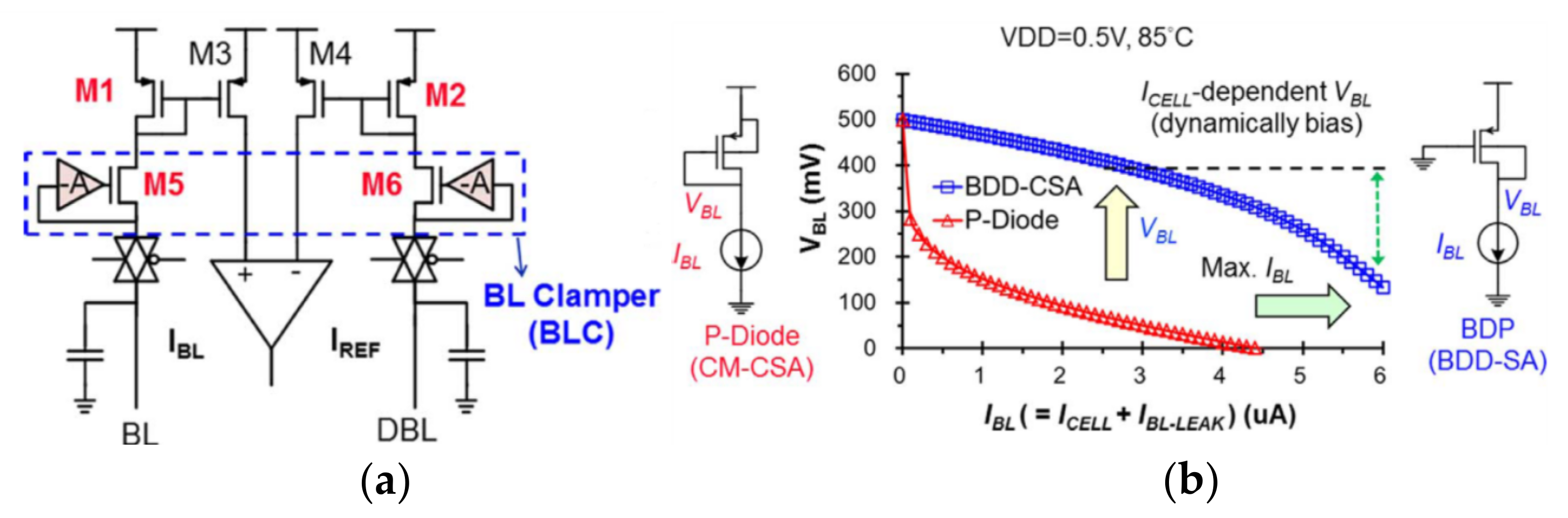

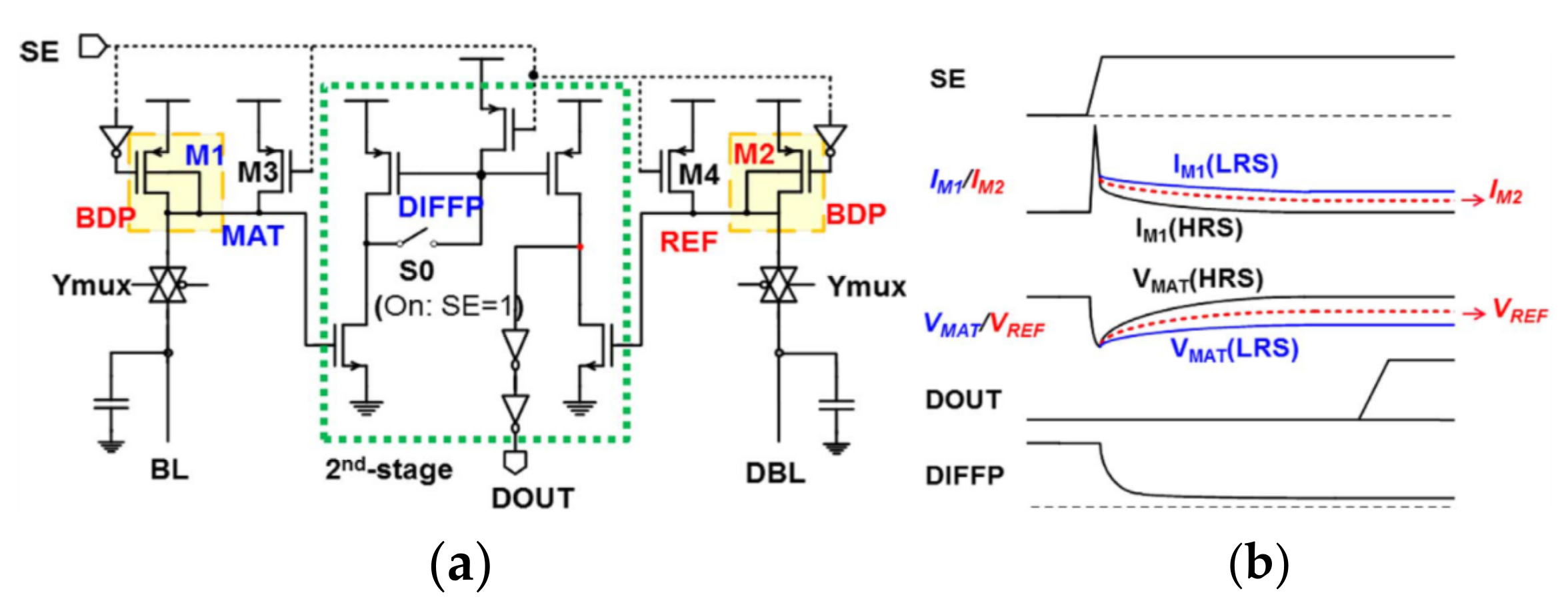

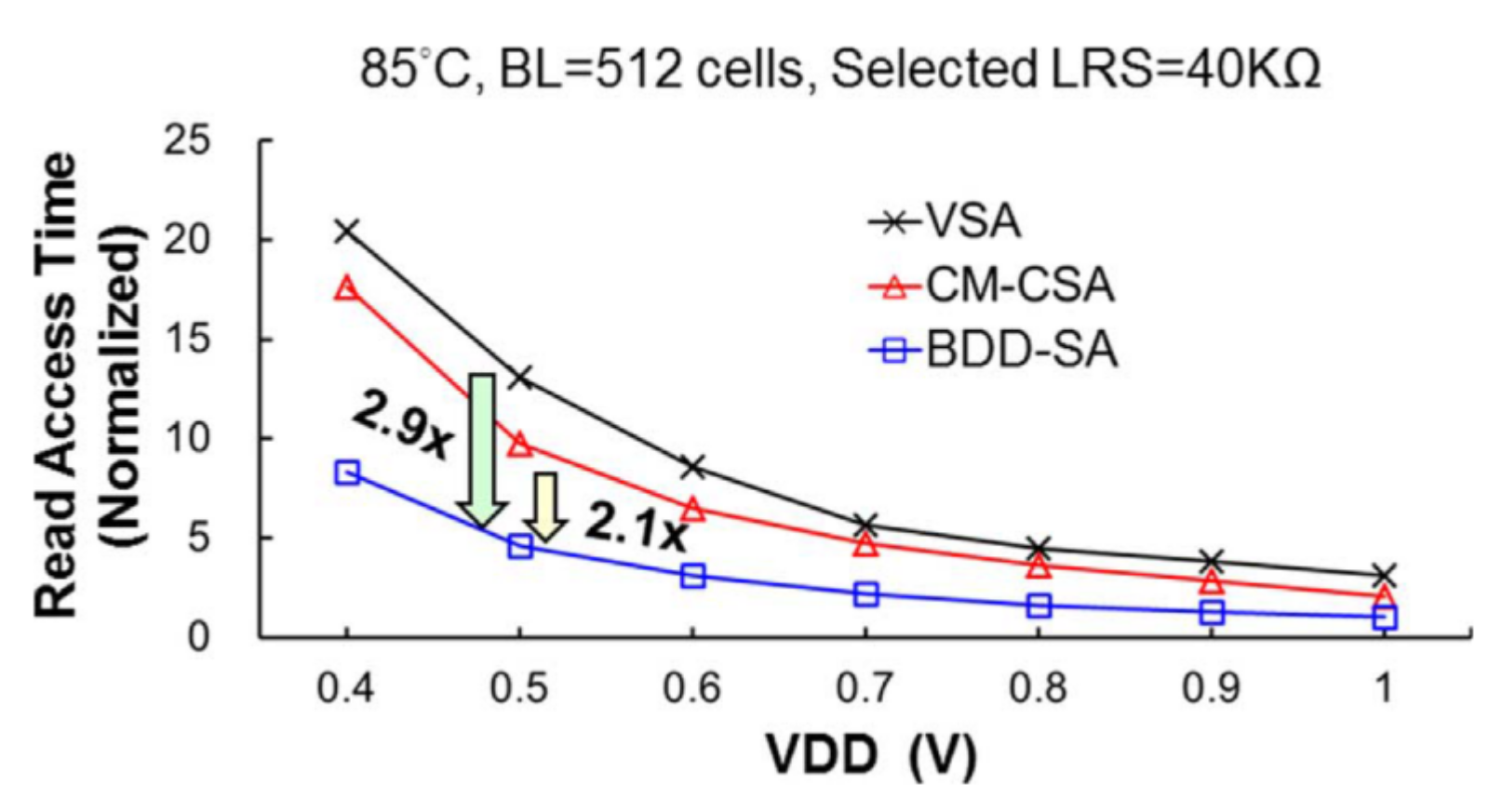

3.2. Sensing Amplifier Schemes

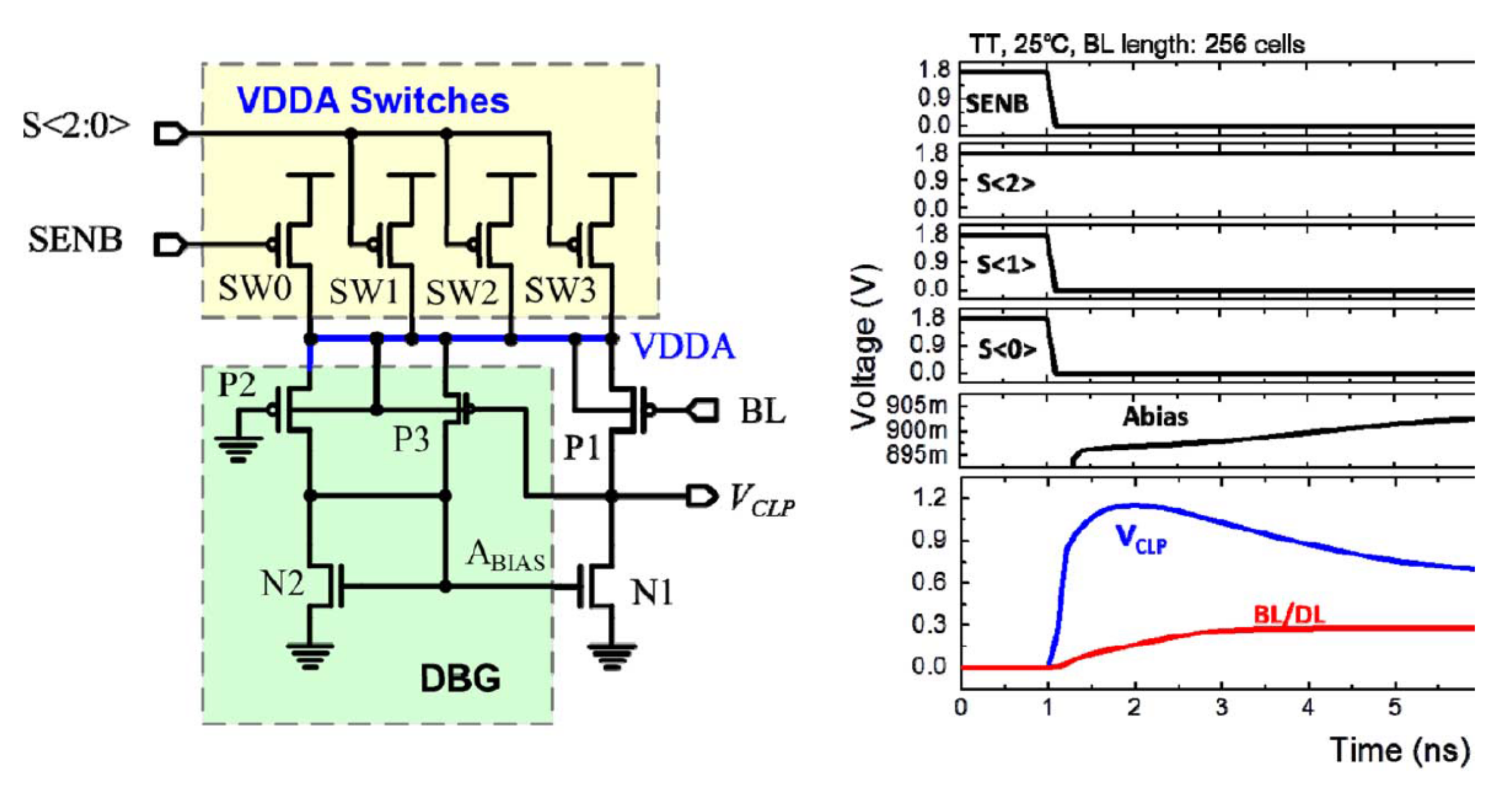

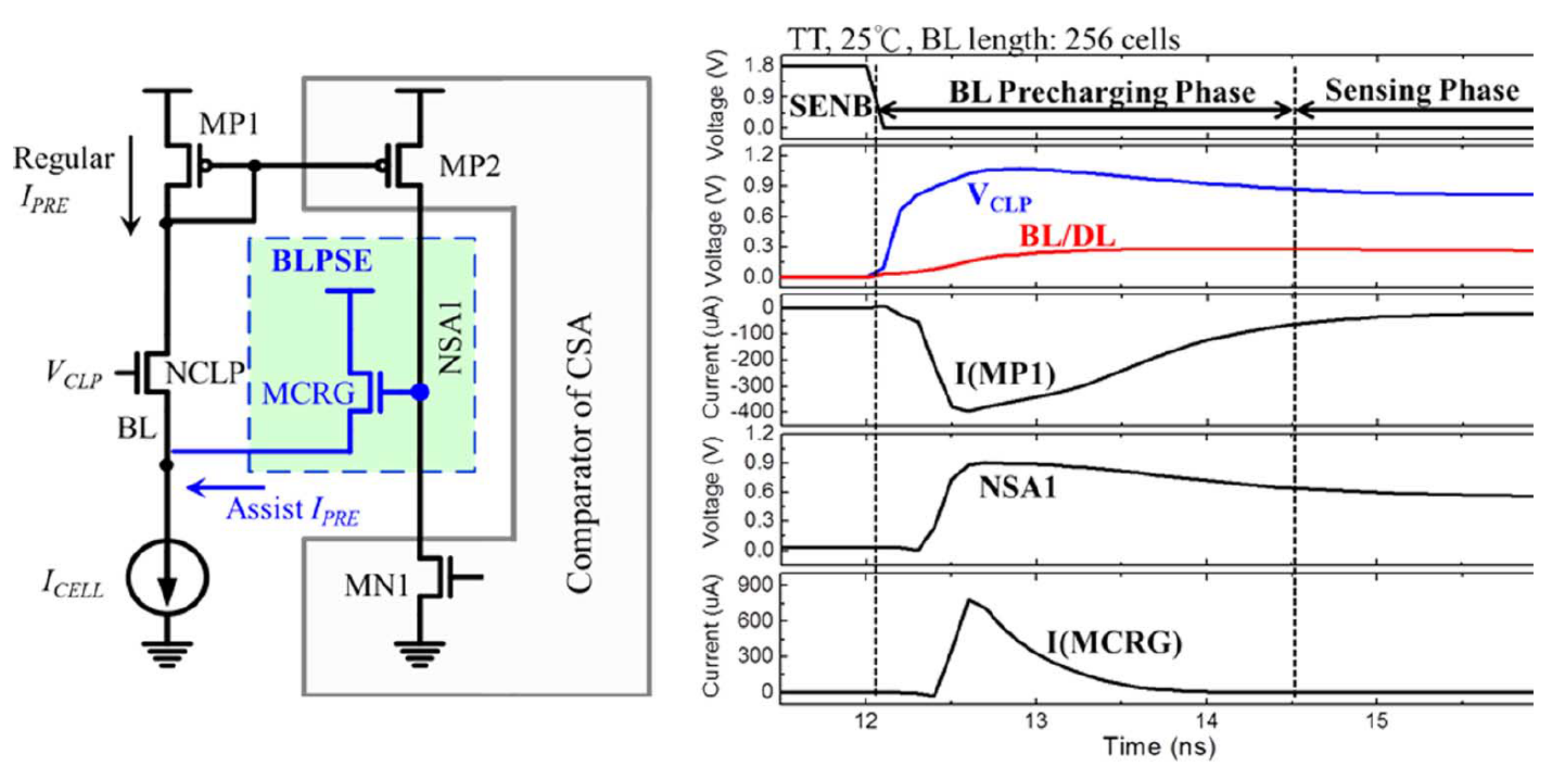

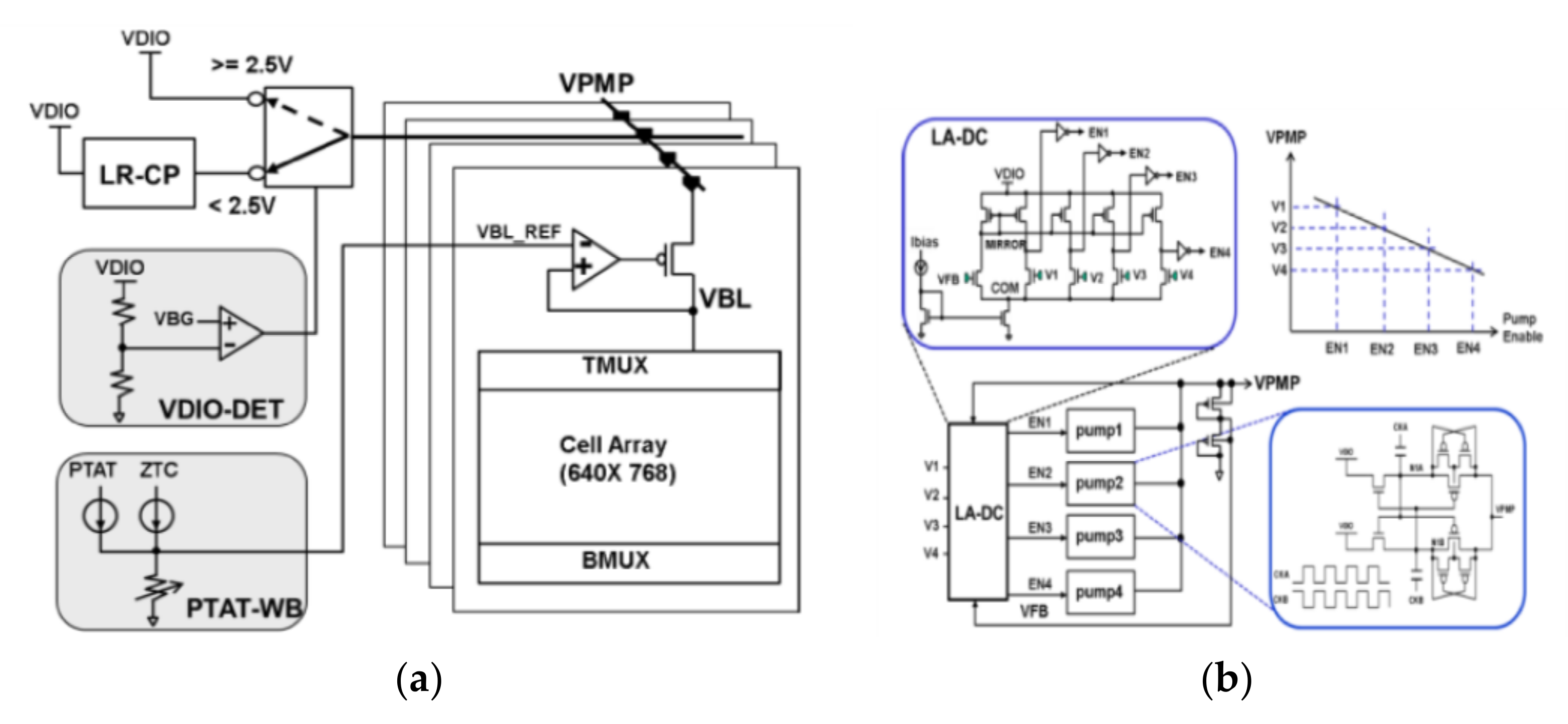

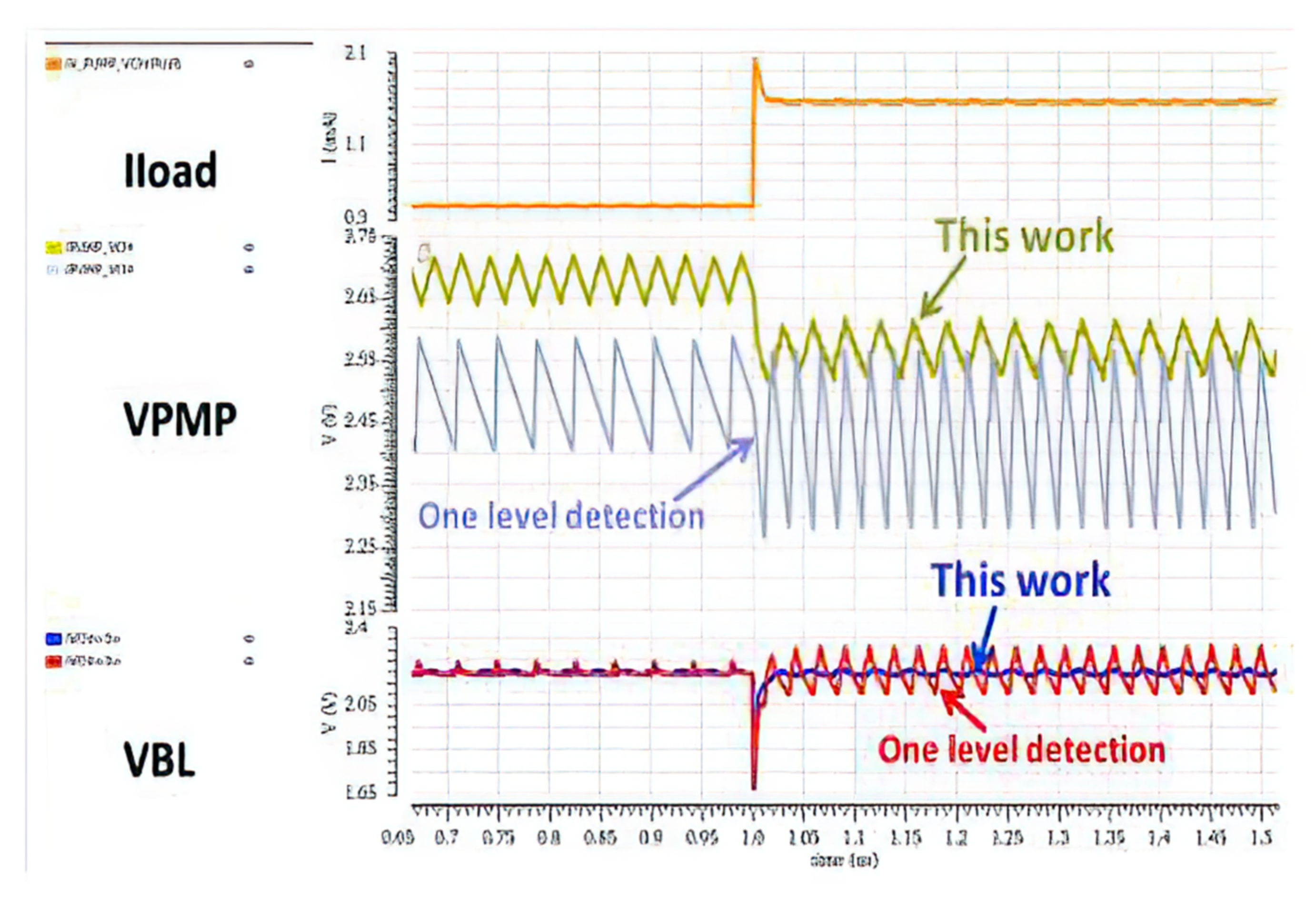

3.3. BL-Enhancing Schemes

3.4. The Summary of Sensing Schemes

4. Summary and Outlook

- (1)

- Reference schemes should track the RRAM cell in not only temperature but also time variation, and deal with the tail-bits issue occurring in reference schemes.

- (2)

- Sensing amplifier schemes should achieve high resolution, strong robustness, high speed, and work at ultra-low voltage.

- (3)

- BL-enhancing schemes should stabilize the BL voltage, ensure enough efficient BL voltage, and work at ultra-low voltage.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Jefremow, M.; Kern, T.; Backhausen, U.; Peters, C.; Parzinger, C.; Roll, C.; Kassenetter, S.; Thierold, S.; Schmitt-Landsiedel, D. Bitline-capacitance-cancelation sensing scheme with 11 ns read latency and maximum read throughput of 2.9 GB/s in 65 nm embedded flash for automotive. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 428–430. [Google Scholar]

- Chang, M.-F.; Shen, S.-J. A process variation tolerant embedded split-gate flash memory using pre-stable current sensing scheme. IEEE J. Solid State Circuits 2009, 44, 987–994. [Google Scholar] [CrossRef]

- Kanda, A.; Kurafuji, T.; Takeda, K.; Ogawa, T.; Taito, Y.; Yoshihara, K.; Nakano, M.; Ito, T.; Kondo, H.; Kono, T. A 24-MB Embedded Flash System Based on 28-nm SG-MONOS Featuring 240-MHz Read Operations and Robust Over-the-Air Software Update for Automotive Applications. IEEE Solid State Circuits Lett. 2019, 2, 273–276. [Google Scholar] [CrossRef]

- Chang, M.; Lin, Y.-F.; Liu, Y.-C.; Wu, J.-J.; Shen, S.-J.; Tsai, W.-C.; Chih, Y.-D. An Asymmetric-Voltage-Biased Current-Mode Sensing Scheme for Fast-Read Embedded Flash Macros. IEEE J. Solid State Circuits 2015, 50, 2188–2198. [Google Scholar] [CrossRef]

- Halupka, D.; Huda, S.; Song, W.; Sheikholeslami, A.; Tsunoda, K.; Yoshida, C.; Aoki, M. Negative-resistance read and write schemes for STT-MRAM in 0.13 µm CMOS. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 256–257. [Google Scholar]

- Jefremow, M.; Kern, T.; Allers, W.; Peters, C.; Otterstedt, J.; Bahlous, O.; Hofmann, K.; Allinger, R.; Kassenetter, S.; Schmitt-Landsiedel, D. Time-differential sense amplifier for sub-80 mV bitline voltage embedded STT-MRAM in 40 nm CMOS. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 216–217. [Google Scholar]

- Noguchi, H.; Ikegami, K.; Takaya, S.; Arima, E.; Kushida, K.; Kawasumi, A.; Hara, H.; Abe, K.; Shimomura, N.; Ito, J.; et al. 7.2 4 Mb STT-MRAM-based cache with memory-access-aware power optimization and write-verify-write/read-modify-write scheme. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 132–133. [Google Scholar]

- Yang, Z.-H.; Li, K.-X.; Chiang, Y.-N.; Lin, W.-Y.; Lin, H.-T.; Chang, M.-F. A 28 nm 32 Kb embedded 2T2MTJ STT-MRAM macro with 1.3 ns read-access time for fast and reliable read applications. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 480–481. [Google Scholar]

- Kim, C.; Kwon, K.; Park, C.; Jang, S.; Choi, J. 7.4 A covalent-bonded cross-coupled current-mode sense amplifier for STT-MRAM with 1T1MTJ common source-line structure array. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Ogiwara, R.; Takashima, D.; Doumae, S.; Shiratake, S.; Takizawa, R.; Shiga, H. Highly Reliable Reference Bitline Bias Designs for 64 Mb and 128 Mb Chain FeRAMs. IEEE J. Solid State Circuits 2015, 50, 1324–1331. [Google Scholar] [CrossRef]

- Khwa, W.-S.; Chang, M.-F.; Wu, J.-Y.; Lee, M.-H.; Su, T.-H.; Yang, K.-H.; Chen, T.-F.; Wang, T.-Y.; Li, H.-P.; Brightsky, M.; et al. A resistance-drift compensation scheme to reduce MLC PCM raw BER by over 100× for storage-class memory applications. IEEE Int. Solid State Circuits 2016, 52, 218–228. [Google Scholar] [CrossRef]

- De Sandre, G.; Bettinl, L.; Pirola, A.; Marmonier, L.; Pasotti, M.; Borghi, M.; Mattavelli, P.; Zuliani, P.; Scotti, L.; Mastracchio, G.; et al. A 90 nm 4 Mb embedded phase-change memory with 1.2 V 12 ns read access time and 1 MB/s write throughput. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 268–269. [Google Scholar]

- Chang, M.-F. A 0.5 V 4 Mb logic-process compatible embedded resistive RAM (ReRAM) in 65 nm CMOS using low-voltage current-mode sensing scheme with 45 ns random read time. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 19–23 February 2012; pp. 434–435. [Google Scholar]

- Kawahara, A. An 8 Mb multi-layered cross-point ReRAM macro with 443 MB/s write throughput. IEEE J. Solid State Circuits 2012, 48, 178–185. [Google Scholar] [CrossRef]

- Sheu, S.-S. A 4 Mb embedded SLC resistive-RAM macro with 7.2 ns read-write random-access time and 160 ns MLC-access capability. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 200–201. [Google Scholar]

- Govoreanu, B.; Kar, G.S. 10 × 10 nm2 Hf/HfOx crossbar resistive RAM with excellent performance, reliability and low-energy operation. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 31.6.1–31.6.4. [Google Scholar]

- Redolfi, A.; Goux, L. A novel CBRAM integration using subtractive dry-etching process of Cu enabling high-performance memory scaling down to 10 nm node. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T134–T135. [Google Scholar]

- Ho, C.H.; Hsu, C.-L.; Chen, C.-C.; Liu, J.-T.; Wu, C.-S.; Huang, C.-C.; Hu, C.; Yang, F.-L. 9 nm half-pitch functional resistive memory cell with <1 µA programming current using thermally oxidized sub-stoichiometric WOx film. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 19.1.1–19.1.4. [Google Scholar]

- Banno, N.; Tada, T. A fast and low-voltage Cu complementary-atom-switch 1 Mb array with high-temperature retention. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Govoreanu, B.; Di Piazza, L. Advanced a-VMCO resistive switching memory through inner interface engineering with wide (>102) on/off window, tunable μA-range switching current and excellent variability. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Tsunoda, K.; Kinoshita, K.; Noshiro, H.; Yamazaki, Y.; Iizuka, T.; Ito, Y.; Takahashi, A.; Okano, A.; Sato, Y.; Fukano, T.; et al. Low Power and High Speed Switching of Ti-doped NiO ReRAM under the Unipolar Voltage Source of less than 3 V. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 767–770. [Google Scholar]

- Goux, L.; Fantini, A. Ultralow sub-500 nA operating current high-performance TiN\Al2O3\HfO2\Hf\TiN bipolar RRAM achieved through understanding-based stack-engineering. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 159–160. [Google Scholar]

- Govoreanu, B.; Redolfi, A. Vacancy-modulated conductive oxide resistive RAM (VMCO-RRAM): An area-scalable switching current, self-compliant, highly nonlinear and wide on/off-window resistive switching cell. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 10.2.1–10.2.4. [Google Scholar]

- Cheng, C.-H.; Tsai, C.-Y.; Chin, A.; Yeh, F.S. High performance ultra-low energy RRAM with good retention and endurance. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 19.4.1–19.4.4. [Google Scholar]

- Kim, W. Forming-free nitrogen-doped AlOX RRAM with sub-μA programming current. In Proceedings of the 2011 Symposium on VLSI Technology—Digest of Technical Papers, Kyoto, Japan, 14–16 June 2011; pp. 22–23. [Google Scholar]

- Xu, X.; Luo, Q.; Gong, T.; Lv, H.; Long, S.; Liu, Q.; Chung, S.S.; Li, J.; Liu, M. Fully CMOS compatible 3D vertical RRAM with self-aligned self-selective cell enabling sub-5 nm scaling. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Suri, M.; Bichler, O. CBRAM devices as binary synapses for low-power stochastic neuromorphic systems: Auditory (Cochlea) and visual (Retina) cognitive processing applications. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 10.3.1–10.3.4. [Google Scholar]

- Lee, F.M.; Lin, Y.Y. A novel cross point one-resistor (0T1R) conductive bridge random access memory (CBRAM) with ultra low set/reset operation current. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 67–68. [Google Scholar]

- Vianello, E.; Thomas, O. Resistive Memories for Ultra-Low-Power embedded computing design. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 6.3.1–6.3.4. [Google Scholar]

- Luo, Q.; Xu, X. Demonstration of 3D vertical RRAM with ultra-low-leakage, high-selectivity and self-compliance memory cells. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 10.2.1–10.2.4. [Google Scholar]

- Ho, C.-H.; Shen, T.Y. Random soft error suppression by stoichiometric engineering: CMOS compatible and reliable 1 Mb HfO2-ReRAM with 2 extra masks for embedded IoT systems. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Symanczyk, R.; Dittrich, R. Conductive Bridging Memory Development from Single Cells to 2 Mbit Memory Arrays. In Proceedings of the 2007 Non-Volatile Memory Technology Symposium, Albuquerque, NM, USA, 10–13 November 2007; pp. 71–75. [Google Scholar]

- Goux, L.; Belmonte, A. Retention disturb and variability improvements enabled by local chemical-potential tuning and controlled Hour-Glass filament shape in a novel W\WO3\Al2O3\Cu CBRAM. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Chua, L. Memristor-The missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef]

- Fackenthal, R.; Kitagawa, M. 19.7 A 16 Gb ReRAM with 200 MB/s write and 1 GB/s read in 27 nm technology. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 338–339. [Google Scholar]

- Sills, S.; Yasuda, S. A copper ReRAM cell for Storage Class Memory applications. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Zahurak, J.; Miyata, K. Process integration of a 27 nm, 16 Gb Cu ReRAM. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 6.2.1–6.2.4. [Google Scholar]

- Liu, T.Y.; Yan, T.H. A 130.7-mm2 2-Layer 32-Gb ReRAM Memory Device in 24-nm Technology. IEEE J. Solid State Circuits 2014, 49, 140–153. [Google Scholar] [CrossRef]

- Wu, H. Resistive Random Access Memory for Future Information Processing System. Proc. IEEE 2017, 105, 1770–1789. [Google Scholar] [CrossRef]

- Waser, R.; Dittmann, R. Redox-based resistive switching memories—Nanoionic mechanisms prospects and challenges. Adv. Mater. 2009, 21, 2632–2663. [Google Scholar] [CrossRef]

- Kim, K.M.; Jeong, D.S.; Hwang, C.S. Nanofilamentary resistive switching in binary oxide system: A review on the present status and outlook. Nanotechnology 2011, 22, 254002. [Google Scholar] [CrossRef] [PubMed]

- Valov, I.; Waser, R.; Jameson, J.R.; Kozicki, M.N. Electrochemical metallization memories—Fundamentals applications prospects. Nanotechnology 2011, 22, 254003. [Google Scholar] [CrossRef] [PubMed]

- Jeong, D.S. Emerging memories: Resistive switching mechanisms and current status. Rep. Prog. Phys. 2012, 9, 076502. [Google Scholar] [CrossRef]

- Xu, X. First Demonstration of OxRRAM Integration on 14 nm FinFet Platform and Scaling Potential Analysis towards Sub-10 nm Node. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 24.3.1–24.3.4. [Google Scholar]

- Govoreanu, B. Performance and reliability of Ultra-Thin HfO2-based RRAM (UTO-RRAM). In Proceedings of the IEEE International Memory Workshop, Monterey, CA, USA, 26–29 May 2013; pp. 48–51. [Google Scholar]

- Zhuo, V.Y. Improved Switching Uniformity and Low-Voltage Operation in TaOx-Based RRAM Using Ge Reactive Layer. IEEE Electron. Device Lett. 2013, 34, 1130–1132. [Google Scholar] [CrossRef]

- Wei, Z. Highly reliable TaOx ReRAM and direct evidence of redox reaction mechanism. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Chang, M. Challenges at circuit designs for resistive-type Nonvolatile memory and nonvolatile logics in mobile and cloud applications. In Proceedings of the 2014 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Guilin, China, 28–31 October 2014; pp. 1–4. [Google Scholar]

- Shang, Y.; Ohsawa, T. Accurate Measurement of Sneak Current in ReRAM Crossbar Array with Data Storage Pattern Dependencies. In Proceedings of the International Symposium on VLSI Technology Systems and Application (VLSI-TSA), Hsinchu, Taiwan, 22–25 April 2019; pp. 1–2. [Google Scholar]

- Bae, W.; Yoon, K.J.; Hwang, C.S.; Jeong, D.-K. A crossbar resistance switching memory readout scheme with sneak current cancellation based on a two-port current-mode sensing. Nanotechnology 2016, 27, 485201. [Google Scholar] [CrossRef]

- Zidan, M.A.; Eltawil, A.M.; Kurdahi, F.; Fahmy, H.A.H.; Salama, K.N. Memristor multiport readout: A closed-form solution for sneak paths. IEEE Trans. Nanotechnol. 2014, 13, 274–283. [Google Scholar] [CrossRef] [Green Version]

- Ambrogio, S. Data retention statistics and modelling in HfO2 resistive switching memories. In Proceedings of the 2015 IEEE International Reliability Physics Symposium, Monterey, CA, USA, 19–23 April 2015; pp. MY.7.1–MY.7.6. [Google Scholar]

- Liang, J.; Wong, H.P. Cross-point memory array without cell selectors—Device characteristics and data storage pattern dependencies. IEEE Trans. Electron. Devices 2010, 57, 2531–2538. [Google Scholar] [CrossRef]

- Lin, Y.; Yuan, R. 3D vertical RRAM architecture and operation algorithms with effective IR-drop suppressing and anti-disturbance. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 377–380. [Google Scholar]

- Huang, C.; Xu, N. Efficient and optimized methods for alleviating the impacts of IR-drop and fault in RRAM based neural computing systems. J. Electron. Devices Soc. 2021, 9, 645–652. [Google Scholar] [CrossRef]

- Singh, B.; Davis, L. An analysis of scale invariance in object detection–snip. Proceedings of 2018 IEEE/CVF Conference on Computer Vision and Pattern Recognition, Salt Lake City, UT, USA, 18–23 June 2018; pp. 3578–3587. [Google Scholar]

- Zhu, Y.; Zhao, X. Insights and Optimizations on IR-drop Induced Sneak-Path for RRAM Crossbar-based Convolutions. In Proceedings of the 2020 25th Asia and South Pacific Design Automation Conference (ASP-DAC), Beijing, China, 13–16 January 2020; pp. 506–511. [Google Scholar]

- Xu, C.; Niu, D.; Muralimanohar, N.; Balasubramonian, R.; Zhang, T. Overcoming the challenges of crossbar resistive memory architectures. In Proceedings of the IEEE 21st International Symposium on High Performance Computer Architecture (HPCA), Burlingame, CA, USA, 7–11 February 2015; pp. 476–488. [Google Scholar]

- Hazra, J.; Liehr, M.; Beckmann, K.; Rafiq, S.; Cady, N. Improving the Memory Window/Resistance Variability Trade-Off for 65 nm CMOS Integrated HfO2 Based Nanoscale RRAM Devices. In Proceedings of the IEEE International Integrated Reliability Workshop (IIRW), South Lake Tahoe, CA, USA, 13–17 October 2019; pp. 1–4. [Google Scholar]

- Grossi, A. Impact of Intercell and Intracell Variability on Forming and Switching Parameters in RRAM Arrays. IEEE Trans. Electron. Devices 2015, 62, 2502–2509. [Google Scholar] [CrossRef]

- Garbin, D. Modeling of OxRAM variability from low to high resistance state using a stochastic trap assisted tunneling-based resistor network. In Proceedings of the Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon, Bologna, Italy, 26–28 January 2015; pp. 125–128. [Google Scholar]

- Chen, A.; Lin, M. Variability of resistive switching memories and its impact on crossbar array performance. In Proceedings of the International Reliability Physics Symposium, Monterey, CA, USA, 10–14 April 2011; pp. 7.1–7.4. [Google Scholar]

- Park, J.; Jo, M. Investigation of state stability of low-resistance state in resistive memory. IEEE Electron. Device Lett. 2010, 31, 485–487. [Google Scholar] [CrossRef]

- Muraoka, S.; Ninomiya, T. Comprehensive understanding of conductive filament characteristics and retention properties for highly reliable ReRAM. In Proceedings of the 2013 Symposium on VLSI Technology, Kyoto, Japan, 11–13 June 2013; pp. 62–63. [Google Scholar]

- Pérez, E.; Grossi, A. Temperature impact and programming algorithm for RRAM based memories. In Proceedings of the IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Ann Arbor, MI, USA, 16–18 July 2018; pp. 1–3. [Google Scholar]

- Puglisi, F.M.; Qafa, A. Temperature Impact on the Reset Operation in HfO2 RRAM. IEEE Electron. Device Lett. 2015, 36, 244–246. [Google Scholar] [CrossRef]

- Wu, L. Nonlinear Weight Quantification for Mitigating Read Disturb Effect on Multilevel RRAM-Based Neural Network. In Proceedings of the IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Chengdu, China, 8–11 April 2021; pp. 1–3. [Google Scholar]

- Li, X. Improvement of read disturb on TaOx-based RRAM cells with optimized pulse programming method. In Proceedings of the IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Chengdu, China, 13–15 November 2019; pp. 176–177. [Google Scholar]

- Shim, W.; Luo, Y.; Seo, J. Impact of Read Disturb on Multilevel RRAM based Inference Engine: Experiments and Model Prediction. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–5. [Google Scholar]

- Su, P.C.; Jiang, C.M.; Wang, C.W. Correlation between SET-state current level and read-disturb failure time in a resistive switching memory. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. P-MY.1-1–P-MY.1-5. [Google Scholar]

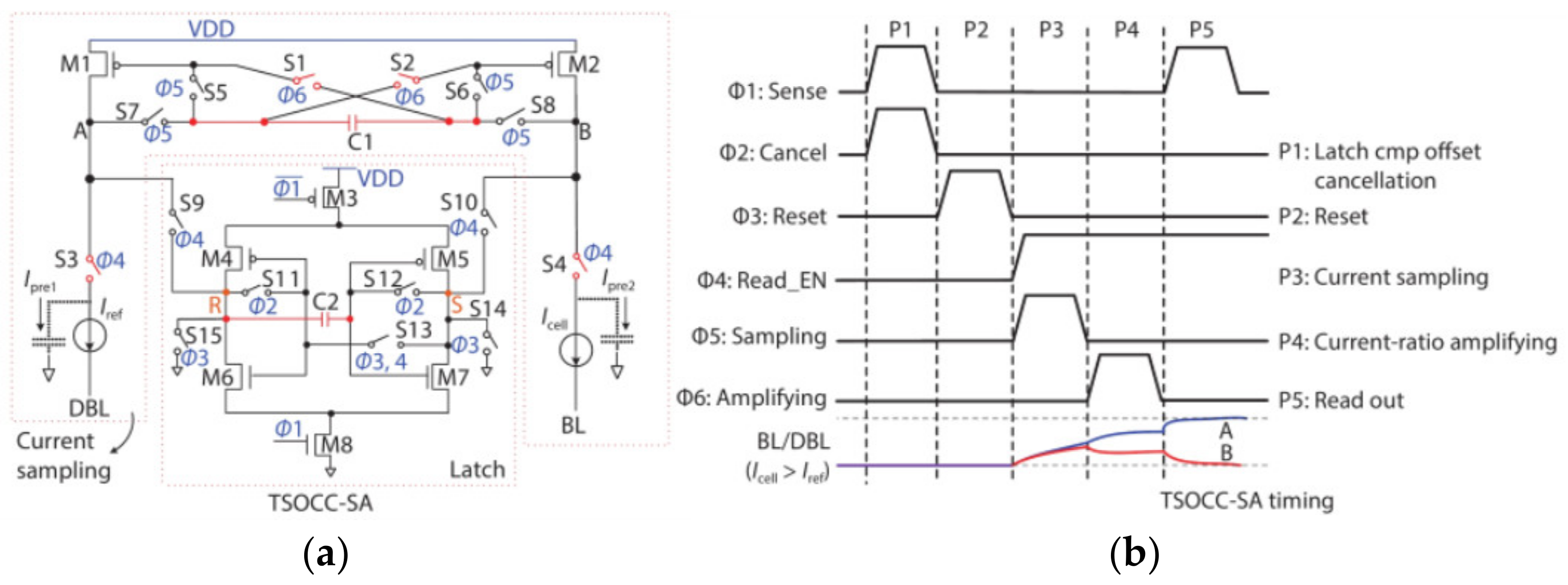

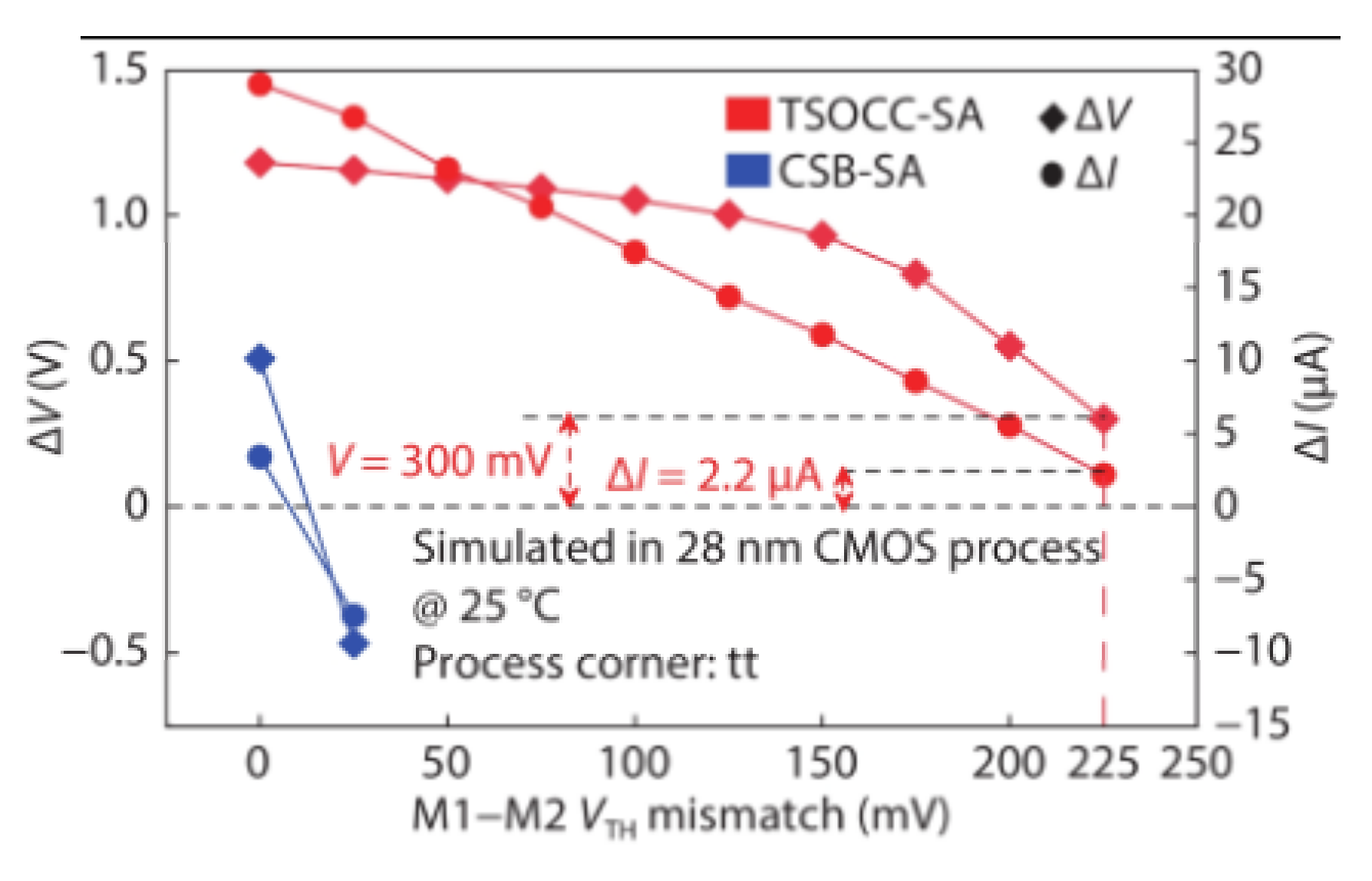

- Na, T.; Song, B.; Kim, J.P.; Kang, S.H.; Jung, S. Offset-Canceling Current-Sampling Sense Amplifier for Resistive Nonvolatile Memory in 65 nm CMOS. IEEE J. Solid State Circuits 2017, 52, 496–504. [Google Scholar] [CrossRef]

- Chang, M. An Offset-Tolerant Fast-Random-Read Current-Sampling-Based Sense Amplifier for Small-Cell-Current Nonvolatile Memory. IEEE J. Solid State Circuits 2013, 48, 864–877. [Google Scholar] [CrossRef]

- Chen, Y.; Chin, A. An Offset Readout Current Sensing Scheme for One-Resistor RRAM-Based Cross-Point Array. IEEE Electron. Device Lett. 2019, 40, 208–211. [Google Scholar] [CrossRef]

- Luo, Y.; Chen, W.; Cheng, M.; Yin, W. Electrothermal Characterization in 3-D Resistive Random Access Memory Arrays. IEEE Trans. Electron. Devices 2016, 63, 4720–4728. [Google Scholar] [CrossRef]

- Chang, M. A High-Speed 7.2-ns Read-Write Random Access 4-Mb Embedded Resistive RAM (ReRAM) Macro Using Process-Variation-Tolerant Current-Mode Read Schemes. J. Solid State Circuits 2013, 48, 878–891. [Google Scholar] [CrossRef]

- Wang, Q.; Zhang, D.L. Low-cost dual-stage offset-cancelled sense amplifier with hybrid read reference generator for improved read performance of RRAM at advanced technology nodes. J. Semicond. 2021, 42, 082401. [Google Scholar] [CrossRef]

- Chou, C.C. A 22 nm 96KX144 RRAM Macro with a Self-Tracking Reference and a Low Ripple Charge Pump to Achieve a Configurable Read Window and a Wide Operating Voltage Range. In Proceedings of the IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar]

- Yang, J. A 14 nm-FinFET 1 Mb Embedded 1T1R RRAM with a 0.022 µm2 Cell Size Using Self-Adaptive Delayed Termination and Multi-Cell Reference. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 336–338. [Google Scholar]

- Yang, J. A 2 Mb ReRAM with two bits error correction codes circuit for high reliability application. In Proceedings of the IEEE 10th International Conference on ASIC, Shenzhen, China, 28–31 October 2013; pp. 1–4. [Google Scholar]

- Chang, M. 19.4 embedded 1 Mb ReRAM in 28 nm CMOS with 0.27-to-1 V read using swing-sample-and-couple sense amplifier and self-boost-write-termination scheme. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 332–333. [Google Scholar]

- Jain, P. A 3.6 Mb 10.1 Mb/mm2 Embedded Non-Volatile ReRAM Macro in 22 nm FinFET Technology with Adaptive Forming/Set/Reset Schemes Yielding Down to 0.5 V with Sensing Time of 5 ns at 0.7 V. In Proceedings of the IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 212–214. [Google Scholar]

- Lin, C.C. A 256b-wordlength ReRAM-based TCAM with 1 ns search-time and 14× improvement in wordlength-energyefficiency-density product using 2.5T1R cell. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 136–137. [Google Scholar]

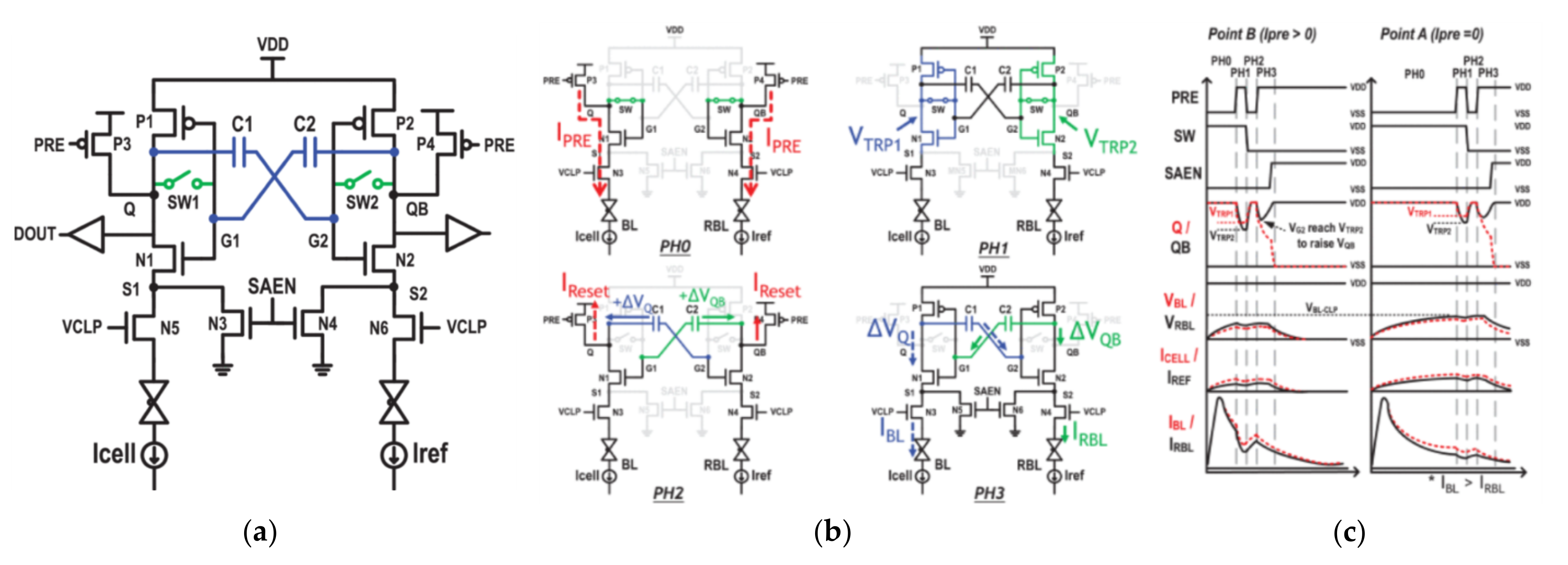

- Lo, C.P. A ReRAM Macro Using Dynamic Trip-Point-Mismatch Sampling Current-Mode Sense Amplifier and Low-DC Voltage-Mode Write-Termination Scheme against Resistance and Write-Delay Variation. IEEE J. Solid State Circuits 2019, 54, 584–595. [Google Scholar] [CrossRef]

- Chang, M.F.; Shen, S.J. An offset-tolerant current-sampling-based sense amplifier for sub-100 nA-cell-current nonvolatile memory. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; p. 206. [Google Scholar]

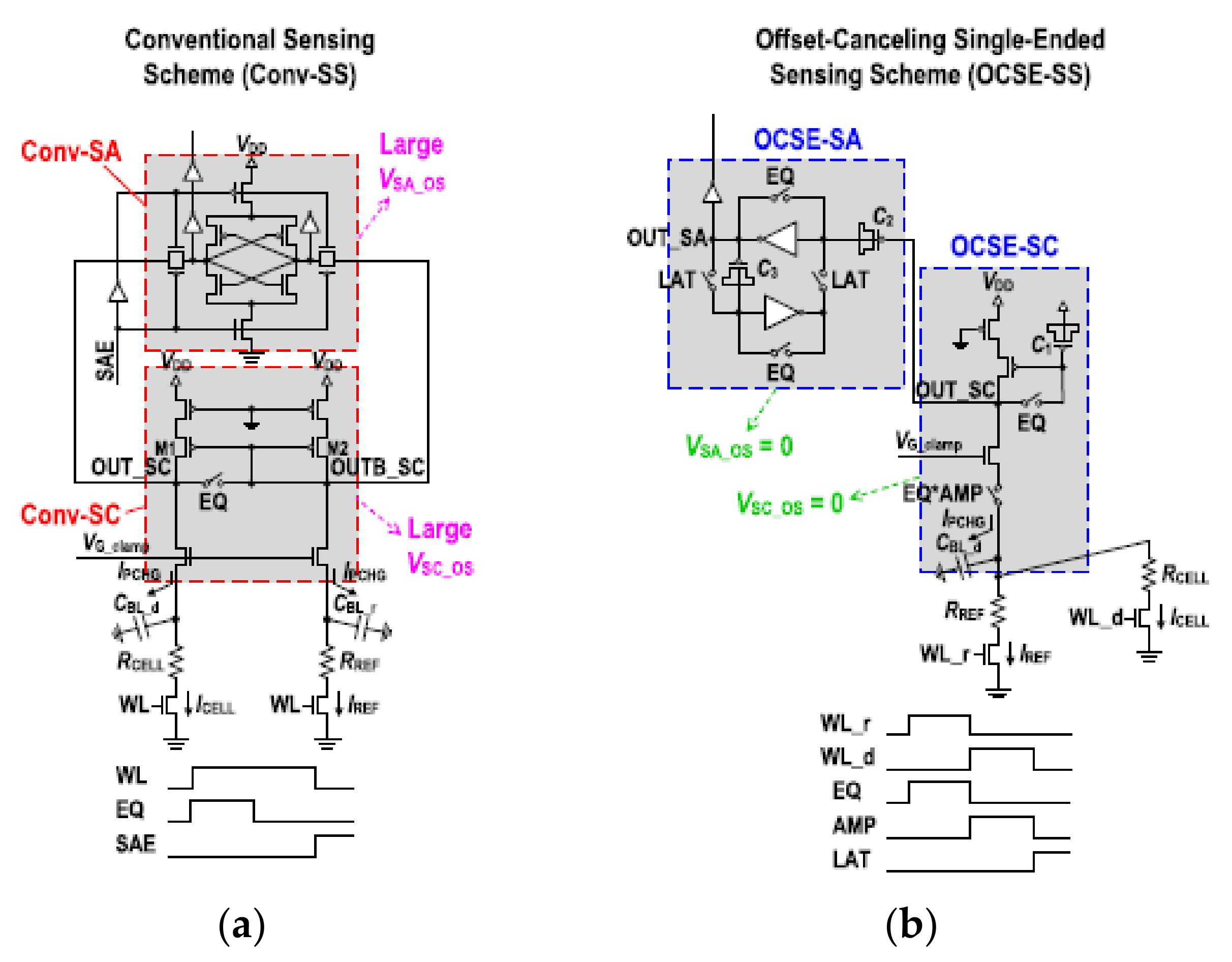

- Na, T.; Song, B. Offset-Canceling Single-Ended Sensing Scheme with One-Bit-Line Precharge Architecture for Resistive Nonvolatile Memory in 65-nm CMOS. IEEE Trans. Large Scale Integr. VLSI Syst. 2019, 27, 2548–2555. [Google Scholar] [CrossRef]

- Chang, M. A Low-Voltage Bulk-Drain-Driven Read Scheme for Sub-0.5 V 4 Mb 65 nm Logic-Process Compatible Embedded Resistive RAM (ReRAM) Macro. IEEE J. Solid State Circuits 2013, 48, 2250–2259. [Google Scholar] [CrossRef]

| Reference | Cell Structure/ Storge Size (Bite)/ Technology Node | Speed/Programming Condition | Optimization of Scheme |

|---|---|---|---|

| X.Y.Xue 2012 VLSI (Fudan) | 1T1R/8 M/130 nm | TAC = 21 ns@VDD = 1.2 V | self-adaptive write mode (SAWM) self-adaptive read mode (SARM) |

| Meng-Fan Chang 2013 JSSC (NTHU) | 1T1R/4 M/180 nm | TAC = 7.2 ns@VDD = 1.8 V | parallel-series reference cell (PSRC) process temperature-aware dynamic BL-bias (PTADB) schemes |

| Sung Hyun Jo 2014 IEDM (Crossbar) | 1S1R/4 M/100 nm | NA | NA |

| Meng-Fan Chang 2014 ISSCC (NTHU) | 1T1R/1 M/28 nm | TAC = 6.8 ns@VDD = 0.85 V TAC = 404 ns@VDD = 0.27 V | swing-sample-and couple voltage-mode sense amplifier (SSCVSA) self-boost-write-termination(SBWT) |

| Tz-yi Liu 2014 JSSC (Sandick) | 1D1R/32 G/24 nm | NA | A dynamic charge pump control scheme Smart Read approach Write scheme and leakage compensation |

| Wei-Hao Chen 2017 IEDM (NTHU) | 1T1R/16 M/150 nm | NA | self-write termination scheme (SAWM) |

| Chung-Cheng Chou 2018 ISSCC (TSMC) | 1T1R/11 M/40 nm | TAC = 9 ns | a low voltage write-current-limiting scheme (LV-WCLS) SL-Precharge SA |

| Chieh-Pu Lo 2019 JSSC (NTHU) | 1T1R/2 M/65 nm | TCD = 2.9 ns | dynamic trip-point-mismatch sampling (DTPMS) scheme a low dc current voltage-mode write termination (LDC-VWT) |

| Pulkit Jain 2019 ISSCC (Intel) | 1T1R/NA/22nm | TAC < 5 ns@VDD = 0.7 V TAC < 10 ns@VDD = 0.5 V | pulse-width (PW) voltage-current write-verify-write (PVC-WVW) offset cancelling current sense amplifier(OC-CAS) |

| Chung-Cheng Chou 2020 VLSI (TSMC) | 1T1R/13.5 M/22 nm | TAC = 6.5 ns@VDD = 0.7 V | Low-Ripple Charge Pump Scheme The Hybrid Self-Tracking Reference |

| Jianguo Yang 2020 VLSI (IMCAS) | 1T2R/1.5 M/28 nm | TAC = 3.3 ns@VDD = 0.8 V | 1T2R cell using PMOS selector hierarchical bitline and 3-state cell storage self-adaptive write with current limiter and sneaking current compensator reverse read with dummy ref. |

| Jianguo Yang 2021 ISSCC (IMCAS) | 1T1R/1 M/14 nm | TAC = 9.5 ns@VDD = 0.8 V TAC = 21 ns@VDD = 0.4 V | Array Architecture Self-adaptive delayed termination (SADT) Multi-Cell Reference |

| The Category of Sensing Schemes | The Acronym of Sensing Schemes | Advantages | Weaknesses |

|---|---|---|---|

| Reference Schemes | Traditional reference | Simple | The poor tracking ability |

| PSRC | Large R-ratio | Cannot adopt to tail bit | |

| HRRS | Tight reference current | Cannot adopt to tail bit | |

| 4T3R reference | Good temperature tracking ability | Cannot adopt to tail bit | |

| MCDC | Adopt to tail bit | Complex | |

| Sensing Amplifier Schemes | Traditional SA | Simple | Low speed, offset current, small sensing margin, high working voltage |

| SSC-VSA | Larger sensing margin | Offset current | |

| OC-CSA | Cancel the offset at data path | Offset current | |

| RS-SA | Cancel the offset at sampling transistors | Offset current | |

| DTPMS-CSA | Cancel the offset at latch | Large area | |

| TSOCC-SA | Small area | Complex | |

| OCSE-SS | Low power consumption | A little poor robustness | |

| BDD-CSA | Low working voltage | Large R-ratio offset current | |

| BL Enhancing Schemes | PTADB | Process temperature-aware | Simple coding |

| LR-CP | Low ripple at BL | High working voltage |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, D.; Peng, B.; Zhao, Y.; Han, Z.; Hu, Q.; Liu, X.; Han, Y.; Yang, H.; Cheng, J.; Ding, Q.; et al. Sensing Circuit Design Techniques for RRAM in Advanced CMOS Technology Nodes. Micromachines 2021, 12, 913. https://doi.org/10.3390/mi12080913

Zhang D, Peng B, Zhao Y, Han Z, Hu Q, Liu X, Han Y, Yang H, Cheng J, Ding Q, et al. Sensing Circuit Design Techniques for RRAM in Advanced CMOS Technology Nodes. Micromachines. 2021; 12(8):913. https://doi.org/10.3390/mi12080913

Chicago/Turabian StyleZhang, Donglin, Bo Peng, Yulin Zhao, Zhongze Han, Qiao Hu, Xuanzhi Liu, Yongkang Han, Honghu Yang, Jinhui Cheng, Qingting Ding, and et al. 2021. "Sensing Circuit Design Techniques for RRAM in Advanced CMOS Technology Nodes" Micromachines 12, no. 8: 913. https://doi.org/10.3390/mi12080913