Comparative Analysis of Modulation Techniques on the Losses and Thermal Limits of Uninterruptible Power Supply Systems

Abstract

1. Introduction

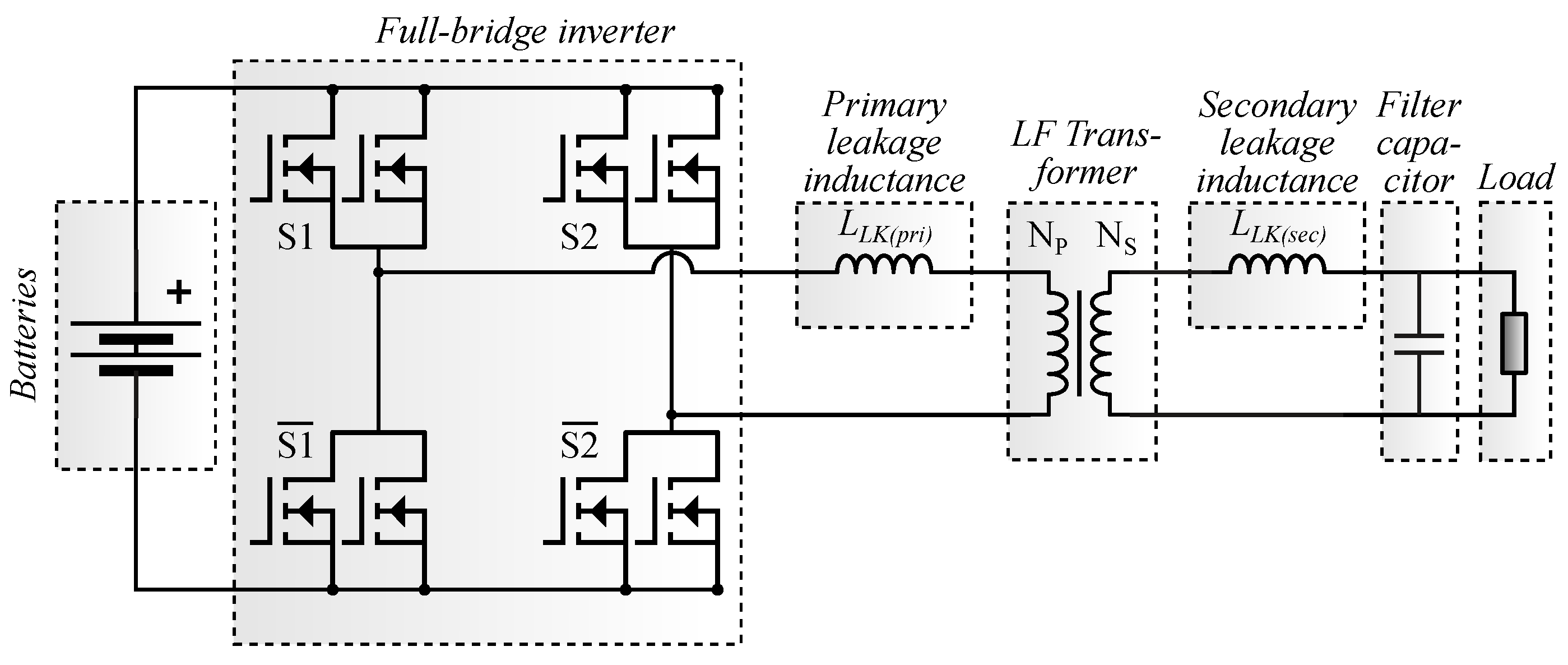

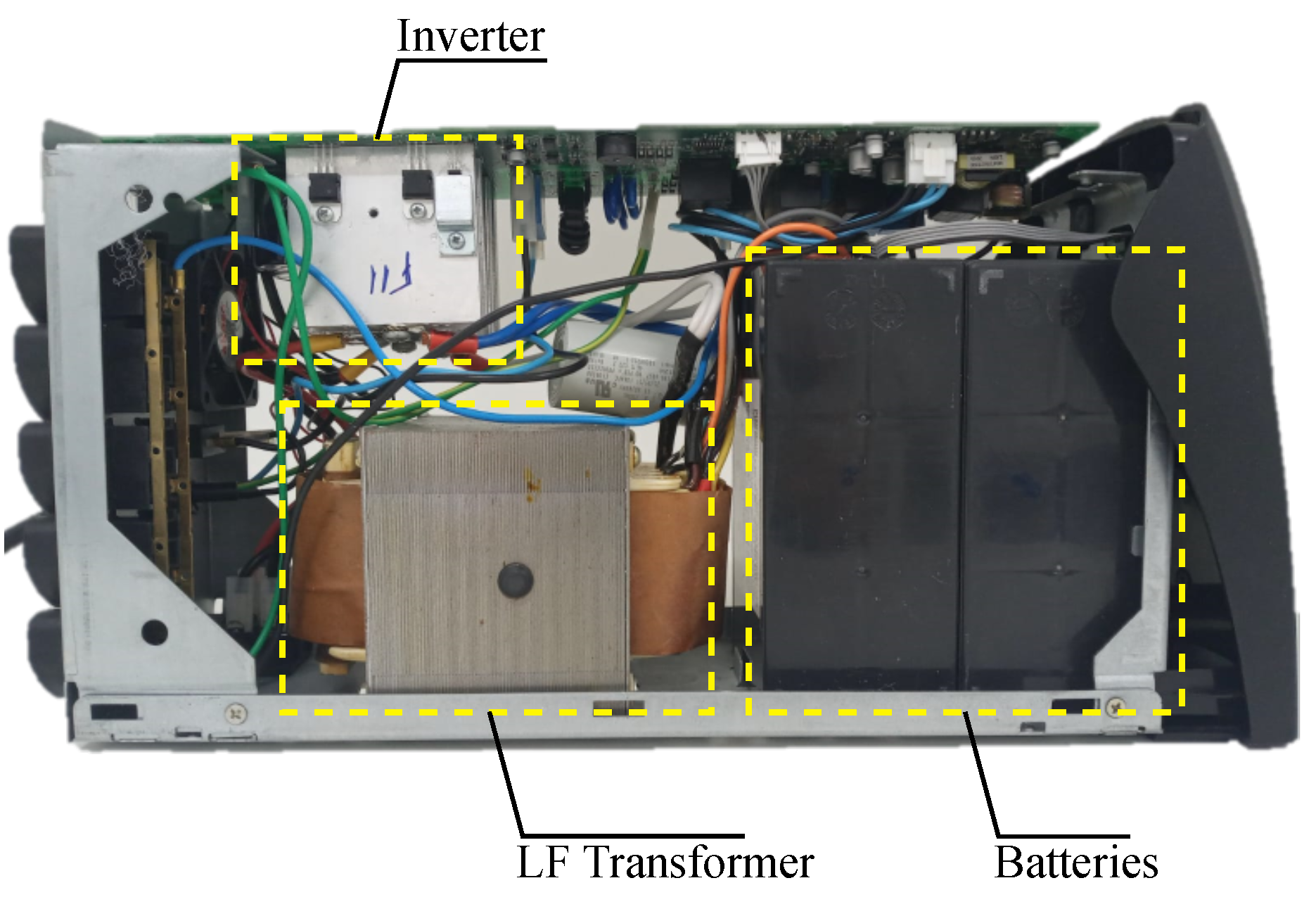

2. UPSs for Applications of Small Office and Home Office (SOHO)

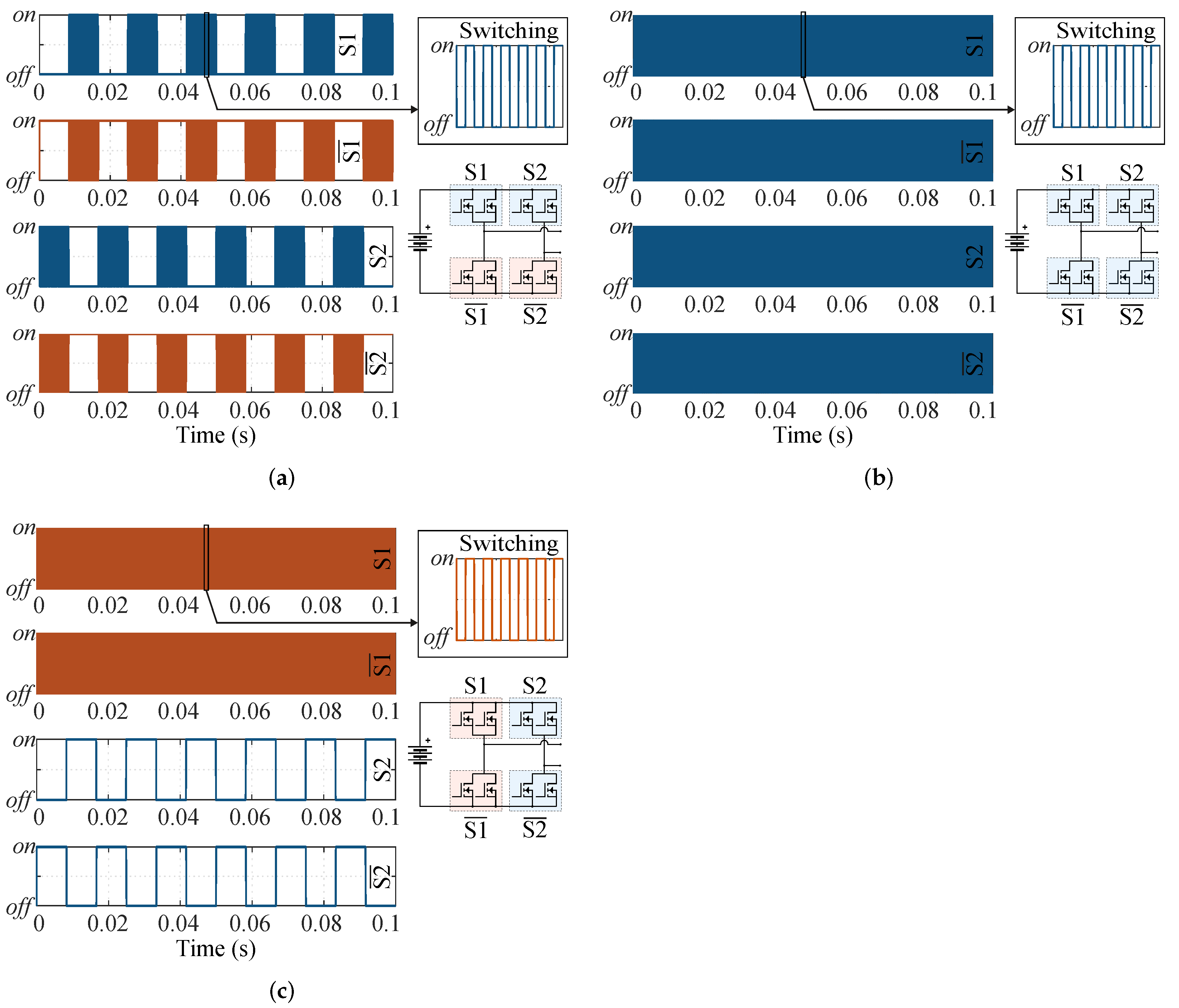

3. Three-Level PWM Applied to Single-Phase Full-Bridge Inverter

- MT1: discontinuous modulation, where only one phase leg is modulated at high frequency in the first half of the fundamental cycle, while the other phase leg is modulated in the second half of the fundamental cycle. The phase legs never switch over within the same carrier period [25].

- MT2: phase-shifted, where both legs of the converter operate at high-frequency [25].

- MT3: discontinuous single-phase leg switched, where one leg works at high frequency and the other at the fundamental cycle frequency [25].

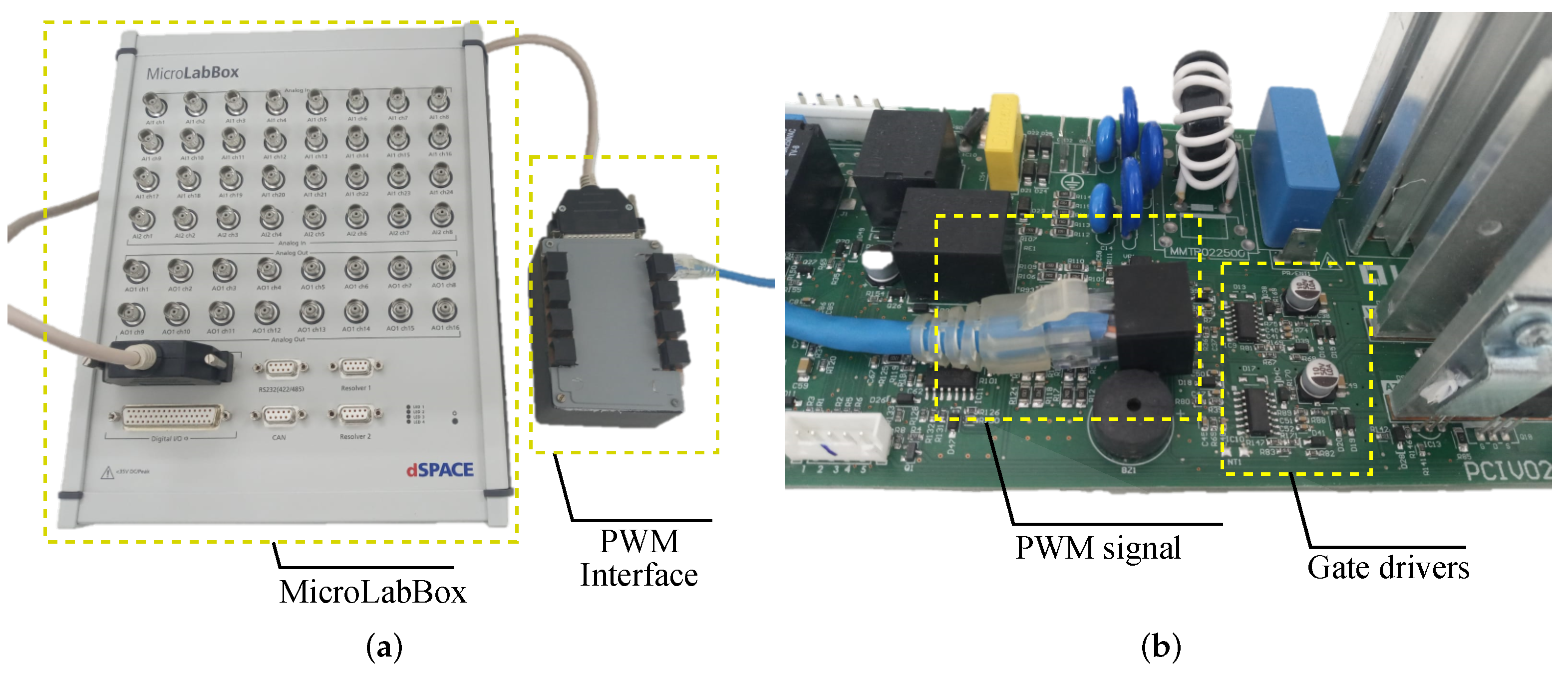

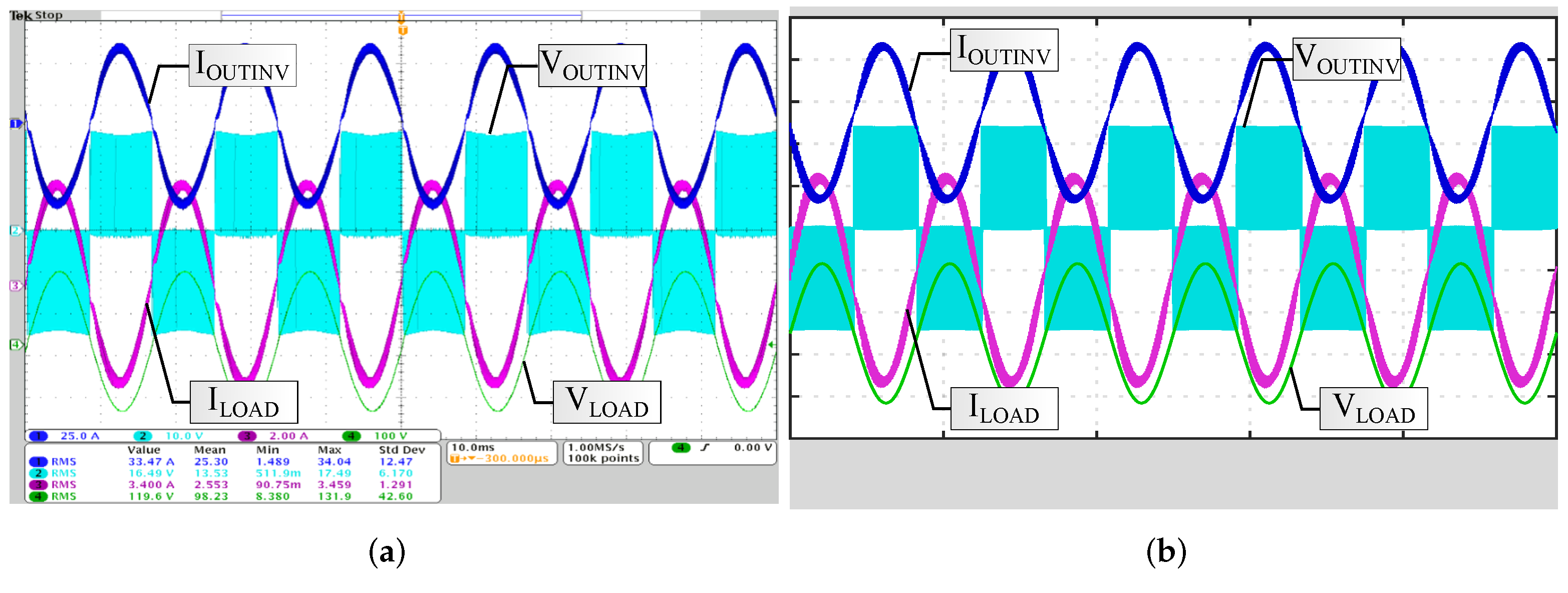

4. Experimental Validation of Computational and Thermal Models

4.1. Computational Models and UPS Waveforms

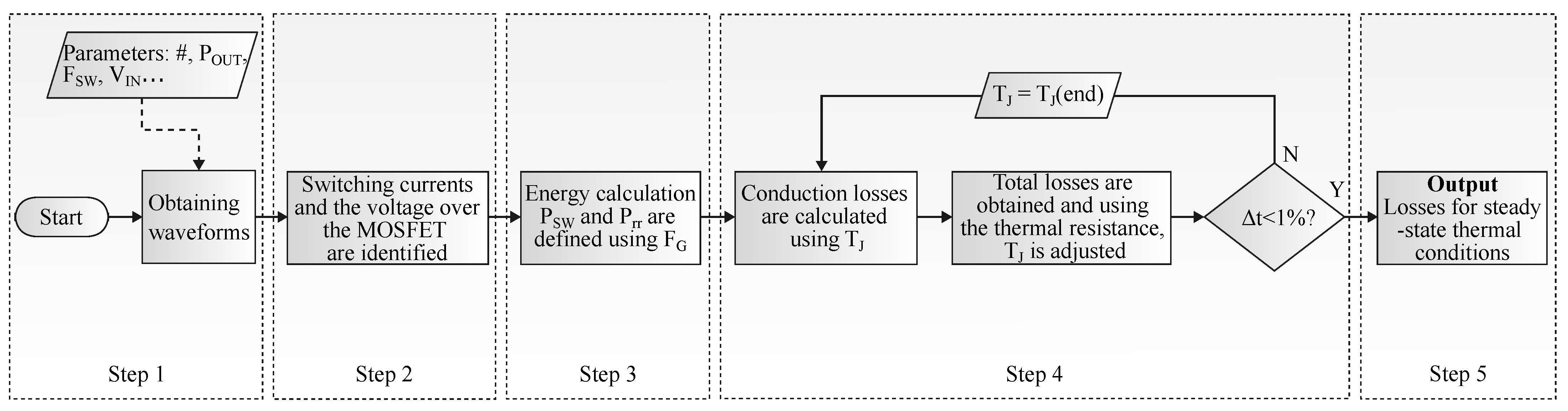

4.2. Model and Methodology for Losses Calculation

- Step 1: system inputs are defined: part number of the MOSFET, power levels, switching frequency range, and input voltage. These data are loaded into MATLAB Simulink® and the waveforms are obtained;

- Step 2: the switching currents and the voltage over the MOSFET are identified;

- Step 3: the energies related to the turn-on and turn-off for each switching cycle are calculated, and using the grid frequency (), and are defined;

- Step 4: the calculation of conduction losses is performed using the junction temperature () and the drain–source on-state resistance () given in the datasheet. Total losses are obtained by adding , , and . Based on the junction-case and case-ambient thermal resistances, is calculated. As influences , and the increase in increases the losses, and [38], the loss calculation process is repeated. This process runs until the difference between the iterations is % (MOSFET thermal steady-state operating point).

- Step 5: as output, the losses for thermal steady-state conditions are defined.

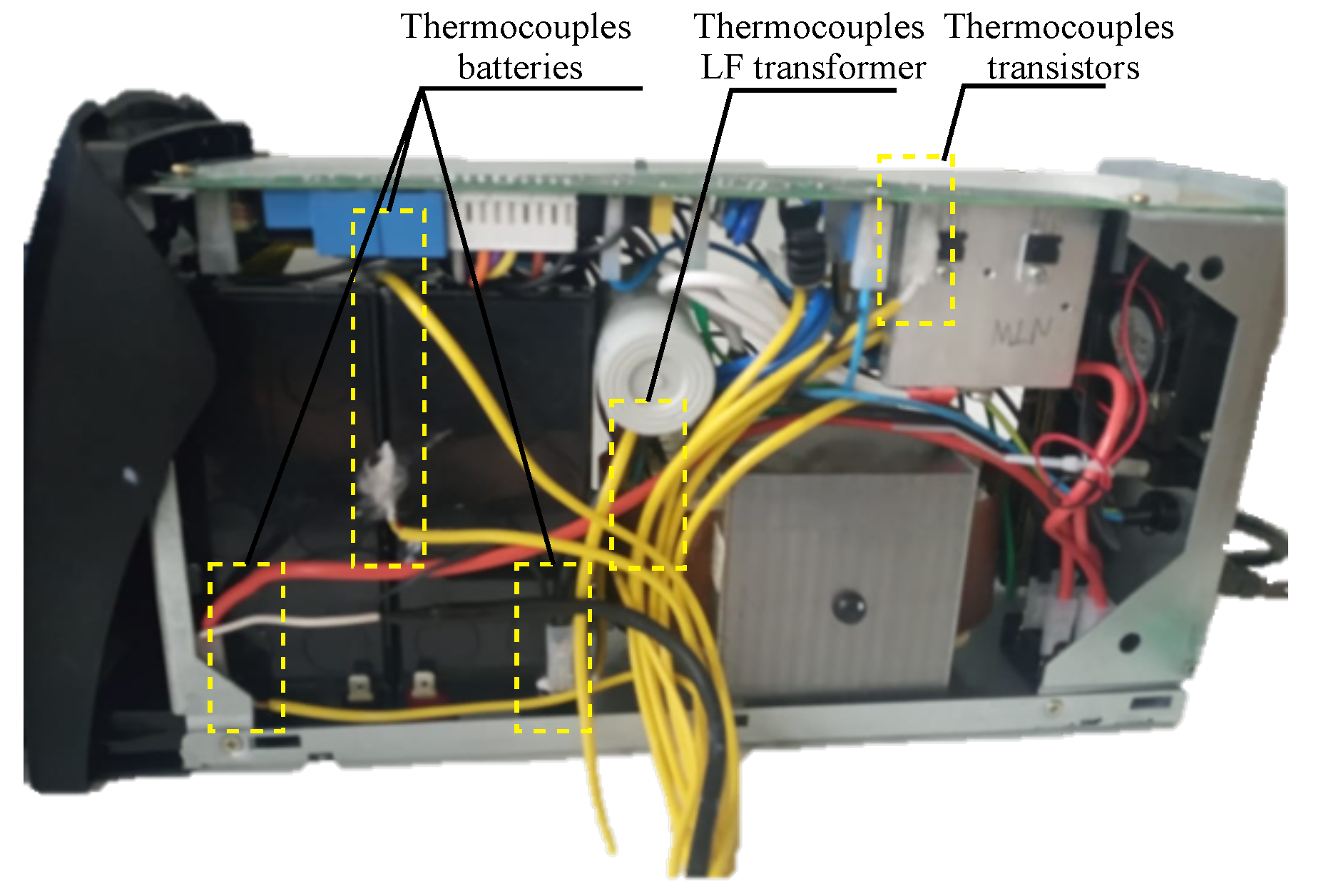

4.3. Thermal Models

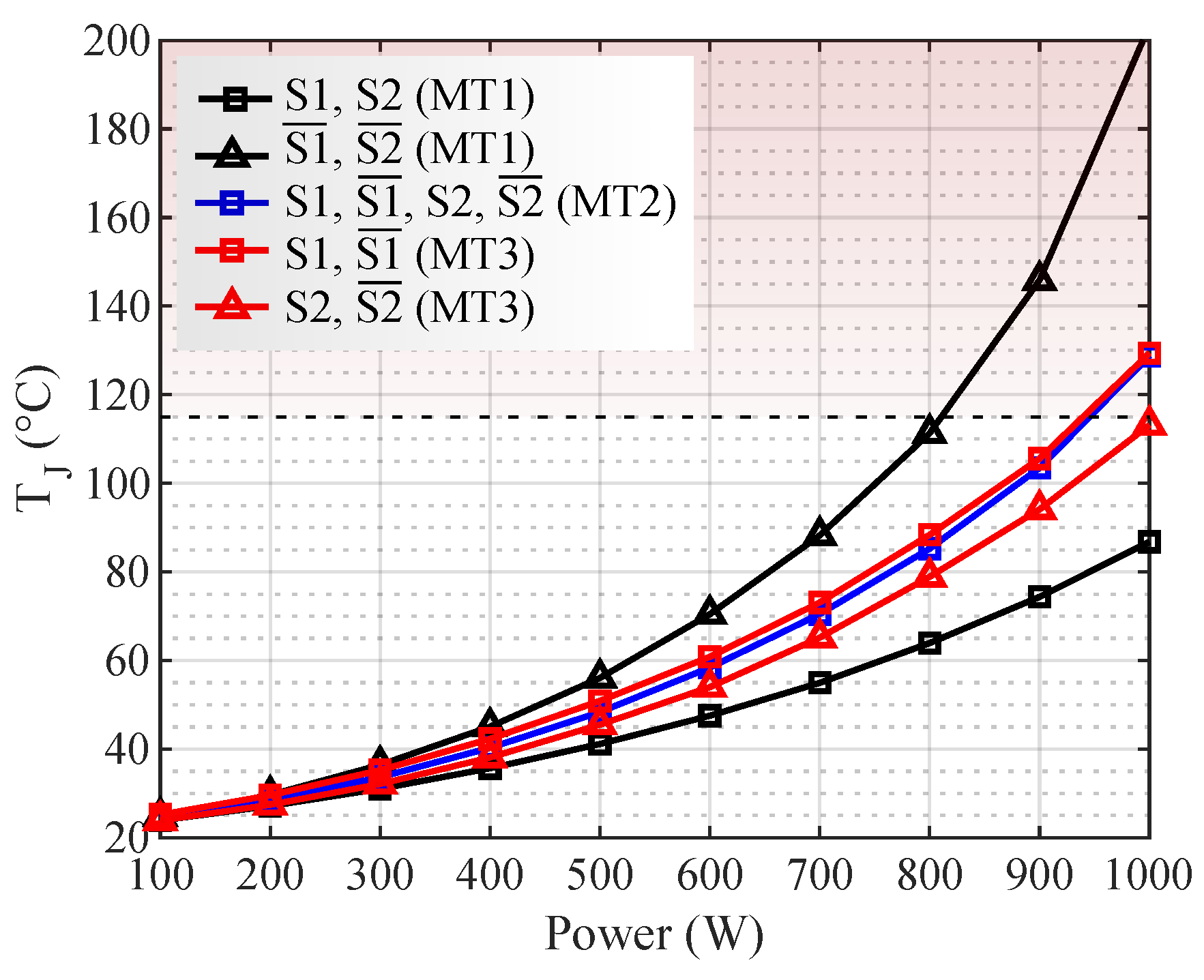

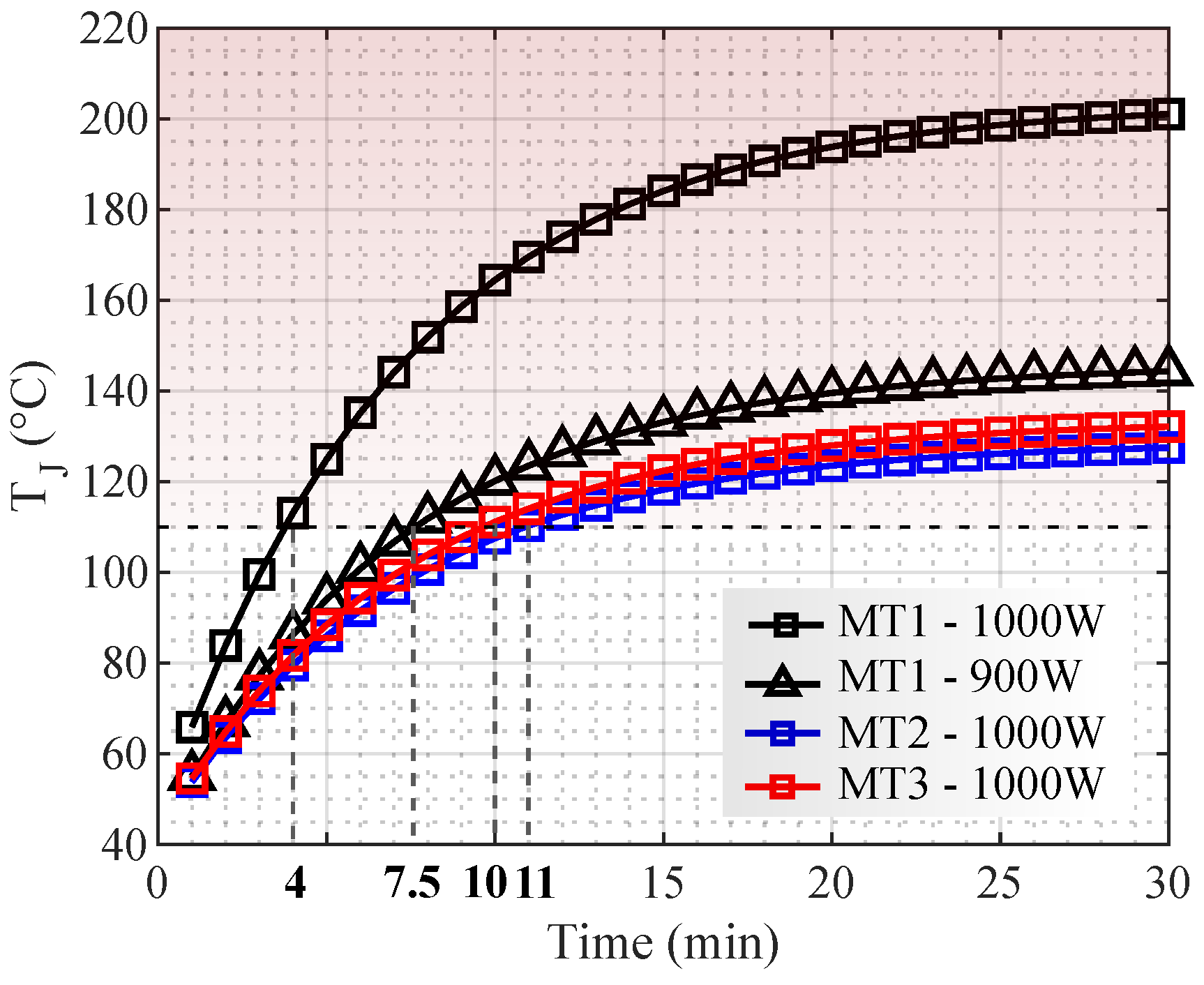

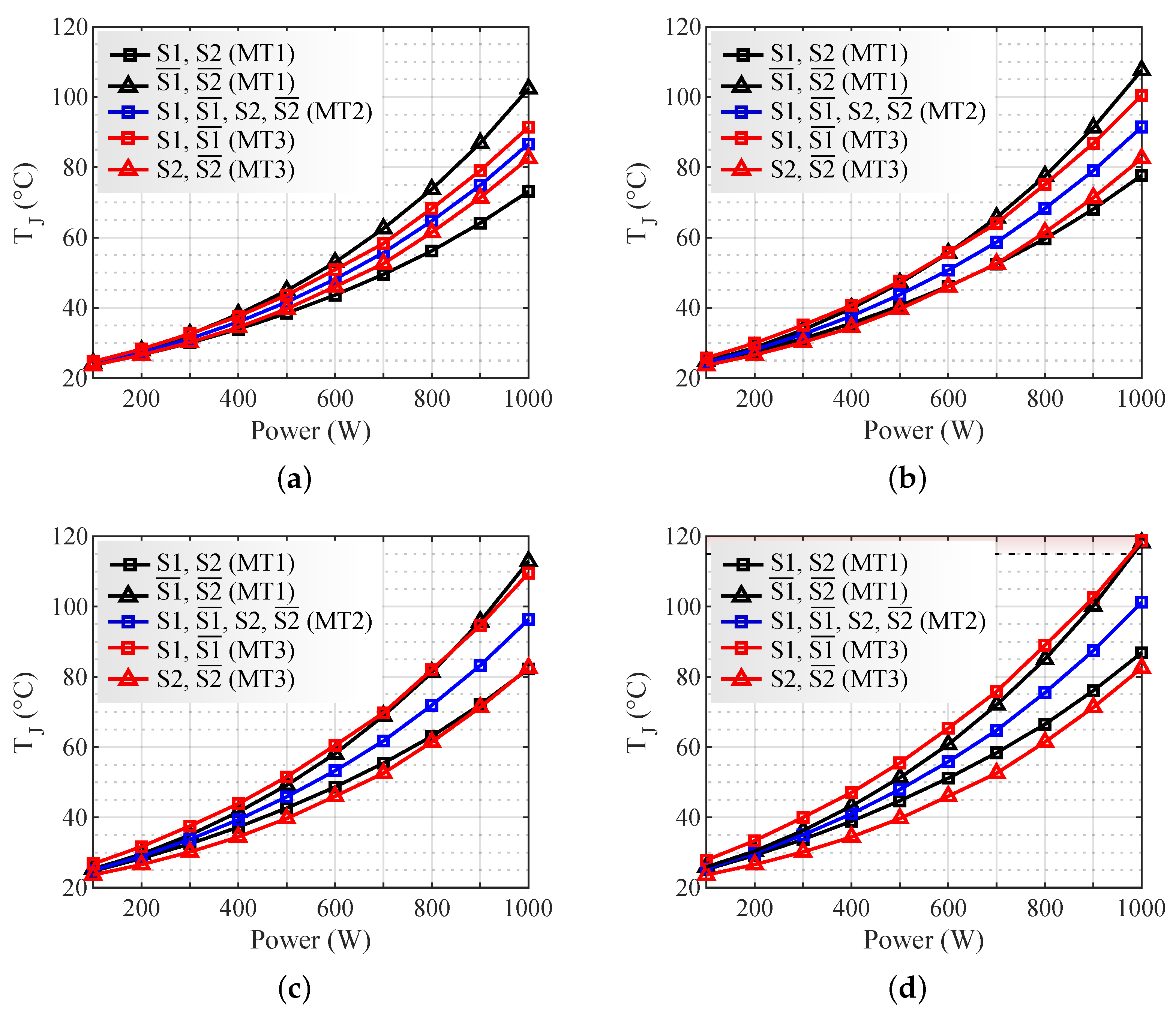

5. Influence of Modulation Techniques on Inverter Losses and Temperature

5.1. Loss Comparison

5.1.1. Scenario 1: Transformer Turn Ratio of

5.1.2. Scenario 2: Transformer Turn Ratio of

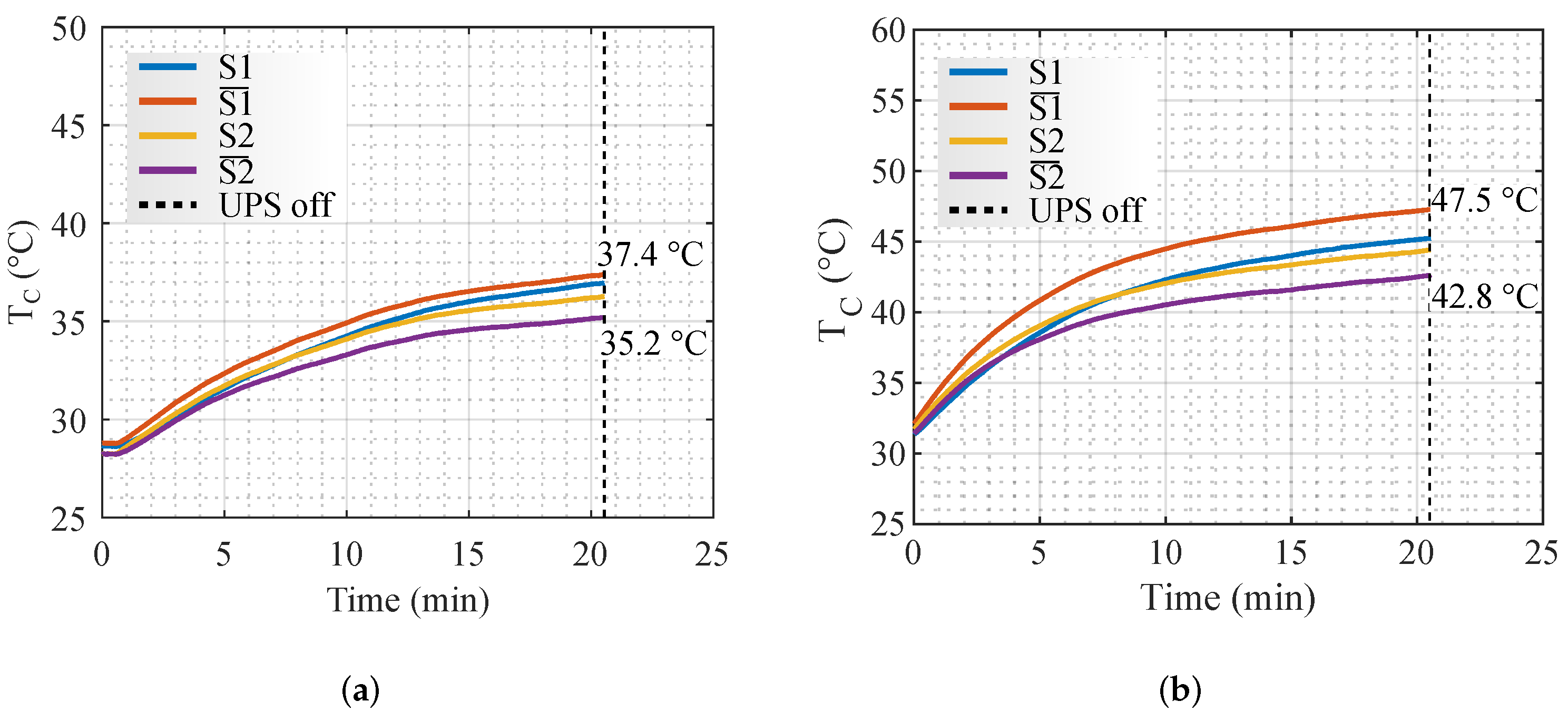

5.2. Thermal Analysis of The Influence of Frequency Variation

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- IEC62040; Uninterruptible Power Systems (UPS) Part 3: Method of Specifying the Performance and Test Requirements. International standard IEC: Geneva, Switzerland, 1999.

- Kwon, B.H.; Choi, J.H.; Kim, T.W. Improved single-phase line-interactive UPS. IEEE Trans. Ind. Electron. 2001, 48, 804–811. [Google Scholar] [CrossRef]

- Bekiarov, S.B.; Emadi, A. Uninterruptible power supplies: Classification, operation, dynamics, and control. In Proceedings of the APEC. Seventeenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No. 02CH37335), Dallas, TX, USA, 10–14 March 2002; Volume 1, pp. 597–604. [Google Scholar]

- Yeh, C.C.; Manjrekar, M.D. A reconfigurable uninterruptible power supply system for multiple power quality applications. IEEE Trans. Power Electron. 2007, 22, 1361–1372. [Google Scholar] [CrossRef]

- Aamir, M.; Kalwar, K.A.; Mekhilef, S. Uninterruptible power supply (UPS) system. Renew. Sustain. Energy Rev. 2016, 58, 1395–1410. [Google Scholar] [CrossRef]

- Iftikhar, M.; Aamir, M.; Waqar, A.; Muslim, F.B.; Alam, I. Line-interactive transformerless uninterruptible power supply (UPS) with a fuel cell as the primary source. Energies 2018, 11, 542. [Google Scholar] [CrossRef]

- Shahzad, D.; Pervaiz, S.; Zaffar, N.A.; Afridi, K.K. GaN-Based High-Power-Density AC–DC–AC Converter for Single-Phase Transformerless Online Uninterruptible Power Supply. IEEE Trans. Power Electron. 2021, 36, 13968–13984. [Google Scholar] [CrossRef]

- Krishnan, R.; Srinivasan, S. Topologies for uninterruptible power supplies. In Proceedings of the ISIE’93-Budapest: IEEE International Symposium on Industrial Electronics Conference Proceedings, Budapest, Hungary, 1–3 June 1993; pp. 122–127. [Google Scholar]

- Karve, S. Three of a kind [UPS topologies, IEC standard]. IEE Rev. 2000, 46, 27–31. [Google Scholar] [CrossRef]

- Bukhari, S.S.H.; Atiq, S.; Lipo, T.A.; Kwon, B.i. Line-interactive uninterruptible power supply system eliminating the inrush current phenomenon. Electr. Power Components Syst. 2016, 44, 1203–1214. [Google Scholar] [CrossRef]

- Bukhari, S.S.H.; Ro, J.S. A single-phase line-interactive UPS system for transformer-coupled loading conditions. IEEE Access 2020, 8, 23143–23153. [Google Scholar] [CrossRef]

- Ton, M.; Fortenbury, B. High Performance Buildings: Data Centers Uninterruptible Power Supplies (UPS); Final PIER-CEC Report; Lawrence Berkeley National Laboratory: Berkeley, CA, USA, 2005. [Google Scholar]

- Guerrero, J.M.; De Vicuna, L.G.; Uceda, J. Uninterruptible power supply systems provide protection. IEEE Ind. Electron. Mag. 2007, 1, 28–38. [Google Scholar] [CrossRef]

- Abusara, M.A.; Guerrero, J.M.; Sharkh, S.M. Line-interactive UPS for microgrids. IEEE Trans. Ind. Electron. 2013, 61, 1292–1300. [Google Scholar] [CrossRef]

- Sharkh, S.M.; Abu-Sara, M.A.; Orfanoudakis, G.I.; Hussain, B. Line Interactive UPS; Wiley-IEEE Press: Hoboken, NJ, USA, 2014. [Google Scholar]

- Green, P.B. MOSFET Selection for Low Voltage UPS; Infineon Technologies AG: Munich, Germany, 2019; Rev. 1.2. [Google Scholar]

- Green, P.B. Low Frequency Transformer Based SOHO UPS Design; Infineon Technologies AG: Munich, Germany, 2020; Rev. 1.1. [Google Scholar]

- Aamir, M.; Kim, H.J. Non-isolated single phase uninterruptible power supply (UPS) system. In Proceedings of the 8th International Conference on Power Electronics-ECCE Asia, Jeju, Korea, 30 May–3 June 2011; pp. 2282–2289. [Google Scholar]

- Alves, W.C.; Morais, L.M.F.; Cortizo, P.C. Design of an Highly Efficient AC-DC-AC Three-Phase Converter Using SiC for UPS Applications. Electronics 2018, 7, 425. [Google Scholar] [CrossRef]

- Lin, Q.; Cai, F.; Wang, W.; Chen, S.; Zhang, Z.; You, S. A high-performance online uninterruptible power supply (UPS) system based on multitask decomposition. IEEE Trans. Ind. Appl. 2019, 55, 7575–7585. [Google Scholar] [CrossRef]

- Ahmed, K.M.U.; Bollen, M.H.; Alvarez, M. A Review of Data Centers Energy Consumption And Reliability Modeling. IEEE Access 2021. [Google Scholar] [CrossRef]

- Bolsi, P.C.; Prado, E.O.; Sartori, H.C.; Lenz, J.M.; Pinheiro, J.R. LCL Filter Parameter and Hardware Design Methodology for Minimum Volume Considering Capacitor Lifetimes. Energies 2022, 15, 4420. [Google Scholar] [CrossRef]

- Jain, P.K.; Espinoza, J.R.; Jin, H. Performance of a single-stage UPS system for single-phase trapezoidal-shaped AC-voltage supplies. IEEE Trans. Power Electron. 1998, 13, 912–923. [Google Scholar] [CrossRef]

- Zhou, Z.J.; Zhang, X.; Xu, P.; Shen, W.X. Single-phase uninterruptible power supply based on Z-source inverter. IEEE Trans. Ind. Electron. 2008, 55, 2997–3004. [Google Scholar] [CrossRef]

- Holmes, D.G.; Lipo, T.A. Pulse Width Modulation for Power Converters: Principles and Practice; John Wiley & Sons: Hoboken, NJ, USA, 2003; Volume 18, pp. 155–214. [Google Scholar]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2007. [Google Scholar]

- Rashid, M.H. Power Electronics: Circuits, Devices, and Applications; Prentice Hall: Englewood Cliffs, NJ, USA, 2003. [Google Scholar]

- Bernacki, K.; Rymarski, Z. Electromagnetic compatibility of voltage source inverters for uninterruptible power supply system depending on the pulse-width modulation scheme. IET Power Electron. 2015, 8, 1026–1034. [Google Scholar] [CrossRef]

- Pinheiro, H.; Jain, P.K.; Joos, G. A comparison of UPS for powering hybrid fiber/coaxial networks. IEEE Trans. Power Electron. 2002, 17, 389–397. [Google Scholar] [CrossRef]

- Racine, M.S.; Parham, J.D.; Rashid, M. An overview of uninterruptible power supplies. In Proceedings of the 37th Annual North American Power Symposium, Ames, IA, USA, 25 October 2005; pp. 159–164. [Google Scholar]

- Rahmat, M.K.; Jovanovic, S.; Lo, K.L. Reliability estimation of uninterruptible power supply systems: Boolean truth table method. In Proceedings of the INTELEC 06-Twenty-Eighth International Telecommunications Energy Conference, Providence, RI, USA, 10–14 September 2006; pp. 1–6. [Google Scholar]

- Rahmat, M.K.; Jovanovic, S.; Lo, K.L. Reliability and Availability modelling of Uninterruptible Power Supply (UPS) systems using Monte-Carlo simulation. In Proceedings of the 2011 5th International Power Engineering and Optimization Conference, Shah Alam, Malaysia, 6–7 June 2011; pp. 267–272. [Google Scholar]

- Rahmat, M.K.; Karim, A.Z.A.; Salleh, M.N.M. Sensitivity analysis of the AC uninterruptible power supply (UPS) reliability. In Proceedings of the 2017 International Conference on Engineering Technology and Technopreneurship (ICE2T), Kuala Lumpur, Malaysia, 18–20 September 2017; pp. 1–6. [Google Scholar]

- Treviso, C.H.; Demian, A.E., Jr.; Ferreira, A.L. Residential, commercial and industrial applications for a 5kW ups unit with interface for solar pannel coupling. Eletrônica Potência 2009, 14, 173–180. [Google Scholar] [CrossRef]

- STMicroelectronics. N-channel 60 V Power MOSFET in a TO-220 package, STP220N6F7. 2015; Rev. 3.

- Prado, E.O.; Bolsi, P.C.; Sartori, H.C.; Pinheiro, J.R. Simple analytical model for accurate switching loss calculation in power MOSFETs using non-linearities of Miller capacitance. IET Power Electron. 2022, 15, 594–604. [Google Scholar] [CrossRef]

- Graovac, D.; Purschel, M.; Kiep, A. MOSFET power losses calculation using the data-sheet parameters. Infineon Appl. Note 2006, 1, 1–23. [Google Scholar]

- Prado, E.O.; Bolsi, P.C.; Sartori, H.C.; Pinheiro, J.R. An Overview about Si, Superjunction, SiC and GaN Power MOSFET Technologies in Power Electronics Applications. Energies 2022, 15, 5244. [Google Scholar] [CrossRef]

- Lakkas, G. MOSFET power losses and how they affect power-supply efficiency. Analog Appl 2016, 10, 22–26. [Google Scholar]

- Prado, E.O.; Sartori, H.C.; Pinheiro, J.R. How to select power transistors for static converters applications? In Proceedings of the 2018 13th IEEE International Conference on Industry Applications (INDUSCON), Sao Paulo, Brazil, 12–14 November 2018; pp. 138–143. [Google Scholar]

- Seshasayee, N. Understanding thermal dissipation and design of a heatsink. Texas Instruments Dallas 2011, 1–4. [Google Scholar]

- Chen, H.; Ji, B.; Pickert, V.; Cao, W. Real-time temperature estimation for power MOSFETs considering thermal aging effects. IEEE Trans. Device Mater. Reliab. 2013, 14, 220–228. [Google Scholar] [CrossRef]

- Yang, K.; Guo, J.; Ge, H.; Bilgin, B.; Loukanov, V.; Emadi, A. Transient electro-thermal analysis for a MOSFET based traction inverter. In Proceedings of the 2014 IEEE Transportation Electrification Conference and Expo (ITEC), Dearborn, MI, USA, 15–18 June 2014; pp. 1–6. [Google Scholar]

- On Semiconductor. Heat Sink Selection Guide for Thermally Enhaced SO8-FL; On Semiconductor: Phoenix, AZ, USA, 2015; Rev. 1. [Google Scholar]

- Melito, M.; Gaito, A.; Sorrentino, G. Thermal effects and junction temperature evaluation of Power MOSFETs. DocID028570 Rev. 2015, 1, 141. [Google Scholar]

| Experimental | Simulation | |

|---|---|---|

| Current at the inverter output | 33.47 A | 33 A |

| Voltage at the inverter output | 16.49 V | 16.44 V |

| Current at the load | 3.4 A | 3.38 A |

| Voltage at the load | 119.6 V | 120 V |

| (°C/W) | (J/°C) | |||||

|---|---|---|---|---|---|---|

| 400 W | 600 W | Average | 400 W | 600 W | Average | |

| S1 | 10.5 | 10.5 | 10.5 | 0.85 | 0.85 | 0.85 |

| 7.2 | 7.2 | 7.2 | 1.1 | 1.1 | 1.1 | |

| S2 | 9.7 | 10.2 | 10 | 0.8 | 0.75 | 0.77 |

| 5.6 | 5.8 | 5.7 | 1.4 | 1.3 | 1.35 | |

| MOSFET Losses (W) | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MT1 | MT2 | MT3 | ||||||||||

| Power (W) | S1 | S2 | S1 | S2 | S1 | S2 | ||||||

| 100 | 0.09 | 0.15 | 0.09 | 0.15 | 0.17 | 0.17 | 0.17 | 0.17 | 0.30 | 0.31 | 0.09 | 0.08 |

| 200 | 0.21 | 0.37 | 0.21 | 0.37 | 0.38 | 0.37 | 0.38 | 0.37 | 0.57 | 0.58 | 0.23 | 0.23 |

| 300 | 0.39 | 0.72 | 0.39 | 0.72 | 0.68 | 0.67 | 0.69 | 0.68 | 0.95 | 0.95 | 0.45 | 0.46 |

| 400 | 0.63 | 1.20 | 0.63 | 1.19 | 1.08 | 1.08 | 1.08 | 1.08 | 1.44 | 1.41 | 0.77 | 0.77 |

| 500 | 0.94 | 1.81 | 0.94 | 1.81 | 1.58 | 1.59 | 1.58 | 1.58 | 2.03 | 2.02 | 1.19 | 1.20 |

| 600 | 1.32 | 2.59 | 1.33 | 2.59 | 2.20 | 2.20 | 2.20 | 2.20 | 2.74 | 2.69 | 1.74 | 1.75 |

| 700 | 1.80 | 3.59 | 1.79 | 3.59 | 2.95 | 2.95 | 2.96 | 2.95 | 3.66 | 3.57 | 2.41 | 2.38 |

| 800 | 2.36 | 4.79 | 2.36 | 4.82 | 3.90 | 3.89 | 3.90 | 3.89 | 4.68 | 4.52 | 3.27 | 3.23 |

| 900 | 3.07 | 6.28 | 3.07 | 6.28 | 5.00 | 5.00 | 5.00 | 5.00 | 5.97 | 5.78 | 4.30 | 4.22 |

| 1000 | 3.90 | 8.11 | 3.90 | 8.11 | 6.34 | 6.34 | 6.34 | 6.33 | 7.36 | 7.39 | 5.42 | 5.56 |

| = 30 kHz | |||

|---|---|---|---|

| Power (W) | MT1 | MT2 | MT3 |

| 100 | 0.47 | 0.48 | 0.57 |

| 200 | 1.15 | 1.16 | 1.26 |

| 300 | 2.21 | 2.20 | 2.30 |

| 400 | 3.65 | 3.63 | 3.74 |

| 500 | 5.50 | 5.47 | 5.61 |

| 600 | 7.83 | 7.76 | 6.53 |

| 700 | 10.78 | 10.56 | 10.76 |

| 800 | 14.33 | 14.10 | 14.34 |

| 900 | 18.70 | 18.28 | 18.64 |

| 1000 | 24.01 | 23.33 | 23.84 |

| = 30 kHz | |||

|---|---|---|---|

| Power (W) | MT1 | MT2 | MT3 |

| 800 | 14.33 | 14.10 | 14.34 |

| 900 | 18.70 | 18.28 | 18.64 |

| 1000 | 24.01 | 23.33 | 23.84 |

| 800 | 22.29 | 21.98 | 22.1 |

| 900 | 29.27 | 28.69 | 29 |

| 1000 | 37.64 | 36.81 | 37.2 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Prado, E.O.; Bolsi, P.C.; Sartori, H.C.; Pinheiro, J.R. Comparative Analysis of Modulation Techniques on the Losses and Thermal Limits of Uninterruptible Power Supply Systems. Micromachines 2022, 13, 1708. https://doi.org/10.3390/mi13101708

Prado EO, Bolsi PC, Sartori HC, Pinheiro JR. Comparative Analysis of Modulation Techniques on the Losses and Thermal Limits of Uninterruptible Power Supply Systems. Micromachines. 2022; 13(10):1708. https://doi.org/10.3390/mi13101708

Chicago/Turabian StylePrado, Edemar O., Pedro C. Bolsi, Hamiltom C. Sartori, and José R. Pinheiro. 2022. "Comparative Analysis of Modulation Techniques on the Losses and Thermal Limits of Uninterruptible Power Supply Systems" Micromachines 13, no. 10: 1708. https://doi.org/10.3390/mi13101708

APA StylePrado, E. O., Bolsi, P. C., Sartori, H. C., & Pinheiro, J. R. (2022). Comparative Analysis of Modulation Techniques on the Losses and Thermal Limits of Uninterruptible Power Supply Systems. Micromachines, 13(10), 1708. https://doi.org/10.3390/mi13101708