IC-Based Rectification Circuit Techniques for Biomedical Energy-Harvesting Applications

Abstract

:1. Introduction

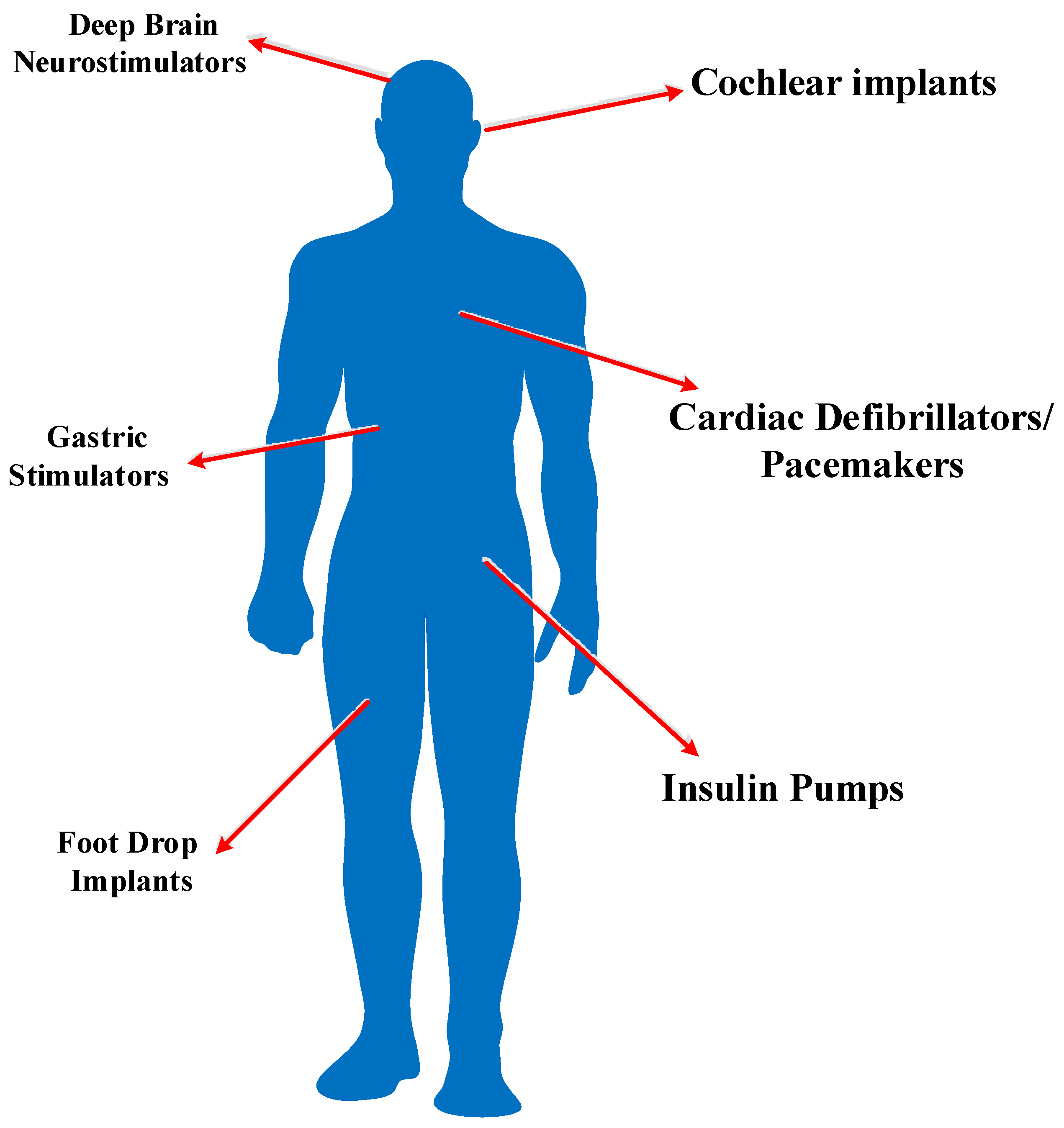

Wireless Implantable Medical Systems

2. Underlying Principles of Wireless Powering

2.1. Theory

2.2. Frequency Selection

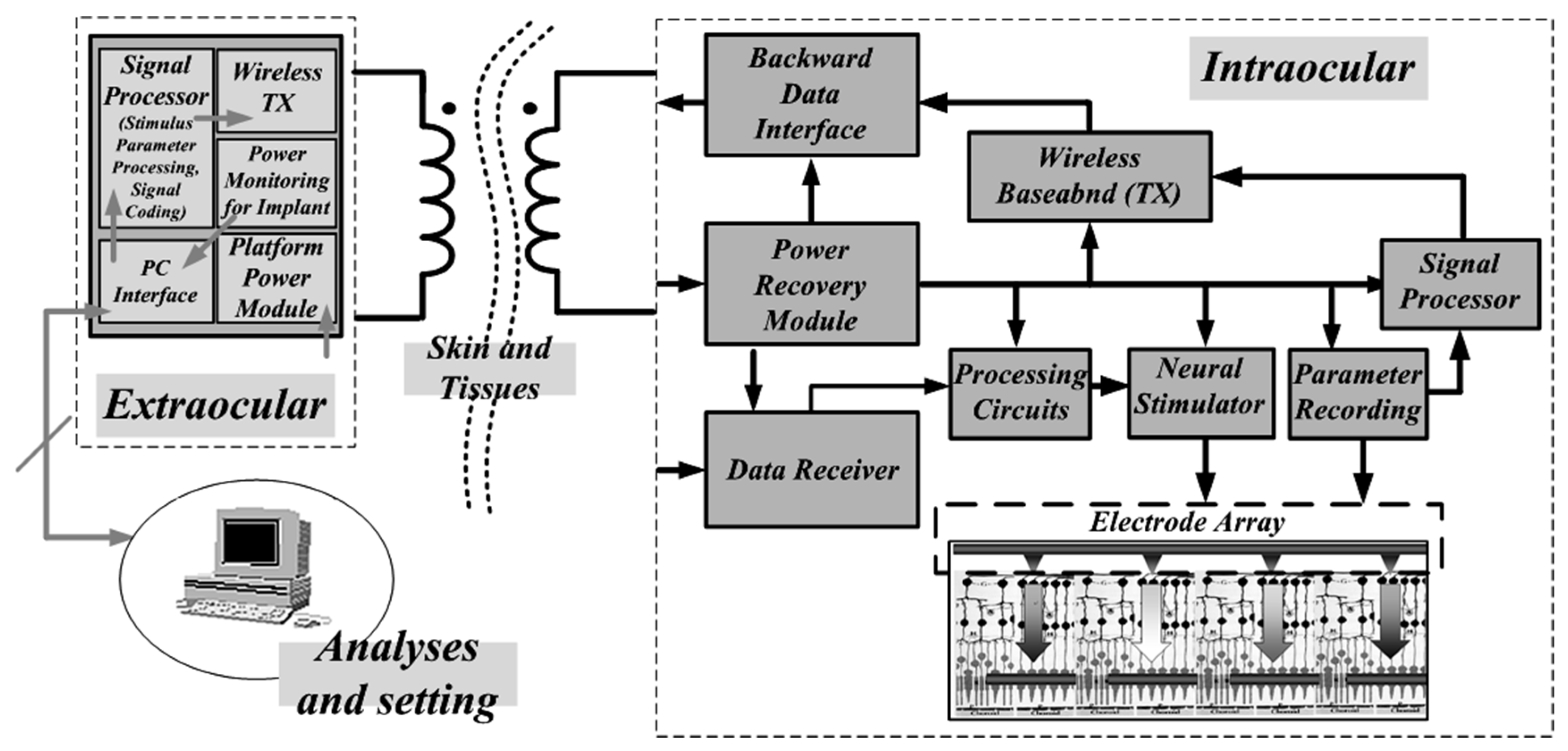

2.3. Wireless Powering in Medicine

3. AC-DC Conversion Circuit Architecture

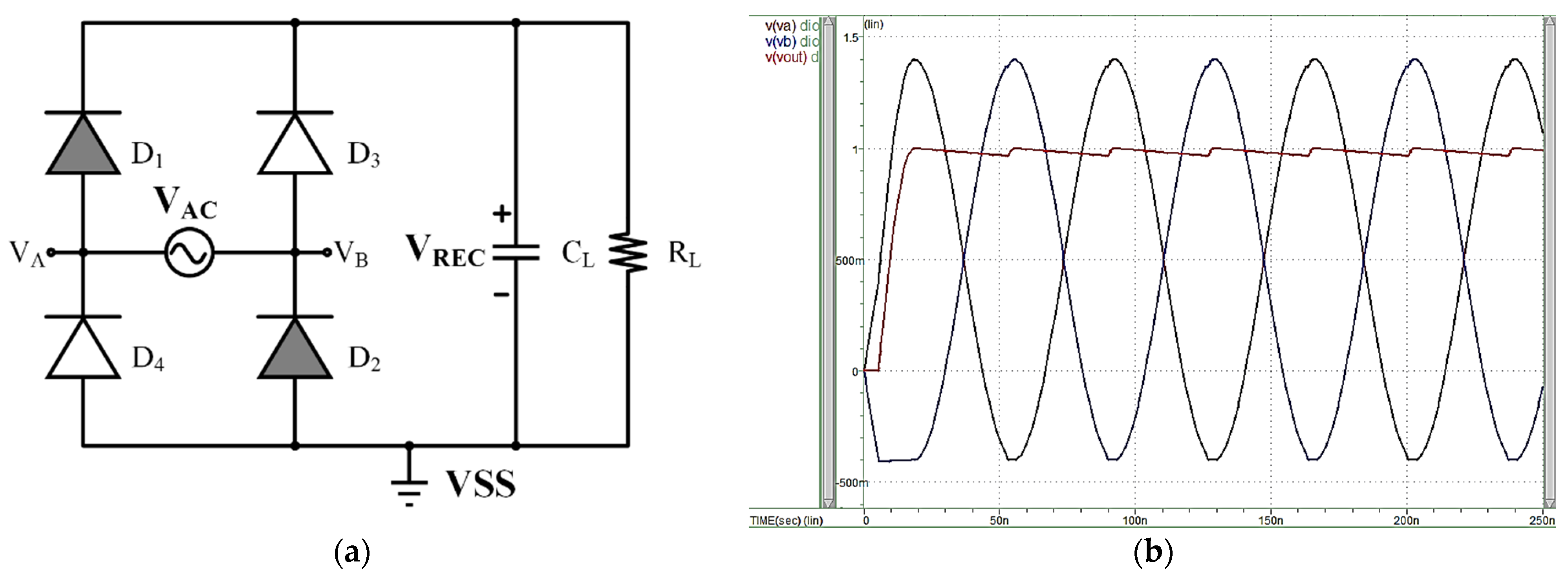

3.1. Full-Wave Diode Bridge Rectifier

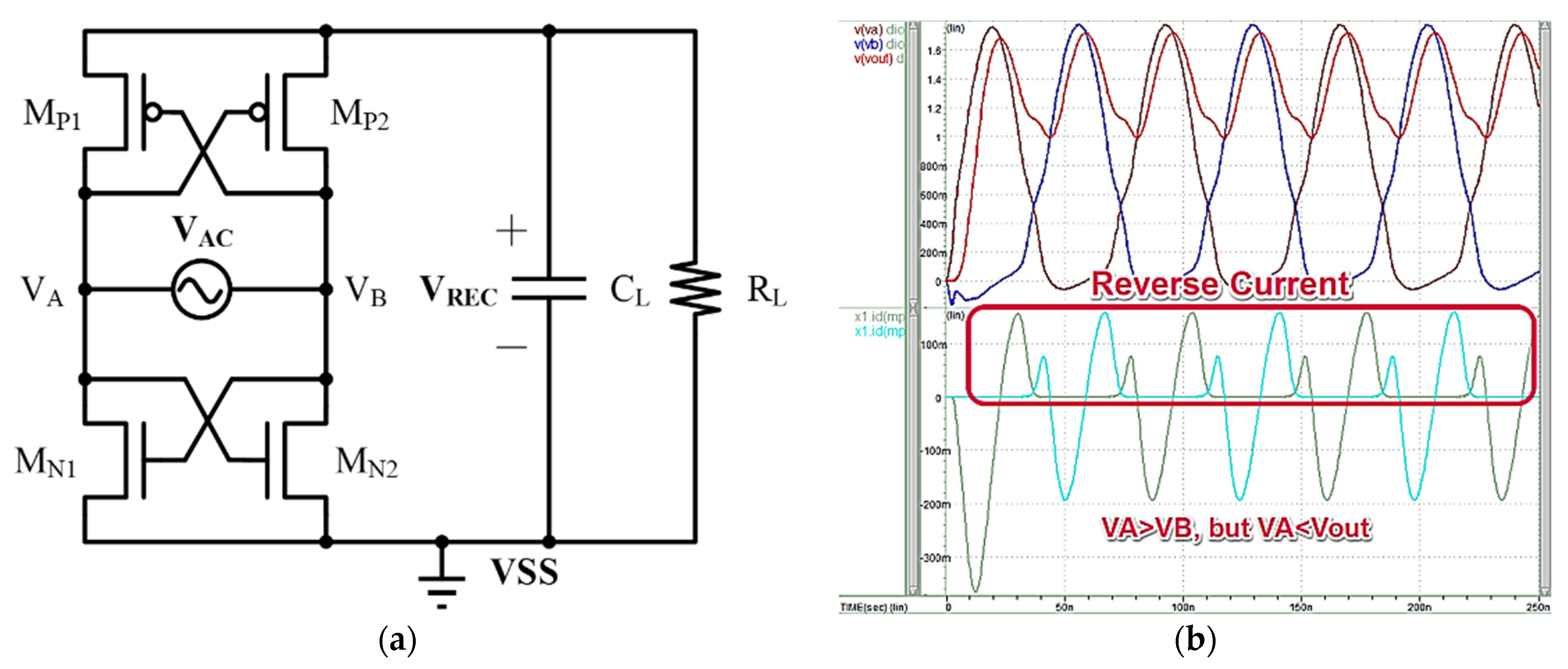

3.2. Dual Cross-Coupled Rectifier

3.3. Hybrid Rectifier

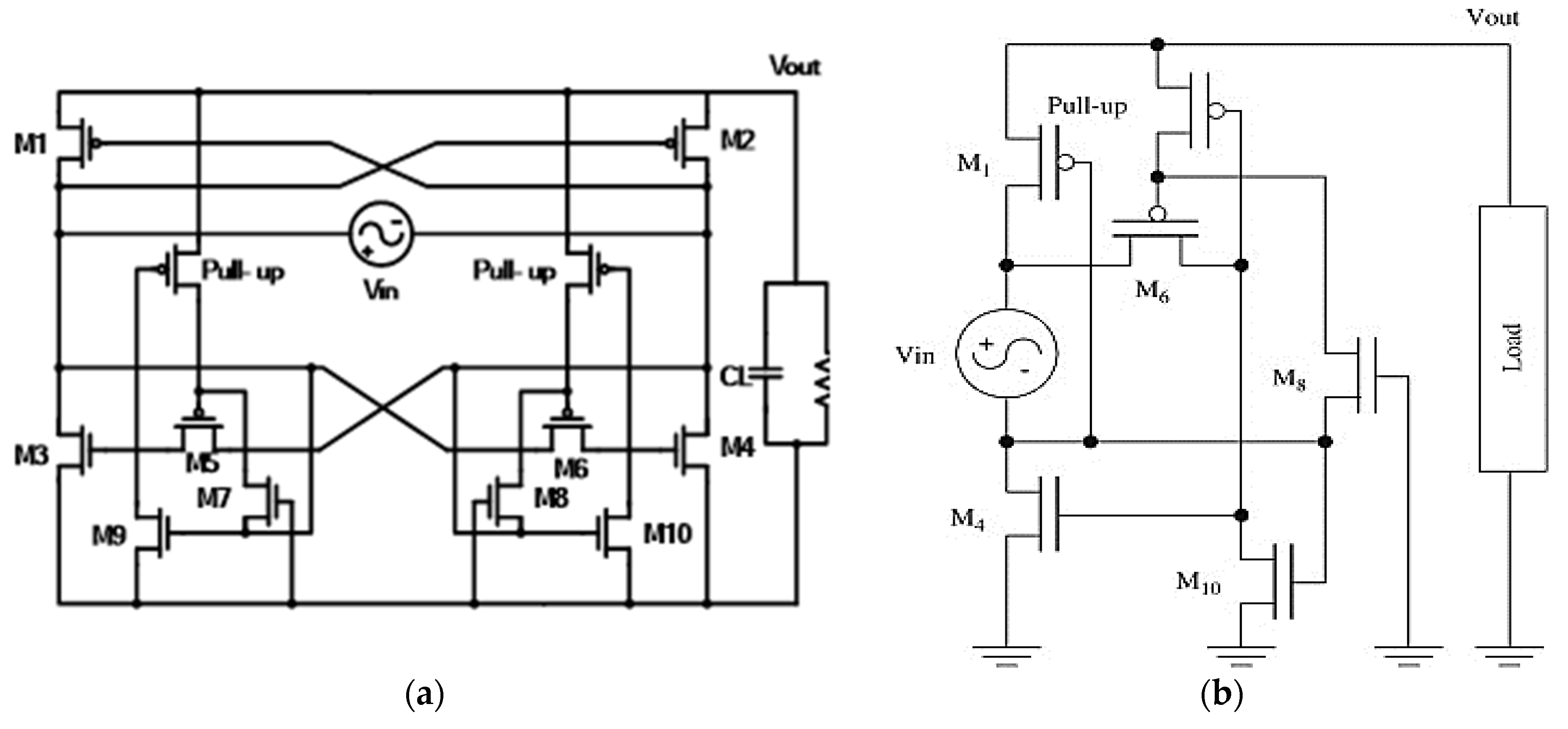

3.4. CMOS Active Rectifier Using Pull-Up Vth Elimination Technology

3.5. CMOS Active Rectifier with Resistance Division Vth Elimination Technology

3.6. Bootstrapped Rectifier

3.7. Full-Wave Active Rectifier

3.8. Active Diode Rectifier

3.9. Two-Stage Active Rectifier

3.10. Highly Efficient Active Rectifier

3.11. Adaptive Delay-Compensated Active Rectifier

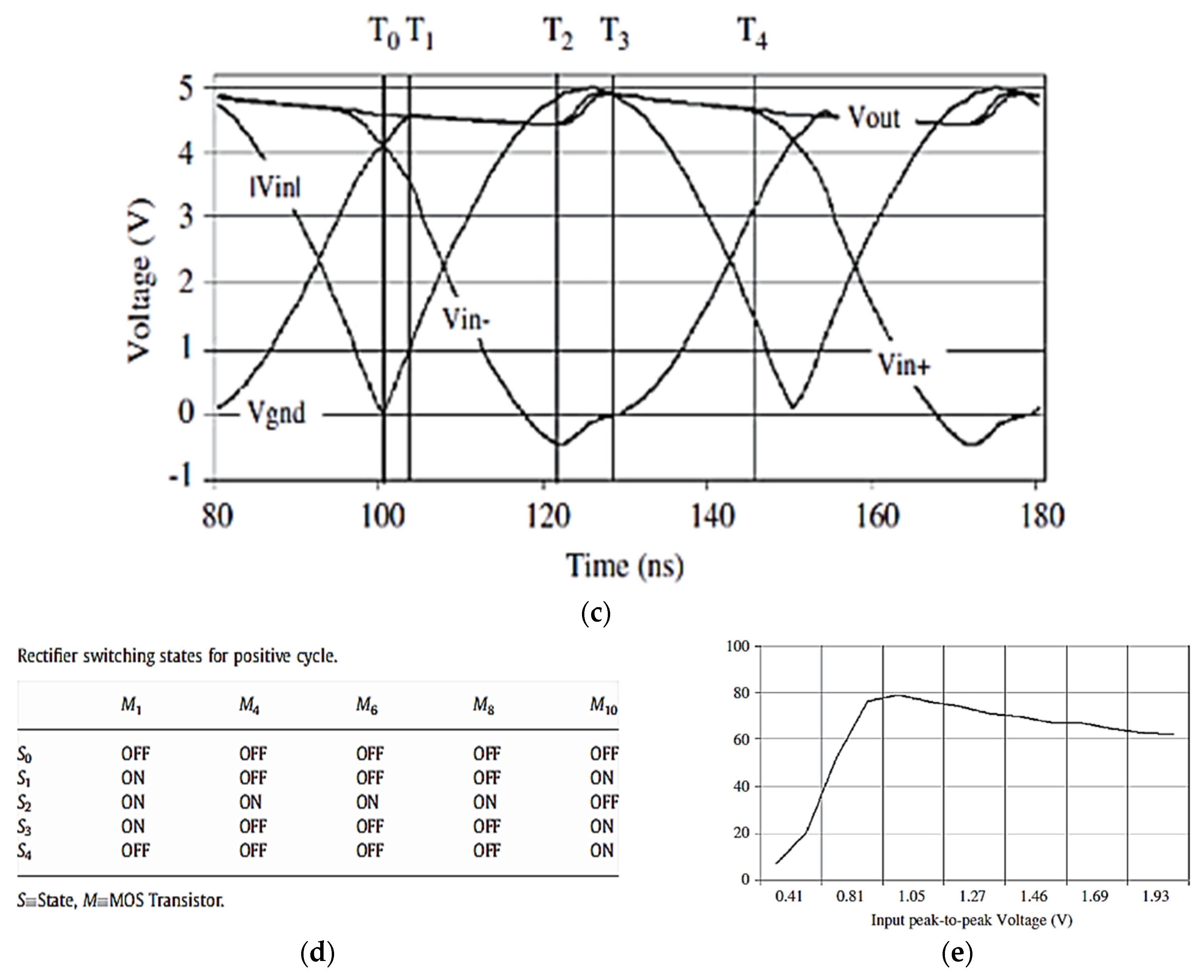

3.12. PCE Estimation Model for the Active Full-Wave Rectifier

4. Conclusions and Discussion

Funding

Acknowledgments

Conflicts of Interest

References

- Sauer, C.; Stanacevic, M.; CaμWenberghs, G.; Thakor, N. Power harvesting andtelemetryin CMOS for implanted devices. IEEE Trans. Circuits Syst. I 2005, 52, 2605–2613. [Google Scholar] [CrossRef]

- Georgiou, J.; Toumazou, C. A 126 W cochlear chip for a totally implantable system. IEEE J. Solid-State Circuits 2005, 40, 430–443. [Google Scholar] [CrossRef]

- Sivaprakasam, M.; Liu, W.; Wang, G.; Weiland, J.D.; Humayun, M.S. Architecture tradeoffs in high-density microstimulators for retinal prosthesis. IEEE Trans. Circuits Syst. I 2005, 52, 2629–2641. [Google Scholar] [CrossRef]

- Lee, S.Y.; Lee, S.C. An implantable wireless bidirectional communication microstimulator for neuromuscular stimulation. IEEE Trans. Circuits Syst. I 2005, 52, 2526–2538. [Google Scholar]

- Ghovanloo, M.; Najafi, K. Fully integrated wideband high-current rectifiers for inductively powered devices. IEEE J. Solid-State Circuits 2004, 39, 1976–1984. [Google Scholar] [CrossRef]

- Hashemi, S.; Sawan, M.; Savaria, Y. A novel low-drop CMOS active rectifier for RF-powered devices: Experimental results. J. Microelectron. 2009, 40, 1547–1554. [Google Scholar] [CrossRef]

- Zargham, M.; Glenn Gulak, P. High-efficiency CMOS rectifier for fully integrated mW wireless power transfer. In Proceedings of the 2012 IEEE International Symposium on Circuits and Systems (ISCAS), Seoul, Korea, 20–23 May 2012; pp. 2869–2872. [Google Scholar]

- Saeid Hashemi, S.; Sawan, M.; Savaria, Y. A high-efficiency low-voltage CMOS rectifier for harvesting energy in implantable devices. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 326–335. [Google Scholar] [CrossRef]

- Chen, C.L.; Chen, K.H.; Liu, S.I. Efficiency-enhanced CMOS rectifier for wireless telemetry. IET Electron. Lett. 2007, 43, 976–978. [Google Scholar] [CrossRef]

- Peters, C.; Handwerker, J.; Maurath, D.; Manoli, Y. A sub-500 mV highly efficient active rectifier for energy harvesting applications. IEEE Trans. Circuits Syst. I 2011, 58, 1542–1550. [Google Scholar] [CrossRef]

- Lee, H.M.; Ghovanloo, M. An integrated power-efficient active rectifier with offset-controlled high speed comparators for inductively powered applications. IEEE Trans. Circuits Syst. I 2011, 58, 1749–1760. [Google Scholar] [CrossRef] [Green Version]

- Heng, L.; Ki, W.H.; Lu, Y.; Yim, T.S. Adaptive on/off delay-compensated active rectifiers for wireless power transfer systems. IEEE J. Solid-State Circuits 2016, 51, 712–723. [Google Scholar]

- Park, H.G.; Jang, J.H.; Kim, H.-J.; Park, Y.-J.; Oh, S.J.; Pu, Y.G.; Hwang, K.C.; Yang, Y.; Lee, K.Y. A Design of a Wireless Power Receiving Unit with a High-Efficiency 6.78-MHz Active Rectifier Using Shared DLLs for Magnetic-Resonant WP Applications. IEEE Trans. Power Electron. 2016, 31, 4484–4498. [Google Scholar] [CrossRef]

- Fu, M.F.; Tang, Z.F.; Liu, M.; Ma, C.B.; Zhu, X.N. Full-Bridge Rectifier Input Reactance Compensation in Megahertz Wireless Power Transfer Systems. In Proceedings of the 2015 IEEE PELS Workshop on Emerging Technologies: Wireless Power, Daejeon, Korea, 5–6 June 2015; pp. 1–5. [Google Scholar]

- Liu, M.; Fu, M.F.; Ma, C.B. Parameter Design for a 6.78-MHz Wireless Power Transfer System Based on Analytical Derivation of Class E Current-Driver Rectifier. IEEE Trans. Power Electron. 2016, 31, 4280–4291. [Google Scholar] [CrossRef]

- Lu, Y.; Ki, W.H. A 13.56 MHz CMOS Active Rectifier with Switched-Offset and Compensated Biasing for Biomedical Wireless Power Transfer System. IEEE Trans Biomed Circuits Syst. 2013, 8, 334–344. [Google Scholar] [CrossRef] [PubMed]

- Shamseh, M.B.; Yuzurihara, I.; Kawamura, A. A 3.2-kw 13.56-MHz SiC Passive Rectifier With 94% Efficiency Using Commutation Capacitor. IEEE Trans. Power Electron. 2016, 31, 6787–6791. [Google Scholar] [CrossRef]

- Liu, Z.T.; Zhong, Z.; Guo, Y.X. In Vivo High-Efficiency Wireless Power Transfer with Multisine Excitation. IEEE Trans. Microw. Theory Tech. 2017, 65, 3530–3540. [Google Scholar] [CrossRef]

- Chen, P.P.; Yang, H.Z.; Luo, R.; Zhao, B. A Tissue-Channel Transcutaneous Power Transfer Technique for Implantable Devices. IEEE Trans. Power Electron. 2018, 33, 9753–9761. [Google Scholar] [CrossRef]

- Zeng, Q.; Zhao, S.; Yang, H.; Zhang, Y.; Wu, T. Micro/Nano Technologies for High-Density Retinal Implant. Micromachines 2019, 10, 419. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Gagnon-Turcotte, G.; Khiarak, M.N.; Ethier, G.; Koninck, Y.D.; Gosselin, B. A 0.13 μm CMOS SoC for simultaneous multichannel optogenetics and electrophysiological brain recording. IEEE J. Solid-State Circuits 2018, 53, 3087–3100. [Google Scholar] [CrossRef]

- Lu, C.; Tsui, C.Y.; Ki, W.-H. Vibration Energy Scavenging System with Maximum Power Tracking for Micropower Applications. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2011, 19, 2109–2119. [Google Scholar] [CrossRef]

- Raghunathan, V. Design and power management of energy harvesting embedded systems. In Proceedings of the 2006 International Symposium on Low Po wer Electronics and Design, Tegernsee, Germany, 4–6 October 2006; pp. 369–374. [Google Scholar]

- Lu, C.; Raghunathan, V.; Roy, K. Efficient Design of Micro-Scale Energy Harvesting Systems. IEEE J. Emerg. Sel. Top. Circuits Syst. 2011, 1, 254–266. [Google Scholar] [CrossRef]

- Chen, C.Y.; Chou, P.H. DuraCap: A supercapacitor-based, power-bootstrapping, maximum power point tracking energy-harvesting system. In Proceedings of the 2010 ACM/IEEE International Symposium on Low-Power Electronics and Design, Austin, TX, USA, 18–20 August 2010; pp. 313–318. [Google Scholar]

- Zhang, K.; Hao, Q.; Song, Y.; Wang, J.; Huang, R.; Liu, Y. Modeling and characterization of the implant intra-body communication based on capacitive coupling using a transfer function method. Sensors 2014, 14, 1740–1756. [Google Scholar] [CrossRef]

- Sawma, C.; Sawan, M.; Kassem, A. Capacitive data links intended for implantable medical devices: A survey. In Proceedings of the 2015 International Conference on Advances in Biomedical Engineering (ICABME), Beirut, Lebanon, 16–18 September 2015; pp. 266–269. [Google Scholar]

- Erfani, R.; Marefat, F.; Mohseni, P. Biosafety considerations of a capacitive link for wireless power transfer to biomedical implants. In Proceedings of the 2018 IEEE Biomedical Circuits and Systems Conference (BioCAS), Cleveland, OH, USA, 17–19 October 2018; pp. 355–358. [Google Scholar]

- Erfani, R.; Marefat, F.; Sodagar, A.M.; Mohseni, P. Transcutaneous capacitive wireless power transfer (C-WPT) for biomedical implants. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 2561–2564. [Google Scholar]

- Erfani, R.; Marefat, F.; Sodagar, A.M.; Mohseni, P. Modeling and characterization of capacitive elements with tissue as dielectric material for wireless powering of neural implants. IEEE Trans. Neural Syst. Rehabil. Eng. 2018, 26, 1093–1099. [Google Scholar] [CrossRef] [PubMed]

- Koruprolu, A.; Nag, S.; Erfani, R.; Mohseni, P. Capacitive wireless power and data transfer for implantable medical devices. In Proceedings of the 2018 IEEE Biomedical Circuits and Systems Conference (BioCAS), Cleveland, OH, USA, 17–19 October 2018; pp. 291–294. [Google Scholar]

- Jegadeesan, R.; Agarwal, K.; Guo, Y.-X.; Yen, S.-C.; Thakor, N.V. Wireless power delivery to flexible subcutaneous implants using capacitive coupling. IEEE Trans. Microw. Theory Tech. 2017, 65, 280–292. [Google Scholar] [CrossRef]

- Lee, S.-H.; Bang, J.-S.; Yoon, K.-S.; Gwon, H.-D.; Kim, S.-W.; Cho, I.-K.; Hong, S.-W.; Cho, G.H. Voltage-boosted current-mode wireless power receiver for directly charging a low-voltage battery in implantable medical systems. IEEE Trans. Ind. Electron. 2019, 66, 8860–8865. [Google Scholar] [CrossRef]

- Gougheri, H.S.; Kiani, M. An inductive voltage-/currentmode integrated power management with seamless mode transition and energy recycling. IEEE J. Solid-State Circuits 2019, 54, 874–884. [Google Scholar] [CrossRef]

- Engur, Y.; Ulusan, H.; Yigit, H.A.; Chamanian, S.; Kulah, H. 13.56 MHz mixed mode rectifier circuit for implantable medical devices. In Proceedings of the 19th International Conference on Micro and Nanotechnology for Power Generation and Energy Conversion Applications (PowerMEMS), Krakow, Poland, 2–6 December 2019; pp. 1–4. [Google Scholar]

- Erfani, R.; Marefat, F.; Nag, S.; Mohseni, P. A 1–10-MHz frequency-aware CMOS active rectifier with dual-loop adaptive delay compensation and >230-mW output power for capacitively powered biomedical implants. IEEE J. Solid-State Circuits 2020, 55, 756–766. [Google Scholar] [CrossRef]

- Noh, K.; Amanor-Boadu, J.; Zhang, M.; Sanchez-Sinencio, E. A 13.56-MHz CMOS active rectifier with a voltage mode switched offset comparator for implantable medical devices. IEEE Trans. Very Large Scale Integr. Syst. 2018, 26, 2050–2060. [Google Scholar] [CrossRef]

- Huang, C.; Kawajiri, T.; Ishikuro, H. A 13.56-MHz wireless power transfer system with enhanced load-transient response and efficiency by fully integrated wireless constant-idle-time control for biomedical implants. IEEE J. Solid-State Circuits 2018, 53, 538–551. [Google Scholar] [CrossRef]

- Cheng, H.-C.; Gong, C.-S.A.; Kao, S.-K. A 13.56 MHz CMOS high-efficiency active rectifier with dynamically controllable comparator for biomedical wireless power transfer systems. IEEE Access 2018, 6, 49979–49989. [Google Scholar] [CrossRef]

- Xue, Z.; Fan, S.; Li, D.; Zhang, L.; Gou, W.; Geng, L. A 13.56 MHz, 94.1% peak efficiency CMOS active rectifier with adaptive delay time control for wireless power transmission systems. IEEE J. Solid-State Circuits 2019, 54, 1744–1754. [Google Scholar] [CrossRef]

- Xue, Z.; Fan, S.; Zhang, L.; Guo, Z.; Dong, L.; Li, D.; Geng, L. Single-stage dual-output AC–DC converter for wireless power transmission. In Proceedings of the 2018 IEEE Custom Integrated Circuits Conference (CICC), San Diego, CA, USA, 8–11 April 2018; pp. 1–4. [Google Scholar]

- Cheng, L.; Ki, W.-H.; Tsui, C.-Y. A 6.78-MHz single-stage wireless power receiver using a 3-mode reconfigurable resonant regulating rectifier. IEEE J. Solid-State Circuits 2017, 52, 1412–1423. [Google Scholar] [CrossRef]

- Mohammadi, A.; Redoute, J.; Yuce, M.R. Wireless power transmission for biomedical implants: The role of near-zero threshold CMOS rectifiers. In Proceedings of the 37th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), Milan, Italy, 25–29 August 2015; pp. 5453–5456. [Google Scholar] [CrossRef]

- Kim, C.; Ha, S.; Park, J.; Akinin, A.; Mercier, P.P.; Cauwenberghs, G. A 144-MHz fully integrated resonant regulating rectifier with hybrid pulse modulation for mm-sized implants. IEEE J. Solid-State Circuits 2017, 52, 3043–3055. [Google Scholar] [CrossRef]

- Pan, J.; Abidi, A.A.; Jiang, W.; Markovic, D. Simultaneous transmission of up to 94-mW self-regulated wireless power and up to 5-Mb/s reverse data over a single pair of coils. IEEE J. Solid-State Circuits 2019, 54, 1003–1016. [Google Scholar] [CrossRef]

- Weber, M.J.; Yoshihara, Y.; Sawaby, A.; Charthad, J.; Chang, T.C.; Arbabian, A. A miniaturized single-transducer implantable pressure sensor with time-multiplexed ultrasonic data and power links. IEEE J. Solid-State Circuits 2018, 53, 1089–1101. [Google Scholar] [CrossRef]

- Noghabaei, S.M.; Radin, R.L.; Savaria, Y.; Sawan, M. A High-Efficiency Ultra-Low-Power CMOS Rectifier for RF Energy Harvesting Applications. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018. [Google Scholar]

- Trigui, A.; Hached, S.; Mounaim, F.; Ammari, A.C.; Sawan, M. Inductive Power Transfer System with Self-Calibrated Primary Resonant Frequency. IEEE Trans. Power Electron. 2015, 30, 6078–6087. [Google Scholar] [CrossRef]

- Trigui, A.; Ali, M.; Ammari, A.C.; Savaria, Y.; Sawan, M. Energy Efficient Generic Demodulator for High Data Transmission Rate Over an Inductive Link for Implantable Devices. IEEE Access 2019, 7, 159379–159389. [Google Scholar] [CrossRef]

- Trigui, A.; Ali, M.; Hached, S.; David, J.-P.; Ammari, A.C.; Savaria, Y.; Sawan, M. Generic Wireless Power Transfer and Data Communication System Based on a Novel Modulation Technique. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3978–3990. [Google Scholar] [CrossRef]

| WPC | A4WP | PMA | |

|---|---|---|---|

| Logo |  |  |  |

| Technology | Inductive Coupling + Magnetic Resonance | Magnetic Resonance | Inductive Coupling |

| Main members | Philips Panasonic HTC | Samsung Qualcomm NXP | Duracell-Powermat BlackBerry NEC Starbucks |

| Members | 214 | 120 | 71 |

| Products | >750 | 0 | 10 |

| Phone integrated | >80 | 0 | 0 |

| Market | Phone/industry | Phone/tablet | Phone/tablet |

| Reference | [13] | [14] | [15] | [16] | [17] | [18] | [19] |

|---|---|---|---|---|---|---|---|

| Year | 2016 | 2015 | 2016 | 2014 | 2016 | 2017 | 2018 |

| Frequency | 6.78 MHz | 6.78 MHz | 6.78 MHz | 13.56 MHz | 13.56 MHz | 6.78 MHz | 13.9 MHz |

| Efficiency | 91.5% | 84% | 84% | 90.1% | 94% | 72.6% | 0.39% |

| Description | Full CMOS active rectifier | Full bridge rectifier | Class-E current-driven rectifier | Full wave active rectifier | Passive rectifier | Reconfigurable Rectifier | Tissue-Channel |

| Power | 10 W | 10 W | 20 W | 10 mW | 3.2 kW | NA | NA |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gong, C.-S.A. IC-Based Rectification Circuit Techniques for Biomedical Energy-Harvesting Applications. Micromachines 2022, 13, 411. https://doi.org/10.3390/mi13030411

Gong C-SA. IC-Based Rectification Circuit Techniques for Biomedical Energy-Harvesting Applications. Micromachines. 2022; 13(3):411. https://doi.org/10.3390/mi13030411

Chicago/Turabian StyleGong, Cihun-Siyong Alex. 2022. "IC-Based Rectification Circuit Techniques for Biomedical Energy-Harvesting Applications" Micromachines 13, no. 3: 411. https://doi.org/10.3390/mi13030411

APA StyleGong, C.-S. A. (2022). IC-Based Rectification Circuit Techniques for Biomedical Energy-Harvesting Applications. Micromachines, 13(3), 411. https://doi.org/10.3390/mi13030411