Investigation of the Electrical Coupling Effect for Monolithic 3-Dimensional Nonvolatile Memory Consisting of a Feedback Field-Effect Transistor Using TCAD

Abstract

:1. Introduction

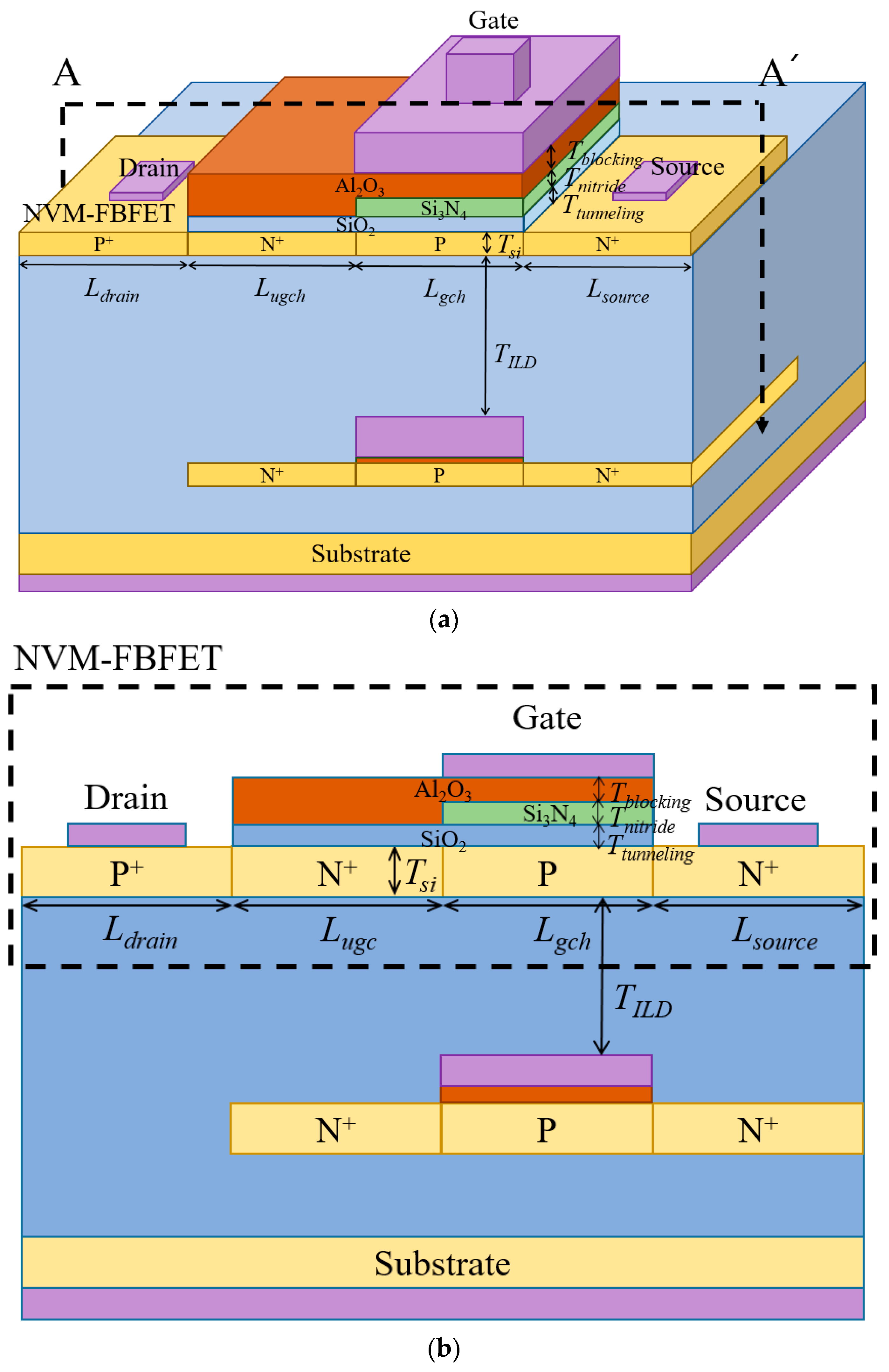

2. Simulation Structure and Parameters

3. Simulation Results

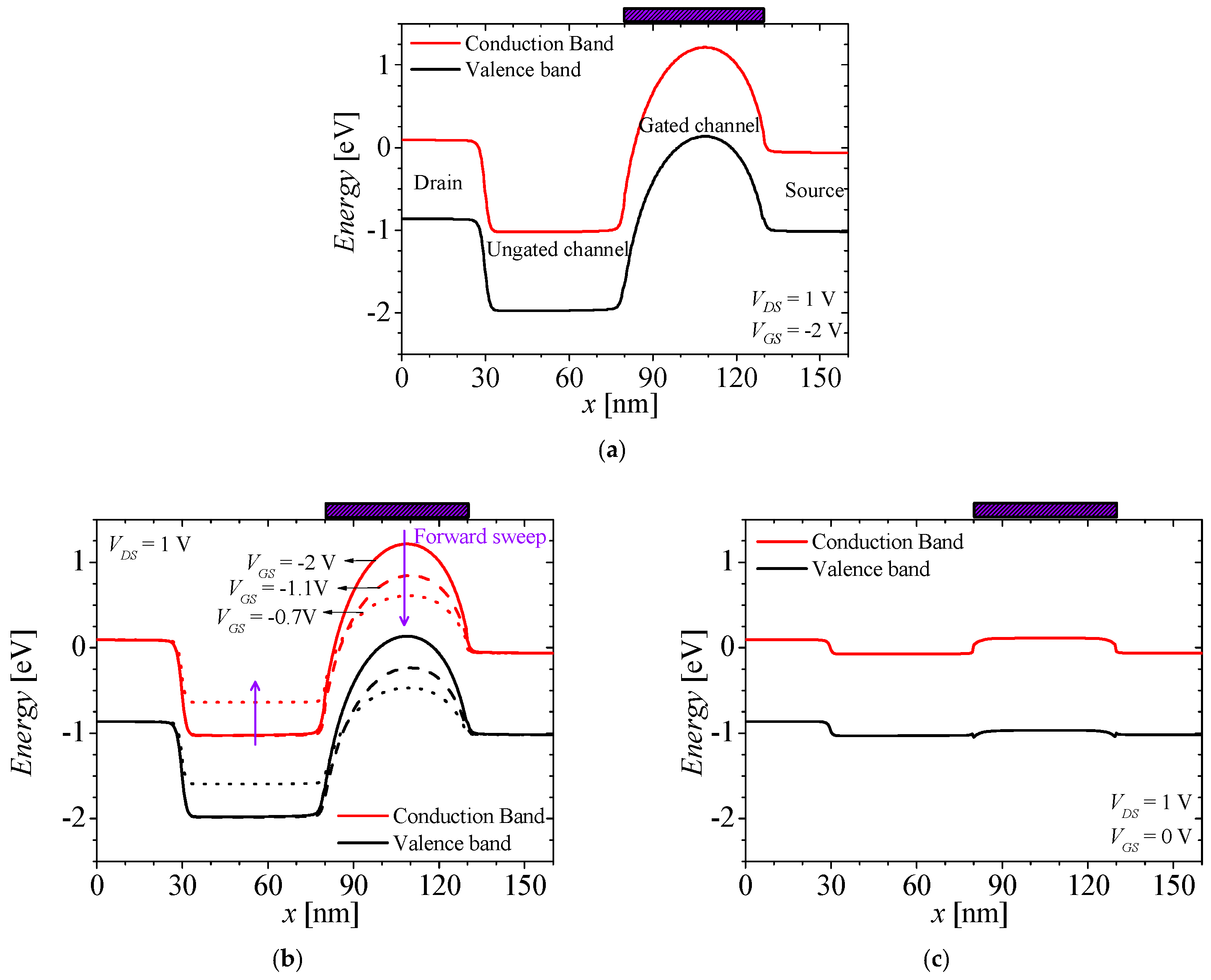

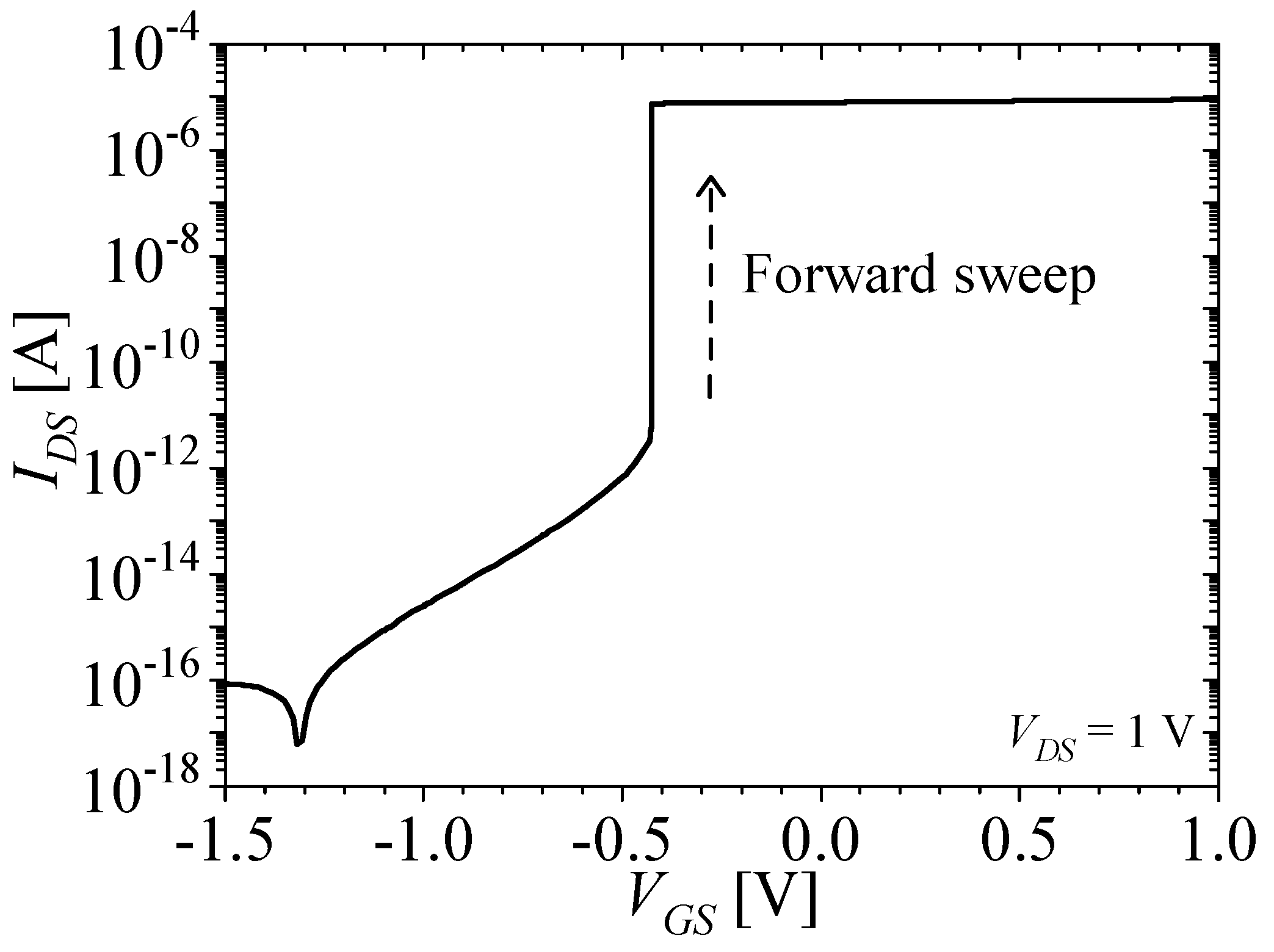

3.1. Mechanism of the M3D-NVM-FBFET

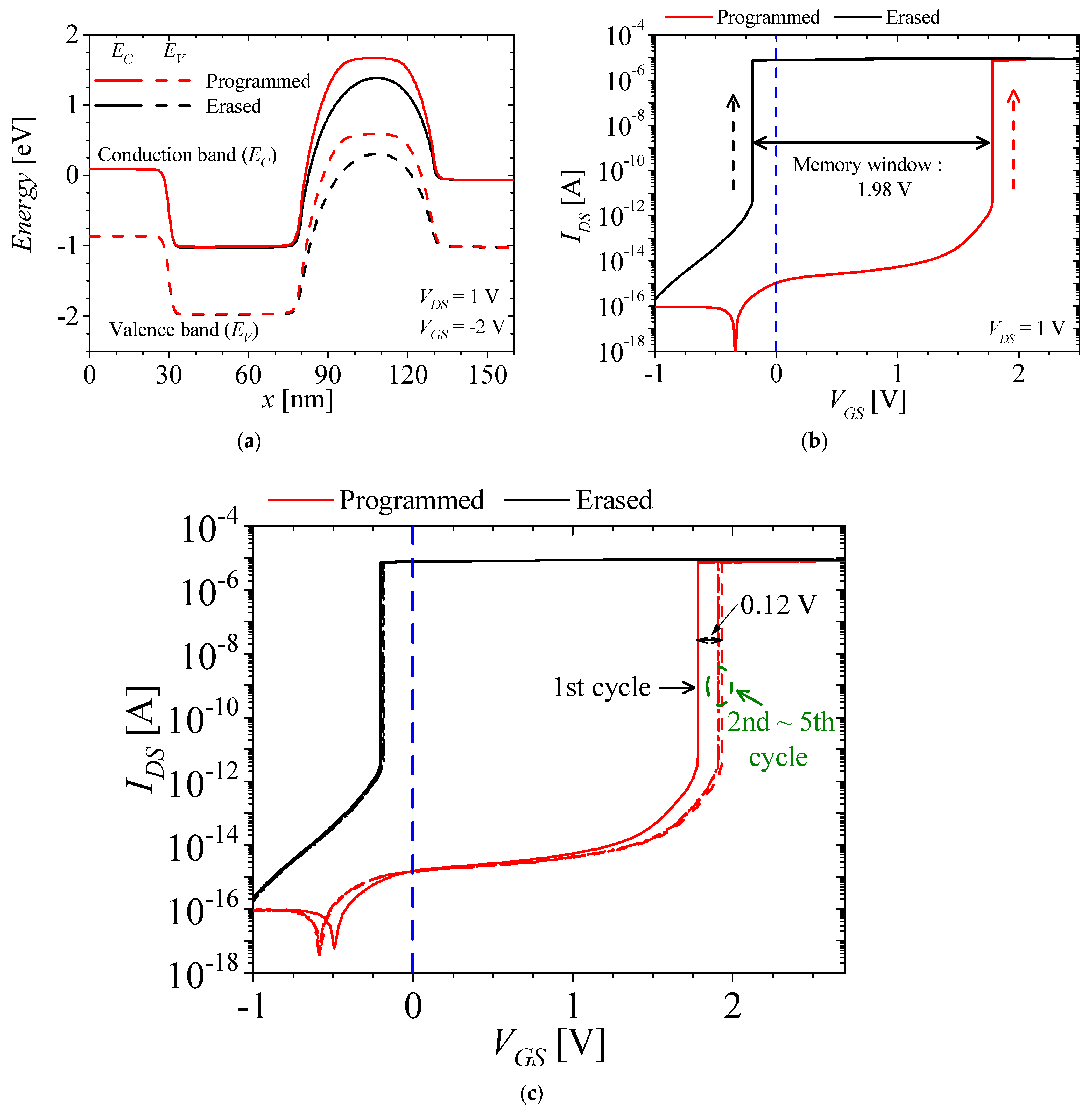

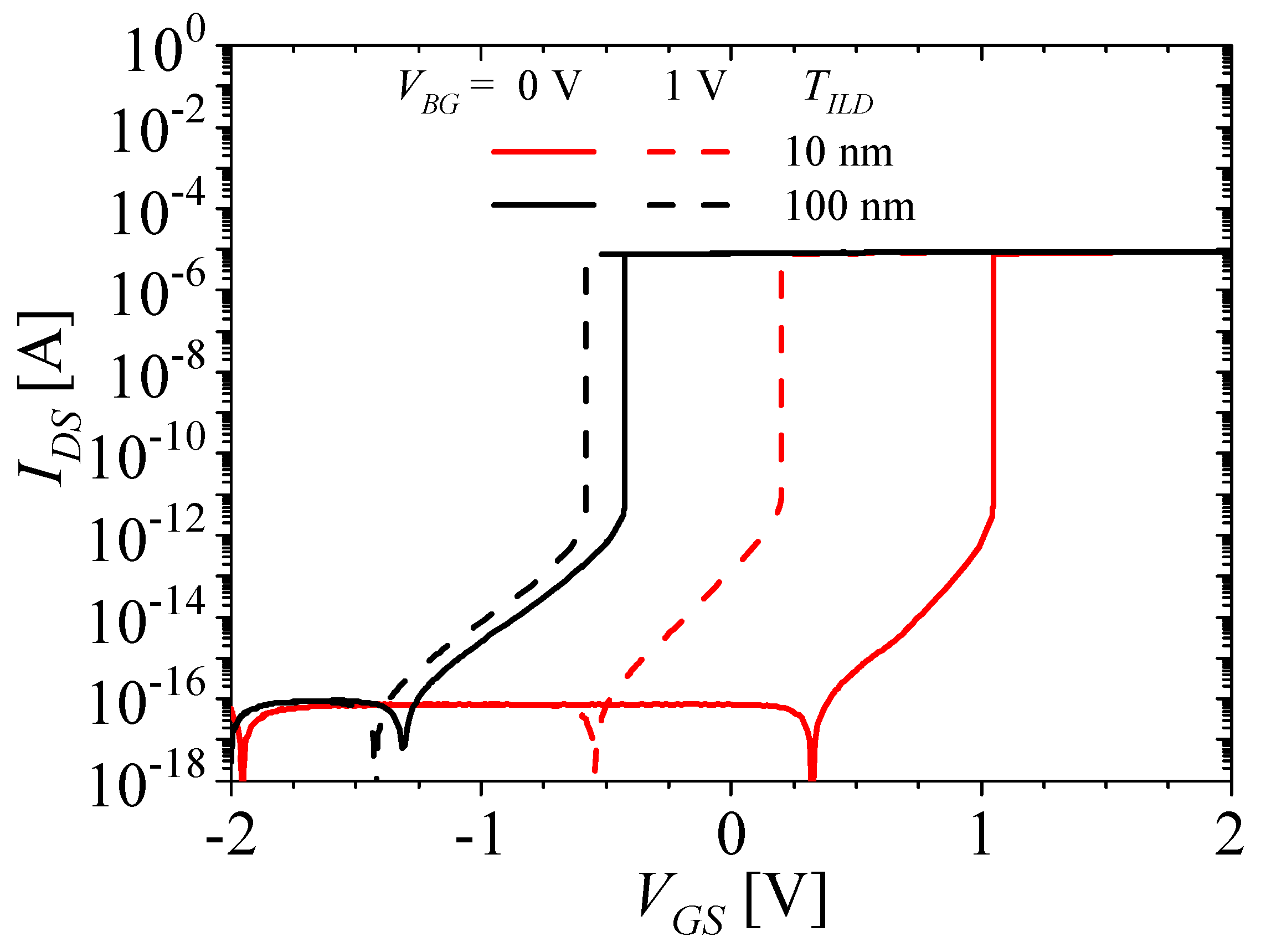

3.2. Memory Characteristics of the M3D-NVM-FBFET

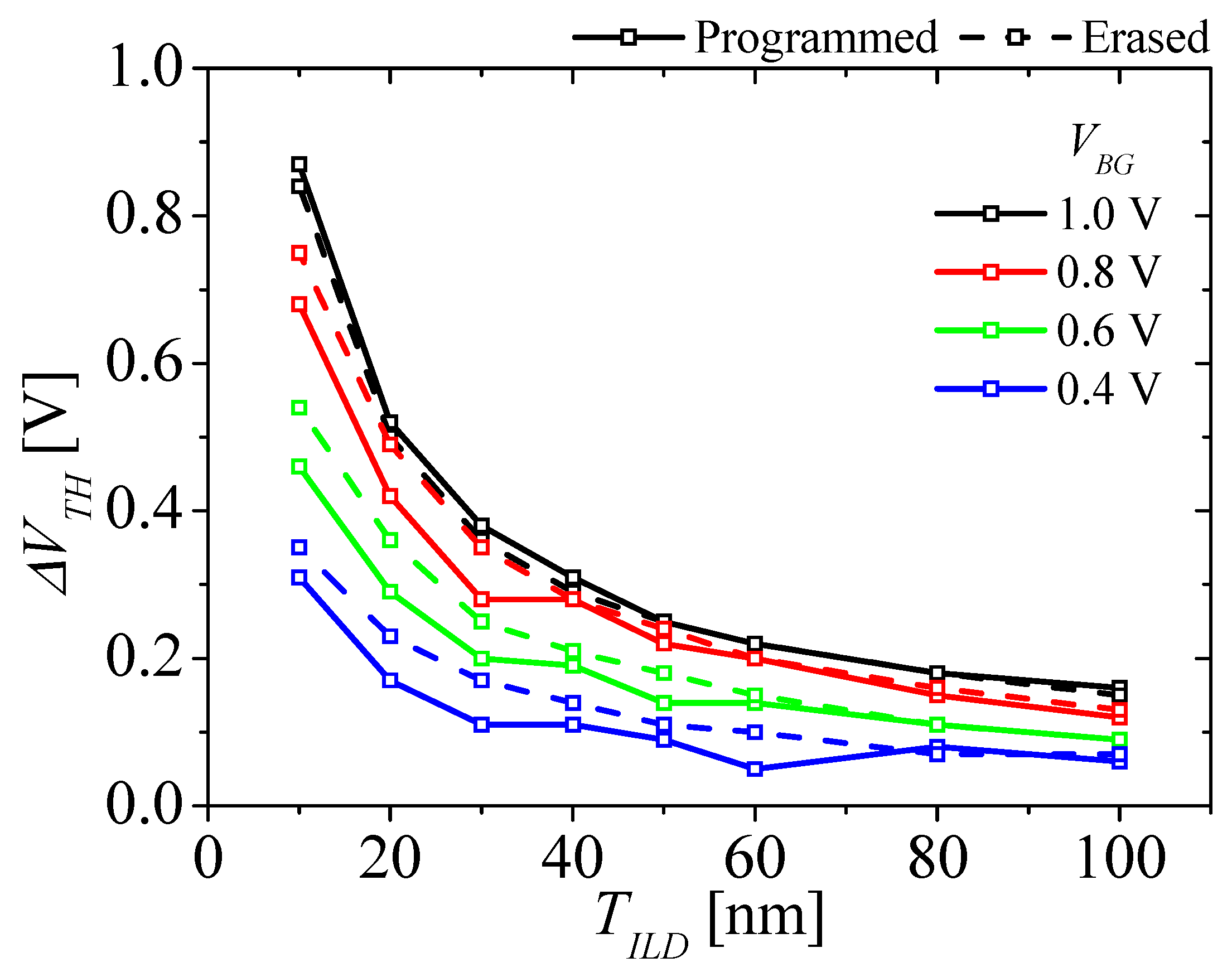

3.3. The Electrical Coupling Effect for the M3D-NVM-FBFET

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Cavin, R.K.; Lugli, P.; Zhirnov, V.V. Science and Engineering Beyond Moore’s Law. Proc. IEEE 2012, 100, 1720–1749. [Google Scholar] [CrossRef]

- Frank, D.J.; Dennard, R.H.; Nowak, E.; Solomon, P.M.; Taur, Y.; Wong, H.-S.P. Device Scaling Limits of Si MOSFETs and Their Application Dependencies. Proc. IEEE 2001, 89, 259–288. [Google Scholar] [CrossRef]

- Clavelier, L.; Deguet, C.; Di Cioccio, L.; Augendre, E.; Brugere, A.; Gueguen, P.; Le Tiec, Y.; Moriceau, H.; Rabarot, M.; Signamarcheix, T.; et al. Engineered Substrates for Future More Moore and More than Moore Integrated Devices. In Proceedings of the 2010 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010; pp. 2.6.1–2.6.4. [Google Scholar]

- Grenouillet, L.; De Salvo, B.; Brunet, L.; Coignus, J.; Tabone, C.; Mazurier, J.; Le Royer, C.; Grosse, P.; Jaud, M.A.; Rivallin, P.; et al. Smart Co-Integration of Light Sensitive Layers with FDSOI Transistors for More than Moore Applications. In Proceedings of the 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–2. [Google Scholar]

- Hisamoto, D.; Lee, W.-C.; Kedzierski, J.; Takeuchi, H.; Asano, K.; Kuo, C.; Anderson, E.; King, T.-J.; Bokor, J.; Hu, C. FinFET-a Self-Aligned Double-Gate MOSFET Scalable to 20 nm. IEEE Trans. Electron Devices 2000, 47, 2320–2325. [Google Scholar]

- Singh, N.; Agarwal, A.; Bera, L.K.; Liow, T.Y.; Yang, R.; Rustagi, S.C.; Tung, C.H.; Kumar, R.; Lo, G.Q.; Balasubramanian, N.; et al. High-Performance Fully Depleted Silicon Nanowire (diameter/spl les/5 nm) Gate-All-around CMOS Devices. IEEE Electron Device Lett. 2006, 27, 383–386. [Google Scholar] [CrossRef]

- Ferhati, H.; Djeffal, F. Planar Junctionless Phototransistor: A Potential High-Performance and Low-Cost Device for Optical-Communications. Opt. Laser Technol. 2017, 97, 29–35. [Google Scholar] [CrossRef]

- Ferhati, H.; Djeffal, F. Boosting the Optical Performance and Commutation Speed of Phototransistor Using SiGe/Si/Ge Tunneling Structure. Mater. Res. Express 2018, 5, 065902. [Google Scholar] [CrossRef]

- Meguellati, M.; Djeffal, F. New Dual-Dielectric Gate All Around (DDGAA) RADFET Dosimeter Design to Improve the Radiation Sensitivity. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrom. Detect. Assoc. Equip. 2012, 683, 24–28. [Google Scholar] [CrossRef]

- Yu, Y.S.; Najam, F. Compact Capacitance Model of L-Shape Tunnel Field-Effect Transistors for Circuit Simulation. J. Inf. Commun. Converg. Eng. 2021, 19, 263–268. [Google Scholar]

- Wong, S.; El-Gamal, A.; Griffin, P.; Nishi, Y.; Pease, F.; Plummer, J. Monolithic 3D Integrated Circuits. In Proceedings of the 2007 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), Hsinchu, Taiwan, 23–25 April 2007; pp. 1–4. [Google Scholar]

- Vinet, M.; Batude, P.; Fenouillet-Beranger, C.; Clermidy, F.; Brunet, L.; Rozeau, O.; Hartmannn, J.; Billoint, O.; Cibrario, G.; Previtali, B.; et al. Monolithic 3D Integration: A Powerful Alternative to Classical 2D Scaling. In Proceedings of the 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–3. [Google Scholar]

- Batude, P.; Vinet, M.; Pouydebasque, A.; Le Royer, C.; Previtali, B.; Tabone, C.; Hartmann, J.-M.; Sanchez, L.; Baud, L.; Carron, V.; et al. 3D Monolithic Integration. In Proceedings of the 2011 IEEE International Symposium of Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 2233–2236. [Google Scholar]

- Bishop, M.D.; Wong, H.-S.P.; Mitra, S.; Shulaker, M.M. Monolithic 3-D Integration. IEEE Micro 2019, 39, 16–27. [Google Scholar] [CrossRef]

- Lee, G.J.; Ahn, T.J.; Lim, S.K.; Yu, Y.S. Investigation into electrical characteristics of logic circuit consisting of modularized mon-olithic 3D inverter unit cell. J. Inf. Commun. Converg. Eng. 2022, 20, 137–142. [Google Scholar]

- Nayak, D.K.; Banna, S.; Samal, S.K.; Lim, S.K. Power, Performance, and Cost Comparisons of Monolithic 3D ICs and TSV-Based 3D ICs. In Proceedings of the 2015 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Rohnert Park, CA, USA, 5–8 October 2015; pp. 1–2. [Google Scholar]

- Ebrahimi, M.S.; Hills, G.; Sabry, M.M.; Shulaker, M.M.; Wei, H.; Wu, T.F.; Mitra, S.; Wong, H.-S.P. Monolithic 3D Integration Advances and Challenges: From Technology to System Levels. In Proceedings of the 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–2. [Google Scholar]

- Lee, S.-Y.; Park, J. Architecture of 3D Memory Cell Array on 3D IC. In Proceedings of the 2012 4th IEEE International Memory Workshop, Milan, Italy, 20–23 May 2013; pp. 1–3. [Google Scholar]

- Lee, S.-Y.; Schroder, D.K. 3D IC Architecture for High Density Memories. In Proceedings of the 2010 IEEE International Memory Workshop, Seoul, Republic of Korea, 16–19 May 2010; pp. 1–6. [Google Scholar]

- Padilla, A.; Yeung, C.W.; Shin, C.; Hu, C.; King Liu, T.-J. Feedback FET: A Novel Transistor Exhibiting Steep Switching Behavior at Low Bias Voltages. In Proceedings of the 2008 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Dirani, H.E.; Solaro, Y.; Fonteneau, P.; Ferrari, P.; Cristoloveanu, S. Sharp-Switching Z2-FET Device in 14 nm FDSOI Technology. In Proceedings of the 2015 45th European Solid State Device Research Conference (ESSDERC), Graz, Austria, 14–18 September 2015; pp. 250–253. [Google Scholar]

- Lee, K.H.; Dirani, H.E.; Fonteneau, P.; Bawedin, M.; Sato, S.; Cristoloveanu, S. Sharp Switching, Hysteresis-Free Characteristics of Z2-FET for Fast Logic Applications. In Proceedings of the 2018 48th European Solid-State Device Research Conference (ESSDERC), Dresden, Germany, 3–6 September 2018; pp. 74–77. [Google Scholar]

- Kwon, M.-W.; Hwang, S.; Baek, M.-H.; Cho, S.; Park, B.-G. Dual Gate Positive Feedback Field-Effect Transistor for Low Power Analog Circuit. In Proceedings of the 2017 Silicon Nanoelectronics Workshop (SNW), Kyoto, Japan, 4–5 June 2017; pp. 115–116. [Google Scholar]

- Lee, C.; Ko, E.; Shin, C. Steep Slope Silicon-On-Insulator Feedback Field-Effect Transistor: Design and Performance Analysis. IEEE Trans. Electron Devices 2019, 66, 286–291. [Google Scholar] [CrossRef]

- Suddarsi, S.K.; Dhanaraj, K.J.; Saramekala, G.K. Investigation of Switching and Inverter Characteristics of Recessed-Source/Drain (Re–S/D) Silicon-on-Insulator (SOI) Feedback Field Effect Transistor (FBFET). Microelectron. J. 2023, 138, 105855. [Google Scholar] [CrossRef]

- Cho, J.; Lim, D.; Woo, S.; Cho, K.; Kim, S. Static Random Access Memory Characteristics of Single-Gated Feedback Field-Effect Transistors. IEEE Trans. Electron Devices 2019, 66, 413–419. [Google Scholar] [CrossRef]

- Woo, S.; Cho, J.; Lim, D.; Cho, K.; Kim, S. Transposable 3T-SRAM Synaptic Array Using Independent Double-Gate Feedback Field-Effect Transistors. IEEE Trans. Electron Devices 2019, 66, 4753–4758. [Google Scholar] [CrossRef]

- Parihar, M.S.; Lee, K.H.; El Dirani, H.; Navarro, C.; Lacord, J.; Martinie, S.; Barbe, J.-C.; Fonteneau, P.; Galy, P.; Le Royer, C.; et al. Low-Power Z2-FET Capacitorless 1T-DRAM. In Proceedings of the 2017 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; pp. 1–4. [Google Scholar]

- Kwon, M.-W.; Park, K.; Baek, M.-H.; Lee, J.; Park, B.-G. A Low-Energy High-Density Capacitor-Less I&F Neuron Circuit Using Feedback FET Co-Integrated with CMOS. IEEE J. Electron Devices Soc. 2019, 7, 1080–1084. [Google Scholar]

- Woo, S.; Cho, J.; Lim, D.; Park, Y.-S.; Cho, K.; Kim, S. Implementation and Characterization of an Integrate-and-Fire Neuron Circuit Using a Silicon Nanowire Feedback Field-Effect Transistor. IEEE Trans. Electron Devices 2020, 67, 2995–3000. [Google Scholar] [CrossRef]

- Kang, H.; Cho, J.; Kim, Y.; Lim, D.; Woo, S.; Cho, K.; Kim, S. Nonvolatile and Volatile Memory Characteristics of a Silicon Nanowire Feedback Field-Effect Transistor with a Nitride Charge-Storage Layer. IEEE Trans. Electron Devices 2019, 66, 3342–3348. [Google Scholar] [CrossRef]

- Spessot, A.; Oh, H. 1T-1C Dynamic Random Access Memory Status, Challenges, and Prospects. IEEE Trans. Electron Devices 2020, 67, 1382–1393. [Google Scholar] [CrossRef]

- Lee, J.C.; Kim, J.; Kim, K.W.; Ku, Y.J.; Kim, D.S.; Jeong, C.; Yun, T.S.; Kim, H.; Cho, H.S.; Oh, S.; et al. High Bandwidth Memory (HBM) with TSV Technique. In Proceedings of the 2016 International SoC Design Conference (ISOCC), Jeju, Republic of Korea, 23–26 October 2016; pp. 181–182. [Google Scholar]

- Yu, Y.S.; Panth, S.; Lim, S.K. Electrical Coupling of Monolithic 3-D Inverters. IEEE Trans. Electron Devices 2016, 63, 3346–3349. [Google Scholar] [CrossRef]

- Ahn, T.J.; Perumal, R.; Lim, S.K.; Yu, Y.S. Parameter Extraction and Power/Performance Analysis of Monolithic 3-D Inverter (M3INV). IEEE Trans. Electron Devices 2019, 66, 1006–1011. [Google Scholar] [CrossRef]

- Ahn, T.-J.; Yu, Y.S.; Kim, N.H. Comparison of Two-Types of Monolithic 3D Inverter Consisting of MOSFETs and Junctionless FETs. In Proceedings of the 2020 International Conference on Electronics, Information, and Communication (ICEIC), Barcelona, Spain, 19–22 January 2020; pp. 1–3. [Google Scholar]

- Ahn, T.J.; Yu, Y.S. Circuit Simulation Considering Electrical Coupling in Monolithic 3D Logics with Junctionless FETs. Micromachines 2020, 11, 887. [Google Scholar] [CrossRef] [PubMed]

- Oh, J.H.; Yu, Y.S. Investigation of Monolithic 3D Integrated Circuit Inverter with Feedback Field Effect Transistors Using TCAD Simulation. Micromachines 2020, 11, 852. [Google Scholar] [CrossRef] [PubMed]

- Oh, J.H.; Yu, Y.S. A Monolithic 3-Dimensional Static Random Access Memory Containing a Feedback Field Effect Transistor. Micromachines 2022, 13, 1625. [Google Scholar] [CrossRef]

- Hwang, J.-R.; Lee, T.-L.; Ma, H.-C.; Lee, T.-C.; Chung, T.-H.; Chang, C.-Y.; Liu, S.-D.; Perng, B.-C.; Hsu, J.-W.; Lee, M.-Y.; et al. 20nm Gate Bulk-finFET SONOS Flash. In Proceedings of the IEEE International Electron Devices Meeting, 2005, IEDM Technical Digest, Washington, DC, USA, 5 December 2005; pp. 154–157. [Google Scholar]

- Silvaco Int. ATLAS Ver. 5. 32. 1. R Manual; Silvaco Int.: Santa Clara, CA, USA, 2022. [Google Scholar]

- Nowak, E.; Hubert, A.; Perniola, L.; Ernst, T.; Ghibaudo, G.; Reimbold, G.; De Salvo, B.; Boulanger, F. In-Depth Analysis of 3D Silicon Nanowire SONOS Memory Characteristics by TCAD Simulations. In Proceeding of the 2010 IEEE International Memory Workshop, Seoul, Republic of Korea, 16–19 May 2010; pp. 1–4. [Google Scholar]

- Paul, A.; Sridhar, C.; Gedam, S.; Mahapatra, S. Comprehensive Simulation of Program, Erase and Retention in Charge Trapping Flash Memories. In Proceedings of the 2006 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar]

- Bachhofer, H.; Reisinger, H.; Bertagnolli, E.; von Philipsborn, H. Transient Conduction in Multidielectric Silicon–Oxide–Nitride–Oxide Semiconductor Structures. J. Appl. Phys. 2001, 89, 2791–2800. [Google Scholar] [CrossRef]

- Vianello, E.; Driussi, F.; Arreghini, A.; Palestri, P.; Esseni, D.; Selmi, L.; Akil, N.; van Duuren, M.J.; Golubovic, D.S. Experimental and Simulation Analysis of Program/Retention Transients in Silicon Nitride-Based NVM Cells. IEEE Trans. Electron Devices 2009, 56, 1980–1990. [Google Scholar] [CrossRef]

- Bentrcia, T.; Djeffal, F.; Benhaya, A.H. Continuous Analytic I-V Model for GS DG MOSFETs Including Hot-Carrier Degradation Effects. J. Semicond. 2012, 33, 014001. [Google Scholar] [CrossRef]

- Djeffal, F.; Bentrcia, T.; Abdi, M.A.; Bendib, T. Drain Current Model for Undoped Gate Stack Double Gate (GSDG) MOSFETs Including the Hot-Carrier Degradation Effects. Microelectron. Reliab. 2011, 51, 550–555. [Google Scholar] [CrossRef]

- ITRS. 2013. Available online: http://www.itrs2.net/2013-itrs.html (accessed on 1 September 2023).

- Han, S.; Kim, Y.; Son, D.; Baac, H.W.; Won, S.M.; Shin, C. Study on Memory Characteristics of Fin-Shaped Feedback Field Effect Transistor. Semicond. Sci. Technol. 2022, 37, 065006. [Google Scholar] [CrossRef]

- Ernst, T.; Cristoloveanu, S.; Ghibaudo, G.; Ouisse, T.; Horiguchi, S.; Ono, Y.; Takahashi, Y.; Murase, K. Ultimately Thin Double-Gate SOI MOSFETs. IEEE Trans. Electron Devices 2003, 50, 830–838. [Google Scholar] [CrossRef]

| Parameters | Description | Value/Unit |

|---|---|---|

| Ldrain, Lsource | Length of the drain and source regions | 30 nm |

| Lugch | Length of the ungated channel region | 50 nm |

| Lgch | Length of the gated channel region | 50 nm |

| Tblocking | Thickness of the blocking oxide layer (Al2O3) | 6 nm |

| Tnitride | Thickness of the nitride layer (Si3N4) | 5 nm |

| Ttunneling | Thickness of the tunneling oxide layer (SiO2) | 4 nm |

| Tsi | Thickness of the silicon body | 6 nm |

| TILD | Thickness of the interlayer dielectric (ILD) | Var. |

| Ndrain, Nsource | Doping concentration of the drain and source regions | 1 × 1020 cm−3 |

| Nugch | Doping concentration of the ungated channel region | 1 × 1020 cm−3 |

| Ngch | Doping concentration of the gated channel region | 1 × 1015 cm−3 |

| ΦFBFET | Work function of the gate metal | 5.3 eV |

| Parameter | Value/Unit |

|---|---|

| Trap energy level | 1.2 eV |

| Effective mass electron, me* | 0.33 m0 |

| Effective mass hole, mh* | 0.46 m0 |

| Capture cross-section | 1 × 10−13 cm2 |

| Trap density | 1 × 1020 cm−3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Oh, J.H.; Yu, Y.S. Investigation of the Electrical Coupling Effect for Monolithic 3-Dimensional Nonvolatile Memory Consisting of a Feedback Field-Effect Transistor Using TCAD. Micromachines 2023, 14, 1822. https://doi.org/10.3390/mi14101822

Oh JH, Yu YS. Investigation of the Electrical Coupling Effect for Monolithic 3-Dimensional Nonvolatile Memory Consisting of a Feedback Field-Effect Transistor Using TCAD. Micromachines. 2023; 14(10):1822. https://doi.org/10.3390/mi14101822

Chicago/Turabian StyleOh, Jong Hyeok, and Yun Seop Yu. 2023. "Investigation of the Electrical Coupling Effect for Monolithic 3-Dimensional Nonvolatile Memory Consisting of a Feedback Field-Effect Transistor Using TCAD" Micromachines 14, no. 10: 1822. https://doi.org/10.3390/mi14101822