Fabrication of Substrate-Integrated Waveguide Using Micromachining of Photoetchable Glass Substrate for 5G Millimeter-Wave Applications

Abstract

:1. Introduction

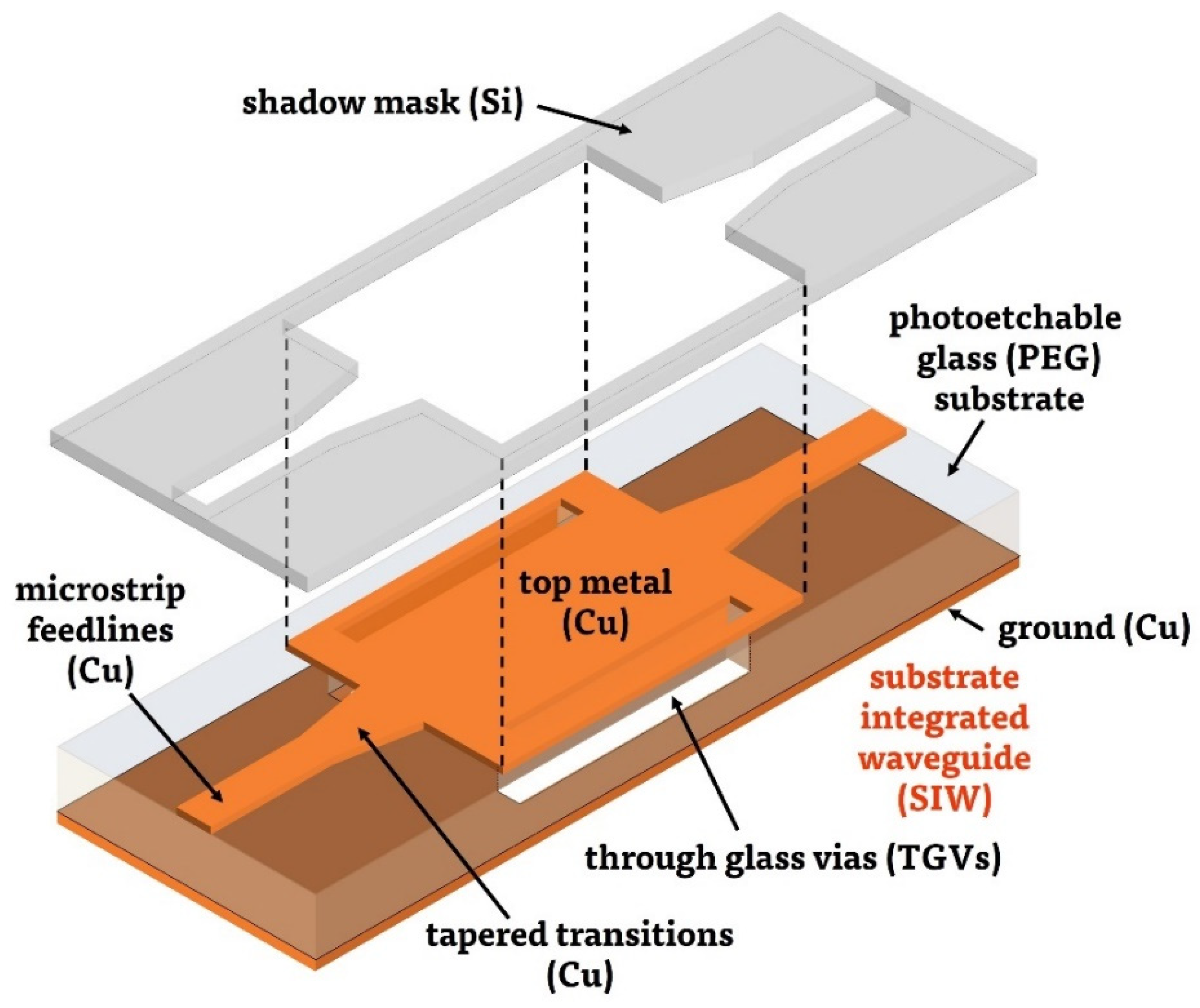

2. Design and Simulation

2.1. Dielectric Properties of PEG Substrate

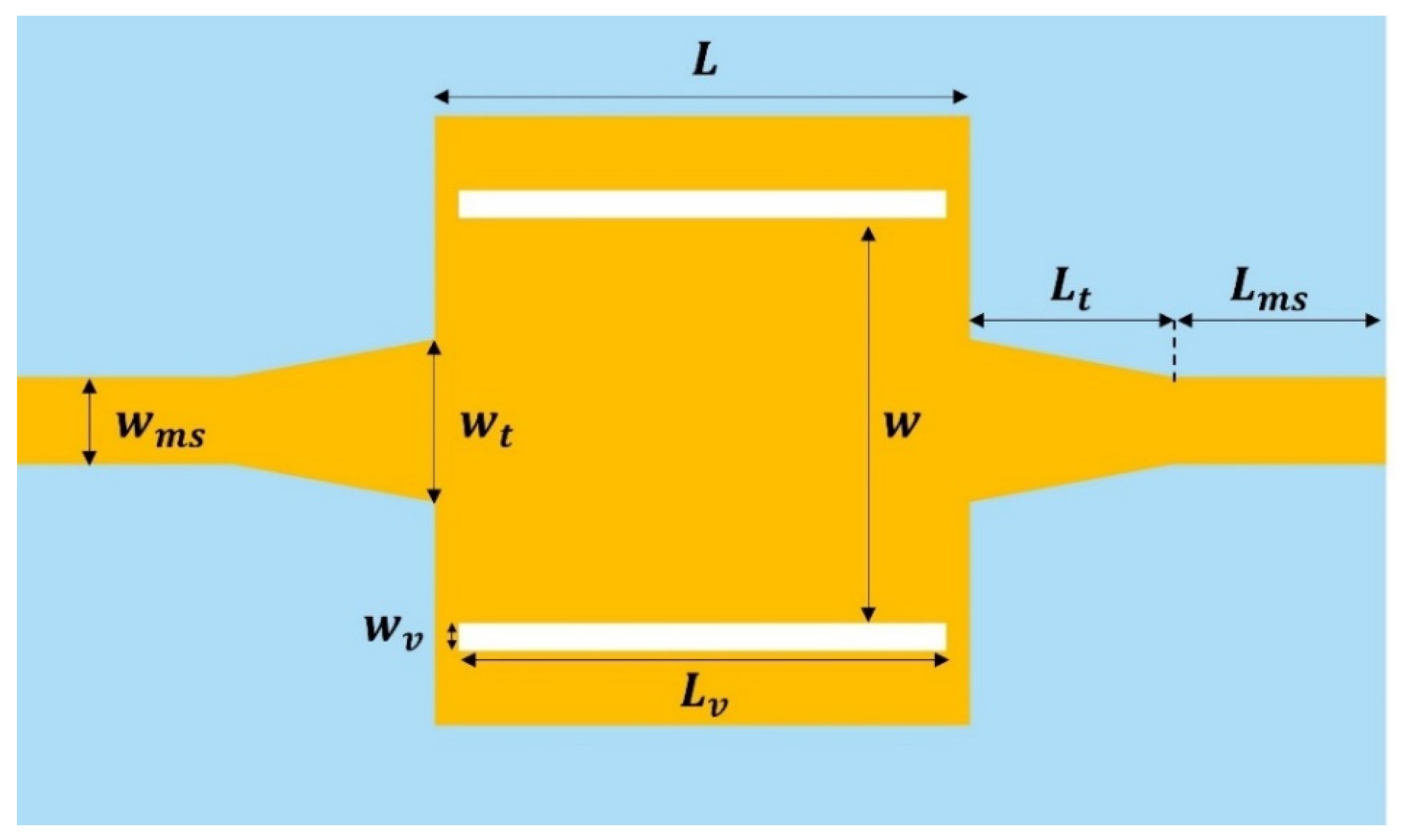

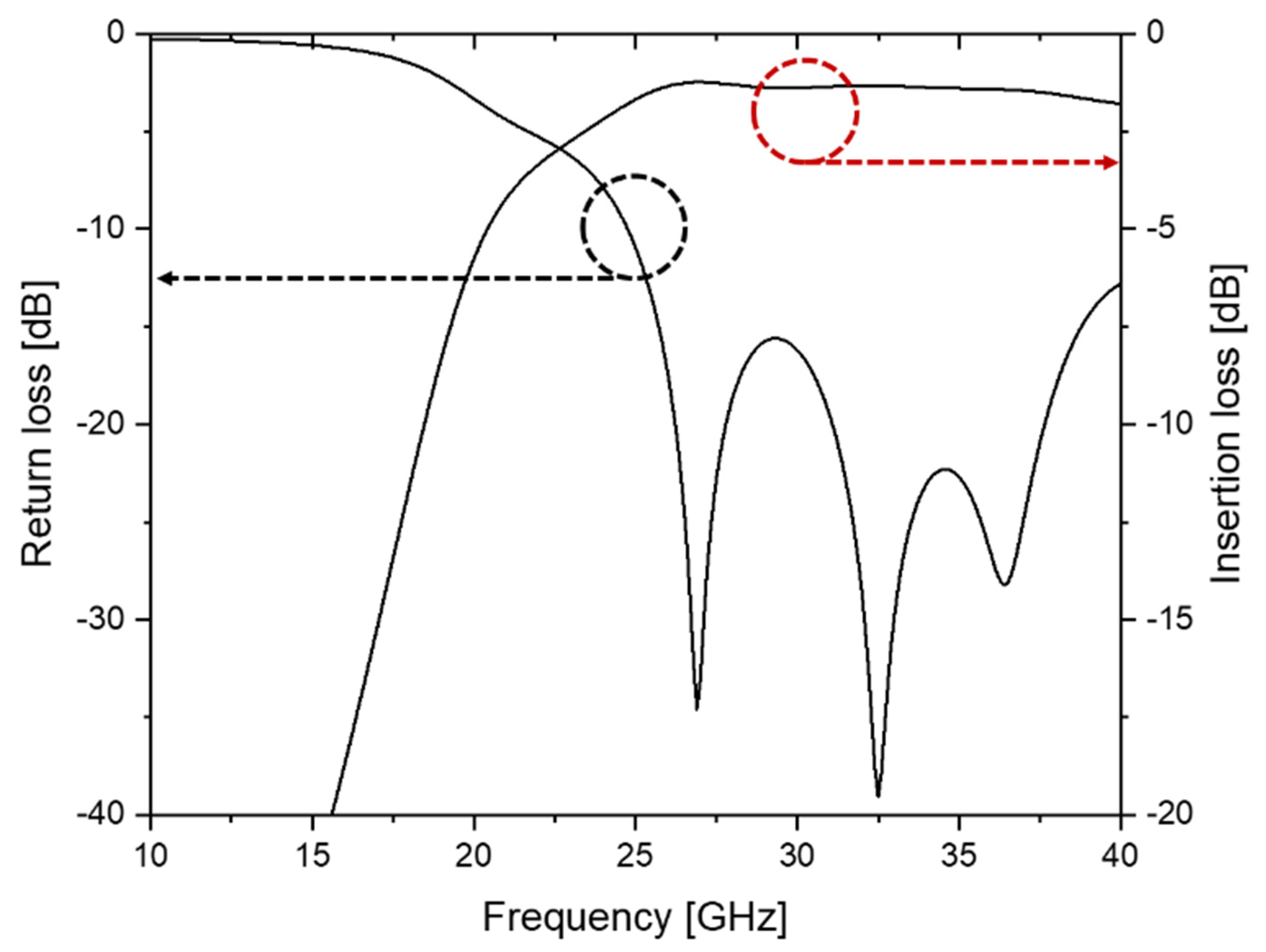

2.2. Design and Simulation of SIW

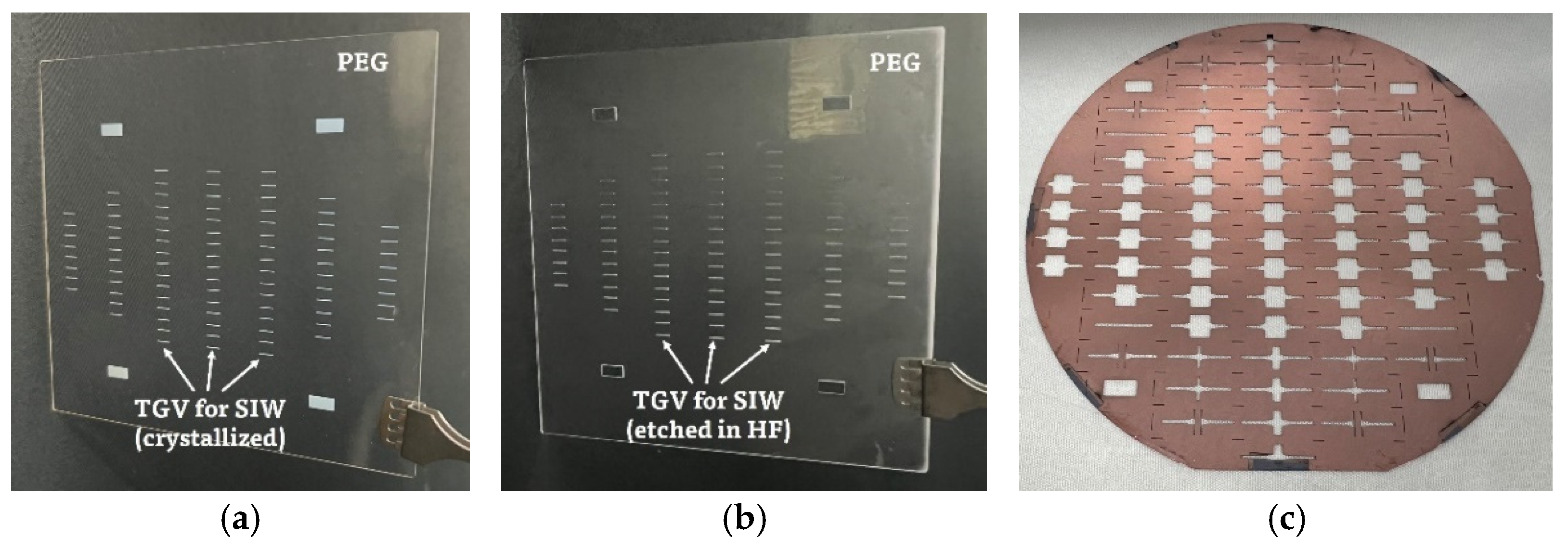

3. Fabrication Process

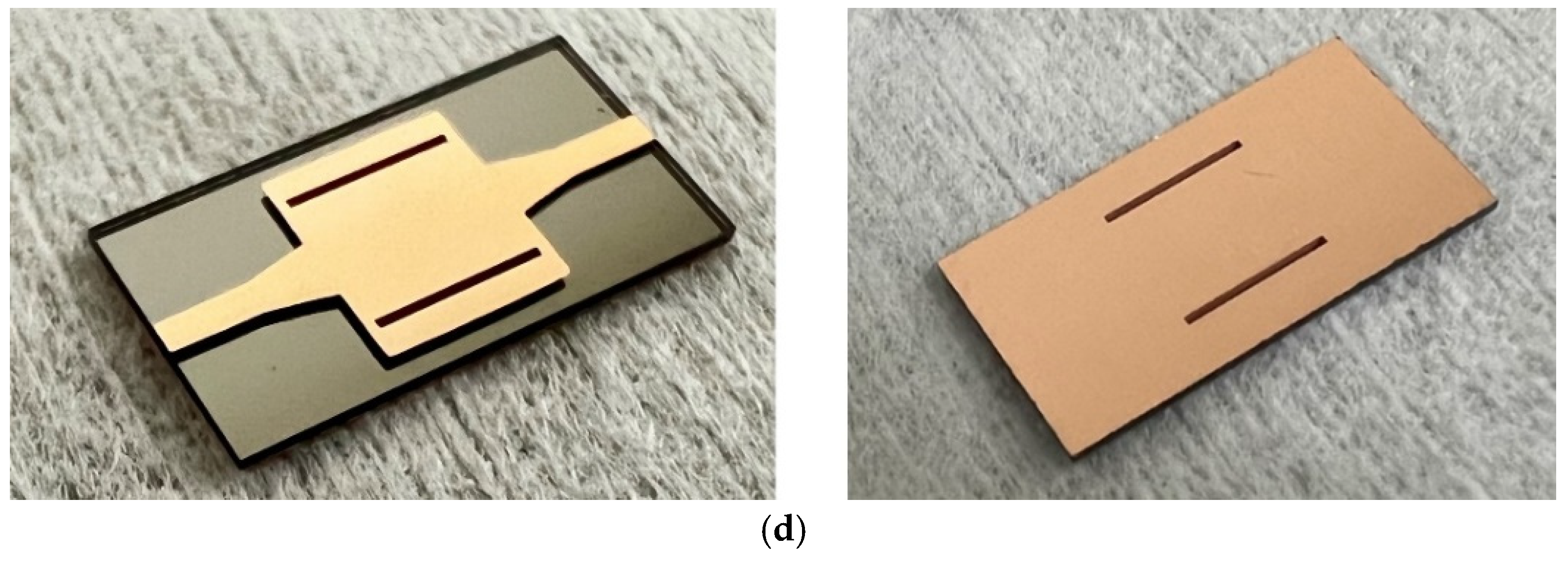

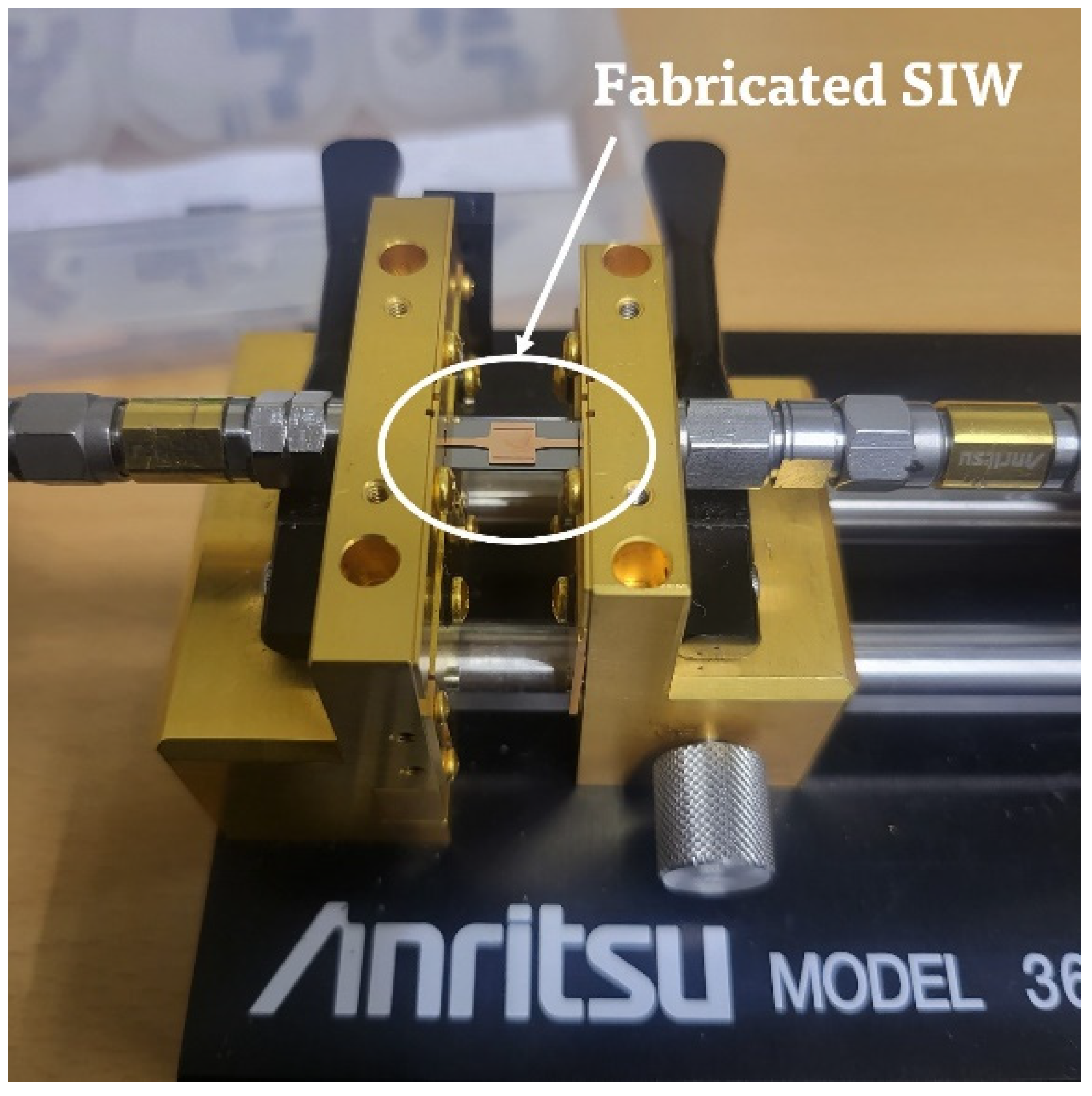

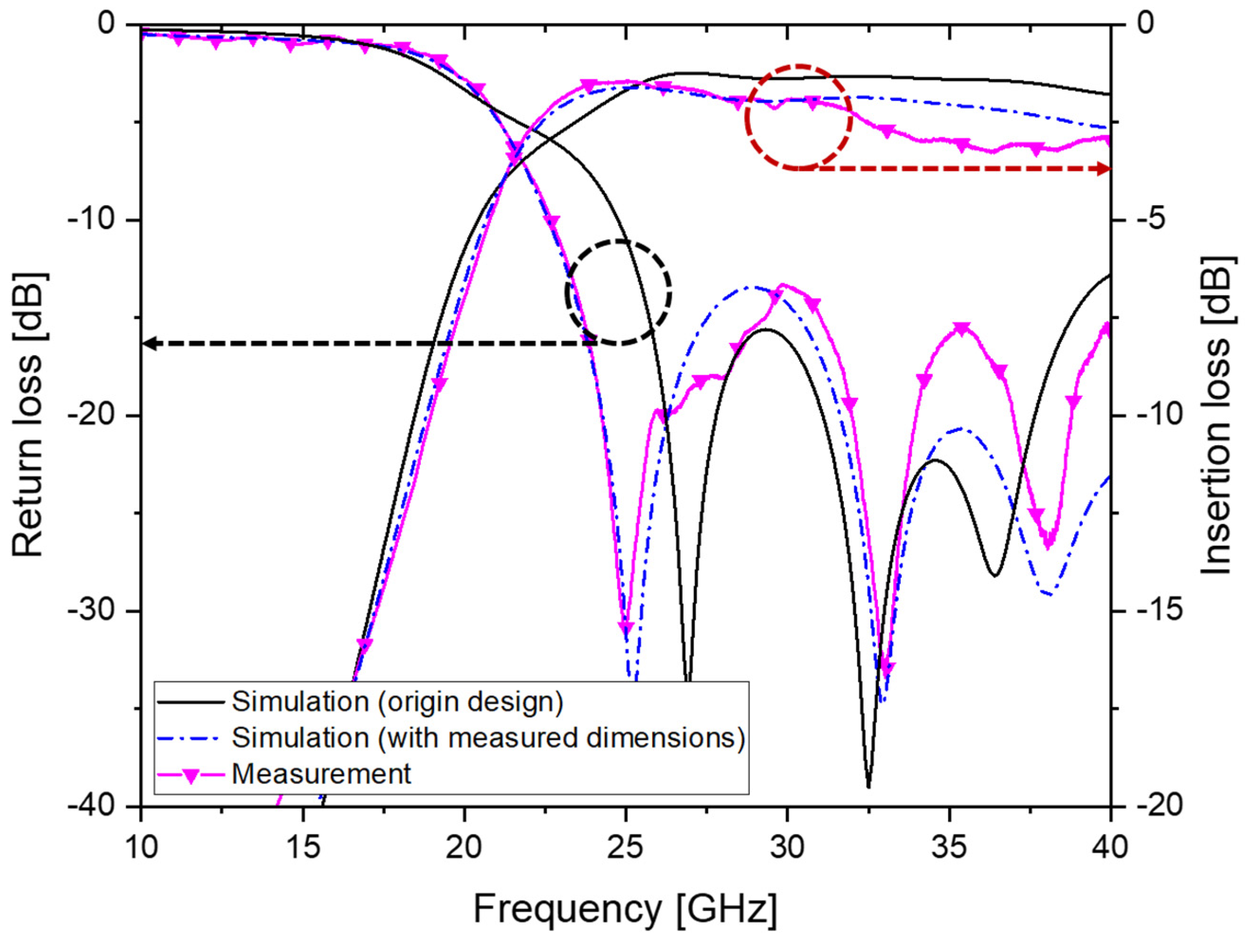

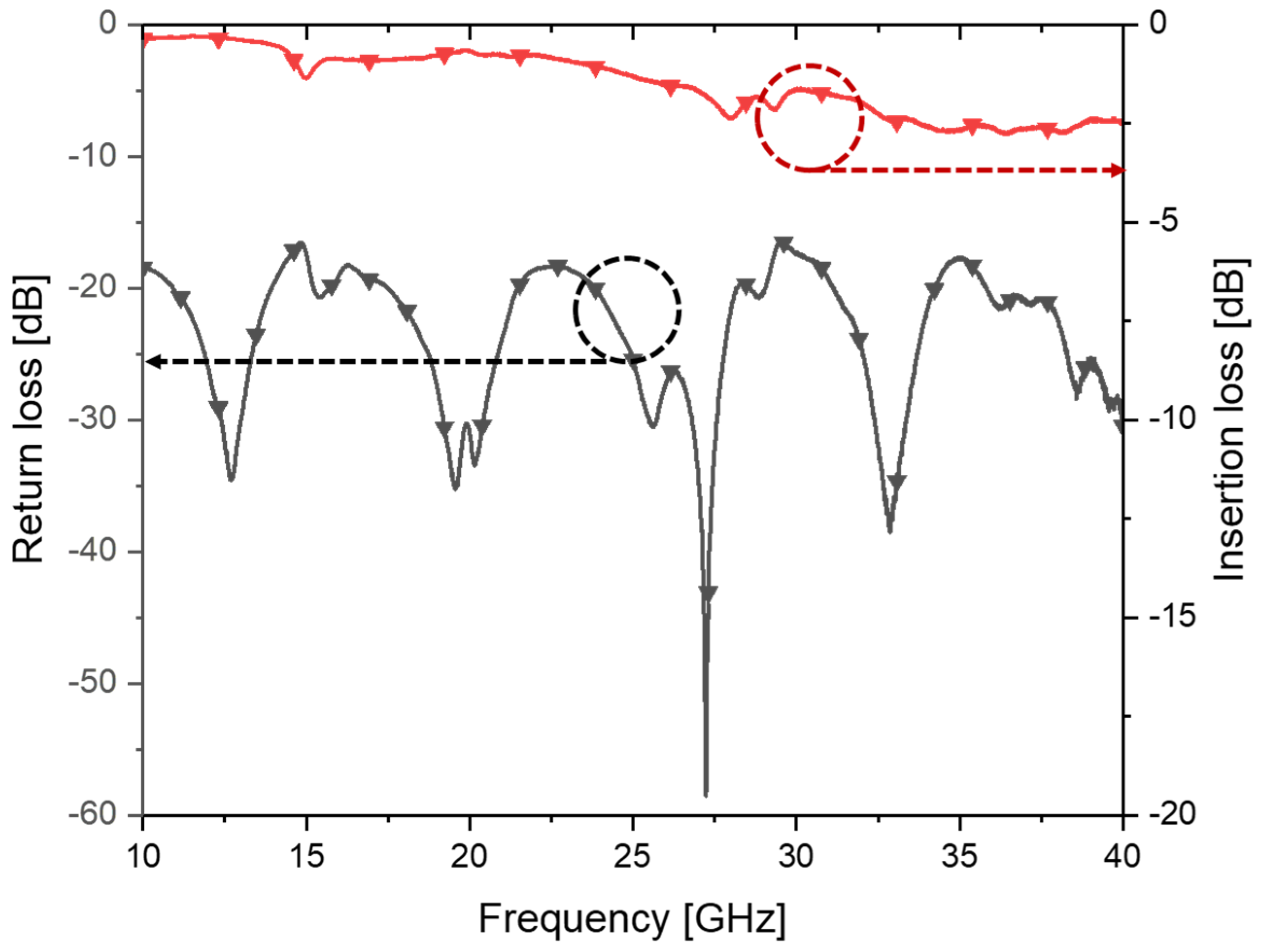

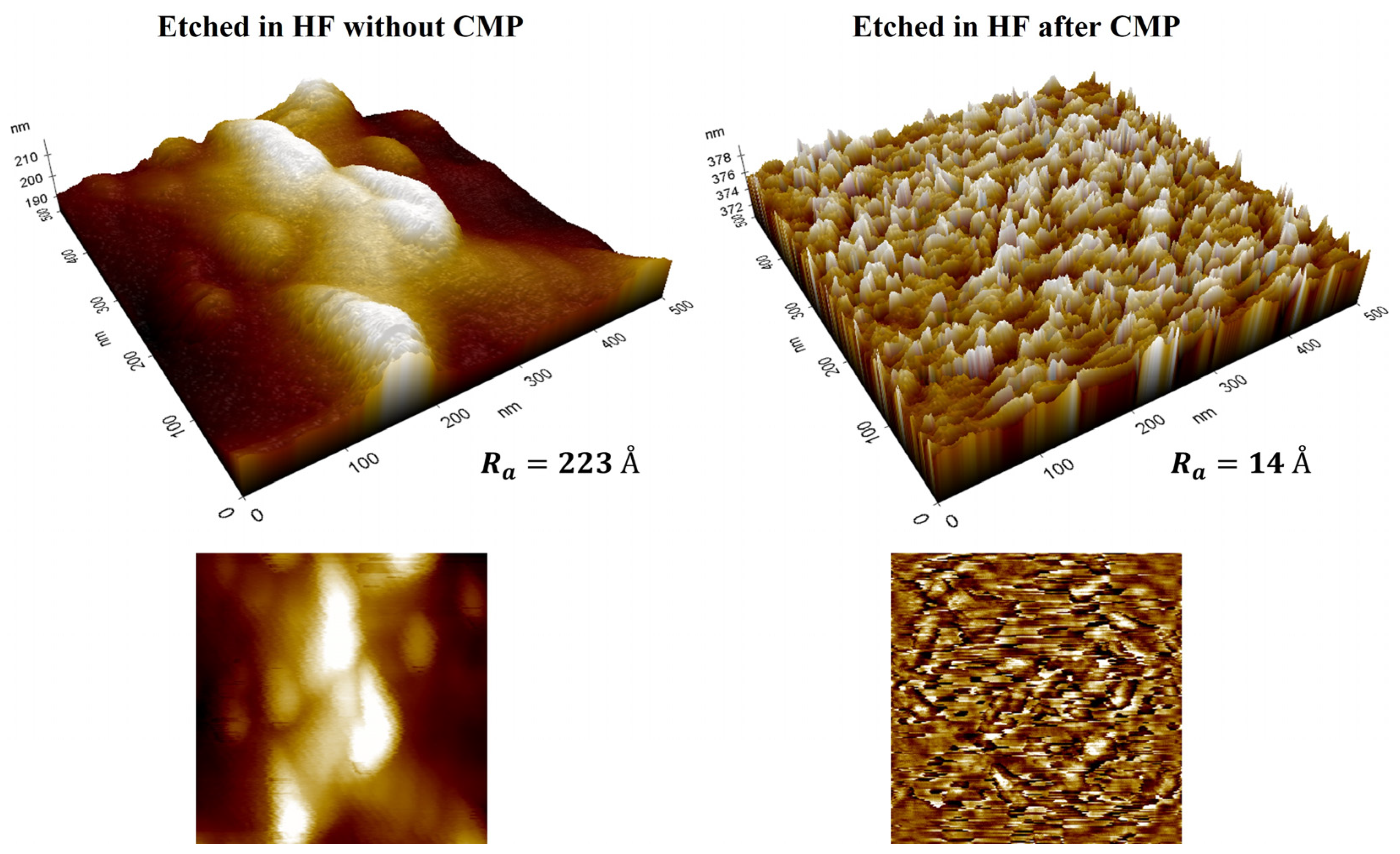

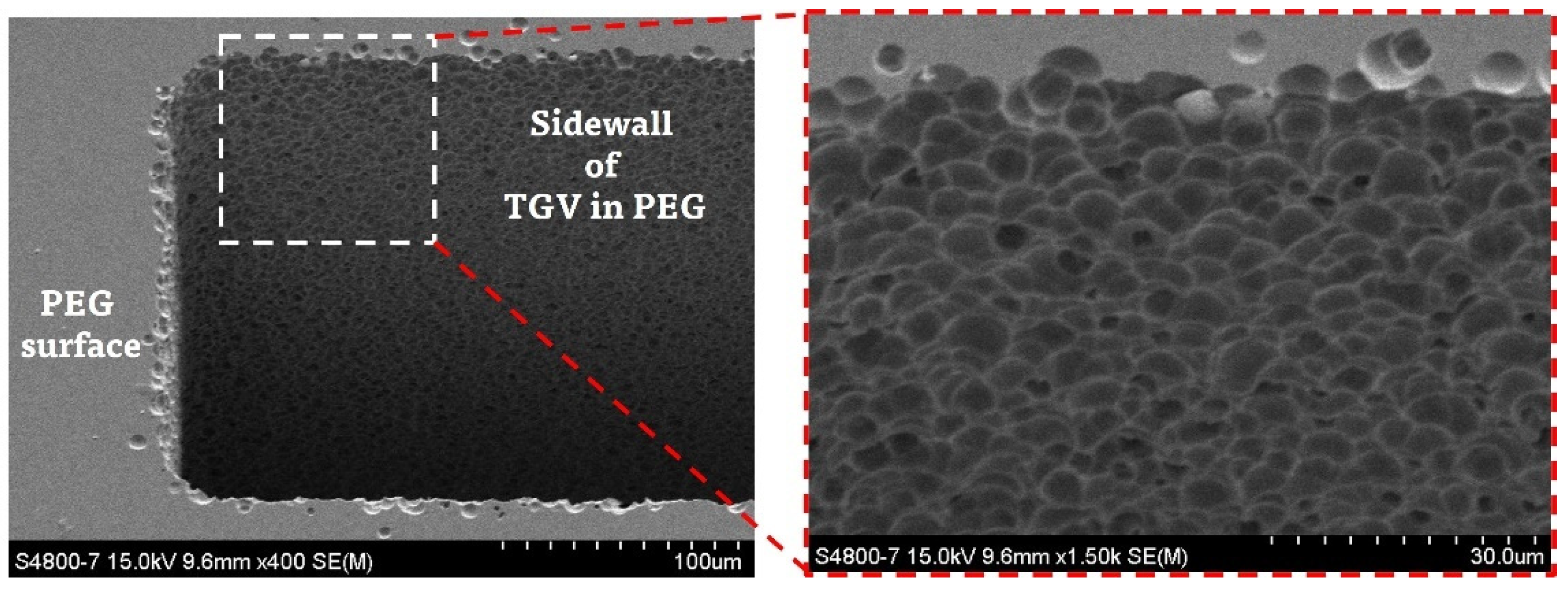

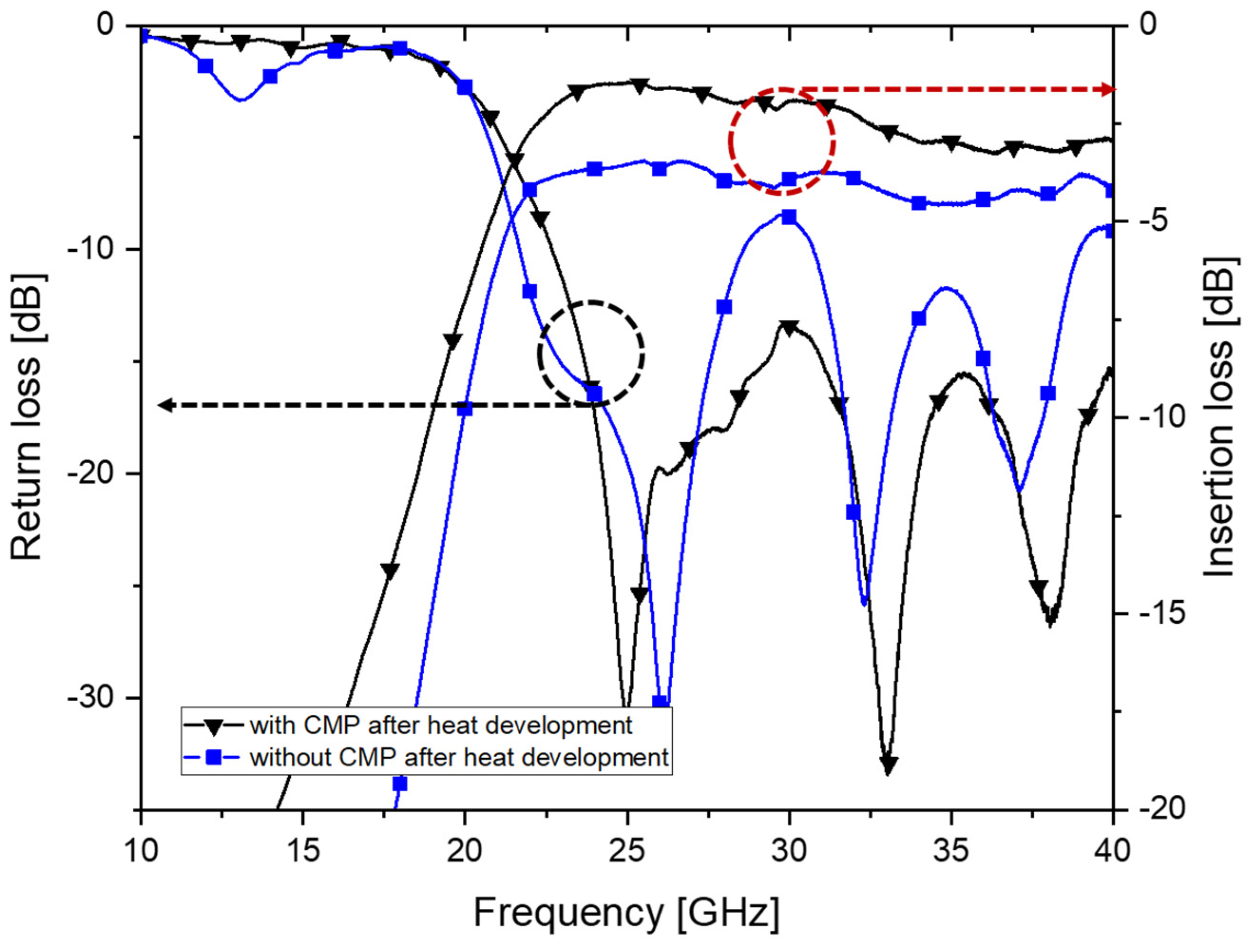

4. Experimental Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Nishio, T. Electronic packaging gears up for 5G mobile race. In Proceedings of the 2017 International Conference on Electronics Packaging (ICEP), Yamagata, Japan, 19–22 April 2017; pp. 328–332. [Google Scholar]

- Watanabe, A.O.; Ali, M.; Sayeed, S.Y.B.; Tummala, R.R.; Pulugurtha, M.R. A review of 5G front-end systems package integration. IEEE Trans. Compon. Packag. Technol. 2021, 11, 118–133. [Google Scholar] [CrossRef]

- Yu, C.H.; Yen, L.J.; Hsieh, C.Y.; Hsieh, J.S.; Chang, V.C.Y.; Hsieh, C.H.; Liu, C.S.; Wang, C.T.; Yee, K.C.; Yu, D.C.H. High performance, high density RDL for advanced packaging. In Proceedings of the IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2018; pp. 587–593. [Google Scholar]

- Ravichandran, S.; Huang, K.-Q.; Rehman, M.u.; Erdogan, S.; Watanabe, A.; Nedumthakady, N.; Liu, F.; Kathaperumal, M.; Swaminathan, M. Packaging approaches for mmWave and sub-THz communications. In Proceedings of the 2019 IEEE MTT-S International Microwave Conference on Hardware and Systems for 5G and Beyond (IMC-5G), Atlanta, GA, USA, 15–16 August 2019. [Google Scholar]

- Sunohara, M.; Tokunaga, T.; Kunihara, T.; Higashi, M. Silicon interposer with TSVs (through silicon vias) and fine multilayer wiring. In Proceedings of the IEEE 58th Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 27–30 May 2008; pp. 847–852. [Google Scholar]

- Töpper, M.; Ndip, I.; Erxleben, R.; Brusberg, L.; Nissen, N.; Schröder, H.; Yamamoto, H.; Todt, G.; Reichl, H. 3-D thin film interposer based on TGV (Through Glass Vias): An alternative to Si-interposer. In Proceedings of the IEEE 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 66–73. [Google Scholar]

- Li, Y.; Wang, C.; Guo, Y.X. A Ka band wideband dual-polarized magnetoelectric dipole antenna array on LTCC. IEEE Trans. Antennas Propag. 2020, 68, 4985–4990. [Google Scholar] [CrossRef]

- Rabbani, M.S.; Ghafouri-Shiraz, H. Liquid crystalline polymer substrate-based THz microstrip antenna arrays for medical applications. IEEE Antennas Wirel. Propag. Lett. 2017, 16, 1533–1536. [Google Scholar] [CrossRef]

- Mohamed, I.; Sebak, A.R. Broadband transition of substrate integrated waveguide-to-air-filled rectangular waveguide. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 966–968. [Google Scholar] [CrossRef]

- Sukumaran, V.; Chen, Q.; Liu, F.; Kumbhat, N.; Bandyopadhyay, T.; Chan, H.; Min, S.; Nopper, C.; Sundaram, V.; Tummala, R. Through-package-via formation and metallization of glass interposers. In Proceedings of the IEEE 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 557–563. [Google Scholar]

- Shorey, A.; Pollard, S.; Streltsov, A.; Piech, G.; Wagner, R. Development of substrates for through glass vias (TGV) for 3DS-IC integration. In Proceedings of the IEEE 62nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2012; pp. 289–291. [Google Scholar]

- Sridharan, V.; Min, S.; Sundaram, V.; Sukumaran, V.; Hwang, S.; Chan, H.; Liu, F.; Nopper, C.; Tummala, R. Design and fabrication of bandpass filters in glass interposer with through-package-vias (TPV). In Proceedings of the IEEE 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 530–535. [Google Scholar]

- Kim, J.; Shenoy, R.; Lai, K.-Y.; Kim, J. High-Q 3D RF solenoid inductors in glass. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Tampa, FL, USA, 1–3 June 2014; pp. 199–200. [Google Scholar]

- Yook, J.-M.; Kim, D.; Kim, J.C. High performance IPDs (integrated passive devices) and TGV (through glass via) interposer technology using the photosensitive glass. In Proceedings of the IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 41–46. [Google Scholar]

- Kamgaing, T.; Elsherbini, A.A.; Frank, T.W.; Oster, S.N.; Rao, V.R. Investigation of a photodefinable glass substrate for millimeter-wave radios on package. In Proceedings of the IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 1610–1615. [Google Scholar]

- Hyeon, I.-J.; Baek, C.-W. Micromachined substrate integrated waveguides with electroplated copper vias in reflowed glass substrate for millimeter-wave applications. Microelectron. Eng. 2015, 131, 19–23. [Google Scholar] [CrossRef]

- Tong, J.; Sundaram, V.; Shorey, A.; Tummala, R. Substrate-integrated waveguides in glass interposers with through-package-vias. In Proceedings of the IEEE 65th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015; pp. 2222–2227. [Google Scholar]

- Hwangbo, S.; Fang, S.-P.; An, H.; Yoon, Y.-K.; Shorey, A.B.; Kazmi, A.M. Directional through glass via (TGV) antennas for wireless point-to-point interconnects in 3D integration and packaging. In Proceedings of the IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2017; pp. 260–265. [Google Scholar]

- Shah, U.; Liljeholm, J.; Campion, J.; Ebefors, T.; Oberhammer, J. Low-loss, high-linearity RF interposers enabled by through glass vias. IEEE Antennas Wirel. Propag. Lett. 2018, 28, 960–962. [Google Scholar] [CrossRef] [Green Version]

- Bowrothu, R.; Hwangbo, S.; Schumann, T.; Yoon, Y.-K. 28 GHz through glass via (TGV) based band pass filter using through fused silica via (TFV) technology. In Proceedings of the IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 28–31 May 2019; pp. 695–699. [Google Scholar]

- Hyeon, I.-J.; Baek, C.-W. Millimeter-wave substrate integrated waveguide using micromachined tungsten-coated through glass silicon via structures. Micromachines 2018, 9, 172. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Watanabe, A.O.; Tehrani, B.K.; Ogawa, T.; Pulugurtha, M.R.; Tentzeris, M.M.; Tummala, R.R. Ultralow-loss substrate-integrated waveguides in glass-based substrates for millimeter-wave applications. IEEE Trans. Compon. Packaging Technol. 2020, 10, 531–533. [Google Scholar] [CrossRef]

- Watanabe, A.O.; Lin, T.; Ali, M.; Wang, Y.; Smet, V.; Raj, P.M.; Tentzeris, M.M.; Tummala, R.R. Ultrathin antenna-integrated glass-based millimeter-wave package with through-glass vias. IEEE Trans. Microw. Theory Tech. 2020, 68, 5082–5092. [Google Scholar] [CrossRef]

- Su, Y.; Yu, D.; Ruan, W.; Jia, N. Development of compact millimeter-wave antenna by stacking of five glass wafers with through glass vias. IEEE Electron. Dev. Lett. 2022, 43, 934–937. [Google Scholar] [CrossRef]

- Naqvi, A.H.; Park, J.-H.; Baek, C.-W.; Lim, S. V-band end-fire radiating planar micromachined helical antenna using through-glass silicon via (TGSV) technology. IEEE Access 2019, 7, 87907–87915. [Google Scholar] [CrossRef]

- Naqvi, A.H.; Park, J.-H.; Baek, C.-W.; Lim, S. Via-monopole based quasi Yagi-Uda antenna for W-band applications using through glass silicon via (TGSV) technology. IEEE Access 2020, 8, 9513–9519. [Google Scholar] [CrossRef]

- Dietrich, T.R.; Ehrfeld, W.; Lacher, M.; Krämer, M.; Speit, B. Fabrication technologies for microsystems utilizing photoetchable glass. Microelectron. Eng. 1996, 30, 497–504. [Google Scholar] [CrossRef]

- Deslandes, D.; Wu, K. Single-substrate integration technique of planar circuits and waveguide filters. IEEE Trans. Microw. Theory Tech. 2003, 51, 593–596. [Google Scholar] [CrossRef]

- Bozzi, M.; Georgiadis, A.; Wu, K. Review of substrate-integrated waveguide circuits and antennas. IET Microw. Antennas Propag. 2011, 5, 909–920. [Google Scholar] [CrossRef]

- Hyeon, I.-J.; Park, W.-Y.; Lim, S.; Baek, C.-W. Ku-band bandpass filters using micromachined substrate integrated waveguide structure with embedded silicon vias in benzocyclobutene dielectrics. Sens. Actuators A Phys. 2012, 188, 463–470. [Google Scholar] [CrossRef]

- ur Rehman, M.; Kumar, L.N.V.; Swaminathan, M. Substrate integrated waveguide filters in glass interposer for mmWave applications. IEEE Trans. Compon. Pack. Manuf. Technol. 2022, 12, 1719–1722. [Google Scholar] [CrossRef]

- Althuwayb, A.A. MTM- and SIW-inspired bowtie antenna loaded with AMC for 5G mm-wave applications. Int. J. Antennas Propag. 2021, 30, 6658819. [Google Scholar] [CrossRef]

- Alibakhshikenari, M.; Virdee, B.S.; Salekzamankhani, S.; Aïssa, S.; See, C.H.; Soin, S.; Fishlock, S.J.; Althuwayb, A.A.; Abd-Alhameed, R.; Huynen, I.; et al. High-isolation antenna array using SIW and realized with a graphene layer for sub-terahertz wireless application. Sci. Rep. 2021, 11, 10218. [Google Scholar] [CrossRef]

- Althuwayb, A.A. On-chip antenna design using the concepts of metamaterial and SIW principles applicable to terahertz integrated circuits operating over 0.6–0.622 THz. Int. J. Antennas Propag. 2020, 2020, 6653095. [Google Scholar] [CrossRef]

- Alibakhshikenari, M.; Virdee, B.S.; See, C.H.; Abd-Alhameed, R.A.; Falcone, F.; Limiti, E. High-isolation leaky-wave array antenna based on CRLH-metamaterial implemented on SIW with ±30° frequency beam-scanning capability at millimetre-waves. Electronics 2019, 8, 642. [Google Scholar] [CrossRef] [Green Version]

- Althuwayb, A.A.; Alibakhshikenari, M.; Virdee, B.S.; Benetatos, H.; Falcone, F.; Limiti, E. Antenna on chip (AoC) design using metasurface and SIW technologies for THz wireless applications. Electronics 2021, 10, 1120. [Google Scholar] [CrossRef]

- Tantawi, K.H.; Waddel, E.; Williams, J.D. Structural and composition analysis of ApexTM and FoturanTM photodefinable glasses. J. Mater. Sci. 2013, 48, 5316–5323. [Google Scholar] [CrossRef]

- Zhao, X.; Pi, Y.; Wang, W.; Ma, S.; Jin, Y. High aspect ratio TGV fabrication using photosensitive glass substrate. In Proceedings of the 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Qingda, China, 31 October–3 November 2018. [Google Scholar]

- Berezhnoi, A.I. Glass-Ceramics and Photo-Sitalls; Plenum Press: London, UK, 1970; ISBN 978-1-4684-1763-0. [Google Scholar]

- EM Labs. Resonator Method: Split Cylinder Resonator for Permittivity Measurement. Available online: http://www.emlabs.jp/en/1-3-split.php (accessed on 15 December 2022).

- Pozar, D.M. Microwave Engineering, 4th ed.; Wiley: Hoboken, NJ, USA, 2011; ISBN 978-0-470-63155-3. [Google Scholar]

- Deslandes, D.; Wu, K. Integrated microstrip and rectangular waveguide in planar form. EEE Microw. Wirel. Compon. Lett. 2001, 11, 68–70. [Google Scholar] [CrossRef]

| Samples | Dielectric Constant | Loss Tangent |

|---|---|---|

| PEG (original) | 6.1 | 0.014 |

| PEG (heat developed) | 5.8 | 0.014 |

| Parameters | Design | Measurement | Description |

|---|---|---|---|

| 0.205 mm | 0.202 mm | Width of the TGV wall | |

| 3.6 mm | 3.591 mm | Length of the TGV wall | |

| 0.64 mm | 0.629 mm | Width of the microstrip line | |

| 1.6 mm | 1.58 mm | Length of the microstrip line | |

| 1.2 mm | 1.18 mm | Width of the tapered transition | |

| 1.5 mm | 1.48 mm | Length of the tapered transition | |

| 3.95 mm | 3.91 mm | Length of the SIW | |

| 3.0 mm | 3.005 mm | Width between the two TGV walls | |

| 0.420 mm | 0.415 mm | Thickness of the PEG substrate |

| Ref. | Vias | Frequency [GHz] | Device Length [mm] | Insertion Loss [dB] | |

|---|---|---|---|---|---|

| [16] | Borosilicate glass (350 μm/4.6/0.0037 1) | Electroplated Cu | 20–45 | 10.0 2 | <1.4 dB 2 |

| [21] | Borosilicate glass (350 μm/4.6/0.0037 1) | Tungsten-coated Si | 20–45 | 7.0 2 | <1.15 dB 2 |

| [22] | Borosilicate glass with low-loss polymer lamination (100 μm/5.4/0.006) | Electroless-plated Cu + SAP (semi-additive patterning) | 24–40 | 4.0 3 | 0.64 dB 3,4 |

| This work | Photoetchable glass (420 μm/5.81/0.014) | Sputtered Cu on the TGV walls | 26.5–40 | 10.0 2 | 2.53 ± 0.55 dB 2 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chung, S.-H.; Shin, J.-H.; Kim, Y.-K.; Baek, C.-W. Fabrication of Substrate-Integrated Waveguide Using Micromachining of Photoetchable Glass Substrate for 5G Millimeter-Wave Applications. Micromachines 2023, 14, 288. https://doi.org/10.3390/mi14020288

Chung S-H, Shin J-H, Kim Y-K, Baek C-W. Fabrication of Substrate-Integrated Waveguide Using Micromachining of Photoetchable Glass Substrate for 5G Millimeter-Wave Applications. Micromachines. 2023; 14(2):288. https://doi.org/10.3390/mi14020288

Chicago/Turabian StyleChung, Seung-Han, Jae-Hyun Shin, Yong-Kweon Kim, and Chang-Wook Baek. 2023. "Fabrication of Substrate-Integrated Waveguide Using Micromachining of Photoetchable Glass Substrate for 5G Millimeter-Wave Applications" Micromachines 14, no. 2: 288. https://doi.org/10.3390/mi14020288

APA StyleChung, S.-H., Shin, J.-H., Kim, Y.-K., & Baek, C.-W. (2023). Fabrication of Substrate-Integrated Waveguide Using Micromachining of Photoetchable Glass Substrate for 5G Millimeter-Wave Applications. Micromachines, 14(2), 288. https://doi.org/10.3390/mi14020288