160 GHz D-Band Low-Noise Amplifier and Power Amplifier for Radar-Based Contactless Vital-Signs-Monitoring Systems

Abstract

:1. Introduction

2. System Architecture

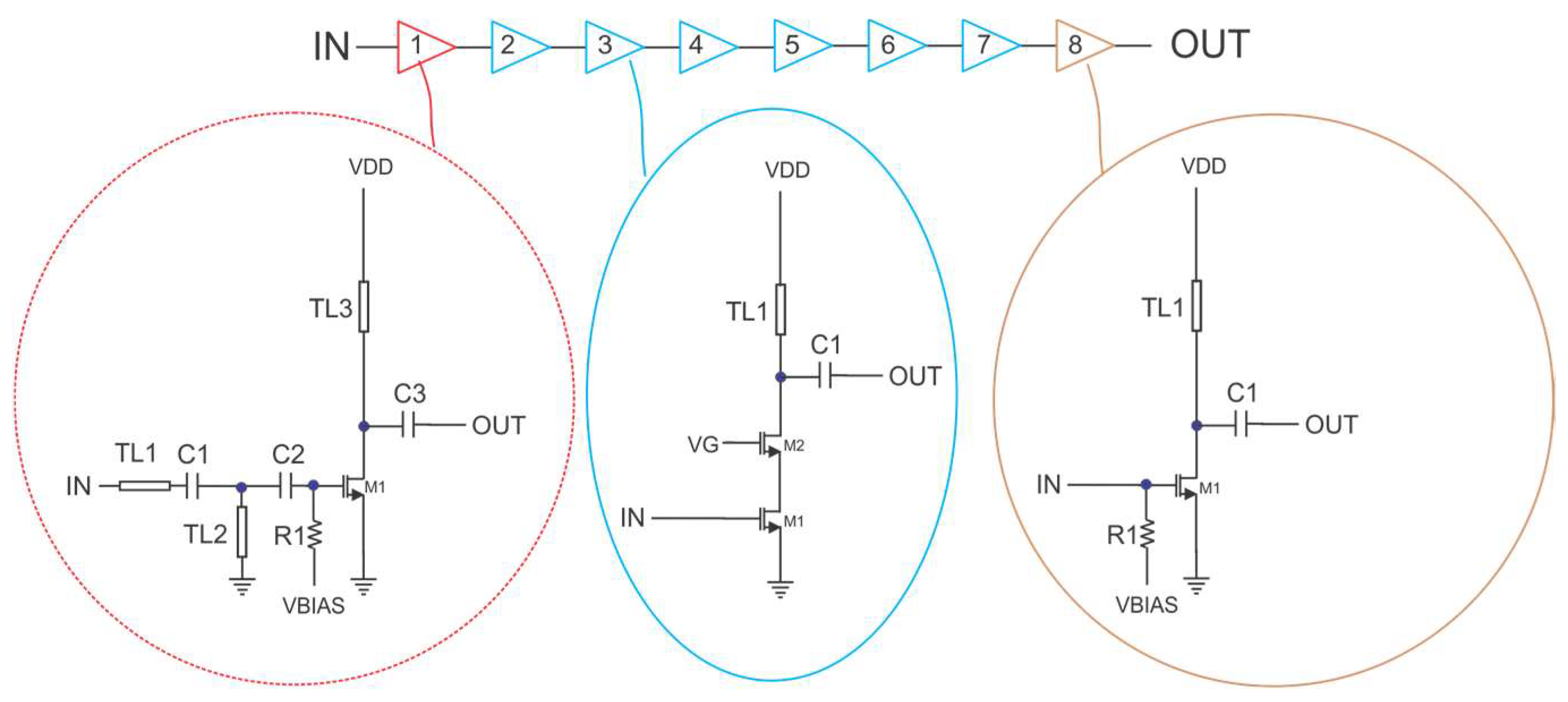

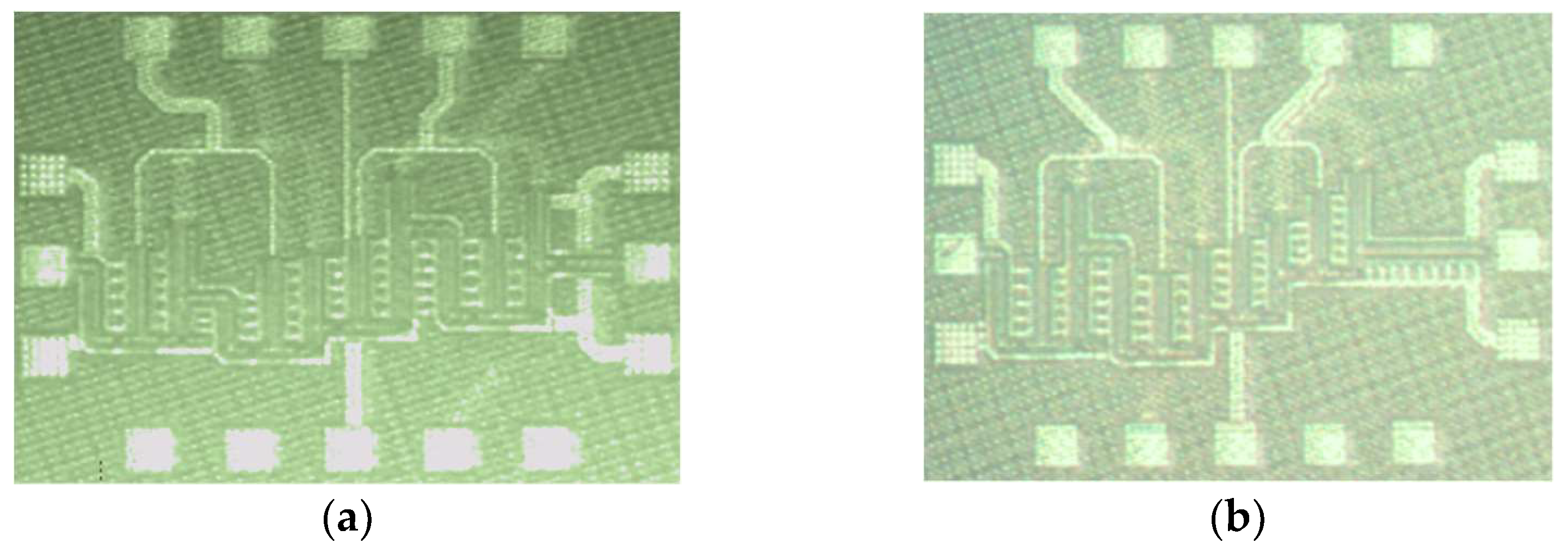

3. Circuit Design

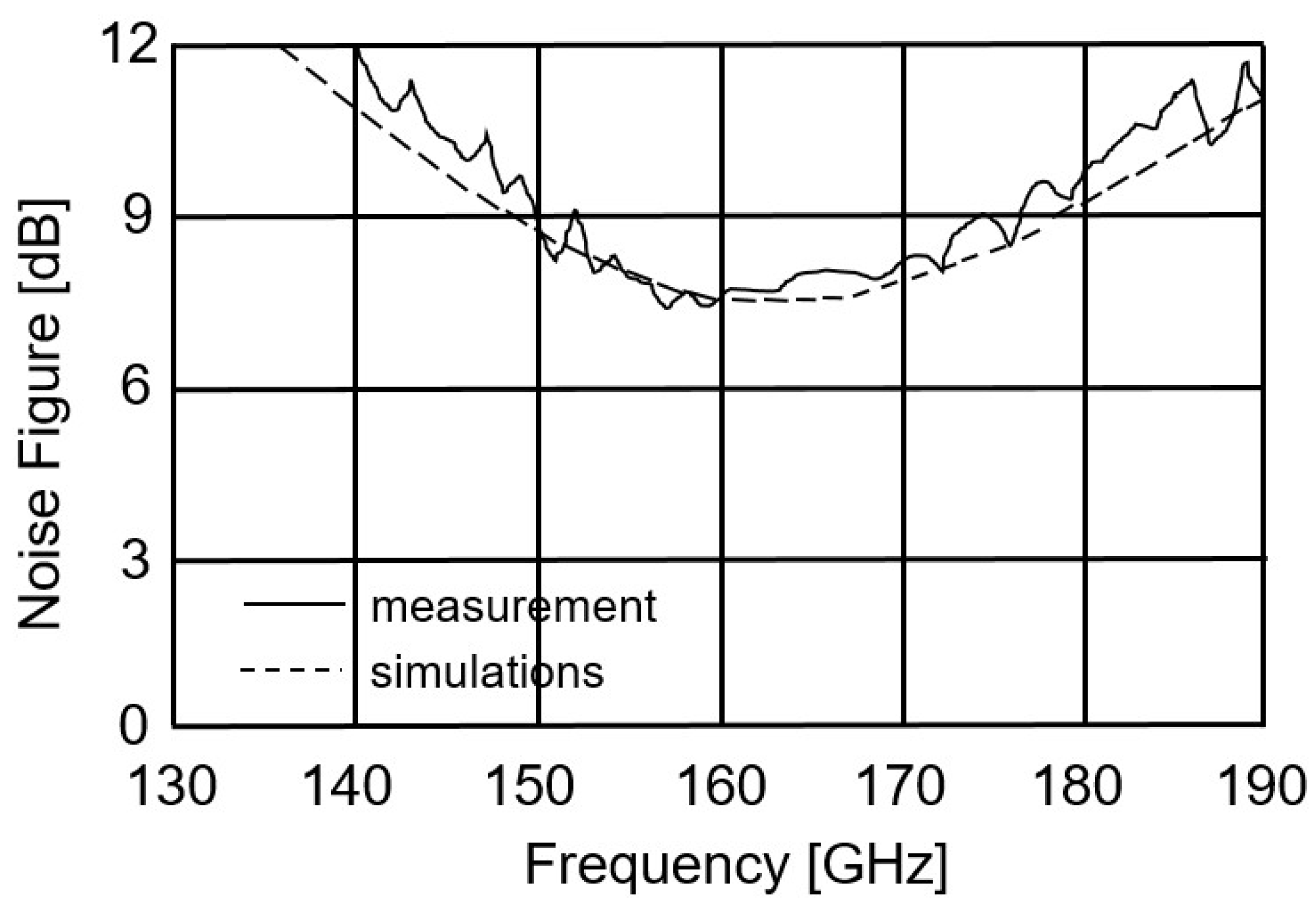

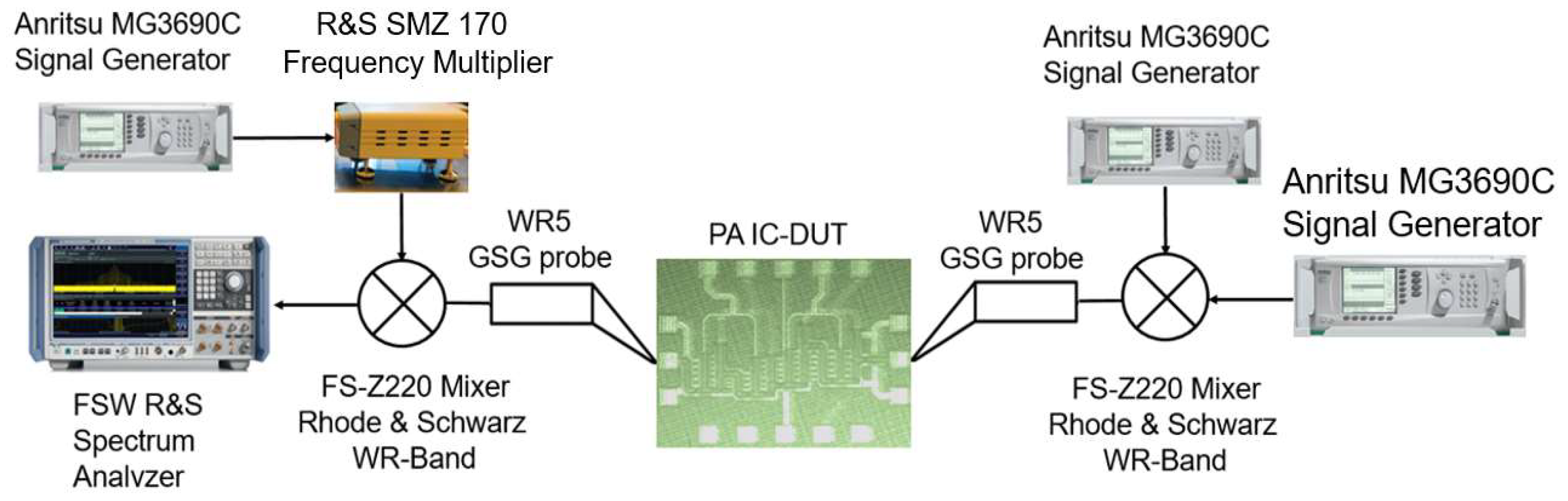

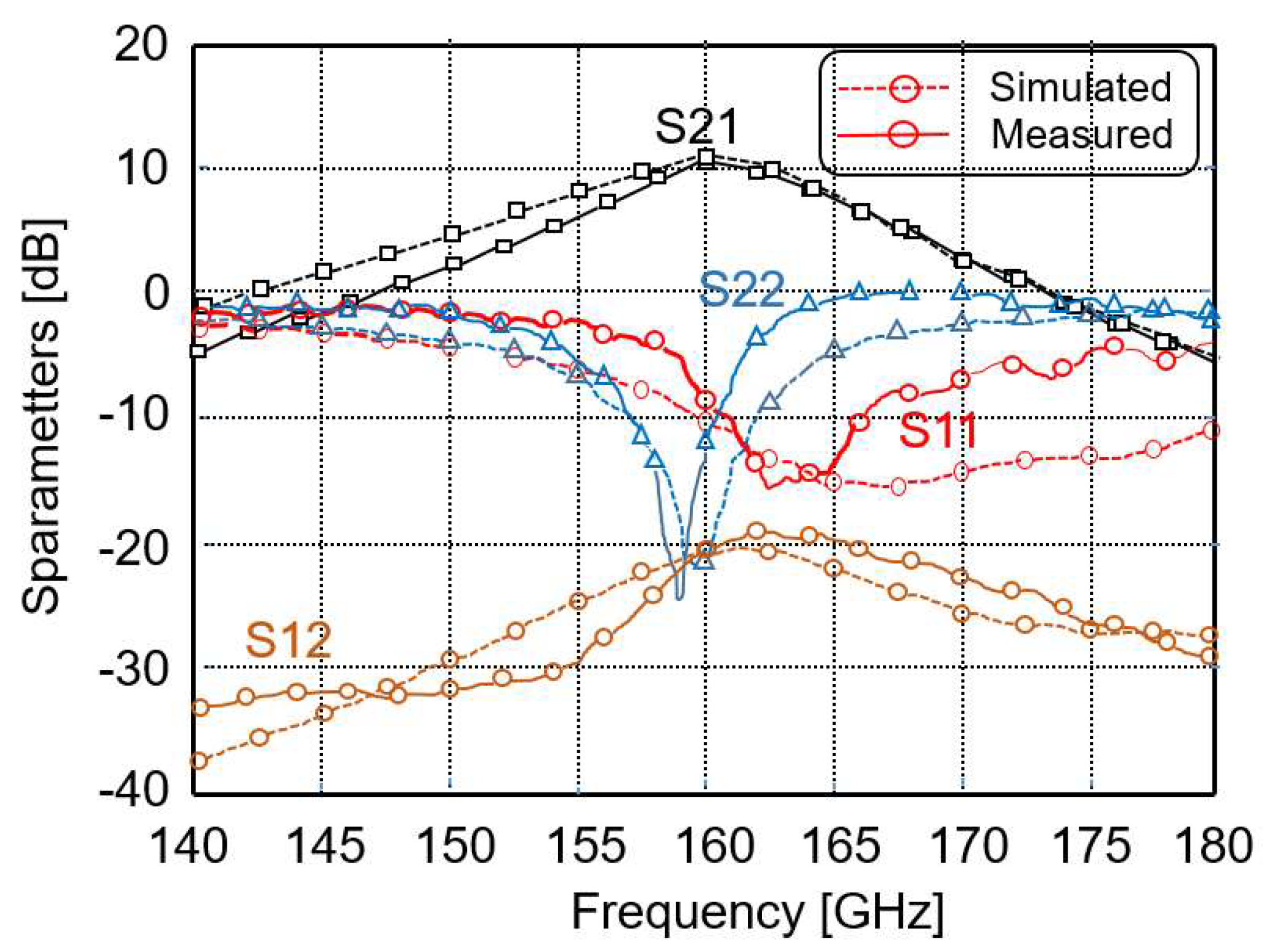

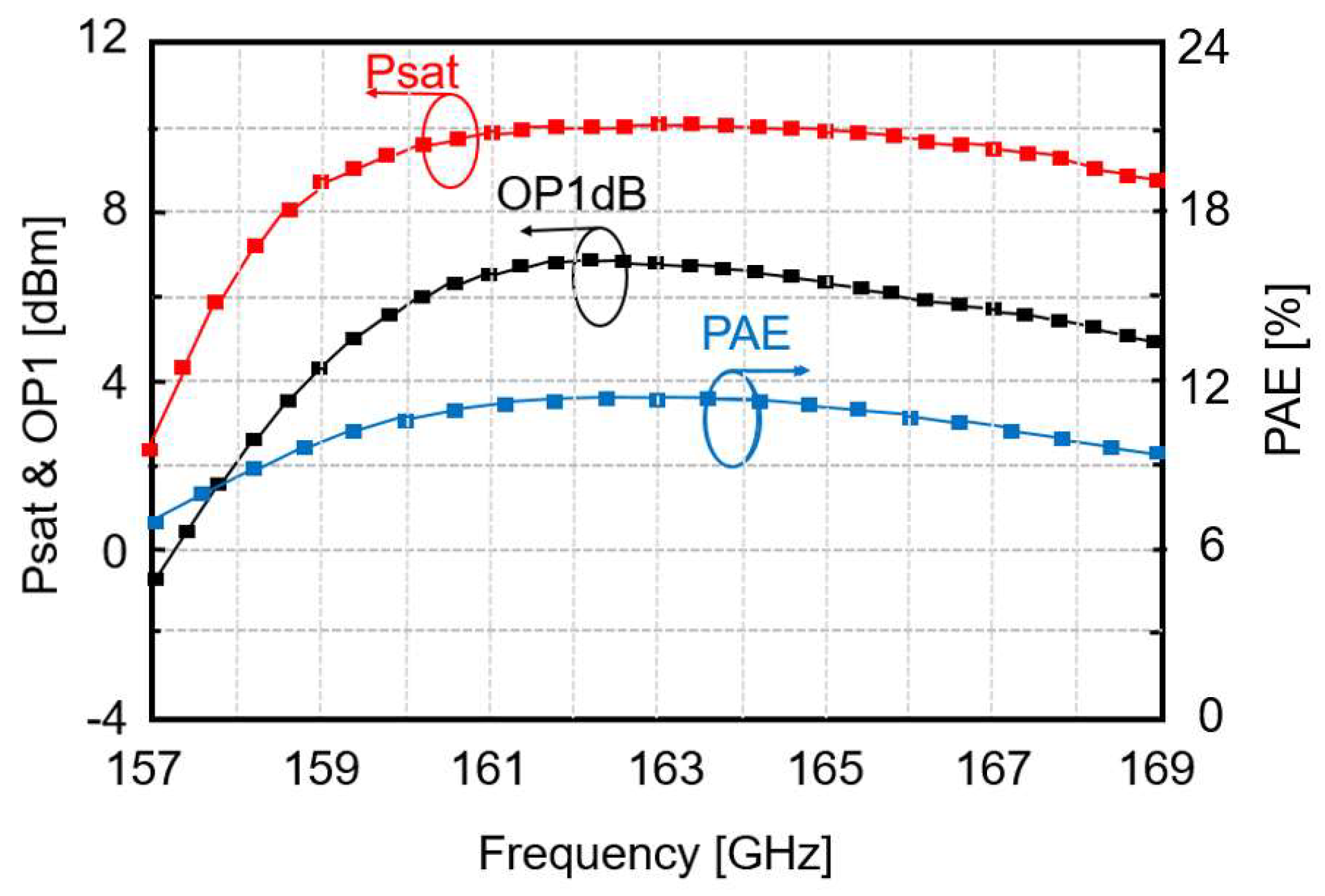

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kebe, M.; Gadhafi, R.; Mohammad, B.; Sanduleanu, M.; Saleh, H.; Al-Qutayri, M. Human vital signs detection methods and potential using radars: A review. Sensors 2020, 20, 1454. [Google Scholar] [CrossRef] [PubMed]

- Gu, C.; Li, C.; Lin, J.; Long, J.; Huangfu, J.; Ran, L. Instrument-based noncontact Doppler radar vital sign detection system using heterodyne digital quadrature demodulation architecture. IEEE Trans. Instrum. Meas. 2009, 59, 1580–1588. [Google Scholar]

- Fang, Z.; Lou, L.; Tang, K.; Wang, W.; Wang, Y.; Guo, T.; Yang, C.; Zheng, Y. Wide Field-of-View Locating and Multimodal Vital Sign Monitoring Based on X-Band CMOS-Integrated Phased-Array Radar Sensor. IEEE Trans. Microw. Theory Tech. 2020, 68, 4054–4065. [Google Scholar] [CrossRef]

- Sayginer, M.; Rebeiz, G.M. A W-band LNA/phase shifter with 5-dB NF and 24-mW power consumption in 32-nm CMOS SOI. IEEE Trans. Microw. Theory Tech. 2018, 66, 1973–1982. [Google Scholar] [CrossRef]

- Mustapha, A.; Shabra, A. A 60–90GHz stagger-tuned low-noise amplifier with 1.2dBm OP1dB in 65nm CMOS. In Proceedings of the 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS) 2017, Batumi, Georgia, 5–8 December 2017; pp. 26–29. [Google Scholar] [CrossRef]

- Pellerano, S.; Palaskas, Y.; Soumyanath, K. A 64 GHz LNA with 15.5 dB gain and 6.5 dB NF in 90 nm CMOS. IEEE J. Solid-State Circuits 2008, 43, 1542–1552. [Google Scholar] [CrossRef]

- Guo, S.; Xi, T.; Gui, P.; Huang, D.; Fan, Y.; Morgan, M. A transformer feedback Gm-boosting technique for gain improvement and noise reduction in mm-wave cascode LNAs. IEEE Trans. Microw. Theory Tech. 2016, 64, 2080–2090. [Google Scholar] [CrossRef]

- Fritsche, D.; Tretter, G.; Carta, C.; Ellinger, F. Millimeter-wave low noise amplifier design in 28-nm low-power digital CMOS. IEEE Trans. Microw. Theory Tech. 2015, 63, 1910–1922. [Google Scholar] [CrossRef]

- Meng, F.; Ma, K.; Yeo, K.S.; Boon, C.C.; Yi, X.; Sun, J.; Feng, G.; Xu, S. A compact 57–67 GHz bidirectional LNAPA in 65-nm CMOS technology. IEEE Microw. Wireless Compon. Lett. 2016, 26, 628–630. [Google Scholar] [CrossRef]

- Pepe, D.; Zito, D. 32 dB gain 28 nm bulk CMOS W-band LNA. IEEE Microw. Wireless Compon. Lett. 2015, 25, 55–57. [Google Scholar] [CrossRef]

- Lee, C.J.; Lee, H.J.; Lee, J.G.; Jang, T.H.; Park, C.S. A W-band CMOS low power wideband low noise amplifier with 22 dB gain and 3 dB bandwidth of 20 GHz. In Proceedings of the 2015 Asia-Pacific Microwave Conference (APMC), Nanjing, China, 6–9 December 2015; pp. 1–3. [Google Scholar]

- Lin, Y.-S.; Nguyen, V.K.; Lin, H.-C.; Lee, C.-Y.; Wang, C.-C.; Chen, C.-C.; Lin, Y.-W. A 7.2 mW 74~82 GHz CMOS low-noise amplifier with 17.3 ± 1.5 dB gain and 7.7 ± 0.3 dB NF for automotive radar system. In Proceedings of the 2016 IEEE Radio and Wireless Symposium (RWS), Austin, TX, USA, 24–27 January 2016; pp. 111–114. [Google Scholar]

- Parveg, D.; Varonen, M.; Karaca, D.; Vahdati, A.; Kantanen, M.; Halonen, K.A.I. Design of a D-Band CMOS Amplifier Utilizing Coupled Slow-Wave Coplanar Waveguides. IEEE Trans. Microw. Theory Tech. 2018, 66, 3. [Google Scholar] [CrossRef]

- Hamani, A.; Siligaris, A.; Blampey, B.; Dehos, C.; Jimenez, J.L.G. A 125.5–157 GHz 8 dB NF and 16 dB of Gain D-band Low Noise Amplifier in CMOS SOI 45 nm. In Proceedings of the 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 4–6 August 2020; pp. 197–200. [Google Scholar] [CrossRef]

- Asada, H.; Matsushita, K.; Bunsen, K.; Okada, K.; Matsuzawa, A. A 60 GHz CMOS Power Amplifier Using Capacitive Cross-Coupling Neutralization with 16% PAE. In Proceedings of the 2011 6th European Microwave Integrated Circuit Conference, Manchester, UK, 10–11 October 2011. [Google Scholar]

- Hamani, A.; Siligaris, A.; Blampey, B.; Dehos, C.; Jimenez, J.L.G. 167-GHz and 155-GHz High Gain D-band Power Amplifiers in CMOS SOI 45-nm Technology. In Proceedings of the 2020 15th European Microwave Integrated Circuits Conference (EuMIC), Utrecht, The Netherlands, 10–15 January 2021; pp. 261–264. [Google Scholar]

- Gu, Q.J.; Xu, Z.; Chang, M.F. Two-way current combining W-band power amplifier in 65-nm CMOS. IEEE Trans. Microw. Theory Tech. 2012, 60, 1365–1374. [Google Scholar] [CrossRef]

- Elsayed, N.; Saleh, H.; Mohammad, B.; Sanduleanu, M. A 28-GHz Cascode inverse Class-D power amplifier utilizing pulse injection in 22-nm FDSOI. IEEE Access 2020, 8, 97353–97360. [Google Scholar] [CrossRef]

- Elsayed, N.; Saleh, H.; Mohammad, B.; Sanduleanu, M. A 28GHz, asymmetrical, modified Doherty power amplifier, in 22 nm FDSOI CMOS. Proceedings of 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Kim, J.; Choi, C.-G.; Lee, K.; Kim, K.; Choi, S.-U.; Song, H.-J. Analysis and Design of Dual-Peak Gmax-Core CMOS Amplifier in D-Band Embedding a T-Shaped Network. Proceedings of 2022 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Denver, CO, USA, 19 June 2022; pp. 87–90. [Google Scholar] [CrossRef]

- Landsberg, N.; Asaf, O.; Shin, W. A D-Band LNA Using a 22 nm FD-SOI CMOS Technology for Radar Applications. In Proceedings of the 2021 IEEE International Conference on Microwaves, Antennas, Communications and Electronic Systems (COMCAS), Tel Aviv, Israel, 1–3 November 2021; pp. 178–180. [Google Scholar] [CrossRef]

- Hetterle, P.; Engelmann, A.; Probst, F.; Weigel, R.; Dietz, M. Design of a Low Voltage D-band LNA in 22 nm FDSOI. In Proceedings of the 2022 17th European Microwave Integrated Circuits Conference (EuMIC), Milan, Italy, 26–27 September 2022; pp. 252–255. [Google Scholar] [CrossRef]

- Artz, P.J.; Scholz, P.; Mausolf, T.; Gerfers, F. A Fully-Differential 1466-1574 GHz LNA Utilizing Back Gate Control to Adjust Gain in 22 nm, F.D.S.O.I. In Proceedings of the 2022 IEEE/MTT-S International Microwave Symposium-IMS, Denver, CO, USA, 19–24 June 2022; pp. 611–614. [Google Scholar]

- Belostotski, L.; Klumperink, E.A.M. Figures of Merit for CMOS Low-Noise Amplifiers and Estimates for Their Theoretical Limits. In IEEE Transactions on Circuits and Systems II: Express Briefs; IEEE: Piscataway, NJ, USA, 2022; Volume 69, pp. 734–738. [Google Scholar] [CrossRef]

- Simic, D.; Reynaert, P. A 14.8 dBm 20.3 dB Power Amplifier for D-band Applications in 40 nm CMOS. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Philadelphia, PA, USA, 10–12 June 2018. [Google Scholar]

- Tang, X.; Nguyen, J.; Medra, A.; Khalaf, K.; Visweswaran, A.; Debaillie, B.; Wambacq, P. Design of D-Band Transformer-Based Gain-Boosting Class-AB Power Amplifiers in Silicon Technologies. In IEEE Transactions on Circuits and Systems I: Regular Papers; IEEE: Piscataway, NJ, USA, 2020; Volume 67, pp. 1447–1458. [Google Scholar] [CrossRef]

- Rahimi, E.; Bozorgi, F.; Hueber, G. A 22nm FD-SOI CMOS 2-way D-band Power Amplifier Achieving PAE of 7.7% at 9.6 dBm OP1dB and 3.1% at 6dB Back-off by Leveraging Adaptive Back-Gate Bias Technique. In Proceedings of the 2022 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Denver, CO, USA, 19–21 June 2022; pp. 175–178. [Google Scholar]

- Chien, J.S.C.; Buckwalter, J.F. A 111-149-GHz, Compact Power-combined Amplifier with 17.5-dBm $ P_ {sat} $, 16.5% PAE in 22-nm CMOS FD-SOI. In Proceedings of the ESSCIRC 2022-IEEE 48th European Solid State Circuits Conference (ESSCIRC), Milan, Italy, 19–22 September 2022; pp. 453–456. [Google Scholar]

- Engelmann, A.; Hetterle, P.; Probst, F.; Weigel, R.; Dietz, M. Design of two Low DC-Power High-Efficiency D-Band Power Amplifiers in 22nm FDSOI. In Proceedings of the 2022 17th European Microwave Integrated Circuits Conference (EuMIC), Milan, Italy, 26–27 September 2022; pp. 212–215. [Google Scholar] [CrossRef]

| Ref. | Tech. | Freq. (GHz) | Gain (dB) | BW (GHz) | NF (dB) | Pdc (mW) | Area (mm2) | FOM |

|---|---|---|---|---|---|---|---|---|

| [13] | FDSOI 28 nm | 143–166 | 15.7 | 23 | 8.5 | 32 | 0.34 (core) | 0.053 |

| [14] | 45 nm CMOS SOI | 125.5–157 | 16 | 31.5 | 8 | 75 | 0.07 (core) | 0.035 |

| [20] | 28 nm FDSOI | 117–143 | 14.5 | 26 | - | 21.6 | 0.1 (core) | 0.045 |

| [21] | 22 nm FDSOI | 131–162 | 21 | 31 | 5.5 * | 28–46 | 0.02 (core) | 0.091 |

| [22] | 22 nm FDSOI | 130 | 17 | 24.8 | 8 | 60 | 0.133 (core) | 0.018 |

| [23] | 22 nm FDSOI | 146.6–157.4 | 9–18 | 10.8 | 7.5–9.3 * | 17.5–27.5 | 0.09 | 0.014 |

| This work | 22 nm FDSOI | 157–166 | 17 | 9 | 7.6 | 28.8 | 0.293 (total) | 0.061 |

| Ref. | Tech. | Freq. (GHz) | Gain (dB) | Psat (dBm) | OP1dB (dBm) | Pdc (mW) | PAE (%) | FOM |

|---|---|---|---|---|---|---|---|---|

| [19] | 45 nm CMOS | 152.5 | 18 | 8.8 | 5 | 92 | 6.8 | 29.6 |

| [25] | 40 nm CMOS | 140 | 20.3 | 14.8 | 10.7 | 305 | 8.9 | 39.49 |

| [26] | 40 nm bulk CMOS | 132 | 22.5 | 8 | 5.2 | 305 | 6.6 | 37.57 |

| [27] | 22 nm FDSOI | 135 | 14.2 | 10.3 | 9.6 | 30 | 7.9 | 26.53 |

| [28] | 22 nm FDSOI | 130 | 13.5 | 17.5 | - | 56 | 16.5 | 35.90 |

| [29] | 22 nm FDSOI | 135.8 | 23.4 | 6.5 | 4 | 46 | 9.1 | 32.60 |

| This work | 22 nm FDSOI | 160 | 10 | 10 | 7 | 10.8 | 11 | 40.82 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mustapha, A.A.; Sanduleanu, M. 160 GHz D-Band Low-Noise Amplifier and Power Amplifier for Radar-Based Contactless Vital-Signs-Monitoring Systems. Micromachines 2023, 14, 993. https://doi.org/10.3390/mi14050993

Mustapha AA, Sanduleanu M. 160 GHz D-Band Low-Noise Amplifier and Power Amplifier for Radar-Based Contactless Vital-Signs-Monitoring Systems. Micromachines. 2023; 14(5):993. https://doi.org/10.3390/mi14050993

Chicago/Turabian StyleMustapha, Ademola Akeem, and Mihai Sanduleanu. 2023. "160 GHz D-Band Low-Noise Amplifier and Power Amplifier for Radar-Based Contactless Vital-Signs-Monitoring Systems" Micromachines 14, no. 5: 993. https://doi.org/10.3390/mi14050993

APA StyleMustapha, A. A., & Sanduleanu, M. (2023). 160 GHz D-Band Low-Noise Amplifier and Power Amplifier for Radar-Based Contactless Vital-Signs-Monitoring Systems. Micromachines, 14(5), 993. https://doi.org/10.3390/mi14050993