An Analytical Model of Dynamic Power Losses in eGaN HEMT Power Devices

Abstract

:1. Introduction

2. Background and Methodology

2.1. Traditional Power Loss Model

2.2. Experimental Circuit and Method

2.3. Qualitative Method Used to Discover the Channel Behavior

3. Extraction of the Dynamic Rdson

4. Discussion on the Effect of the Drain Current using a Double-Mode Test Technique

5. Investigation of the Real Channel Current

6. Modeling of Switching Power Losses

6.1. Stage 1 (S1)—Off-State with a High Vds

6.2. Stage 2 (S2)—On-State in Saturation Region

6.3. Stage 3 (S3)—Turn-on Transition

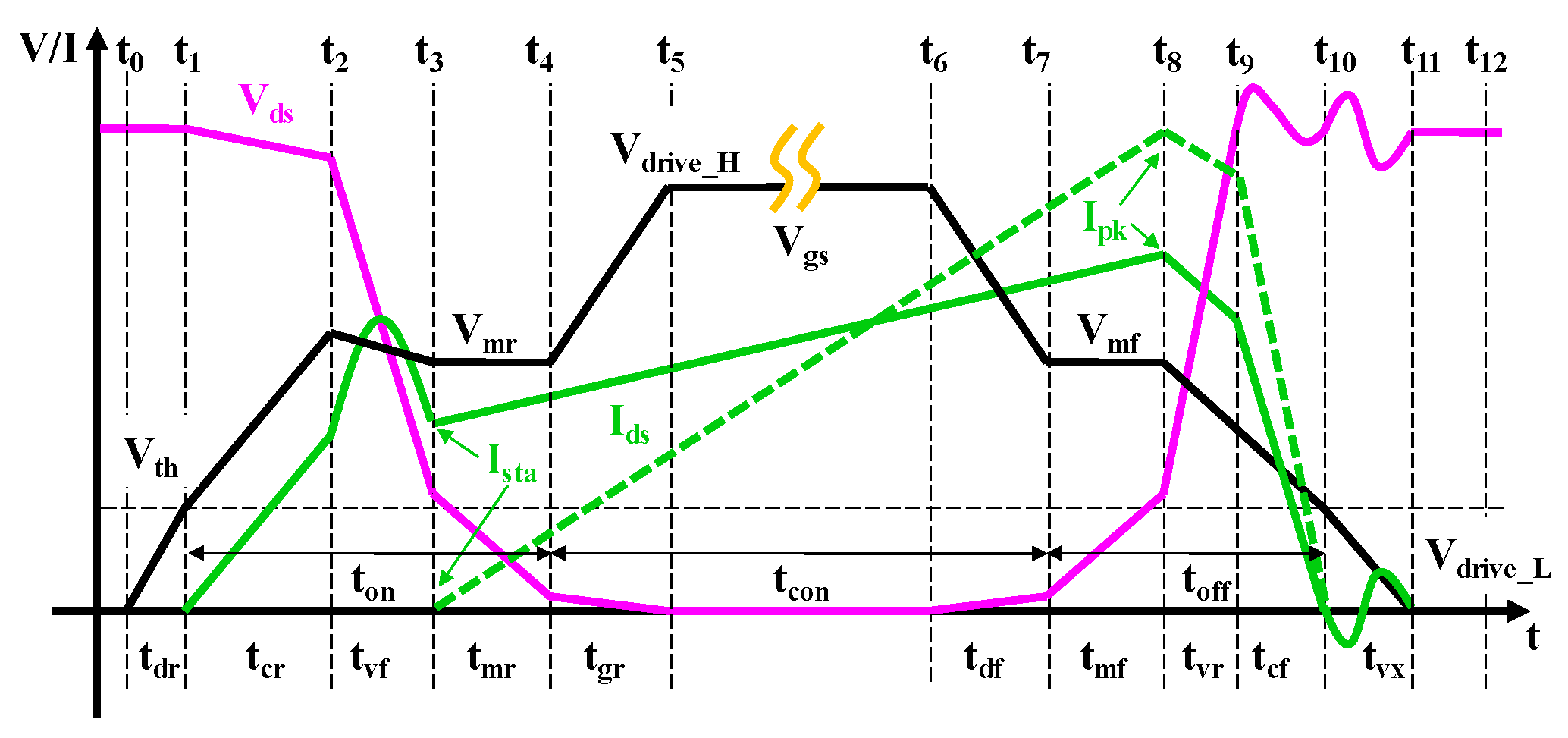

- 1.

- In the t1–t2 time interval, Idrain increases almost linearly from 0 to the Ista at t2, which is similar to a Si-based MOSFET [13,34], while Vdrain decreases slightly from Vds to Vr due to the result of the parasitic inductance voltage drop caused by a high di/dt in the circuit. At t2, the current of the freewheeling diode D1 decreases to zero. In this time interval, the gate voltage of the device slightly exceeds Vth, meaning that the device is operating in a linear region. Meanwhile, the trapping effect of a high electric field will also lead to a large dynamic Rdson in the linear region (Rturn_on_cr), which is similar to that in the on-state, as well as an extra gate lag. Thus, the coefficients of the dynamic Rdson should be the same as those in Figure 4. Assuming that the heatsink is large enough and the self-heating effect is ignored, the t1–t2 time interval, Vr, and the power losses in this time interval (Pturn_on_cr) can be written as follows:where Leff_Gate and Weff_Gate are the effective channel length and width, respectively. Ls is the source inductor, which is in series with and between the source terminal and the ground. The coefficient of the gate lag(klag) is a fitting parameter, which can be obtained by measuring the turn-on delay for various Vds_off, fs and duty cycles.

- 2.

- In the t2–t3 time interval, the HEMT device takes over the total inductive load current, and Vds decreases to a boundary voltage of (Vmr − Vth) at t3 due to the discharging of Coss. The stray inductors in series around the circuit are resonant with Coss and the stray capacitors (Cstray) in this time interval. The current path through the device is illustrated in Figure 5b. It is assumed that Vgs and ista remain unchanged, and the reverse recovery of the D1 is zero. In addition, the current in this time interval is usually large enough; hence, the charging time of Coss can be ignored. Moreover, voltage-dependent Coss is not suitable for the calculation of power losses in this time interval because Vdrain is always changing. Therefore, Qgd is used to replace Coss, and the time interval of t2–t3 can then be written as follows:where is the average channel current during the t2–t3 time interval.

- 3.

- During the t3–t4 time interval, the HEMT device operates in an ohmic conducting state. Then, Vdrain continues to decrease until it reaches a low on-voltage (Von) from (Vmr − Vth). Assuming that ista and the Miller voltage Vmr do not change, the t3–t4 time interval, Von_r, and the power losses in this time interval (Pturn_on_mr) can be written as follows [36]:

6.4. Stage 4 (S4)—Turn-off Transition

- 4.

- In the t7–t8 time interval, the observations are very similar to those in the t3–t4 time interval. The HEMT device moves into a linear region from an ohmic conducting state. Vdrain increases to a boundary voltage of . Assuming that the peak current is unchanged, and , the t7–t8 time interval, Von_f, and the power losses in this time interval (Pturn_on_mf) can be written as follows:

- 5.

- In the t8–t9 time interval, the observations are very similar to those in the t2–t3 time intervals. Vdrain continues to increase more quickly towards the off-state Vds_off, while Idrain decreases slightly to ir. This current drop is caused by a charging shunt to other peripheral devices [33], and the current path through the device is illustrated in Figure 5d. Assuming that the Miller voltage (Vmf) remains unchanged and the current-dependent charging time of Coss can no longer be ignored, we have the following equation:

- 6.

- In the t9–t10 time interval, the observations are similar to those in the t1–t2 time interval. Idrain decreases from ir to a low value because the current begins to divert from the HEMT device to D1. In this time interval, the drain voltage is in a state of resonance, while Vgs decreases to (Vmr − Vth), and the device channel current reaches zero at t10 [20]. Then, the t9–t10 time interval and the power losses at this time interval (Pturn_off_cf) can be written as follows:

- 7.

- During the t10–t11 time interval, the device is turned off, but Vdrain ringing occurs due to the resonance between Coss and Lstray. These fluctuations of the drain voltage will lead to a slight power loss, which depends on the ringing peak voltage (Vds_pk). Assuming that the reverse recovery of D1 is zero, we have the following equation:

7. Model Verification via Experiments

8. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Glossary

| Gate voltage. | |

| Gate voltage in high level. | |

| Gate voltage in low level. | |

| Miller gate voltages during the turn-on transition. | |

| Miller gate voltages during the turn-off transition. | |

| Threshold voltage. | |

| Total turn-on time during the turn-on transition. | |

| Turn-on delay time. | |

| Turn-on current rise time. | |

| Turn-on voltage fall time. | |

| Turn-on Miller rise time. | |

| Turn-on gate voltage rise remaining time. | |

| Total turn-off time during the turn-off transition. | |

| Turn-off delay time. | |

| Miller fall time. | |

| Voltage rise time. | |

| Current fall time. | |

| Voltage continuous rise time. | |

| Gate-source charge. | |

| Gate-drain charge. | |

| Overcharge gate charge. | |

| Total gate charge, equal to the sum of Qgs, Qgd, and Qod. | |

| Drain-source current. | |

| Start drain-source current at turn-on transition. | |

| Peak drain-source current during on-state. | |

| Drain-source voltage. |

References

- del Alamo, J.A.; Joh, J. GaN HEMT reliability. Proc. Microelectron. Reliab. 2009, 49, 1200–1206. [Google Scholar] [CrossRef]

- Mishra, U.K.; Parikh, P.; Wu, Y.F. AlGaN/GaN HEMTs—An overview of device operation and applications. Proc. IEEE 2002, 90, 1022–1031. [Google Scholar] [CrossRef]

- Ambacher, O.; Foutz, B.; Smart, J.; Shealy, J.R.; Weimann, N.G.; Chu, K.; Murphy, M.; Sierakowski, A.J.; Schaff, W.J.; Eastman, L.F.; et al. Two-dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures. J. Appl. Phys. 2000, 87, 334–344. [Google Scholar] [CrossRef]

- Wang, K.; Yang, X.; Li, H.; Ma, H.; Zeng, X.; Chen, W. An Analytical Switching Process Model of Low-Voltage eGaN HEMTs for Loss Calculation. IEEE Trans. Power Electron. 2016, 31, 635–647. [Google Scholar] [CrossRef]

- Wang, K.; Tian, M.; Li, H.; Zhang, F.; Yang, X.; Wang, L. An improved switching loss model for a 650V enhancement-mode GaN transistor. In Proceedings of the 2016 IEEE 2nd Annual Southern Power Electronics Conference (SPEC), Auckland, New Zealand, 5–8 December 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Shen, Y.F.; Wang, H.; Shen, Z.; Blaabjerg, F.; Qin, Z. An Analytical Turn-on Power Loss Model for 650-V GaN eHEMTs. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 913–918. [Google Scholar] [CrossRef]

- Hou, R.; Lu, J.C.; Chen, D. Parasitic Capacitance Eqoss Loss Mechanism, Calculation, and Measurement in Hard-Switching for GaN HEMTs. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 919–924. [Google Scholar] [CrossRef]

- Guacci, M.; Heller, M.; Neumayr, D.; Bortis, D.; Kolar, J.W.; Deboy, G.; Ostermaier, C.; Haberlen, O. On the Origin of the Coss-Losses in Soft-Switching GaN-on-Si Power HEMTs. IEEE J. Emerg. And Sel. Top. Power Electron. 2018, 7, 679–694. [Google Scholar] [CrossRef]

- Chen, J.; Luo, Q.M.; Huang, J.; He, Q.Q.; Du, X. A Complete Switching Analytical Model of Low-Voltage eGaN HEMTs and Its Application in Loss Analysis. IEEE Trans. Ind. Electron. 2019, 67, 1615–1625. [Google Scholar] [CrossRef]

- Spaziani, L. A study of MOSFET performance in processor targeted buck and synchronous rectifier buck converters. In Proceedings of the HFPC Power Conversion Proc, Nurnberg, Germany, 21–23 May 1996; pp. 123–137, ISBN 0931033632. [Google Scholar]

- Klein, J. Synchronous Buck MOSFET Loss Calculations with Excel Model. 2006. Available online: www.fairchildsemi.com (accessed on 21 November 2014).

- Lidow, A.; Strydom, J.; Rooij, M.; Reusch, D. GaN Transistors for Efficient Power Conversion, 2nd ed.; Efficient Power Conversion Corporation; Wiley Press: Hoboken, NJ, USA, 2015; ISBN 978-1-118-84476-2. [Google Scholar]

- Ren, Y.; Xu, M.; Zhou, J.; Lee, F.C. Analytical loss model of power MOSFET. IEEE Trans. Power Electron. 2006, 21, 310–319. [Google Scholar] [CrossRef]

- Wang, J.; Chung, H.S.H.; Li, R.T.H. Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance. IEEE Trans. Power Electron. 2016, 28, 573–590. [Google Scholar] [CrossRef]

- Castro, I.; Roig, J.; Gelagaev, R.; Vlachakis, B.; Bauwens, F.; Lamar, D.G.; Driesen, J. Analytical switching loss model for superjunction MOSFET with capacitive nonlinearities and displacement currents for DC–DC power converters. IEEE Trans. Power Electron. 2016, 31, 2485–2495. [Google Scholar] [CrossRef]

- Cao, J.; Pei, Y.; Wang, Z. Analysis of power of switching components in boost PFC circuit. Adv. Technol. Electron. Eng. Energy 2002, 21, 41–44. [Google Scholar]

- Lei, J.M.; Wang, R.; Yang, G.; Wang, J.; Jiang, F.L.; Chen, D.J.; Lu, H.; Zhang, R.; Zheng, Y.D. Precise Extraction of Dynamic Rdson under High Frequency and High Voltage by A Double-Diode-Isolation Method. IEEE J. Electron. Dev. Soc. 2019, 7, 690–695. [Google Scholar] [CrossRef]

- Alemanno, A.; Anngelotti, A.M.; Gibiino, G.P.; Santarelli, A.; Sangiorgi, E.; Florian, C. A Reconfigurable Setup for the On-Wafer Characterization of the Dynamic RON of 600 V GaN Switches at Variable Operating Regimes. Electronics 2023, 12, 1063. [Google Scholar] [CrossRef]

- Li, R.; Wu, X.K.; Yang, S.; Sheng, K. Dynamic ON-State Resistance Test and Evaluation of GaN Power Devices Under Hard- and Soft-Switching Conditions by Double and Multiple Pulses. IEEE Trans. Power Electron. 2019, 34, 1044–1053. [Google Scholar] [CrossRef]

- Guo, Z.; Hitchcock, C.; Chow, T.P. Lossless turn-off switching projection of lateral and vertical GaN power field-effect transistors. Phys. Status Solidi A 2017, 214, 1600820. [Google Scholar] [CrossRef]

- Wang, H.; Liu, C.; Jiang, Q.; Tang, Z.; Chen, K.J. Dynamic Performance of AlN-Passivated AlGaN/GaN MIS-High Electron Mobility Transistors Under Hard Switching Operation. IEEE Electron Dev. Lett. 2015, 36, 760–762. [Google Scholar] [CrossRef]

- Bocker, J.; Kuring, C.; Tannhauser, M.; Dieckerhoff, S. Ron Increase in GaN HEMTs-Temperature or Trapping Effects. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 1975–1981. [Google Scholar] [CrossRef]

- Zhu, J.J.; Ma, X.H.; Hou, B.; Chen, W.; Hao, Y. Investigation of trap states in high Al content AlGaN/GaN high electron mobility transistors by frequency dependent capacitance and conductance analysis. AIP Adv. 2014, 4, 8070–8215. [Google Scholar] [CrossRef]

- Gupta, S.D.; Sun, M.; Armstrong, A.; Kaplar, R.J.; Marinella, M.J.; Stanley, J.B.; Atcitty, S.; Palacios, T. Slow Detrapping Transients due to Gate and Drain Bias Stress in High Breakdown Voltage AlGaN/GaN HEMTs. IEEE Trans. Electron Dev. 2012, 59, 2115–2122. [Google Scholar] [CrossRef]

- Wells, A.M.; Uren, M.J.; Balmer, R.S.; Hilton, K.P.; Martin, T.; Missous, M. Direct demonstration of the virtual gate mechanism for current collapse in AlGaN/GaN HFETs. Solid-State Electron. Lett. 2005, 49, 279–282. [Google Scholar] [CrossRef]

- Trew, R.J.; Green, D.S.; Shealy, J.B. AlGaN/GaN HFET Reliability. IEEE Microw. Mag. 2009, 10, 116–127. [Google Scholar] [CrossRef]

- GS66502B Bottom-Side Cooled 650 V E-Mode GaN Transistor Preliminary Datasheet, Rev-181214; GaN Syst. Inc.: Ottawa, ON, Canada, 2009–2018.

- Yao, T.; Ayyanar, R. A Multifunctional Double Pulse Tester for Cascode GaN Devices. IEEE Trans. Ind. Electron. 2017, 64, 9023–9031. [Google Scholar] [CrossRef]

- Rossetto, I. Evidence of Hot-Electron Effects during Hard Switching of AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2017, 64, 3734–3739. [Google Scholar] [CrossRef]

- Double Pulse Testing Power Semiconductor Devices with a 5 or 6 Series MSO with Built-in Arbitrary Function Generator, Application Note, Tektronix. Available online: https://www.tek.com.cn/documents/application-note/double-pulse-testing-power-semiconductor-devices-with-a-5-or-6-series-mso-with-built-in-afg (accessed on 12 February 2023).

- Cabizza, S.; Spiazzi, G.; Corradini, L. GaN-Based Isolated Resonant Converter as a Backup Power Supply in Automotive Subnets. IEEE Trans. Power Electron. 2023, 38, 7362–7373. [Google Scholar] [CrossRef]

- Park, J.; Roh, Y.S.; Moon, Y.J.; Yoo, C. A CCM/DCM Dual-Mode Synchronous Rectification Controller for a High-Efficiency Flyback Converter. IEEE T Power Electron. 2014, 29, 768–774. [Google Scholar] [CrossRef]

- Shen, M.; Krishnamurthy, S. Simplified loss analysis for high speed SiC MOSFET inverter. In Proceedings of the 27th Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012; pp. 1682–1687. [Google Scholar] [CrossRef]

- Chern, J.G.J.; Chang, P.; Motta, R.F.; Godinho, N. A New Method to Determine MOSFET Channel Length. IEEE Electron Device Lett. 1980, 9, 170–173. [Google Scholar] [CrossRef]

- Roscoe, N.; McNeill, N.; Finney, S. A simple technique to optimize SiC device selection for minimum loss. In Proceedings of the 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. P.1–P.13. [Google Scholar] [CrossRef]

- Zhao, Q.; Stojcic, G. Characterization of Cdv/dt Induced Power Loss in Synchronous Buck DC–DC Converters. IEEE Trans. Power Electron. 2007, 22, 1508–1513. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lei, J.; Liu, Y.; Yang, Z.; Chen, Y.; Chen, D.; Xu, L.; Yu, J. An Analytical Model of Dynamic Power Losses in eGaN HEMT Power Devices. Micromachines 2023, 14, 1633. https://doi.org/10.3390/mi14081633

Lei J, Liu Y, Yang Z, Chen Y, Chen D, Xu L, Yu J. An Analytical Model of Dynamic Power Losses in eGaN HEMT Power Devices. Micromachines. 2023; 14(8):1633. https://doi.org/10.3390/mi14081633

Chicago/Turabian StyleLei, Jianming, Yangyi Liu, Zhanmin Yang, Yalin Chen, Dunjun Chen, Liang Xu, and Jing Yu. 2023. "An Analytical Model of Dynamic Power Losses in eGaN HEMT Power Devices" Micromachines 14, no. 8: 1633. https://doi.org/10.3390/mi14081633

APA StyleLei, J., Liu, Y., Yang, Z., Chen, Y., Chen, D., Xu, L., & Yu, J. (2023). An Analytical Model of Dynamic Power Losses in eGaN HEMT Power Devices. Micromachines, 14(8), 1633. https://doi.org/10.3390/mi14081633