A Buried Thermal Rail (BTR) Technology to Improve Electrothermal Characteristics of Complementary Field-Effect Transistor (CFET)

Abstract

:1. Introduction

2. Modeling Methodology

3. Results and Discussion

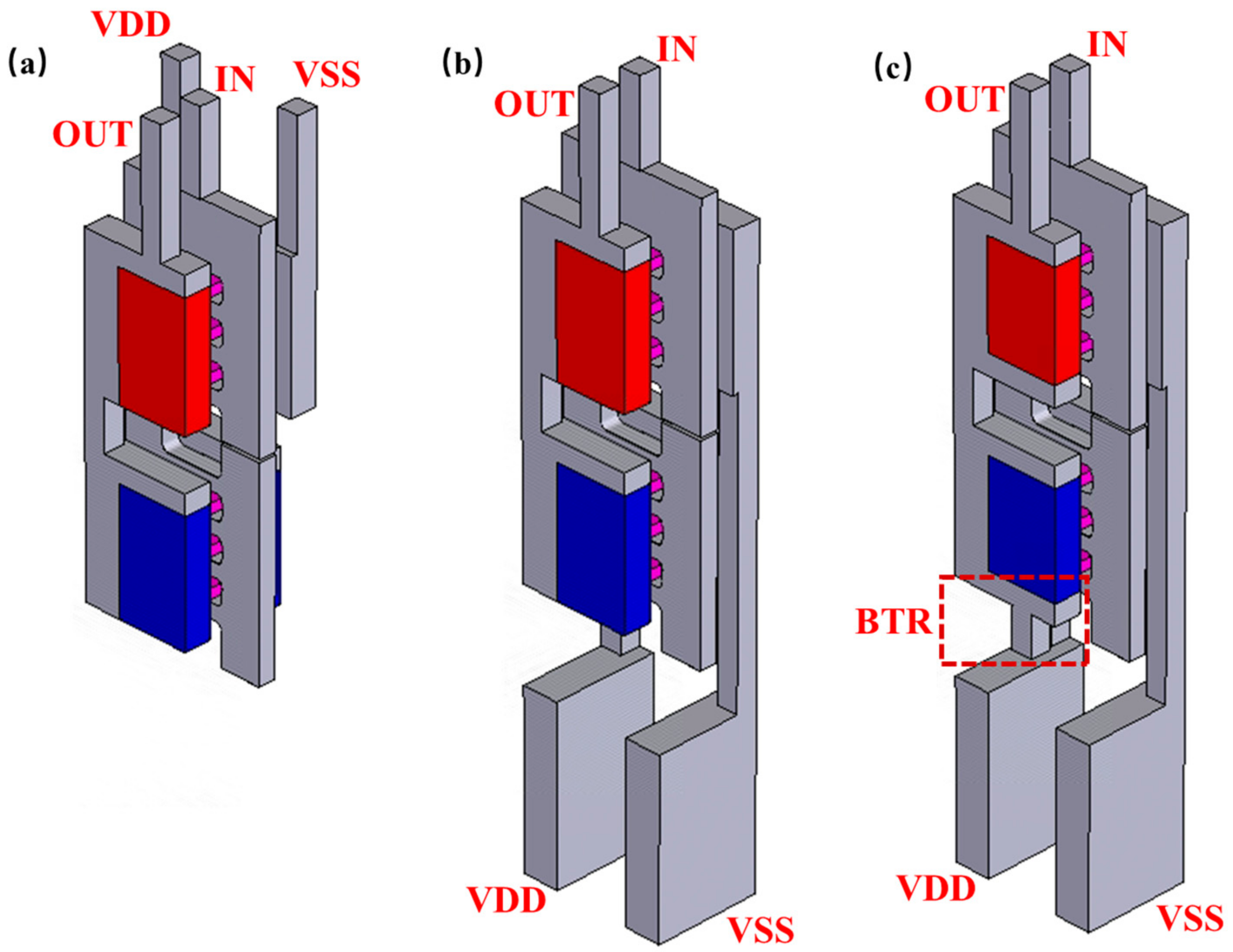

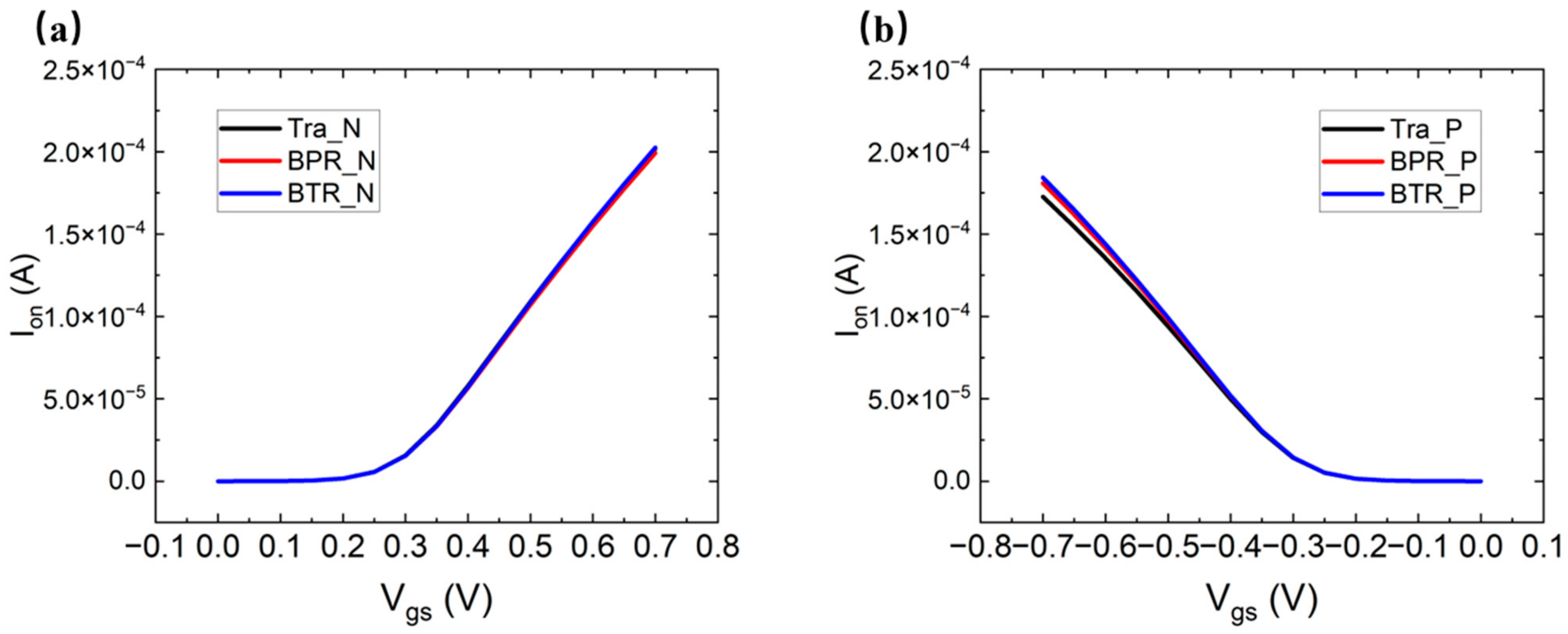

3.1. Buried Thermal Rial

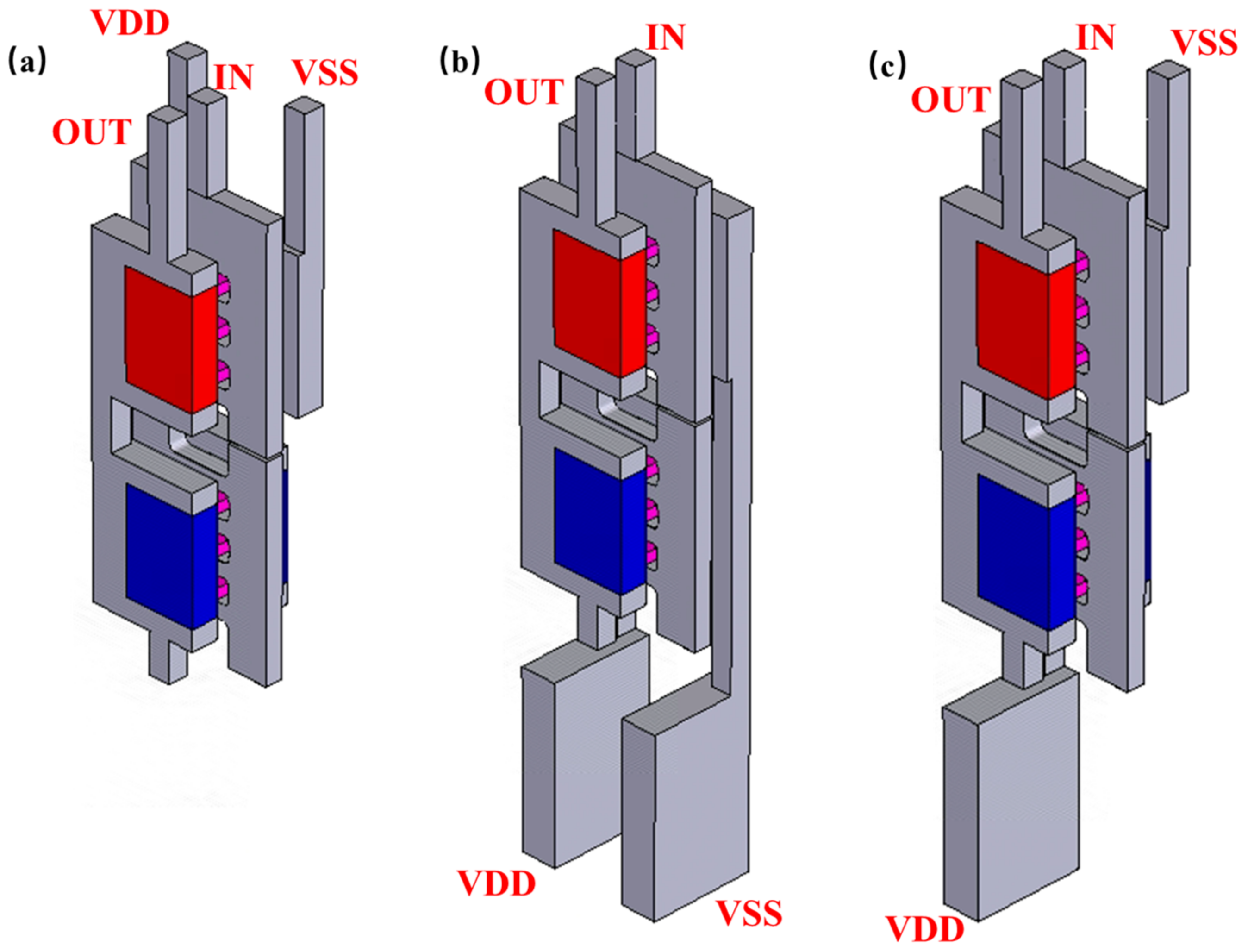

3.2. Power Delivery Network

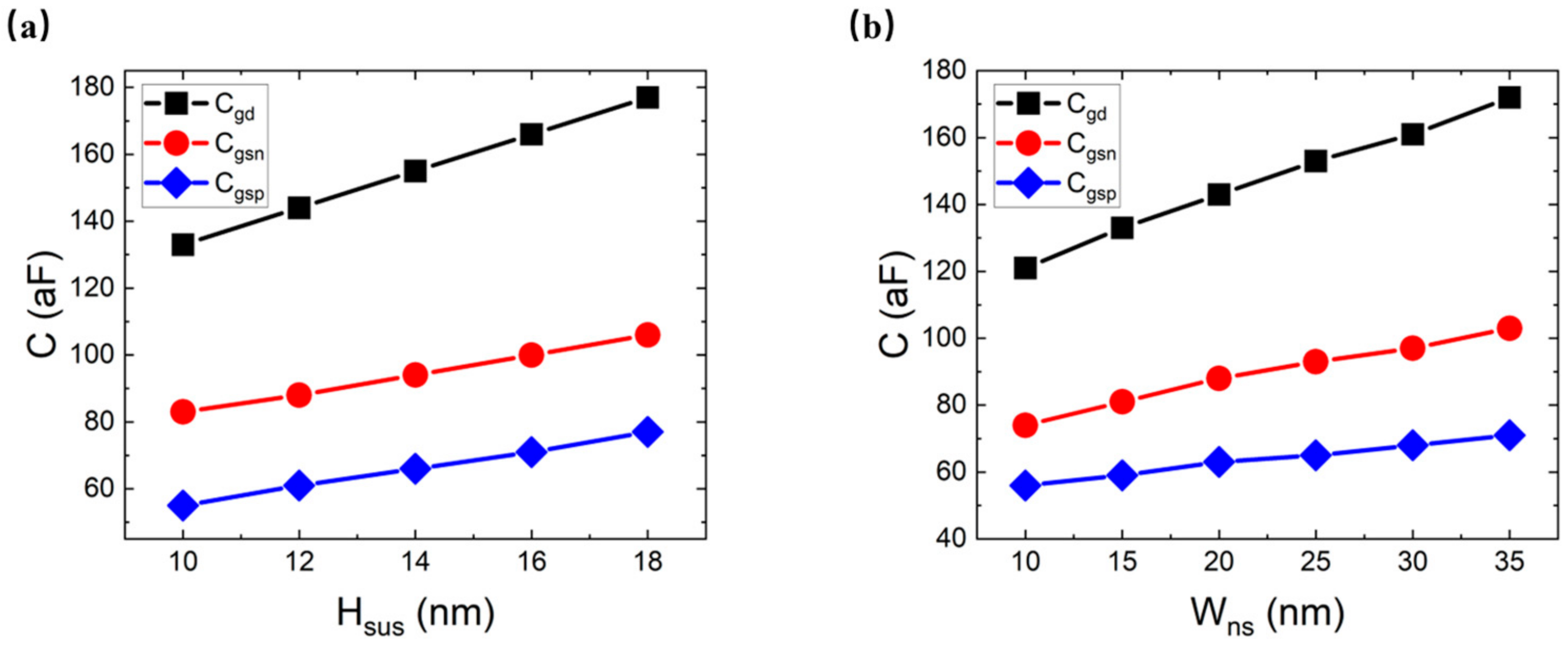

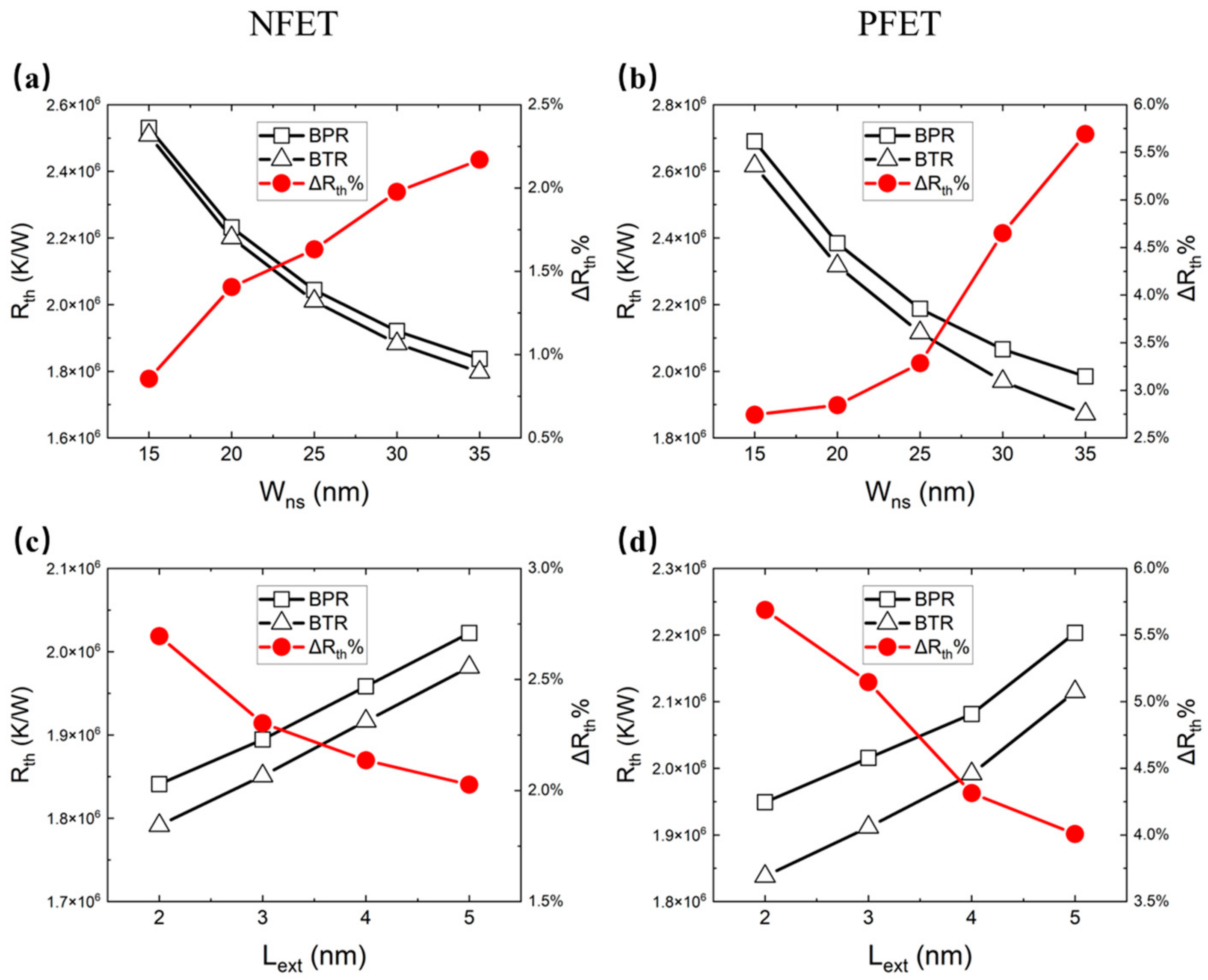

3.3. Characteristics of CFET for Different Dimension Parameters

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- IEEE International Roadmap for Devices and Systems (IRDS™) 2022 Edition. Available online: https://irds.ieee.org/editions/2022 (accessed on 30 December 2022).

- Yoon, J.-S.; Baek, R.-H. Device Design Guideline of 5-nm-Node FinFETs and Nanosheet FETs for Analog/RF Applications. IEEE Access 2020, 8, 189395–189403. [Google Scholar] [CrossRef]

- Yakimets, D.; Bardon, M.G.; Jang, D.; Schuddinck, P.; Sherazi, Y.; Weckx, P.; Miyaguchi, K.; Parvais, B.; Raghavan, P.; Spessot, A.; et al. Power aware FinFET and lateral nanosheet FET targeting for 3 nm CMOS technology. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 20.4.1–20.4.4. [Google Scholar] [CrossRef]

- Bardon, M.G.; Sherazi, Y.; Jang, D.; Yakimets, D.; Schuddinck, P.; Baert, R.; Mertens, H.; Mattii, L.; Parvais, B.; Mocuta, A.; et al. Power-performance Trade-offs for Lateral NanoSheets on Ultra-Scaled Standard Cells. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 143–144. [Google Scholar] [CrossRef]

- Chang, S.-W.; Huang, M.-K.; Huang, S.-T.; Wang, H.-C.; Wang, J.-Y.; Yu, L.-W.; Huang, Y.-F.; Hsueh, F.-K.; Sung, P.-J.; Wu, C.-T.; et al. First Demonstration of CMOS Inverter and 6T-SRAM Based on GAA CFETs Structure for 3D-IC Applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 11.7.1–11.7.4. [Google Scholar] [CrossRef]

- Ryckaert, J.; Schuddinck, P.; Weckx, P.; Bouche, G.; Vincent, B.; Smith, J.; Sherazi, Y.; Mallik, A.; Mertens, H.; Demuynck, S.; et al. The Complementary FET (CFET) for CMOS scaling beyond N3. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 141–142. [Google Scholar] [CrossRef]

- Huang, C.-Y.; Dewey, G.; Mannebach, E.; Phan, A.; Morrow, P.; Rachmady, W.; Tung, I.-C.; Thomas, N.; Alaan, U.; Paul, R.; et al. 3-D Self-aligned Stacked NMOS-on-PMOS Nanoribbon Transistors for Continued Moore’s Law Scaling. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 20.6.1–20.6.4. [Google Scholar] [CrossRef]

- Jiang, L.; Pal, A.; Bazizi, E.M.; Saremi, M.; Ren, H.; Alexander, B.; Ayyagari-Sangamalli, B. Complementary FET Device and Circuit Level Evaluation Using Fin-Based and Sheet-Based Configurations Targeting 3nm Node and Beyond. In Proceedings of the 2020 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Kobe, Japan, 23 September–6 October 2020; pp. 323–326. [Google Scholar] [CrossRef]

- Jung, S.-G.; Jang, D.; Min, S.-J.; Park, E.; Yu, H.-Y. Performance Analysis on Complementary FET (CFET) Relative to Standard CMOS With Nanosheet FET. IEEE J. Electron Devices Soc. 2022, 10, 78–82. [Google Scholar] [CrossRef]

- Sun, B.; Xu, Z.; Ding, R.; Yang, J.; Chen, K.; Xu, S.; Xu, M.; Lu, Y.; Zhu, X.; Yu, S.; et al. Analytical Model of CFET Parasitic Capacitance for Advanced Technology Nodes. IEEE Trans. Electron Devices 2022, 69, 936–941. [Google Scholar] [CrossRef]

- Yang, X.; Sun, Y.; Liu, Z.; Liu, Y.; Li, X.; Shi, Y. 3-D Modeling of Fringe Gate Capacitance in Complementary FET (CFET). IEEE Trans. Electron Devices 2022, 69, 5978–5984. [Google Scholar] [CrossRef]

- Myeong, I.; Song, I.; Kang, M.J.; Shin, H. Self-Heating and Electrothermal Properties of Advanced Sub-5-nm Node Nanoplate FET. IEEE Electron Device Lett. 2020, 41, 977–980. [Google Scholar] [CrossRef]

- Bury, E.; Kaczer, B.; Linten, D.; Witters, L.; Mertens, H.; Waldron, N.; Zhou, X.; Collaert, N.; Horiguchi, N.; Spessot, A.; et al. Self-heating in FinFET and GAA-NW using Si, Ge and III/V channels. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 15.6.1–15.6.4. [Google Scholar] [CrossRef]

- Takahashi, T.; Beppu, N.; Chen, K.; Oda, S.; Uchida, K. Thermal-aware device design of nanoscale bulk/SOI FinFETs: Suppression of operation temperature and its variability. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 34.6.1–34.6.4. [Google Scholar] [CrossRef]

- Jung, S.-G.; Jang, D.; Min, S.-J.; Park, E.; Yu, H.-Y. Device Design Guidelines of 3-nm Node Complementary FET (CFET) in Perspective of Electrothermal Characteristics. IEEE Access 2022, 10, 41112–41118. [Google Scholar] [CrossRef]

- Zhao, S.; Cai, L.; Chen, W.; He, Y.; Du, G. Self-Heating and Thermal Network Model for Complementary FET. IEEE Trans. Electron Devices 2021, 69, 11–16. [Google Scholar] [CrossRef]

- Prasad, D.; Nibhanupudi, S.S.T.; Das, S.; Zografos, O.; Chehab, B.; Sarkar, S.; Baert, R.; Robinson, A.; Gupta, A.; Spessot, A.; et al. Buried Power Rails and Back-side Power Grids: Arm® CPU Power Delivery Network Design beyond 5 nm. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 19.1.1–19.1.4. [Google Scholar] [CrossRef]

- Subramanian, S.; Hosseini, M.; Chiarella, T.; Sarkar, S.; Schuddinck, P.; Chan, B.T.; Radisic, D.; Mannaert, G.; Hikavyy, A.; Rosseel, E.; et al. First Monolithic Integration of 3D Complementary FET (CFET) on 300 mm Wafers. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar] [CrossRef]

- Schuddinck, P.; Zografos, O.; Weckx, P.; Matagne, P.; Sarkar, S.; Sherazi, Y.; Baert, R.; Jang, D.; Yakimets, D.; Gupta, A.; et al. Device-, Circuit- & Block-level evaluation of CFET in a 4 track library. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019; pp. T204–T205. [Google Scholar] [CrossRef]

- Liu, W.; Etessam-Yazdani, K.; Hussin, R.; Asheghi, M. Modeling and Data for Thermal Conductivity of Ultrathin Single-Crystal SOI Layers at High Temperature. IEEE Trans. Electron Devices 2006, 53, 1868–1876. [Google Scholar] [CrossRef]

- Yan, J.-Y.; Jan, S.-R.; Peng, Y.-J.; Lin, H.H.; Wan, W.K.; Huang, Y.-H.; Hung, B.; Chan, K.-T.; Huang, M.; Yang, M.-T.; et al. Thermal resistance modeling of back-end interconnect and intrinsic FinFETs, and transient simulation of inverters with capacitive loading effects. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 35.6.1–35.6.4. [Google Scholar] [CrossRef]

- Pop, E.; Dutton, R.; Goodson, K. Thermal analysis of ultra-thin body device scaling [SOI and FinFet devices]. In Proceedings of the IEEE International Electron Devices Meeting 2003, Washington, DC, USA, 8–10 December 2003; pp. 36.6.1–36.6.4. [Google Scholar] [CrossRef]

- Liu, T.; Wang, D.; Pan, Z.; Chen, K.; Yang, J.; Wu, C.; Xu, S.; Wang, C.; Xu, M.; Zhang, D.W. Novel Postgate Single Diffusion Break Integration in Gate-All-Around Nanosheet Transistors to Achieve Remarkable Channel Stress for N/P Current Matching. IEEE Trans. Electron Devices 2022, 69, 1497–1502. [Google Scholar] [CrossRef]

| Symbol | Quantity | Values |

|---|---|---|

| Gate length | 12 nm | |

| Channel height | 5 nm | |

| Suspension height | 14 nm | |

| Gate thickness | 1.5 nm | |

| Gate thickness | 0.5 nm | |

| Spacer length | 5 nm | |

| CD of BPR | 36 nm | |

| Height of BPR | 90 nm | |

| Buried depth of BPR | 23 nm | |

| Height of MDI | 20 nm | |

| STI depth | 70 nm | |

| Metal 0 pitch | 21 nm | |

| Metal 1 pitch | 42 nm | |

| N-channel doping concentration | ||

| P-channel doping concentration | ||

| S/D epitaxy doping concentration | ||

| Extension doping concentration | ||

| S/D contact resistivity | ||

| NFET S/D material | Si | |

| PFET S/D material | SiGe (75% Ge) | |

| P-channel stress | 0.8 Gpa |

| Thermal Conductivity | |

|---|---|

| Oxide | 1.4 |

| Tungsten | 175 |

| Nitride | 18.5 |

| 2.3 | |

| Substrate | 148 |

| Channel | 7.5 |

| S/D (Si) | 5.5 |

| S/D (SiGe) | 1.0 |

| Thermal Contact Resistance | |

| Top | |

| Bottom | |

| Environment Temperature | 300 K |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pan, Z.; Liu, T.; Yang, J.; Chen, K.; Xu, S.; Wu, C.; Xu, M.; Zhang, D.W. A Buried Thermal Rail (BTR) Technology to Improve Electrothermal Characteristics of Complementary Field-Effect Transistor (CFET). Micromachines 2023, 14, 1751. https://doi.org/10.3390/mi14091751

Pan Z, Liu T, Yang J, Chen K, Xu S, Wu C, Xu M, Zhang DW. A Buried Thermal Rail (BTR) Technology to Improve Electrothermal Characteristics of Complementary Field-Effect Transistor (CFET). Micromachines. 2023; 14(9):1751. https://doi.org/10.3390/mi14091751

Chicago/Turabian StylePan, Zhecheng, Tao Liu, Jingwen Yang, Kun Chen, Saisheng Xu, Chunlei Wu, Min Xu, and David Wei Zhang. 2023. "A Buried Thermal Rail (BTR) Technology to Improve Electrothermal Characteristics of Complementary Field-Effect Transistor (CFET)" Micromachines 14, no. 9: 1751. https://doi.org/10.3390/mi14091751

APA StylePan, Z., Liu, T., Yang, J., Chen, K., Xu, S., Wu, C., Xu, M., & Zhang, D. W. (2023). A Buried Thermal Rail (BTR) Technology to Improve Electrothermal Characteristics of Complementary Field-Effect Transistor (CFET). Micromachines, 14(9), 1751. https://doi.org/10.3390/mi14091751