A Two-Dimensional Computer-Aided Design Study of Unclamped Inductive Switching in an Improved 4H-SiC VDMOSFET

Abstract

:1. Introduction

2. Description of Device Structure and Simulation

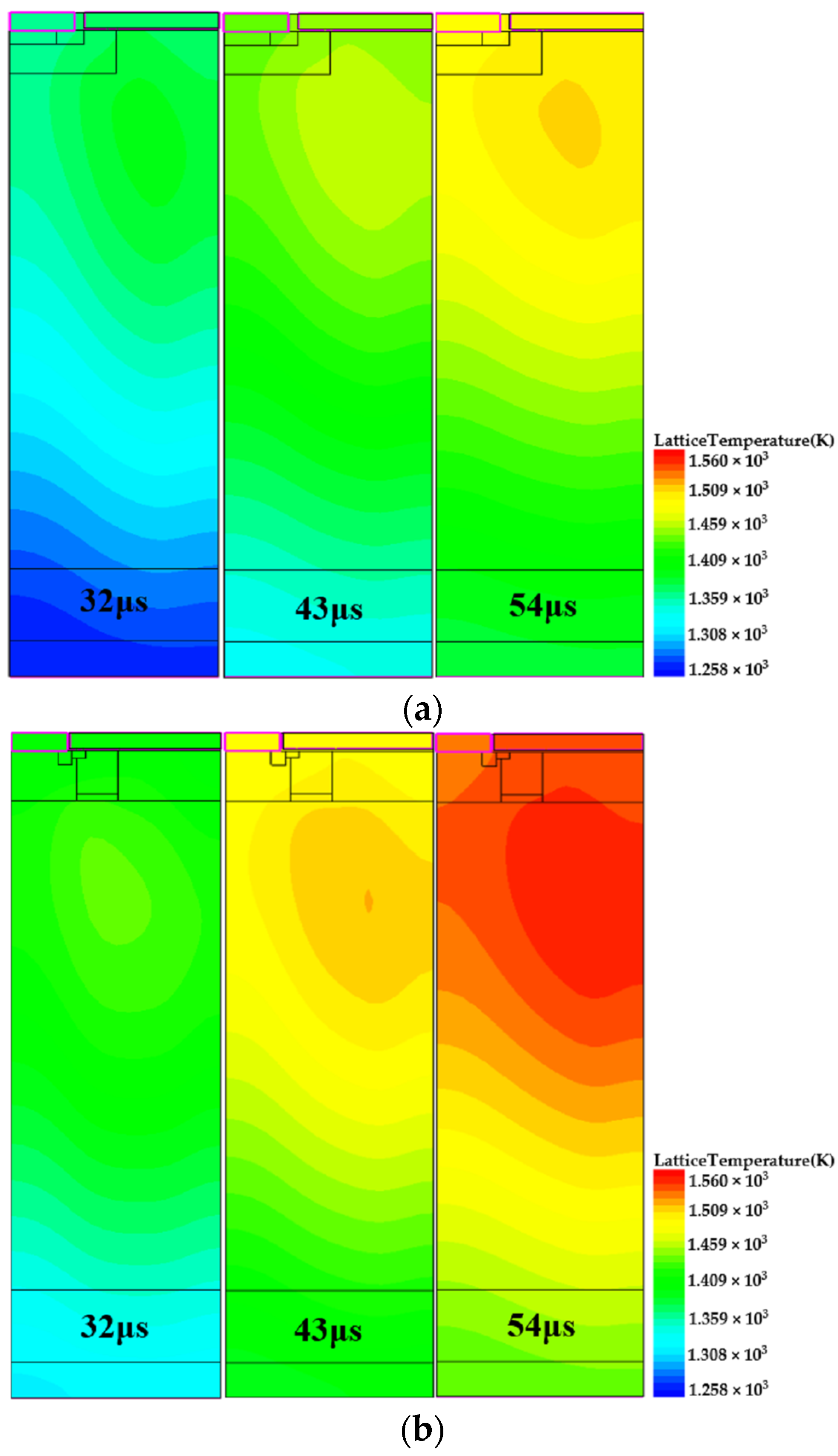

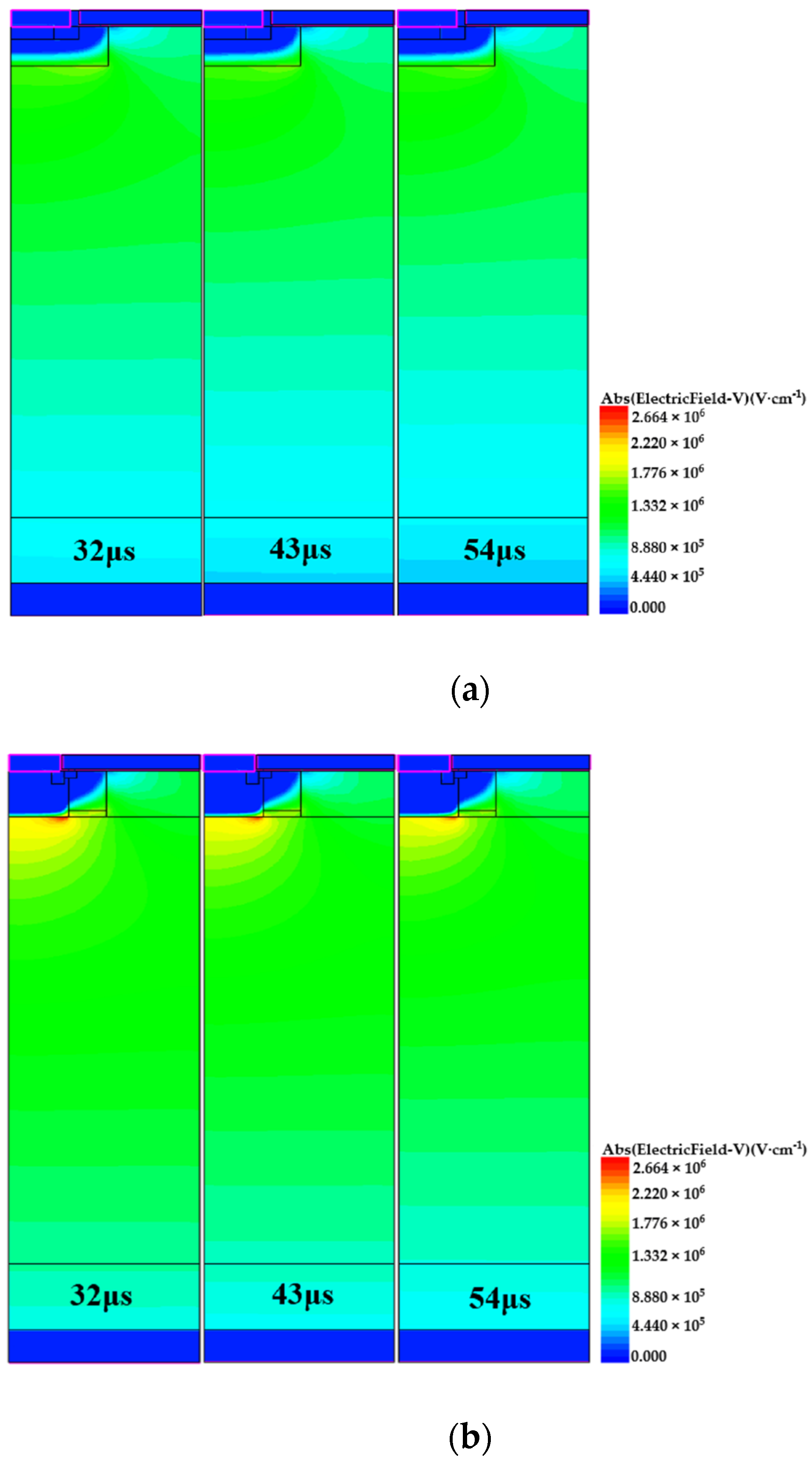

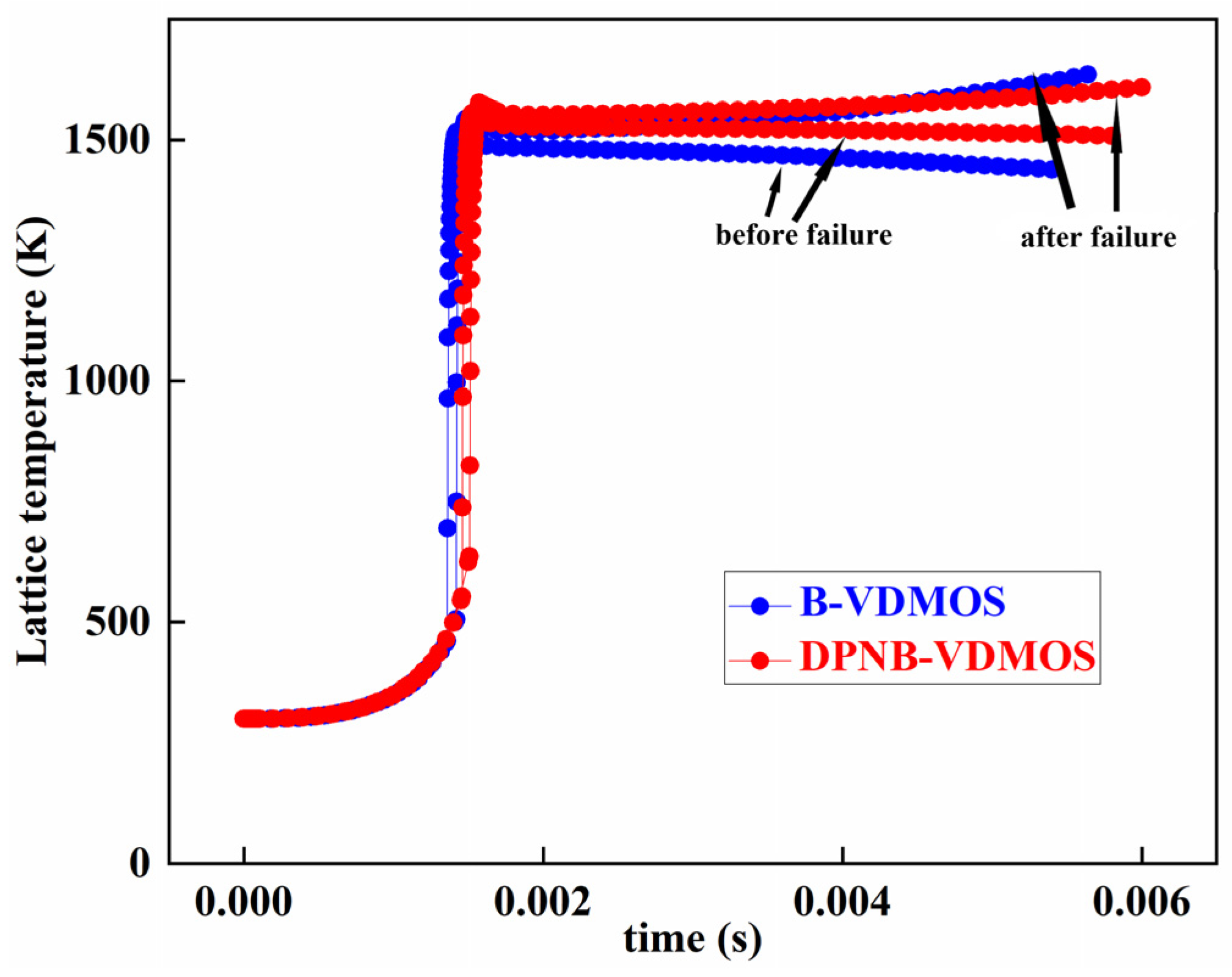

3. Numerical Simulation Results and Discussion

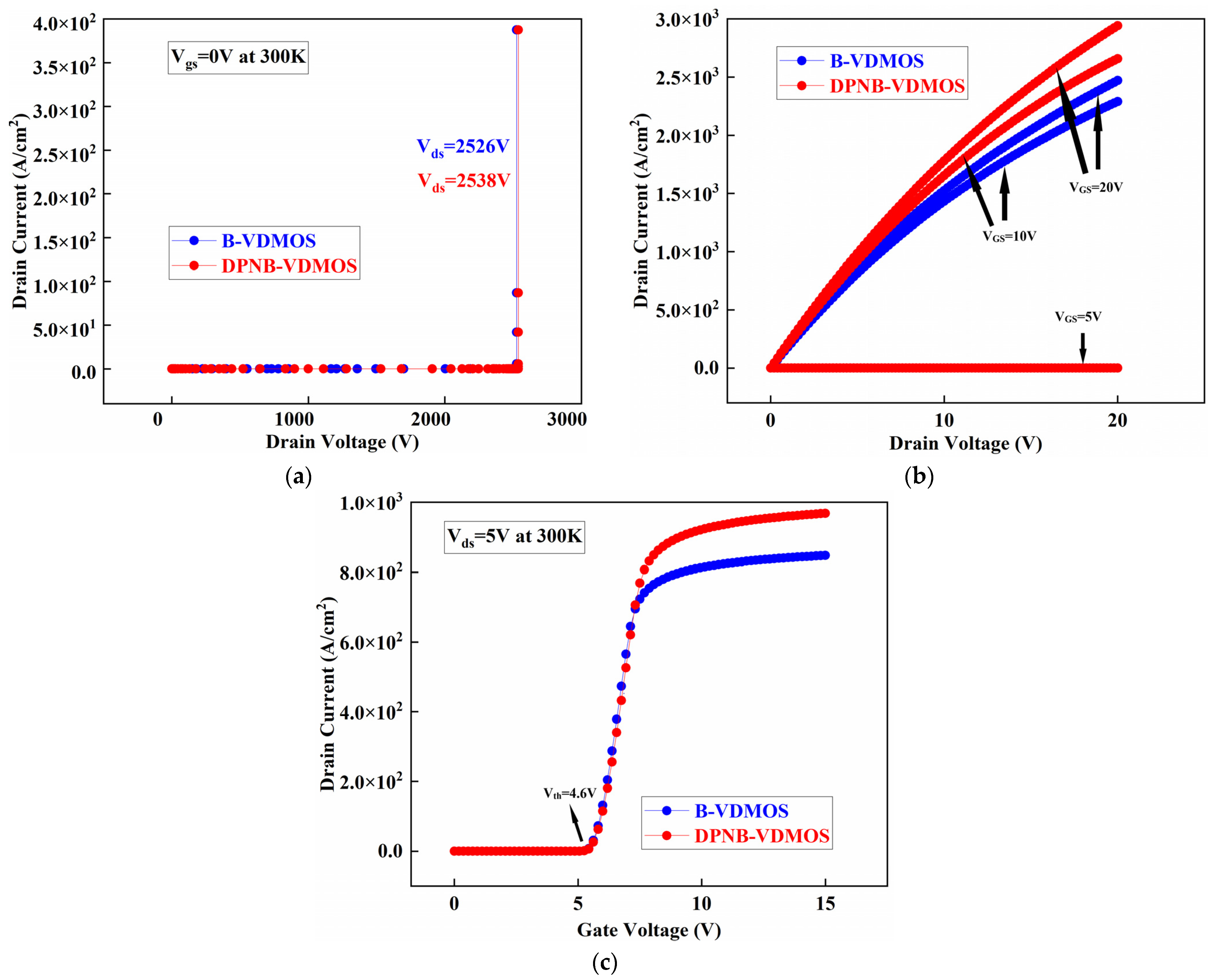

3.1. Basic Electrical Characteristics

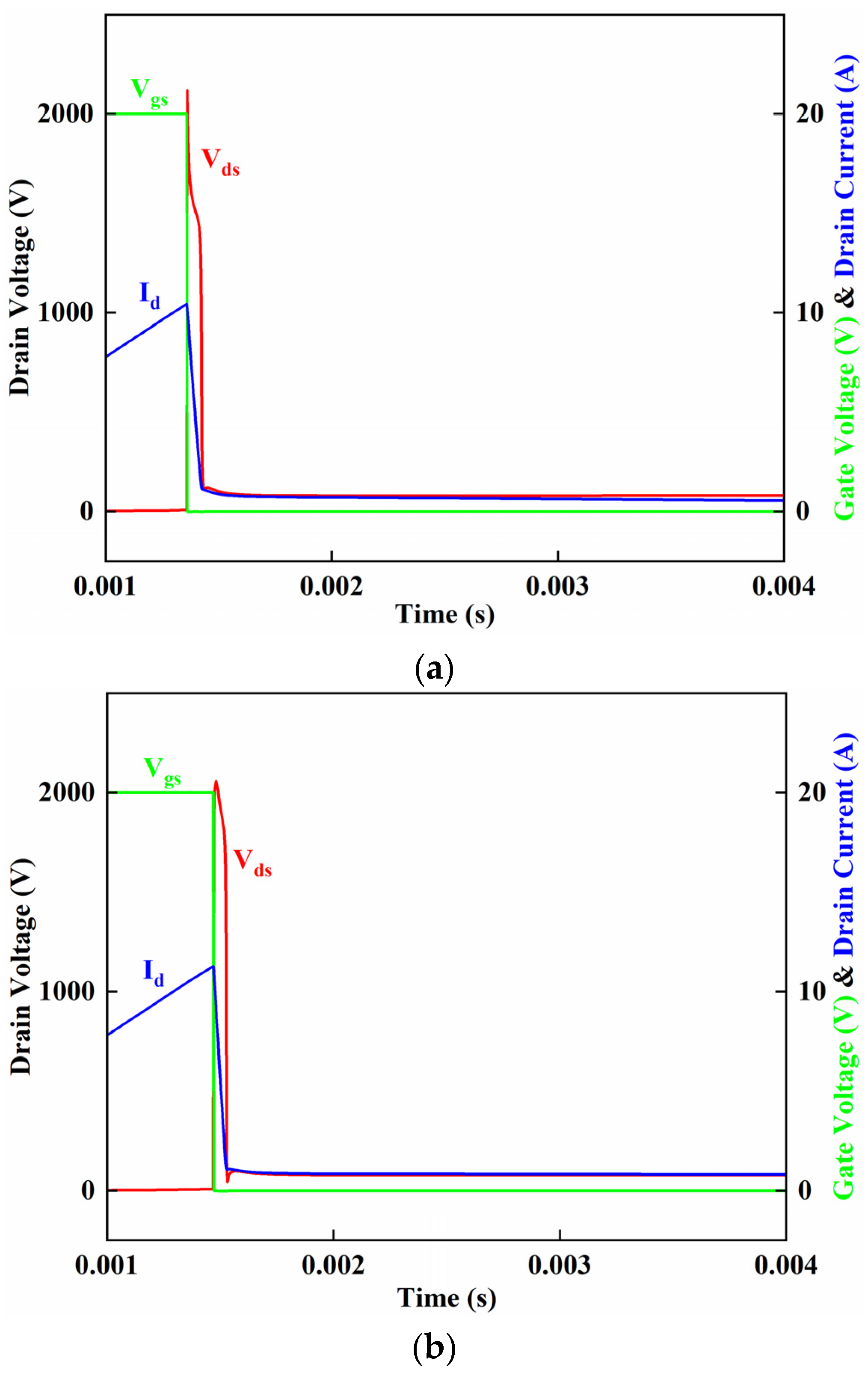

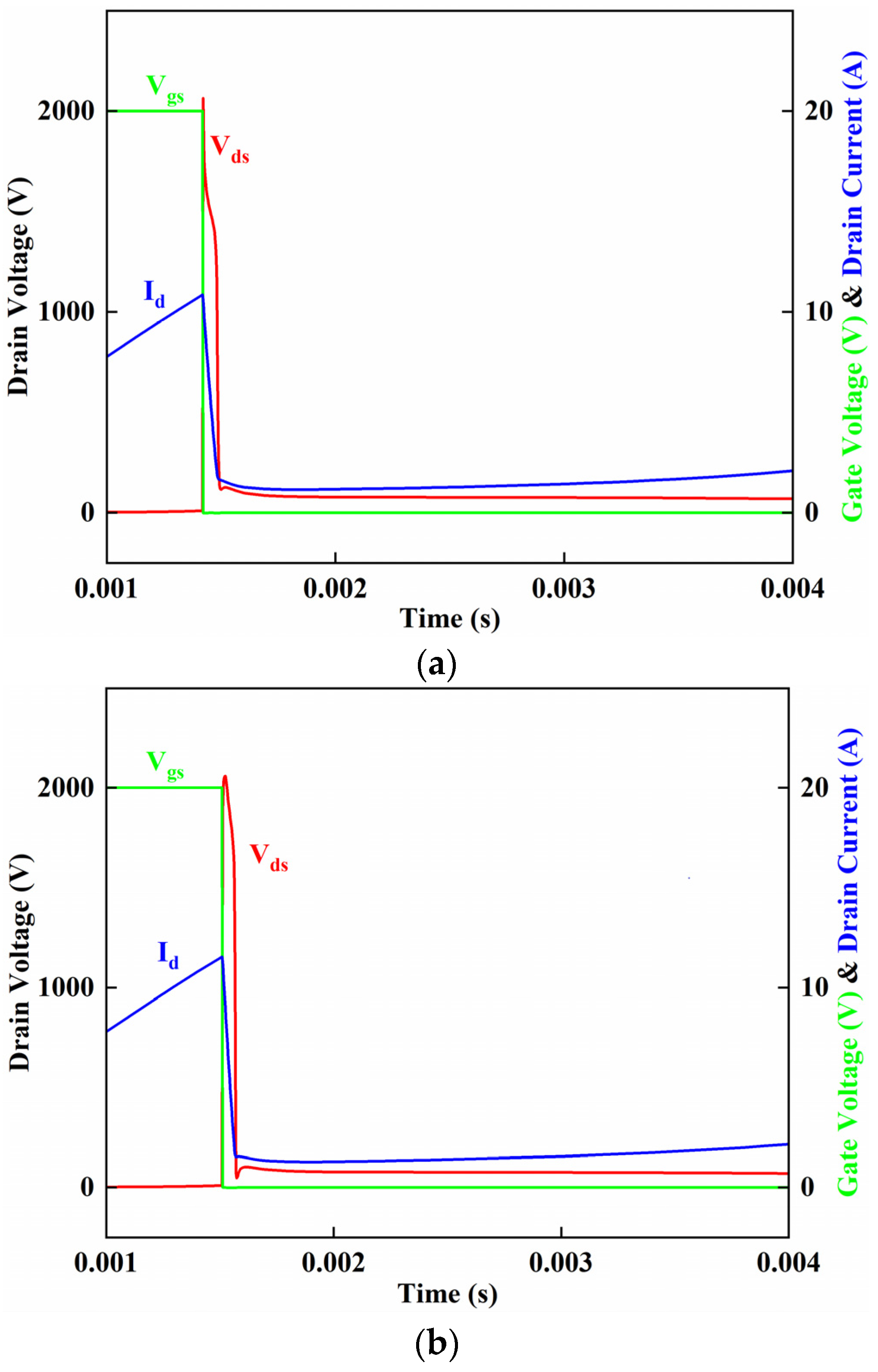

3.2. UIS Characteristic

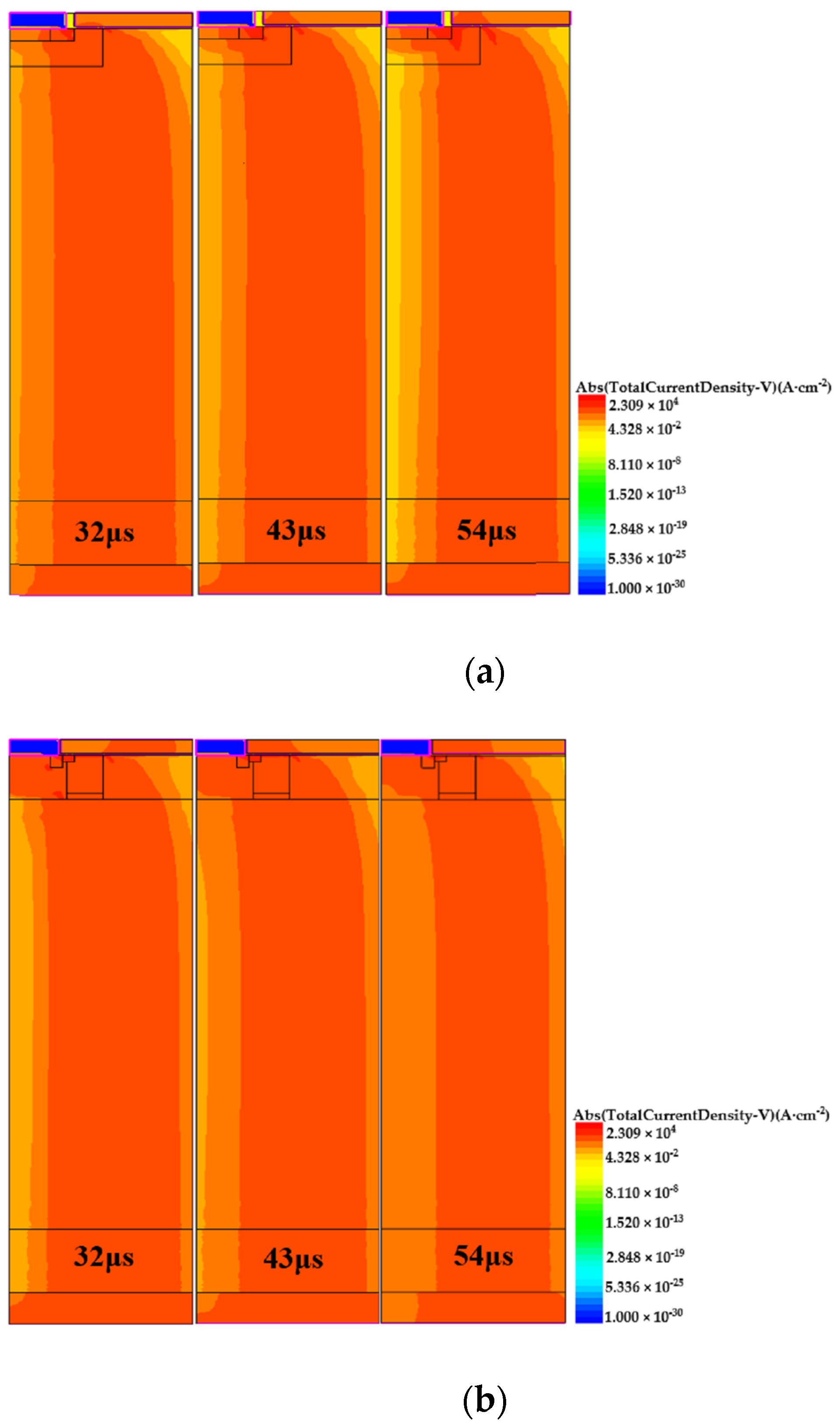

4. UIS Simulation Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Li, Z.; Li, Z.; Zuo, C.; Fang, X. Application of Nanostructured TiO2 in UV Photodetectors: A Review. Adv. Mater. 2022, 34, 2109083. [Google Scholar] [CrossRef] [PubMed]

- Li, Z.; Yan, T.; Fang, X. Low-dimensional wide-bandgap semiconductors for UV photodetectors. Nat. Rev. Mater. 2023, 8, 587–603. [Google Scholar] [CrossRef]

- Li, Z.; Hong, E.; Zhang, X.; Deng, M.; Fang, X. Perovskite-Type 2D Materials for High-Performance Photodetectors. J. Phys. Chem. Lett. 2022, 13, 1215–1225. [Google Scholar] [CrossRef] [PubMed]

- Parashar, S.; Kumar, A.; Bhattacharya, S. High Power Medium Voltage Converters Enabled by High Voltage SiC Power Devices. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 3993–4000. [Google Scholar] [CrossRef]

- Bhatnagar, M.; Baliga, B.J. Comparison of 6H-SiC, 3C-SiC, and Si for power devices. IEEE Trans. Electron Devices 1993, 40, 645–655. [Google Scholar] [CrossRef]

- Adappa, R.; Suryanarayana, K.; Hatwar, H.S.; Rao, M.R. Review of SiC based Power Semiconductor Devices and their Applications. In Proceedings of the 2019 2nd International Conference on Intelligent Computing, Instrumentation and Control Technologies (ICICICT), Kannur, India, 5–6 July 2019; pp. 1197–1202. [Google Scholar] [CrossRef]

- Williams, R.K.; Darwish, M.N.; Blanchard, R.A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The Trench Power MOSFET—Part II: Application Specific VDMOS, LDMOS, Packaging, and Reliability. IEEE Trans. Electron Devices 2017, 64, 692–712. [Google Scholar] [CrossRef]

- Kelley, M.D.; Pushpakaran, B.N.; Bayne, S.B. Single-Pulse Avalanche Mode Robustness of Commercial 1200 V/80 mΩ SiC MOSFETs. IEEE Trans. Power Electron. 2017, 32, 6405–6415. [Google Scholar] [CrossRef]

- Ren, N.; Wang, K.L.; Wu, J.; Xu, H.; Sheng, K. Failure Mechanism Analysis of SiC MOSFETs in Unclamped Inductive Switching Conditions. In Proceedings of the 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 183–186. [Google Scholar] [CrossRef]

- Fayyaz, A.; Castellazzi, A.; Romano, G.; Riccio, M.; Irace, A.; Urresti, J.; Wright, N. UIS failure mechanism of SiC power MOSFETs. In Proceedings of the 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, USA, 7–9 November 2016; pp. 118–122. [Google Scholar] [CrossRef]

- Ren, N.; Hu, H.; Wang, K.L.; Zuo, Z.; Li, R.; Sheng, K. Investigation on single pulse avalanche failure of 900V SiC MOSFETs. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 431–434. [Google Scholar] [CrossRef]

- Nida, S.; Kakarla, B.; Ziemann, T.; Grossner, U. Analysis of Current Capability of SiC Power MOSFETs under Avalanche Conditions. IEEE Trans. Electron Devices 2021, 68, 4587–4592. [Google Scholar] [CrossRef]

- Zhao, X.; Li, T.; Liang, X.; Wu, Y.; Li, C.; Zheng, Z. Investigation on SiC MOSFET’s Avalanche and Short-Circuit Failure Mechanism. In Proceedings of the 2022 IEEE 5th International Electrical and Energy Conference (CIEEC), Nangjing, China, 27–29 May 2022; pp. 3916–3921. [Google Scholar] [CrossRef]

- ACastellazzi; Fayyaz, A.; Romano, G.; Riccio, M.; Irace, A.; Urresti, J.; Wright, N. Transient out-of-SOA robustness of SiC power MOSFETs. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. 2A-3.1–2A-3.8. [Google Scholar] [CrossRef]

- Bai, Z.; Tang, X.; Xie, S.; He, Y.; Yuan, H.; Song, Q.; Zhang, Y. Investigation on Single Pulse Avalanche Failure of 1200-V SiC MOSFETs via Optimized Thermoelectric Simulation. IEEE Trans. Electron Devices 2021, 68, 1168–1175. [Google Scholar] [CrossRef]

- Qi, J.; Yang, X.; Li, X.; Chen, W.; Long, T.; Tian, K.; Hou, X.; Wang, X. Comprehensive Assessment of Avalanche Operating Boundary of SiC Planar/Trench MOSFET in Cryogenic Applications. IEEE Trans. Power Electron. 2021, 36, 6954–6966. [Google Scholar] [CrossRef]

- An, J.; Hu, S. Experimental and Theoretical Demonstration of Temperature Limitation for 4H-SiC MOSFET During Unclamped Inductive Switching. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 206–214. [Google Scholar] [CrossRef]

- Deng, X.; Zhu, H.; Li, X.; Tong, X.; Gao, S.; Wen, Y.; Bai, S.; Chen, W.; Zhou, K.; Zhang, B. Investigation and Failure Mode of Asymmetric and Double Trench SiC mosfets Under Avalanche Conditions. IEEE Trans. Power Electron. 2020, 35, 8524–8531. [Google Scholar] [CrossRef]

- Li, X.; Tong, X.; Hu, R.; Wen, Y.; Deng, X.; Sun, Y.; Chen, W.; Ba, S.; Zhang, B. Failure Mechanism of Avalanche Condition for 1200-V Double Trench SiC MOSFET. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 2147–2154. [Google Scholar] [CrossRef]

- Yao, K.; Yano, H.; Iwamuro, N. Impact of Negative Gate Bias and Inductive Load on the Single-Pulse Avalanche Capability of 1200-V SiC Trench MOSFETs. IEEE Trans. Electron Devices 2022, 69, 637–643. [Google Scholar] [CrossRef]

- Yao, K.; Yano, H.; Iwamuro, N. Investigations of UIS failure mechanism in 1.2 kV trench SiC MOSFETs using electro-thermal-mechanical stress analysis. In Proceedings of the 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 115–118. [Google Scholar]

- Wei, J.; Liu, S.; Li, S.; Fang, J.; Li, T.; Sun, W. Comprehensive Investigations on Degradations of Dynamic Characteristics for SiC Power MOSFETs Under Repetitive Avalanche Shocks. IEEE Trans. Power Electron. 2019, 34, 2748–2757. [Google Scholar] [CrossRef]

- Mao, H.; Qiu, G.; Jiang, X.; Jiang, H.; Zhong, X.; Tang, L.; Zhang, Y.; Ran, L.; Wu, Y. Investigation on the Degradations of Parallel-Connected 4H-SiC MOSFETs under Repetitive UIS Stresses. IEEE Trans. Electron Devices 2022, 69, 650–657. [Google Scholar] [CrossRef]

- Zhou, X.; Su, H.; Yue, R.; Dai, G.; Li, J.; Wang, Y.; Yu, Z. A Deep Insight Into the Degradation of 1.2-kV 4H-SiC mosfets under Repetitive Unclamped Inductive Switching Stresses. IEEE Trans. Power Electron. 2018, 33, 5251–5261. [Google Scholar] [CrossRef]

- Liu, S.; Gu, C.; Wei, J.; Qian, Q.; Sun, W.; Huang, A.Q. Repetitive Unclamped-Inductive-Switching-Induced Electrical Parameters Degradations and Simulation Optimizations for 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2016, 63, 4331–4338. [Google Scholar] [CrossRef]

- Deng, X.; Huang, W.; Li, X.; Li, X.; Chen, C.; Wen, Y.; Ding, J.; Chen, W.; Sun, Y.; Zhang, B. Investigation of Failure Mechanisms of 1200 V Rated Trench SiC MOSFETs under Repetitive Avalanche Stress. IEEE Trans. Power Electron. 2022, 37, 10562–10571. [Google Scholar] [CrossRef]

- Marek, J.; Minárik, M.; Matúš, M.; Kozárik, J.; Stuchlíková, L. SiC Power TrenchMOS Transistor under harsh repetitive switching conditions. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023; pp. 1–8. [Google Scholar] [CrossRef]

- Marek, J.; Kozárik, J.; Minárik, M.; Chvála, A.; Matúš, M.; Stuchlíková, L. SiC Power TrenchMOS Transistor Under Repetitive Avalanche Stress. In Proceedings of the 2022 14th International Conference on Advanced Semiconductor Devices and Microsystems (ASDAM), Smolenice, Slovakia, 23–26 October 2022; pp. 1–4. [Google Scholar] [CrossRef]

- Zhu, Z.; Ren, N.; Xu, H.; Liu, L.; Sheng, K. Characterization and Analysis on Performance and Avalanche Reliability of SiC MOSFETs with Varied JFET Region Width. IEEE Trans. Electron Devices 2021, 68, 3982–3990. [Google Scholar] [CrossRef]

- Liu, S.; Titus, J.L.; Boden, M. Effect of Buffer Layer on Single-Event Burnout of Power DMOSFETs. IEEE Trans. Nucl. Sci. 2007, 54, 2554–2560. [Google Scholar] [CrossRef]

- Luo, J.-H.; Wang, Y.; Bao, M.-T.; Li, X.-J.; Yang, J.-Q.; Cao, F. Simulation Study of Single-Event Burnout Reliability for 1.7-kV 4H-SiC VDMOSFET. IEEE Trans. Device Mater. Reliab. 2022, 22, 431–437. [Google Scholar] [CrossRef]

- Goh, J.; Kim, K. High Efficiency 1700V 4H-SiC UMOSFET with Local Floating Superjunction. In Proceedings of the 2020 International Conference on Electronics, Information, and Communication (ICEIC), Barcelona, Spain, 19–22 January 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Titus, J.L.; Wheatley, C.F.; Van Tyne, K.M.; Krieg, J.F.; Burton, D.I.; Campbell, A.B. Effect of ion energy upon dielectric breakdown of the capacitor response in vertical power MOSFETs. IEEE Trans. Nucl. Sci. 1998, 45, 2492–2499. [Google Scholar] [CrossRef]

- Abbate, C.; Busatto, G.; Tedesco, D.; Sanseverino, A.; Velardi, F.; Wyss, J. Gate Damages Induced in SiC Power MOSFETs During Heavy-Ion Irradiation—Part II. IEEE Trans. Electron Devices 2019, 66, 4243–4250. [Google Scholar] [CrossRef]

- ATLAS User’s Manual: Device Simulation Software; Silvaco: Santa Clara, CA, USA, 2018.

- Zhou, J.-C.; Wang, Y.; Li, X.-J.; Yang, J.-Q.; Bao, M.-T.; Cao, F. Simulation Study of Single-Event Effects for the 4H-SiC VDMOSFET With Ultralow On-Resistance. IEEE Trans. Electron Devices 2022, 69, 3283–3289. [Google Scholar] [CrossRef]

- Chen, H.; Wang, J.; Dong, R.; Yao, J.; Liang, S. Investigation on Single Pulse Avalanche Failure of 3.3kV planar-SiC power MOSFETs. In Proceedings of the 2023 IEEE PELS Students and Young Professionals Symposium (SYPS), Shanghai, China, 27–29 August 2023; pp. 1–5. [Google Scholar] [CrossRef]

- Wang, Z.; Shi, X.; Tolbet, L.M.; Wang, F.; Liang, Z.; Costinett, D.; Blalock, B.J. Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs. IEEE Trans. Power Electron. 2016, 31, 1555–1566. [Google Scholar] [CrossRef]

- Zhu, Z.; Ren, N.; Xu, H.; Liu, L.; Sheng, K. Avalanche Reliability of Planar-gate SiC MOSFET with Varied JFET Region Width and Its Balance with Characteristic Performance. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 231–234. [Google Scholar] [CrossRef]

- Gao, Z.; Cao, L.; Guo, Q.; Sheng, K. Experimental Investigation of the Single Pulse Avalanche Ruggedness of SiC Power MOSFETs. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 2601–2604. [Google Scholar] [CrossRef]

| Structure Parameters | B-VDMOSFET | DPNB-VDMOSFET |

|---|---|---|

| Cell pitch | 9.0 | 9.0 |

| P-base doping concentration (cm−3) | 2.0 × 1017 | 2.0 × 1017 |

| Drift doping concentration (cm−3) | 3.0 × 1015 | 3.0 × 1015 |

| Buffer layer doping concentration (cm−3) | 5.0 × 1015 | 5.0 × 1015 |

| CSL doping concentration (cm−3) | – | 6.0 × 1015 |

| Deep P+ doping Concentration (cm−3) | – | 1.0 × 1018 |

| N− region near N+ doping Concentration (cm−3) | – | 1.0 × 1017 |

| N+ region Concentration (cm−3) | 1.0 × 1019 | 1.0 × 1019 |

| P+ region Concentration (cm−3) | 1.0 × 1019 | – |

| N− region below P-base doping Concentration (cm−3) | – | 1.0 × 1015 |

| Gate oxide Thickness (μm) | 0.05 | 0.05 |

| N+ substrate region Concentration (cm−3) | 1.0 × 1019 | 1.0 × 1019 |

| Structure Name | The Improvement in Avalanche Energy | The Reduction in Ron,sp (mΩ·cm2) | BV (V) |

|---|---|---|---|

| SiC MOSFETs with varied JFET region width [39] | 6.3% | 0.5 | 1200 |

| Asymmetric Trench SiC MOSFET [18] | 13.8% | 0.1 | 1200 |

| SiC planar MOSFET [40] | 13.3% | - | 900 |

| This work | 20% | 1.0 | 1700 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nie, X.; Wang, Y.; Yu, C.; Fei, X.; Yang, J.; Li, X. A Two-Dimensional Computer-Aided Design Study of Unclamped Inductive Switching in an Improved 4H-SiC VDMOSFET. Micromachines 2024, 15, 35. https://doi.org/10.3390/mi15010035

Nie X, Wang Y, Yu C, Fei X, Yang J, Li X. A Two-Dimensional Computer-Aided Design Study of Unclamped Inductive Switching in an Improved 4H-SiC VDMOSFET. Micromachines. 2024; 15(1):35. https://doi.org/10.3390/mi15010035

Chicago/Turabian StyleNie, Xinfeng, Ying Wang, Chenghao Yu, Xinxing Fei, Jianqun Yang, and Xingji Li. 2024. "A Two-Dimensional Computer-Aided Design Study of Unclamped Inductive Switching in an Improved 4H-SiC VDMOSFET" Micromachines 15, no. 1: 35. https://doi.org/10.3390/mi15010035

APA StyleNie, X., Wang, Y., Yu, C., Fei, X., Yang, J., & Li, X. (2024). A Two-Dimensional Computer-Aided Design Study of Unclamped Inductive Switching in an Improved 4H-SiC VDMOSFET. Micromachines, 15(1), 35. https://doi.org/10.3390/mi15010035