Comprehensive Review of FinFET Technology: History, Structure, Challenges, Innovations, and Emerging Sensing Applications

Abstract

:1. Introduction

2. History

2.1. Genesis of FinFETs

2.2. What Is Fin?

3. FinFET Structure Classification

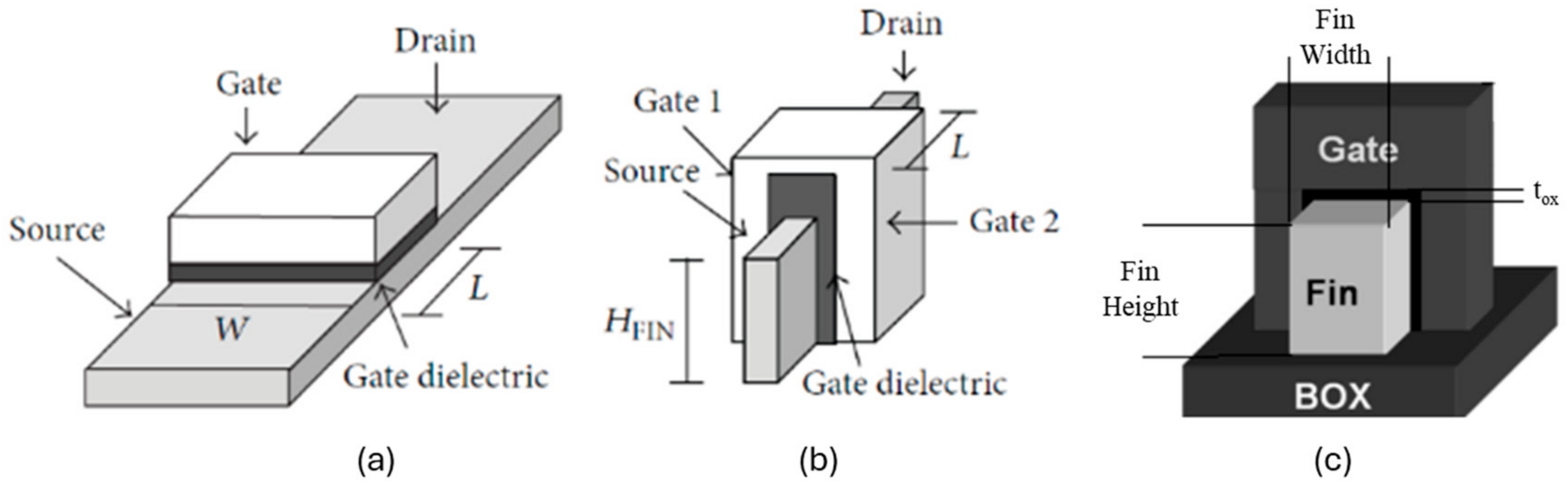

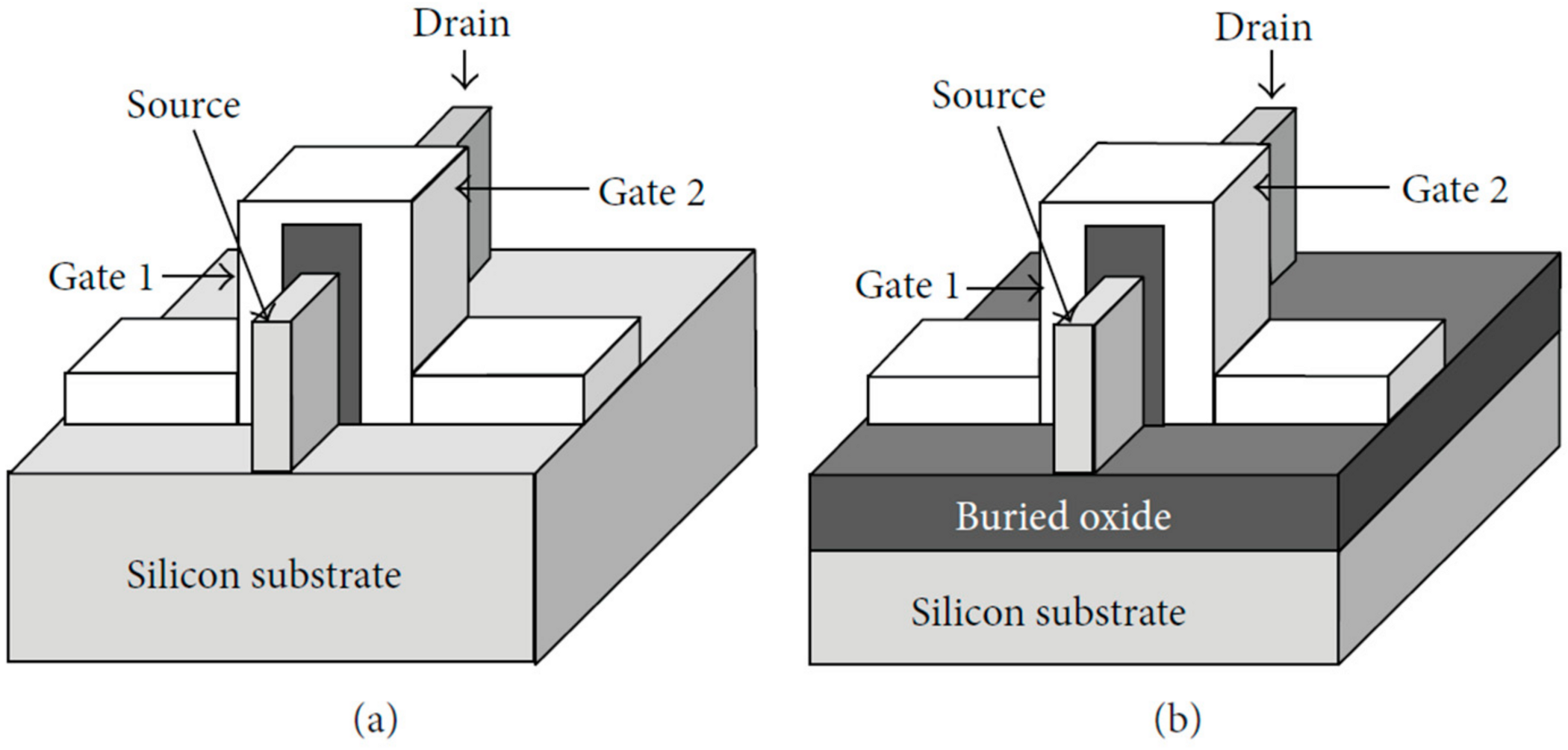

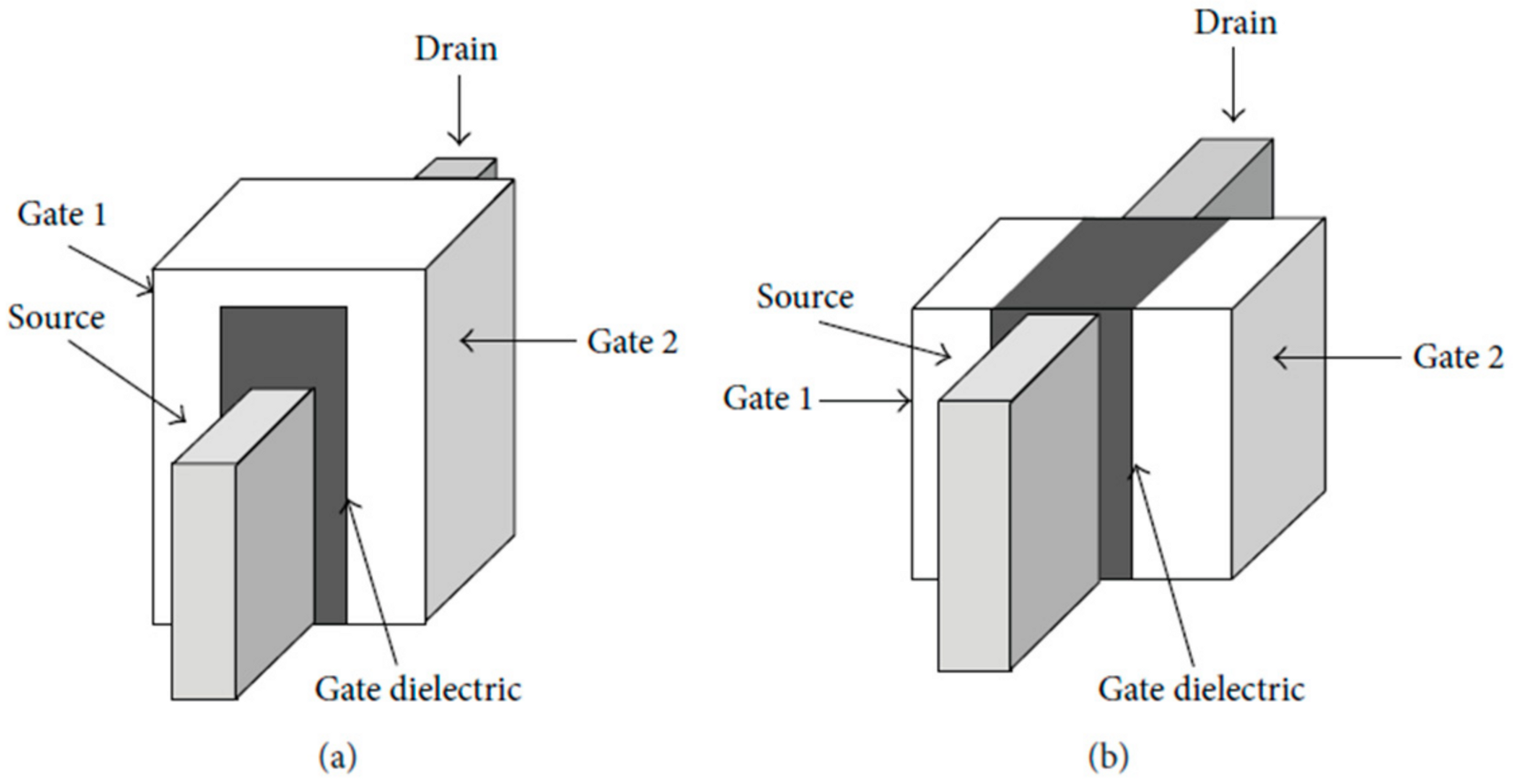

3.1. Based on Physical Structures

3.2. Based on the Number of Terminals

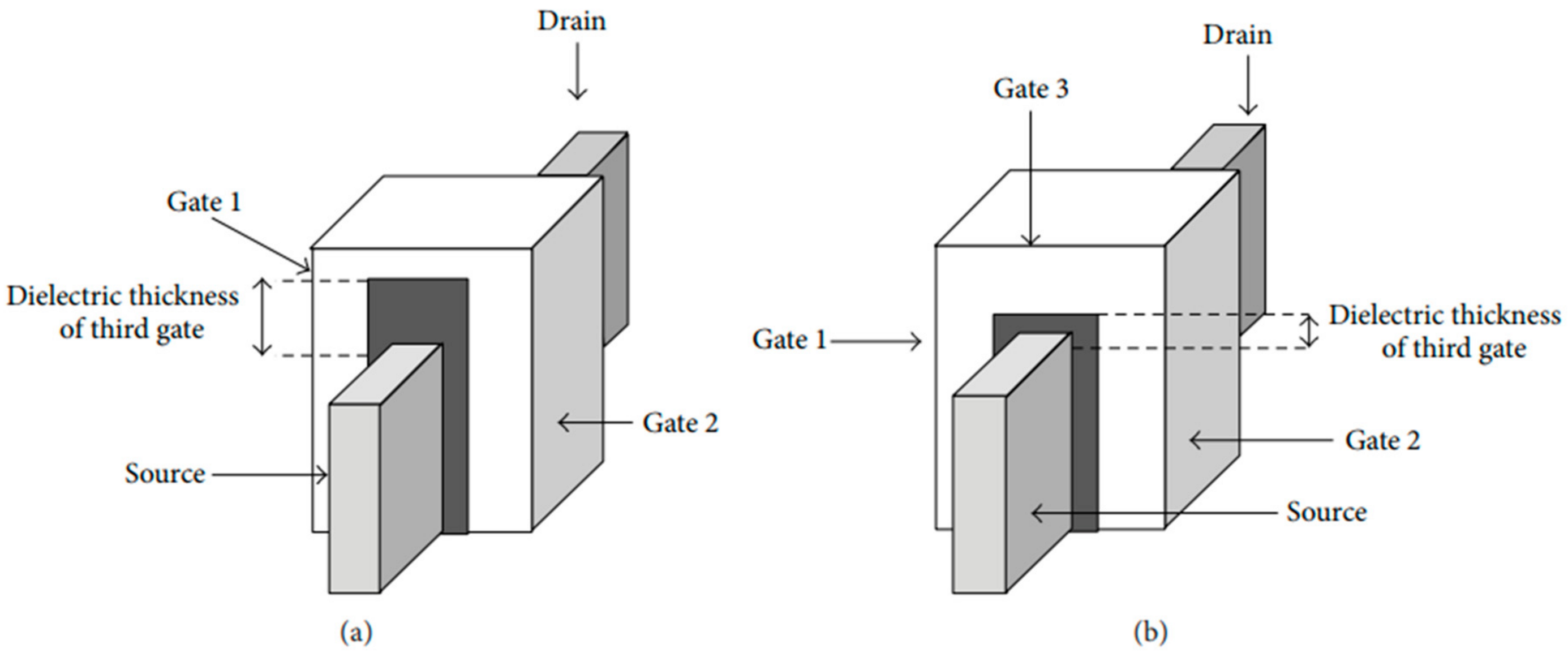

3.3. Based on Dielectric Thickness

4. Various Materials Used in FinFETs

4.1. Materials Used in FinFET Fabrication

4.2. Gate Dielectric Material

4.3. Channel Material

5. FinFET Challenges

5.1. Phenomena in FinFET

5.1.1. Parasitic Capacitance

5.1.2. Corner Effects

5.1.3. Quantum Effects

5.1.4. Crystal Orientation for Fin Surface

5.1.5. Threshold Voltage Adjustment

5.2. Fabrication Drawbacks

5.2.1. Doping Concentration

5.2.2. Integration Challenges

5.2.3. Junction of Multiple FinFETs

5.2.4. Fin Surface Considerations

6. Recent Breakthroughs in FinFET Technology

6.1. Manufacturing a 10 nm Gate Length FinFET

6.2. Ground Plane FinFET

6.3. Bottom Spacer FinFET

6.4. Negative Capacitance FinFET with Ferroelectric Spacer

6.5. Top-Bottom Gated FinFET

7. Sensing Applications of FinFET

7.1. Biosensors

7.1.1. Label-Free Biosensing Using a Negative Capacitance FinFET

7.1.2. Sub-20 nm GaAs Junctionless FinFET Biosensor

7.1.3. Sub-40 nm Dielectric Based FinFET Biosensors

7.2. Chemical Sensors

7.2.1. Gas Sensing

7.2.2. pH Sensing

7.2.3. Ion Sensing

7.3. Physical Sensors

Temperature Sensing

8. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Maurya, R.K.; Bhowmick, B. Review of FinFET devices and perspective on circuit design challenges. Silicon 2022, 14, 5783–5791. [Google Scholar] [CrossRef]

- Jurczak, M.; Collaert, N.; Veloso, A.; Hoffmann, T.; Biesemans, S. Review of FINFET technology. In Proceedings of the 2009 IEEE International SOI Conference, Foster City, CA, USA, 5–8 October 2009. [Google Scholar]

- Pal, R.S.; Sharma, S.; Dasgupta, S. Recent trend of FinFET devices and its challenges: A review. In Proceedings of the 2017 Conference on Emerging Devices and Smart Systems (ICEDSS), Mallasamudram, India, 3–4 March 2017. [Google Scholar]

- Reddy, M.N.; Panda, D.K. A comprehensive review on FinFET in terms of its device structure and performance matrices. Silicon 2022, 14, 12015–12030. [Google Scholar] [CrossRef]

- Bhattacharya, D.; Jha, N.K. FinFETs: From devices to architectures. Adv. Electron. 2014, 2014, 365689. [Google Scholar] [CrossRef]

- Crupi, G.; Schreurs, D.M.-P.; Raskin, J.-P.; Caddemi, A. A comprehensive review on microwave FinFET modeling for progressing beyond the state of art. Solid-State Electron. 2013, 80, 81–95. [Google Scholar] [CrossRef]

- Bhole, M.; Kurude, A.; Pawar, S. Finfet-benefits, drawbacks and challenges. Int. J. Eng. Sci. Res. Technol. 2013, 2, 3219–3222. [Google Scholar]

- Auth, C.; Allen, C.; Blattner, A.; Bergstrom, D.; Brazier, M.; Bost, M.; Buehler, M.; Chikarmane, V.; Ghani, T.; Glassman, T.; et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 131–132. [Google Scholar]

- Xie, R.; Montanini, P.; Akarvardar, K.; Tripathi, M.; Haran, B.; Johnson, S.; Hook, T.; Hamieh, B.; Corliss, D.; Wang, J.; et al. A 7nm FinFET technology featuring EUV patterning and dual strained high mobility channels. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 2.7.1–2.7.4. [Google Scholar]

- Ravariu, C. A NOI—Nanotransistor. In Proceedings of the International Semiconductor Conference, Sinaia, Romania, 3–5 October 2005; pp. 65–68. [Google Scholar]

- Ravariu, C. Gate swing improving for the nothing on insulator transistor in weak tunneling. IEEE Trans. Nanotechnol. 2017, 16, 1115–1121. [Google Scholar] [CrossRef]

- Mohan, C.; Choudhary, S.; Prasad, B. Gate All Around FET: An Alternative of FinFET for Future Technology Nodes. Int. J. Adv. Res. Sci. Eng. 2017, 6, 561–569. [Google Scholar]

- Kim, S.-D.; Guillorn, M.; Lauer, I.; Oldiges, P.; Hook, T.; Na, M.-H. Performance trade-offs in FinFET and gate-all-around device architectures for 7 nm-node and beyond. In Proceedings of the 2015 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Rohnert Park, CA, USA, 5–8 October 2015; pp. 1–3. [Google Scholar]

- Bae, G.; Bae, B.I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; et al. 3 nm GAA Technology featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 28.7.1–28.7.4. [Google Scholar] [CrossRef]

- The International Roadmap for Devices and Systems. 2021. Available online: https://irds.ieee.org/images/files/pdf/2021/2021IRDS_MM.pdf (accessed on 2 October 2022).

- Mukesh, S.; Zhang, J. A Review of the Gate-All-Around Nanosheet FET Process Opportunities. Electronics 2022, 11, 3589. [Google Scholar] [CrossRef]

- Cerdeira, A.; Estrada, M.; Alvarado, J.; Garduño, I.; Contreras, E.; Tinoco, J.; Iñiguez, B.; Kilchytska, V.; Flandre, D. Review on double-gate MOSFETs and FinFETs modeling. Facta Univ.-Ser. Electron. Energetics 2013, 26, 197–213. [Google Scholar] [CrossRef]

- Madhavi, K.B.; Tripathi, S.L. Strategic Review on Different Materials for FinFET Structure Performance Optimization. IOP Conf. Ser. Mater. Sci. Eng. 2020, 988, 012054. [Google Scholar]

- Kumar, J.; Birla, S.; Agarwal, G. A review on effect of various high-k dielectric materials on the performance of FinFET device. Mater. Today Proc. 2023, 79, 297–302. [Google Scholar] [CrossRef]

- Zaki, Z.A.; Tanjila, N.; Saha, J.K. Short channel effects characterization of 3-D FinFET for High-k gate dielectrics. In Proceedings of the 2018 International Conference on Innovations in Science, Engineering and Technology (ICISET), Chittagong, Bangladesh, 27–28 October 2018; pp. 36–40. [Google Scholar]

- Bailey, S.; Rigge, P.; Han, J.; Lin, R.; Chang, E.Y.; Mao, H.; Wang, Z.; Markley, C.; Izraelevitz, A.M.; Wang, A.; et al. A Mixed-Signal RISC-V Signal Analysis SoC Generator With a 16-nm FinFET Instance. IEEE J. Solid-State Circuits 2019, 54, 2786–2801. [Google Scholar] [CrossRef]

- Sriram, S.R.; Bindu, B. A physics-based 3-D potential and threshold voltage model for undoped triple-gate FinFET with interface trapped charges. J. Comput. Electron. 2019, 18, 37–45. [Google Scholar] [CrossRef]

- Srinivasan, V.; Le Tuai, S.; Lee, T.-C. F2: FinFETs & FDSOI—A mixed signal circuit designer’s perspective. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 505–507. [Google Scholar] [CrossRef]

- Gong, H.; Ni, K.; Zhang, E.X.; Sternberg, A.L.; Kozub, J.A.; Ryder, K.L.; Keller, R.F.; Ryder, L.D.; Weiss, S.M.; Weller, R.A.; et al. Scaling Effects on Single-Event Transients in InGaAs FinFETs. IEEE Trans. Nucl. Sci. 2018, 65, 296–303. [Google Scholar] [CrossRef]

- Dargar, S.K.; Srivastava, V.M. Effect of gate-lap and oxide material at 10-nm FinFET device performance. In Proceedings of the International Conference on Advanced Computation and Telecommunication (ICACAT), Bhopal, India, 28–29 December 2018; pp. 1–4. [Google Scholar]

- Arutchelvan, G.; Smets, Q.; Verreck, D.; Ahmed, Z.; Gaur, A.; Sutar, S.; Jussot, J.; Groven, B.; Heyns, M.; Lin, D.; et al. Impact of device scaling on the electrical properties of MoS2 field-effect transistors. Sci. Rep. 2021, 11, 6610. [Google Scholar] [CrossRef]

- Chandar, D.B.; Vadthiya, N.; Kumar, A.; Mishra, R.A. Suppression of short channel effects (SCEs) by dual material gate vertical surrounding gate (DMGVSG) MOSFET: 3-D TCAD simulation. Procedia Eng. 2013, 64, 125–132. [Google Scholar] [CrossRef]

- Boukortt, N.E.I.; Lenka, T.R.; Patanè, S.; Crupi, G. Effects of Varying the Fin Width, Fin Height, Gate Dielectric Material, and Gate Length on the DC and RF Performance of a 14-nm SOI FinFET Structure. Electronics 2021, 11, 91. [Google Scholar] [CrossRef]

- Kumar, S.; Paliwal, K.K.; Mahajan, S. Effect of reduction in gate oxide thickness with different materials for 100NM Mosfet. Int. J. Latest Res. Sci. Technol. 2018, 7, 5–8. [Google Scholar]

- Salami, M.; Abadi, M.S. Simulation Analysis of Hafnium-based-Oxide and Effects of Metallization on Electrical Performance of Gate-All-Around Finfet Devices. Procedia Mater. Sci. 2015, 11, 444–448. [Google Scholar] [CrossRef]

- Kaur, G.; Gill, S.S.; Rattan, M. Impact of lanthanum doped zirconium oxide (LaZrO2) gate dielectric material on FinFET inverter. Int. J. Smart Sens. Intell. Syst. 2020, 13, 1–10. [Google Scholar] [CrossRef]

- Kaur, G.; Gill, S.S.; Rattan, M. Design and performance analysis of 20nm 5-fin SOI FinFET for different channel materials. In Proceedings of the 2017 International Conference on Computing, Communication and Automation (ICCCA), Greater Noida, India, 5–6 May 2017; pp. 1569–1572. [Google Scholar]

- Kumar, H.; Jethwa, M.K.; Porwal, A.; Dhavse, R.; Devre, H.M.; Parekh, R. Effect of Different Channel Material on the Performance Parameters for FinFET Device. In Proceedings of the Fifth International Conference on Microelectronics, Computing and Communication Systems: MCCS 2020; Springer: Singapore, 2021. [Google Scholar]

- Bhat, T.A.; Mustafa, M.; Beigh, M.R. Study of short channel effects in n-FinFET structure for Si, GaAs, GaSb and GaN channel materials. J. Nano-Electron Phys. 2015, 7, 03010. [Google Scholar]

- Kumar, A.; Janakirani, M.; Anand, M.; Sharma, S.; Vivekanand, C.V.; Chakravarti, A. Comparative performance study of difference differential amplifier using 7 nm and 14 nm FinFET technologies and carbon nanotube FET. J. Nanomater. 2022, 2022, 8200856. [Google Scholar] [CrossRef]

- Guillorn, M.; Chang, J.; Bryant, A.; Fuller, N.; Dokumaci, O.; Wang, X.; Newbury, J.; Babich, K.; Ott, J.; Haran, B.; et al. FinFET performance advantage at 22nm: An AC perspective. In Proceedings of the 2008 Symposium on VLSI Technology, Honolulu, HI, USA, 17–19 June 2008; pp. 12–13. [Google Scholar] [CrossRef]

- Kang, C.Y.; Sohn, C.; Baek, R.H.; Hobbs, C.; Kirsch, P.; Jammy, R. Effects of layout and process parameters on device/circuit performance and variability for 10nm node FinFET technology. In Proceedings of the Digest of Technical Papers—Symposium on VLSI Technology, Kyoto, Japan, 11–13 June 2013; pp. T90–T91. [Google Scholar]

- Fossum, J.G.; Yang, J.-W.; Trivedi, V.P. Suppression of corner effects in triple-gate MOSFETs. IEEE Electron Device Lett. 2003, 24, 745–747. [Google Scholar] [CrossRef]

- Takagi, S.; Toriumi, A.; Iwase, M.; Tango, H. On the universality of inversion layer mobility in Si MOSFET’s: Part II-effects of surface orientation. IEEE Trans. Electron Devices 1994, 41, 2363–2368. [Google Scholar] [CrossRef]

- Satô, T.; Takeishi, Y.; Hara, H. Effects of Crystallographic Orientation on Mobility, Surface State Density, and Noise in p-Type Inversion Layers on Oxidized Silicon Surfaces. Jpn. J. Appl. Phys. 1969, 8, 588. [Google Scholar] [CrossRef]

- Collaert, N.; Demand, M.; Ferain, I.; Lisoni, J.; Singanamalla, R.; Zimmerman, P.; Yim, Y.; Schram, T.; Mannaert, G.; Goodwin, M.; et al. Tall triple-gate devices with TiN/HfO/sub 2/gate stack. Digest of Technical Papers. In Proceedings of the 2005 Symposium on VLSI Technology, Kyoto, Japan, 14–16 June 2005; pp. 108–109. [Google Scholar] [CrossRef]

- Colinge, J.-P. (Ed.) FinFETs and Other Multi-Gate Transistors; Springer: New York, NY, USA, 2008; Volume 73. [Google Scholar]

- Hu, C.; Bokor, J.; King, T.-J.; Anderson, E.; Kuo, C.; Asano, K.; Takeuchi, H.; Kedzierski, J.; Lee, W.-C.; Hisamoto, D. FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 2001, 47, 2320–2325. [Google Scholar] [CrossRef]

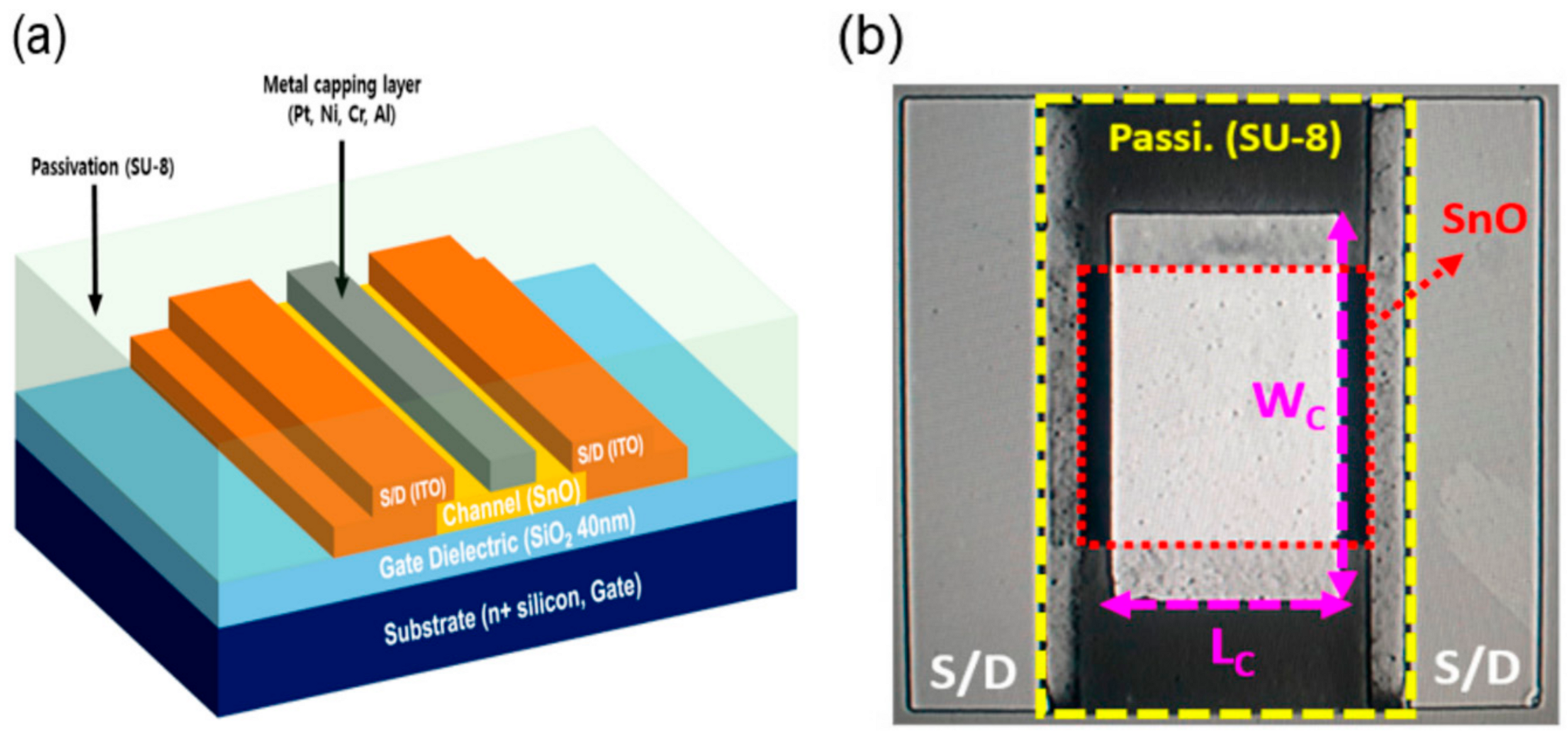

- Shin, M.-G.; Bae, K.-H.; Jeong, H.-S.; Kim, D.-H.; Cha, H.-S.; Kwon, H.-I. Effects of Capping Layers with Different Metals on Electrical Performance and Stability of p-Channel SnO Thin-Film Transistors. Micromachines 2020, 11, 917. [Google Scholar] [CrossRef]

- Van Dal, M.; Collaert, N.; Doornbos, G.; Vellianitis, G.; Curatola, G.; Pawlak, B.; Duffy, R.; Jonville, C.; Degroote, B.; Altamirano, E.; et al. Highly manufacturable FinFETs with sub-10nm fin width and high aspect ratio fabricated with immersion lithography. In Proceedings of the 2007 IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 110–111. [Google Scholar] [CrossRef]

- Duffy, R.; Curatola, G.; Pawlak, B.J.; Doornbos, G.; van der Tak, K.; Breimer, P.; van Berkum, J.G.M.; Roozeboom, F. Doping fin field-effect transistor sidewalls: Impurity dose retention in silicon due to high angle incident ion implants and the impact on device performance. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. 2008, 26, 402–407. [Google Scholar] [CrossRef]

- Lenoble, D.; Doornbos, G.; de Keersgieter, A.; Pawlak, B.; Vandervorst, W.; Jurczak, M.; Skotnicki, T. The junction challenges in the FinFETs device. In Proceedings of the 2006 International Workshop on Junction Technology, Shanghai, China, 15–16 May 2006; pp. 78–83. [Google Scholar] [CrossRef]

- Yu, B.; Chang, L.; Ahmed, S.; Wang, H.; Bell, S.; Yang, C.-Y.; Tabery, C.; Ho, C.; Xiang, Q.; King, T.-J.; et al. FinFET scaling to 10 nm gate length. In Proceedings of the Digest. International Electron Devices Meeting, San Francisco, CA, USA, 8–11 December 2002; pp. 251–254. [Google Scholar] [CrossRef]

- Kumar, M.J.; Siva, M. The Ground Plane in Buried Oxide for Controlling Short-Channel Effects in Nanoscale SOI MOSFETs. IEEE Trans. Electron Devices 2008, 55, 1554–1557. [Google Scholar] [CrossRef]

- Xiong, W.; Colinge, J. Self-aligned implanted ground-plane fully depleted SOI MOSFET. Electron. Lett. 1999, 35, 2059–2060. [Google Scholar] [CrossRef]

- Yanagi, S.; Nakakubo, A.; Omura, Y. Proposal of a partial-ground-plane (PGP) silicon-on-insulator (SOI) MOSFET for deep sub-0.1-μm channel regime. IEEE Electron Device Lett. 2001, 22, 278–280. [Google Scholar] [CrossRef]

- Xiong; Ramkumar; Jang; Park; Colinge. Self-aligned ground-plane FDSOI MOSFET. In Proceedings of the 2002 IEEE International SOI Conference, Williamsburg, VA, USA, 7–10 October 2002; pp. 23–24. [Google Scholar] [CrossRef]

- Saremi, M.; Afzali-Kusha, A.; Mohammadi, S. Ground plane fin-shaped field effect transistor (GP-FinFET): A FinFET for low leakage power circuits. Microelectron. Eng. 2012, 95, 74–82. [Google Scholar] [CrossRef]

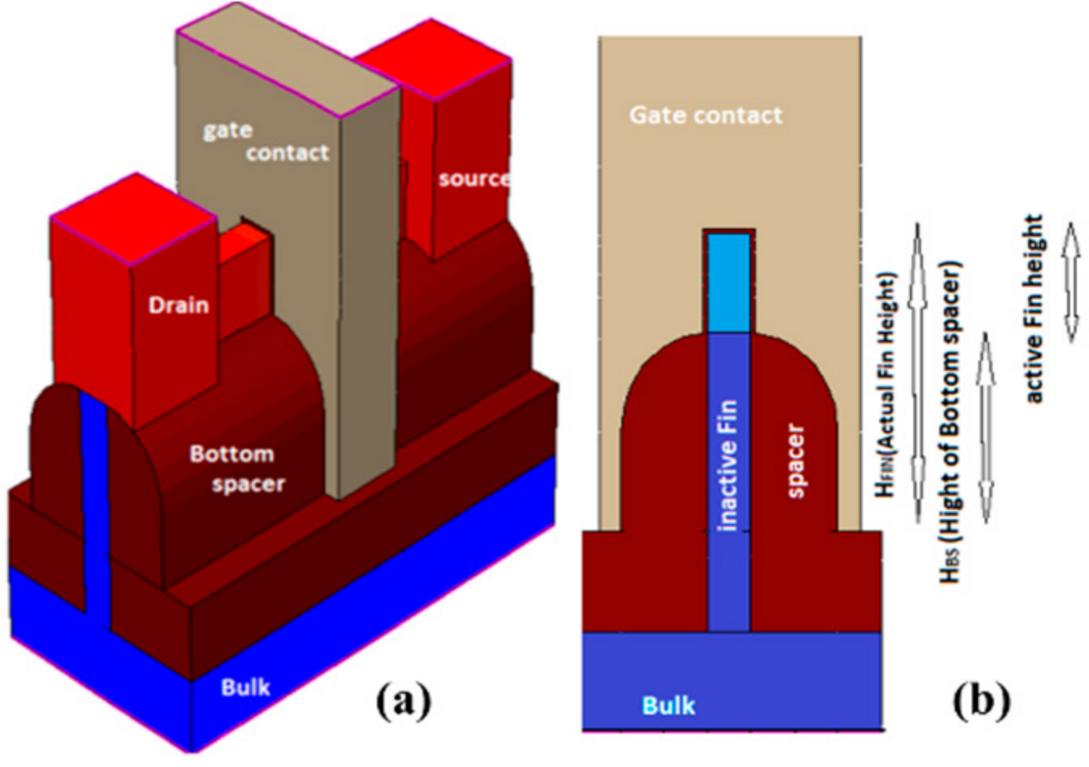

- Shrivastava, M.; Baghini, M.S.; Sharma, D.K.; Rao, V.R. A Novel Bottom Spacer FinFET Structure for Improved Short-Channel, Power-Delay, and Thermal Performance. IEEE Trans. Electron Devices 2010, 57, 1287–1294. [Google Scholar] [CrossRef]

- Tripathi, S.L.; Mishra, R.; Mishra, R.A. Optimization of High Performance Bulk FinFET Structure Independent of Random Dopent Process Variations. Microelectron. Solid State Electron. 2013, 2, 29–38. [Google Scholar] [CrossRef]

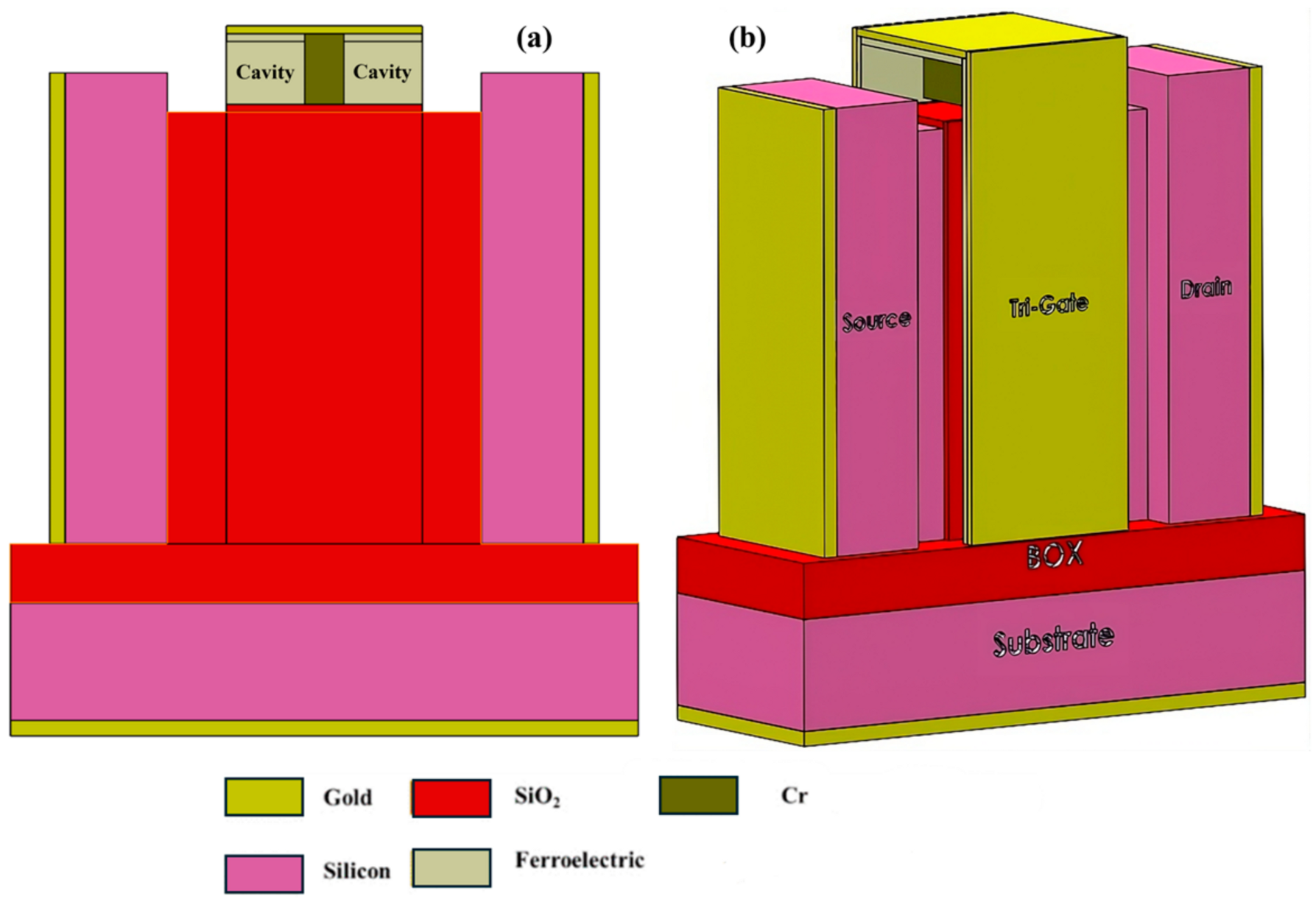

- Chauhan, V.; Samajdar, D.P.; Bagga, N.; Dixit, A. A Novel Negative Capacitance FinFET with Ferroelectric Spacer: Proposal and Investigation. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2021, 68, 3654–3657. [Google Scholar] [CrossRef]

- Gangwani, L.; Chakravarti, R.; Chaujar, R. Investigation of a novel 5nm top bottom gated junctionless FinFET for improved switching and analog performance. J. Phys. Conf. Ser. 2021, 1921, 012100. [Google Scholar] [CrossRef]

- Chhabra, A.; Kumar, A.; Chaujar, R. Sub-20 nm GaAs junctionless FinFET for biosensing application. Vacuum 2018, 160, 467–471. [Google Scholar] [CrossRef]

- Tripathi, S.L.; Raj, B. Design of FinFET as Biosensor. In Nanodevices for Integrated Circuit Design; Wiley: Hoboken, NJ, USA, 2023; pp. 143–156. [Google Scholar]

- Kim, J.-Y.; Ahn, J.-H.; Choi, S.-J.; Im, M.; Kim, S.; Duarte, J.P.; Kim, C.-H.; Park, T.J.; Lee, S.Y.; Choi, Y.-K. An Underlap Channel-Embedded Field-Effect Transistor for Biosensor Application in Watery and Dry Environment. IEEE Trans. Nanotechnol. 2012, 11, 390–394. [Google Scholar] [CrossRef]

- Kumar, A.; Tripathi, M.; Chaujar, R. Comprehensive analysis of sub-20 nm black phosphorus based junctionless-recessed channel MOSFET for analog/RF applications. Superlattices Microstruct. 2018, 116, 171–180, ISSN 0749-6036. [Google Scholar] [CrossRef]

- Dixit, A.; Samajdar, D.P.; Chauhan, V. Sensitivity Analysis of a Novel Negative Capacitance FinFET for Label-Free Biosensing. IEEE Trans. Electron Devices 2021, 68, 5204–5210. [Google Scholar] [CrossRef]

- Dixit, A.; Samajdar, D.P.; Bagga, N. Dielectric modulated GaAs1−xSbx FinFET as a label-free biosensor: Device proposal and investigation. Semicond. Sci. Technol. 2021, 36, 095033. [Google Scholar] [CrossRef]

- Sentaurus Device User Guide; Synopsys Inc.: Mountain View, CA, USA, 2020.

- Narang, R.; Saxena, M.; Gupta, M. Comparative Analysis of Dielectric-Modulated FET and TFET-Based Biosensor. IEEE Trans. Nanotechnol. 2015, 14, 427–435. [Google Scholar] [CrossRef]

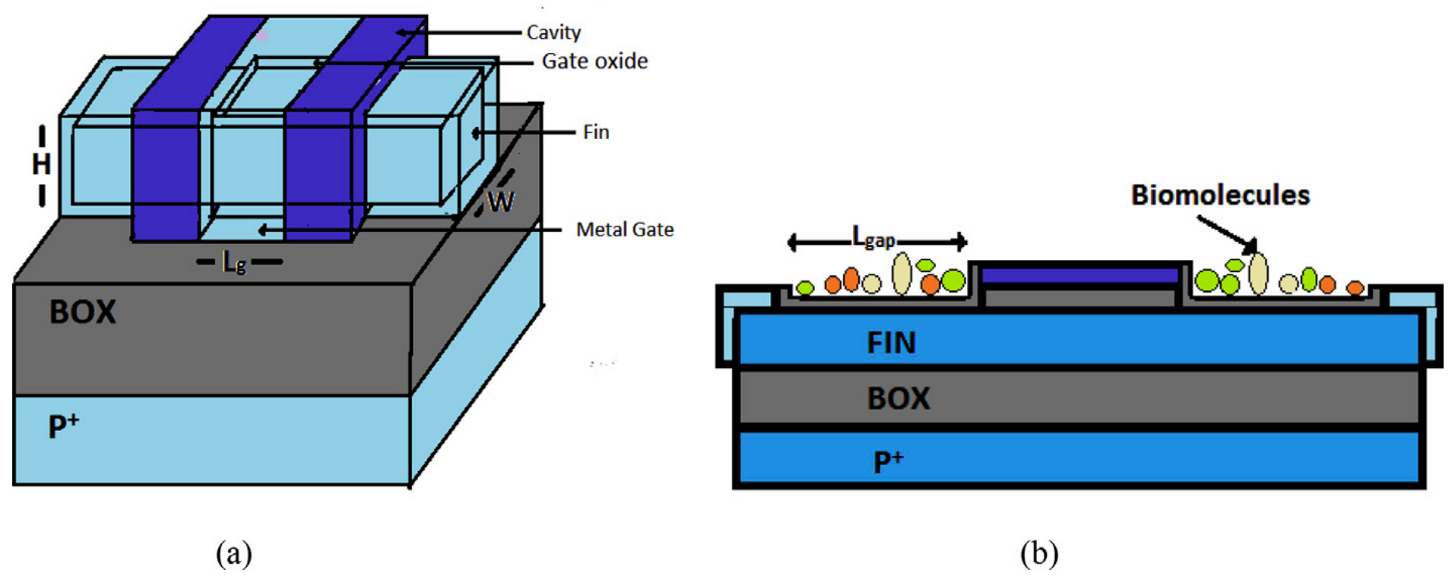

- Kesherwani, S.; Daga, M.; Mishra, G.P. Design of Sub-40nm FinFET Based Label Free Biosensor. Silicon 2022, 14, 12459–12465. [Google Scholar] [CrossRef]

- Gandhi, N.; Rathore, S.; Jaisawal, R.K.; Kondekar, P.N.; Dey, S.; Bagga, N. Unveiling the self-heating and process variation reliability of a junctionless FinFET-based hydrogen gas sensor. IEEE Sens. Lett. 2023, 7, 4503004. [Google Scholar] [CrossRef]

- Gandhi, N.; Jaisawal, R.K.; Rathore, S.; Kondekar, P.N.; Bagga, N. A proof of concept for reliability aware analysis of junctionless negative capacitance FinFET-based hydrogen sensor. Smart Mater. Struct. 2024, 33, 035010. [Google Scholar] [CrossRef]

- Sehgal, H.D.; Pratap, Y.; Gupta, M.; Kabra, S.; Pal, P. Comparative analysis of junctionless FinFET and inverted mode FinFET as phosphine (PH 3) gas sensor. In Proceedings of the 2020 5th International Conference on Devices, Circuits and Systems (ICDCS), Coimbatore, India, 5–6 March 2020; pp. 193–197. [Google Scholar]

- Rani, D.; Rollo, S.; Olthuis, W.; Krishnamoorthy, S.; García, C.P. Combining chemical functionalization and FinFET geometry for field effect sensors as accessible technology to optimize pH sensing. Chemosensors 2021, 9, 20. [Google Scholar] [CrossRef]

- Alharbi, A.G.; Shafi, N. Liquid gate and back gate capacitive coupling effects in ph sensing performance of finfets. Silicon 2022, 14, 11027–11037. [Google Scholar] [CrossRef]

- Shen, Y.; Wang, C.; Liou, K.; Tan, P.; Wang, Y.; Wu, S.; Yang, T.; Yu, Y.; Chiang, T.; Chih, Y.; et al. Multifunctional Ion-Sensitive Floating Gate Fin Field-Effect Transistor with Three-Dimensional Nanoseaweed Structure by Glancing Angle Deposition Technology. Small 2022, 18, 2104168. [Google Scholar] [CrossRef]

- Singh, S.K.; Sharma, D.; Srinivasan, P.; Dixit, A. Quantum-Dot-Based Thermometry Using 12-nm FinFET and Machine Learning Models. IEEE Trans. Electron Devices 2024, 71, 2043–2050. [Google Scholar] [CrossRef]

| Material Used in FinFET | Improvement |

|---|---|

| FinFET based dual KK-structure | (1) gm ~ 9.09% |

| (2) gds ~ 13.04% | |

| (3) Ft ~ 12.91% | |

| (4) Maximum oscillating frequency | |

| InGaAs-on-Insulator FinFET | Improvement in the gate and source of drain length |

| Double Gate based n-FinFET using HfO2 | Leakage current reduces |

| SOI-FinFETs | Fin width improvement |

| MosFET (Multi gate), Deeply Scaled CMOS, FinFET | Short channel effects and Leakage Issues are obtained. Improvement in chip area and high performance |

| Selective Epitaxial Si Growth in FinFET | Repairs the fin outer surface |

| Atomic Layer Deposition (ALD) in FinFET | Improvement in threshold voltage (Vt) |

| Parameters (Vd = 0.75 V, Vg = 0.75 V) | (LaZrO2) Gate dielectric material k = 40 | (SiO2) Gate dielectric material k = 3.9 |

| ION (A) | 4.95 × 10−5 | 1.78 × 10−5 |

| IOFF (A) | 3.61 × 10−14 | 5.02 × 10−13 |

| ION/IOFF | 1.37 × 109 | 3.50 × 107 |

| Vt (V) | 0.253 | 0.207 |

| SS (mV/dec) | 60.3 | 67.02 |

| DIBL (mV/V) | 10.1 | 43 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Karimi, K.; Fardoost, A.; Javanmard, M. Comprehensive Review of FinFET Technology: History, Structure, Challenges, Innovations, and Emerging Sensing Applications. Micromachines 2024, 15, 1187. https://doi.org/10.3390/mi15101187

Karimi K, Fardoost A, Javanmard M. Comprehensive Review of FinFET Technology: History, Structure, Challenges, Innovations, and Emerging Sensing Applications. Micromachines. 2024; 15(10):1187. https://doi.org/10.3390/mi15101187

Chicago/Turabian StyleKarimi, Koosha, Ali Fardoost, and Mehdi Javanmard. 2024. "Comprehensive Review of FinFET Technology: History, Structure, Challenges, Innovations, and Emerging Sensing Applications" Micromachines 15, no. 10: 1187. https://doi.org/10.3390/mi15101187