Two CMOS Wilkinson Power Dividers Using High Slow-Wave and Low-Loss Transmission Lines

Abstract

:1. Introduction

2. Design and Analysis

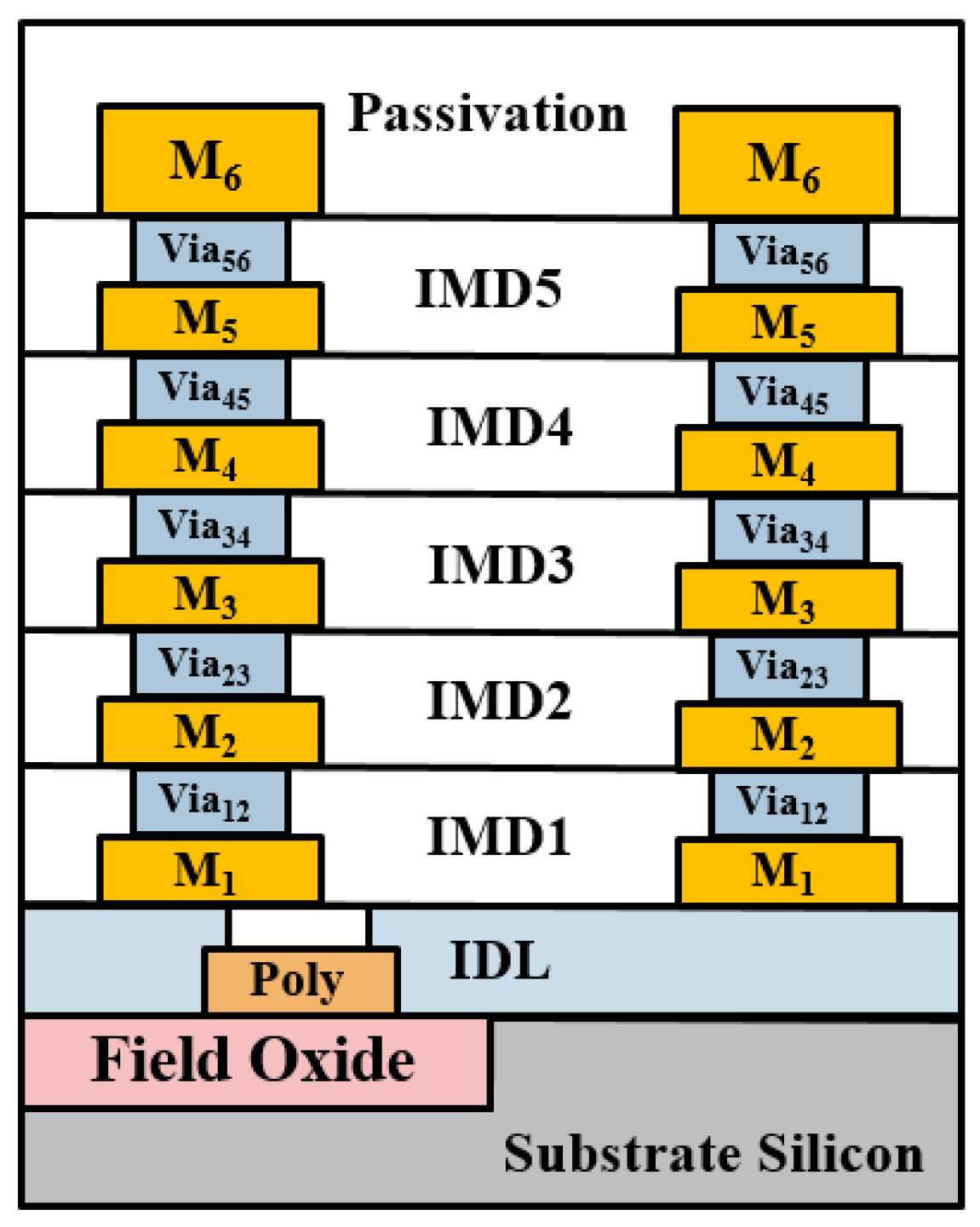

2.1. Process Description and Conventional Transmission Lines

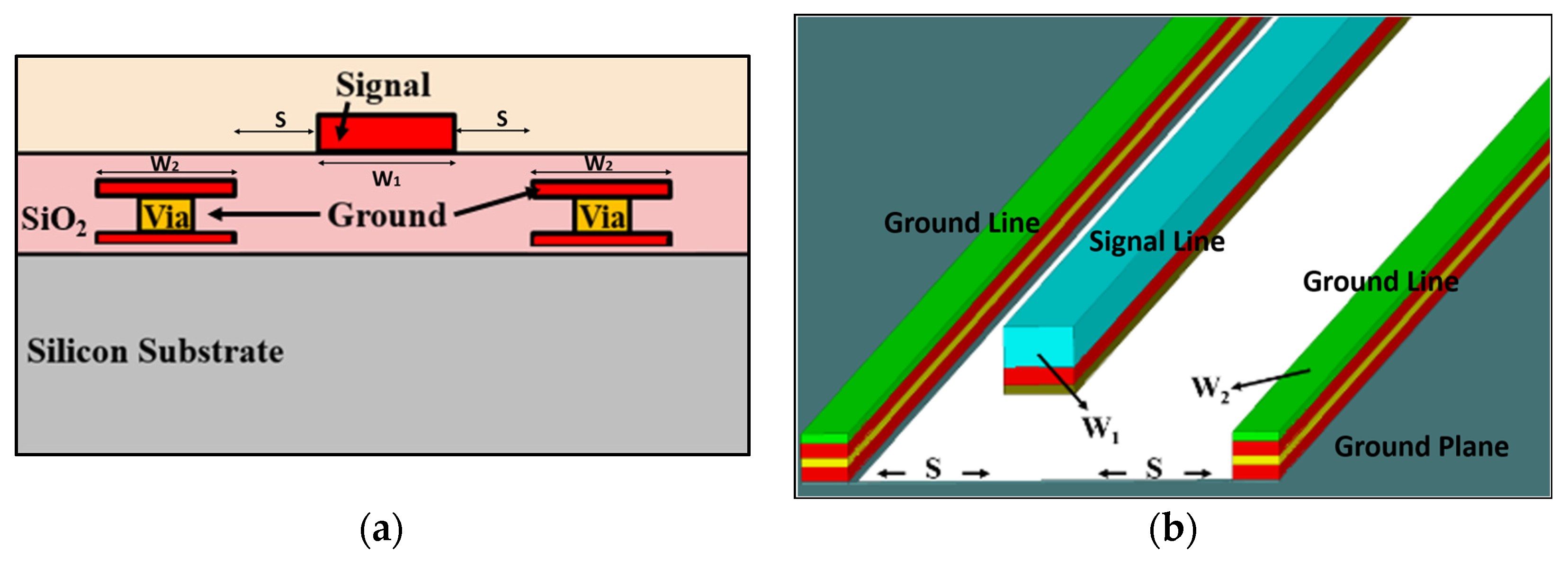

2.2. The Proposed Pseudo Coplanar Waveguide

2.3. Comparison of Different Transmission Lines on CMOS

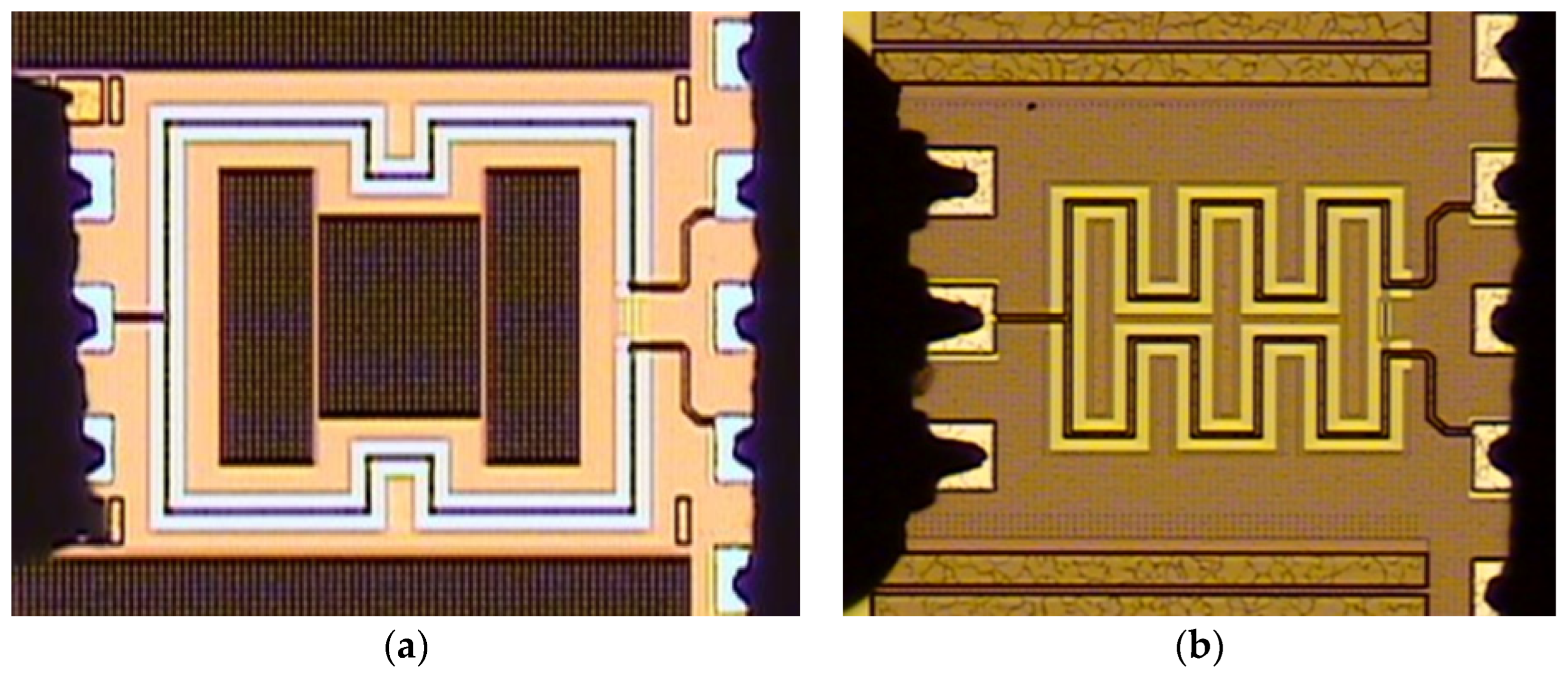

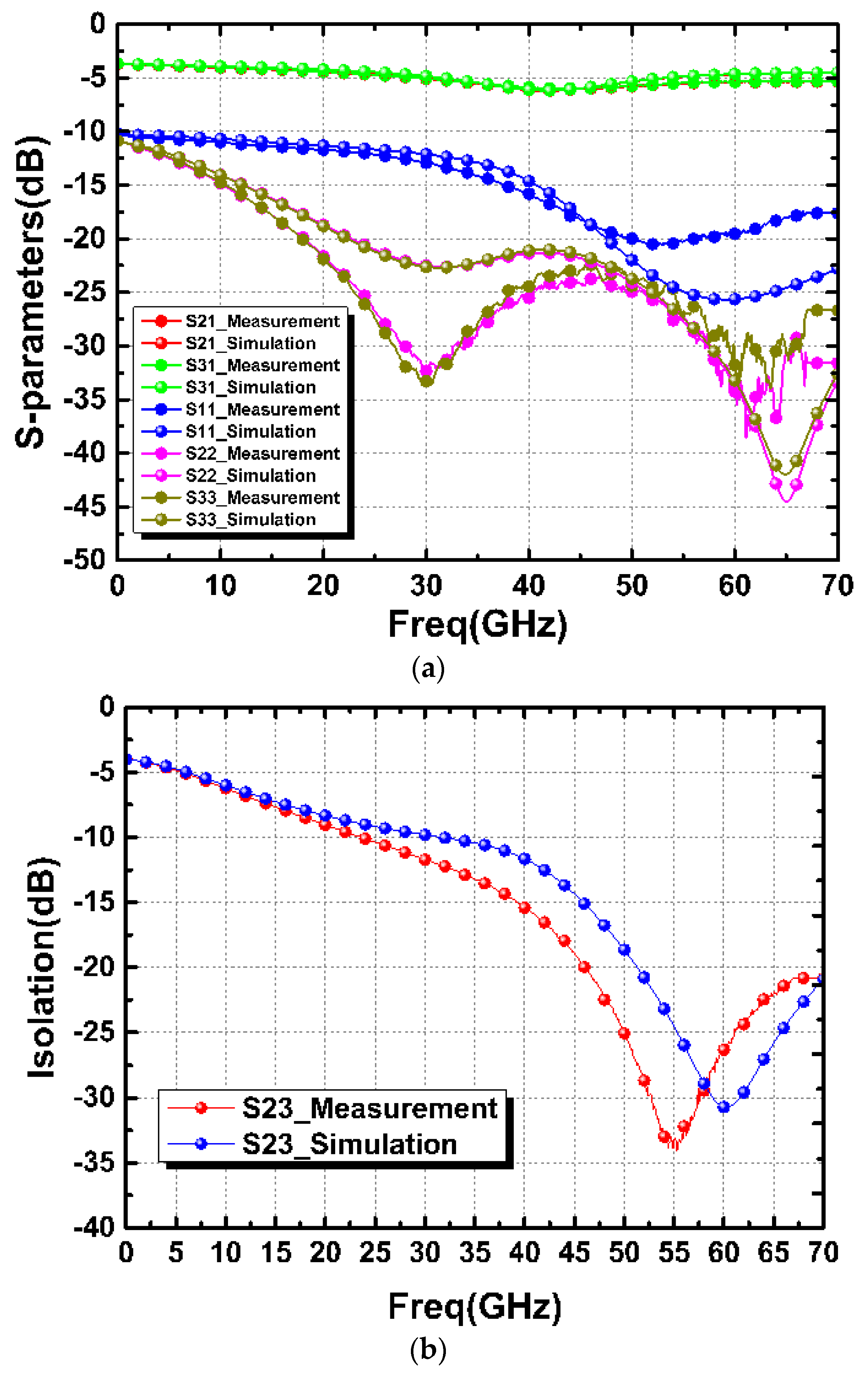

3. Implementation and Experimental Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Wang, D.; Zhang, H.; Xu, T.; Wang, H.; Zhang, G. Design and optimization of equal split broadband microstrip Wilkinson power divider using enhanced particle swarm optimization algorithm. Prog. Electromagn. Res. 2011, 118, 321–334. [Google Scholar] [CrossRef]

- Wu, Y.; Liu, Y.; Xue, Q. An analytical approach for a novel coupled-line dualband Wilkinson power divider. IEEE Trans. Microw. Theory Tech. 2011, 59, 286–294. [Google Scholar] [CrossRef]

- Wang, S.; Chiang, M.-J.; Chang, C.-T. A Novel CMOS 24-GHz In-Phase Power Divider using Synthetic Coupled Lines. IEEE Trans. Compon. Packag. Manuf. Technol. 2015, 5, 398–403. [Google Scholar] [CrossRef]

- Ponchak, G.E.; Downey, A.N. Characterization of Thin Film Microstrip Lines on Polyimide. IEEE Trans. Compon. Packag. Manuf.Technol. Part B 1998, 21, 171–176. [Google Scholar] [CrossRef]

- Wen, C.P. Coplanar waveguide: A Surface Strip Transmission Line Suitable for Nonreciprocal Gyromagnetic Device Applications. IEEE Trans. Microw. Theory Tech. 1969, 17, 1087–1090. [Google Scholar] [CrossRef]

- Magerko, M.A.; Fan, L.; Chang, K. Multiple Dielectric Structures to Eliminate Moding Problems in Conductor-Backed Coplanar Waveguide MIC’. IEEE Microw. Guid. Wave Lett. 1992, 2, 257–259. [Google Scholar] [CrossRef]

- Hsieh, C.; Tsai, Z. A K-Band to Ka-Band CPW-Like Low Loss Transmission Line in 0.18-um CMOS. In Proceedings of the 2016 URSI Asia-Pacific Radio Science Conference (URSI AP-RASC), Seoul, Republic of Korea, 21–25 August 2016; pp. 1808–1810. [Google Scholar]

- Kim, J.-G.; Rebeiz, G.M. Miniature four-way and two-way 24 GHz Wilkinson power dividers in 0.13 μm CMOS. IEEE Microw. Wirel. Compon. Lett. 2007, 17, 658–660. [Google Scholar] [CrossRef]

- Lu, L.-H.; Battacharya, P.; Katehi, L.P.B.; Ponchak, G.E. X-band and K-band lumped Wilkinson power dividers with a micromachined technology. In Proceedings of the 2000 IEEE MTT-S International Microwave Symposium Digest (Cat. No.00CH37017), Boston, MA, USA, 11–16 June 2000; pp. 287–290. [Google Scholar]

- El-Hameed, A.S.A.; Barakat, A.; Abdel-Rahman, A.B.; Allam, A. Design of Low-Loss Coplanar Transmission Lines Using Distributed Loading for Millimeter-Wave Power Divider/Combiner Applications in 0.18-μm CMOS Technology. IEEE Trans. Microw. Theory Tech. 2018, 66, 5221–5229. [Google Scholar] [CrossRef]

- Park, J.S.; Wang, H. A Fully Differential Ultra-Compact Broadband Transformer-Based Wilkinson Power Divider. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 255–257. [Google Scholar] [CrossRef]

- Kuo, C.-Y.; Chen, A.Y.-K.; Li, C.; Luo, C.-H. A mm-Wave Stub-Loaded ECPW Wilkinson Power Divider/Combiner in 90 nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2012, 22, 627–629. [Google Scholar] [CrossRef]

- Haroun, I.; Lin, T.-Y.; Chang, D.-C.; Plett, C. A Reduced-Size, Low-Loss 57–86 GHz IPD-Based Power Divider using Loaded Modified CPW Transmission Lines. In Proceedings of the 2012 Asia Pacific Microwave Conference Proceedings, Kaohsiung, Taiwan, 4–7 December 2012; pp. 1202–1204. [Google Scholar]

- Jiang, Y.; Hu, K.; Feng, L.; Zhang, H.; Shi, Y.; Tang, W.; Yu, X. Ultra wideband lumped Wilkinson power divider on gallium arsenide integrated passive device technology. Int. J. RF Microw. Comput. Eng. 2021, 31, e22898. [Google Scholar] [CrossRef]

- Doan, N.-T.; Ngo, T.-B.; Yoon, S.-W. Compact wideband CMOS lumped-element Wilkinson power divider with asymmetric negative capacitance circuit. Electron. Lett. 2020, 56, 1065–1067. [Google Scholar] [CrossRef]

- Tang, J.; Ni, H.; Peng, R.-L.; Wang, N.; Zuo, L. A Review on Energy Conversion Using Hybrid Photovoltaic and Thermoelectric Systems. J. Power Sources 2023, 562, 232785. [Google Scholar] [CrossRef]

- Song, H.-S.; Lee, Y.-S. A Miniaturized 2.4 GHz Band Multi-Layer Bandpass Filter Using Capacitively Loaded λ/4 Slow-Wave Resonator. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest, 2003, Philadelphia, PA, USA, 8–13 June; 2003; Volume 1, pp. 515–518. [Google Scholar]

- Lee, S.; Choi, J.; May, G.S.; Yun, I. Modeling and Analysis of 3-D Solenoid Embedded Inductors. IEEE Trans. Electron. Packag. Manuf. 2002, 25, 34–41. [Google Scholar]

- Nakatsuka, T.; Itoh, J.; Yamamoto, S.; Yoshida, T.; Nishitsuji, M.; Uda, T.; Nishii, K.; Ishikawa, O. A Highly Miniaturized Receiver Front-End Hybrid IC Using on-Chip High-Dielectric Constant Capacitors for Mobile Communication Equipment. In Proceedings of the IEEE 1995 Microwave and Millimeter-Wave. Monolithic Circuits Symposium. Digest of Papers, Orlando, FL, USA, 15–16 May 1995; Volume 1, pp. 85–88. [Google Scholar]

- Miguel, A.S.-S.; Yves, Q.; Vincent, L.S.; Cedric, Q.; Stephane, C. Average Power Handling Capability of Microstrip Passive Circuits Considering Metal Housing and Environment Conditions. IEEE Trans. Compon. Packag. Manuf. Technol. 2014, 4, 1624–1633. [Google Scholar]

- Chen, C.-C.; Tzuang, C.-K. Synthetic Quasi-TEM Meandered Transmission Lines for Compacted Microwave Integrated Circuits. IEEE Trans. Microw. Theory Tech. 2004, 52, 1637–1647. [Google Scholar] [CrossRef]

- Eisenstadt, W.R.; Eo, Y. S-parameter-based IC interconnect transmission line characterization. IEEE Trans. Compon. Hybrids Manuf. Technol. 1992, 15, 483–490. [Google Scholar] [CrossRef]

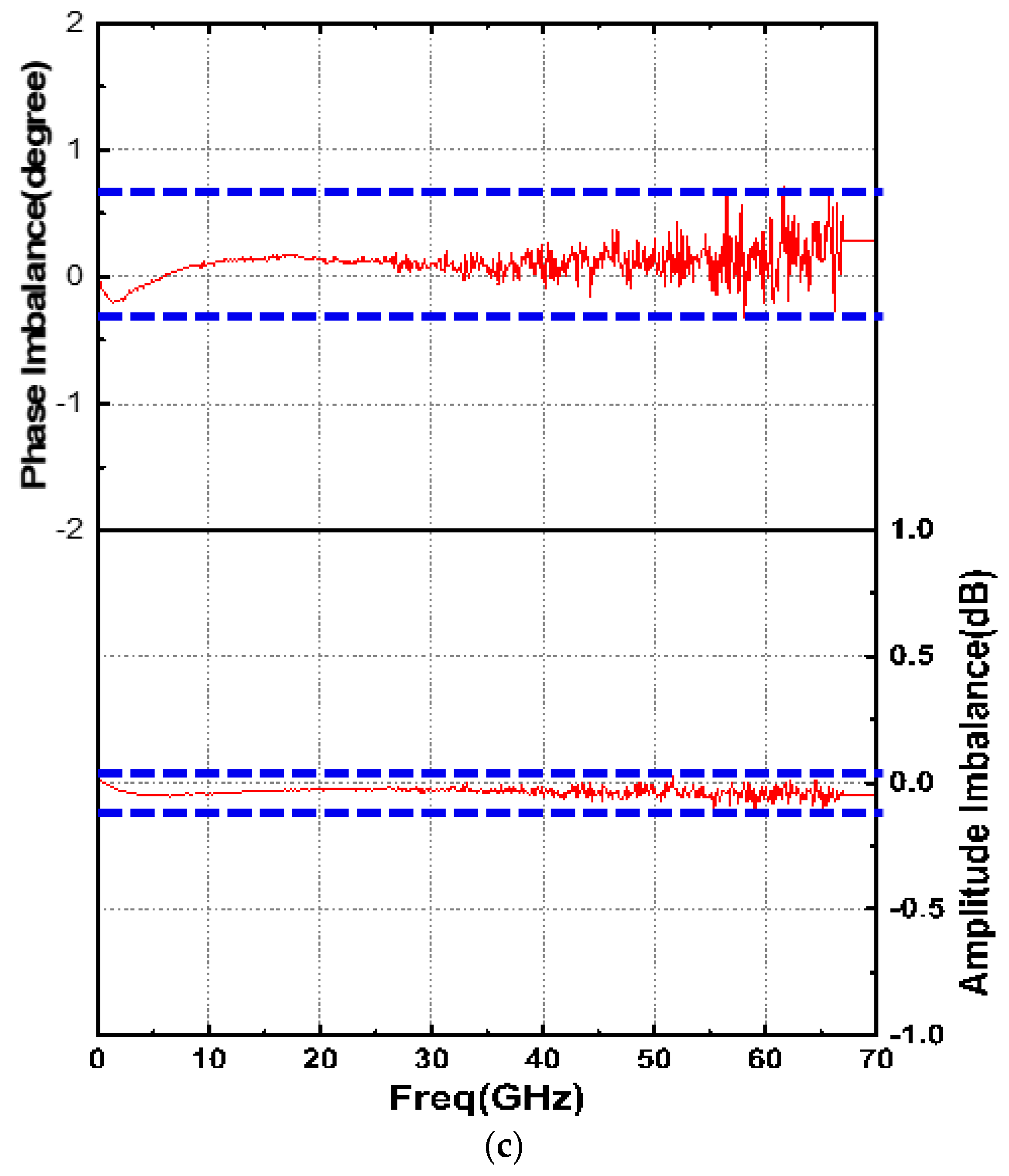

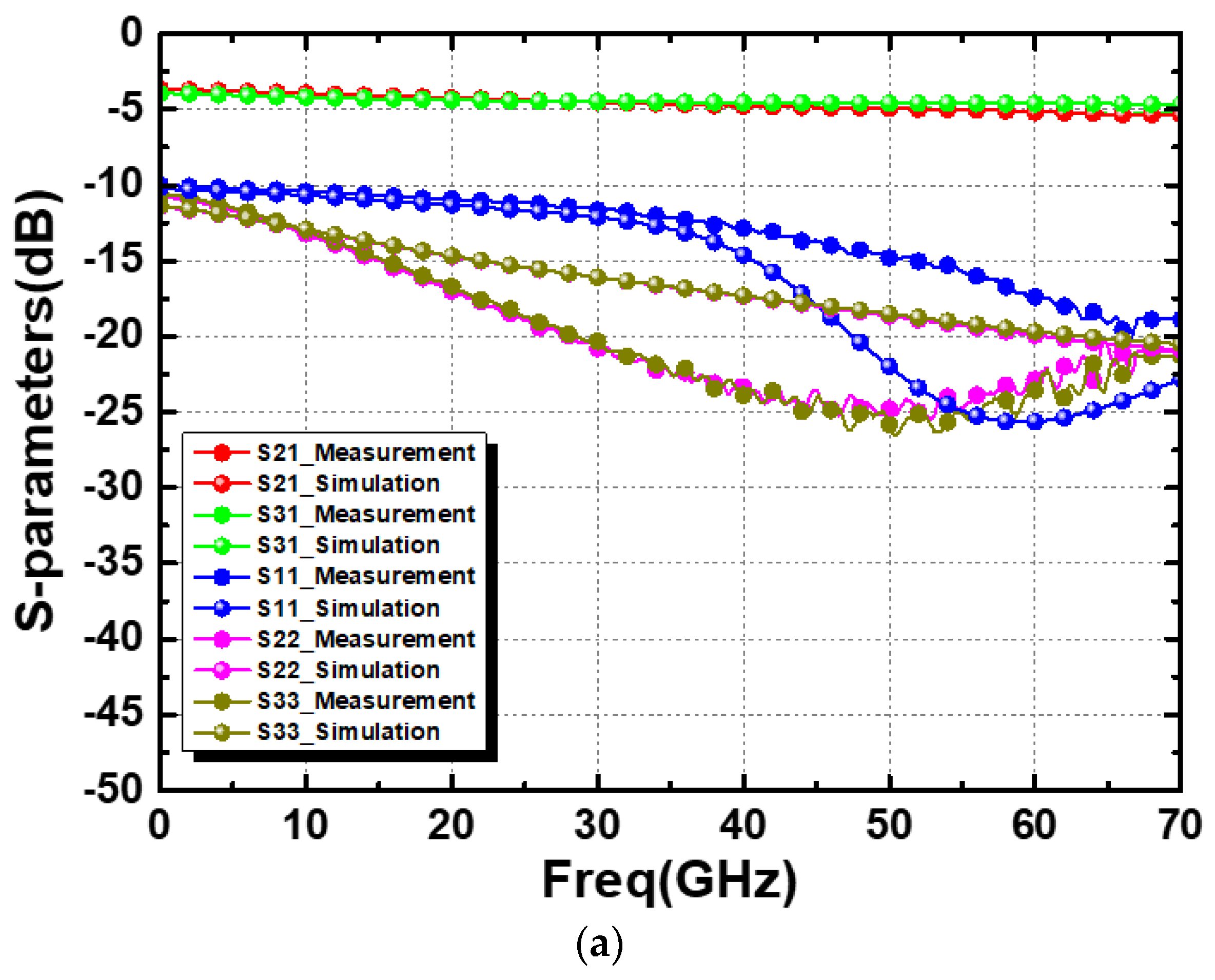

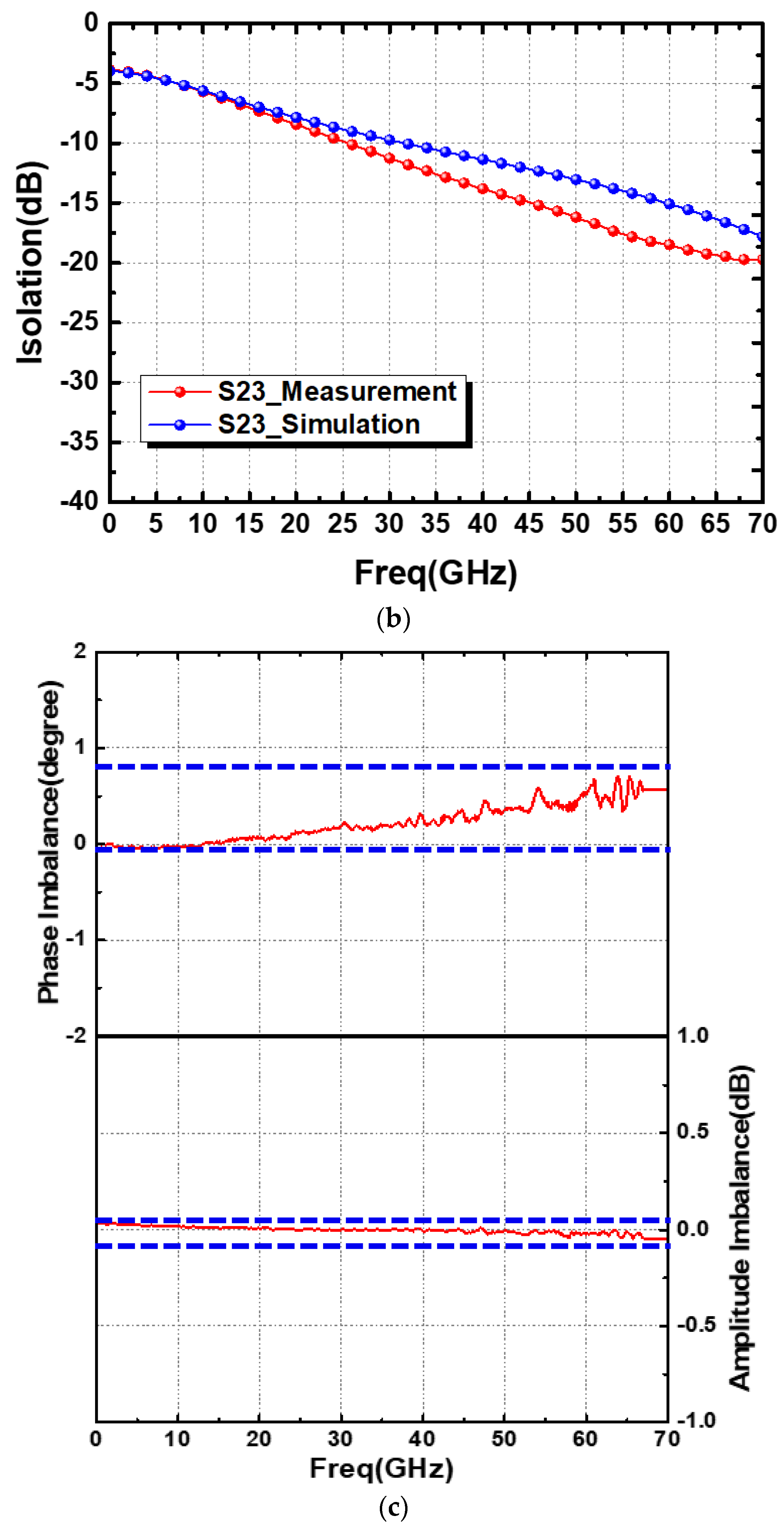

| Ref. | [10] | [11] | [12] | [13] | This Work#1 | This Work#2 |

|---|---|---|---|---|---|---|

| Process | 180 nm CMOS | 130 nm SiGe BiCMOS | 90 nm CMOS | GIPD | 180 nm CMOS | |

| Topology | LC loading | Transformer | Stub-loaded ECPW | Loaded/modified CPW | Straight PCPW | Meandered PCPW |

| Frequency (GHz) | 67 | 62 | 67 | 67 | 60 | |

| I.L. (dB) | <5 | 4.4 | 5.4 | <3.8 | 5.4 | 5.1 |

| Isolation (dB) | 15 | 15 | 14 | >10 | 26.3 | 18.5 |

| Amplitude imbalance (dB) | <0.45 | <0.2 | 0.16 | N/A | <0.1 | <0.03 |

| Phase imbalance (°) | <2 | <5 | 0.45 | <0.3 | <0.7 | <0.4 |

| Area (λ02) | 0.0021 | 0.0012 | 0.0034 | 0.0877 | 0.015 | 0.0018 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pakasiri, C.; Teng, W.-S.; Wang, S. Two CMOS Wilkinson Power Dividers Using High Slow-Wave and Low-Loss Transmission Lines. Micromachines 2024, 15, 1009. https://doi.org/10.3390/mi15081009

Pakasiri C, Teng W-S, Wang S. Two CMOS Wilkinson Power Dividers Using High Slow-Wave and Low-Loss Transmission Lines. Micromachines. 2024; 15(8):1009. https://doi.org/10.3390/mi15081009

Chicago/Turabian StylePakasiri, Chatrpol, Wei-Sen Teng, and Sen Wang. 2024. "Two CMOS Wilkinson Power Dividers Using High Slow-Wave and Low-Loss Transmission Lines" Micromachines 15, no. 8: 1009. https://doi.org/10.3390/mi15081009