4.1. ID-VG Transfer Characteristics of N- and P-Type Transistors

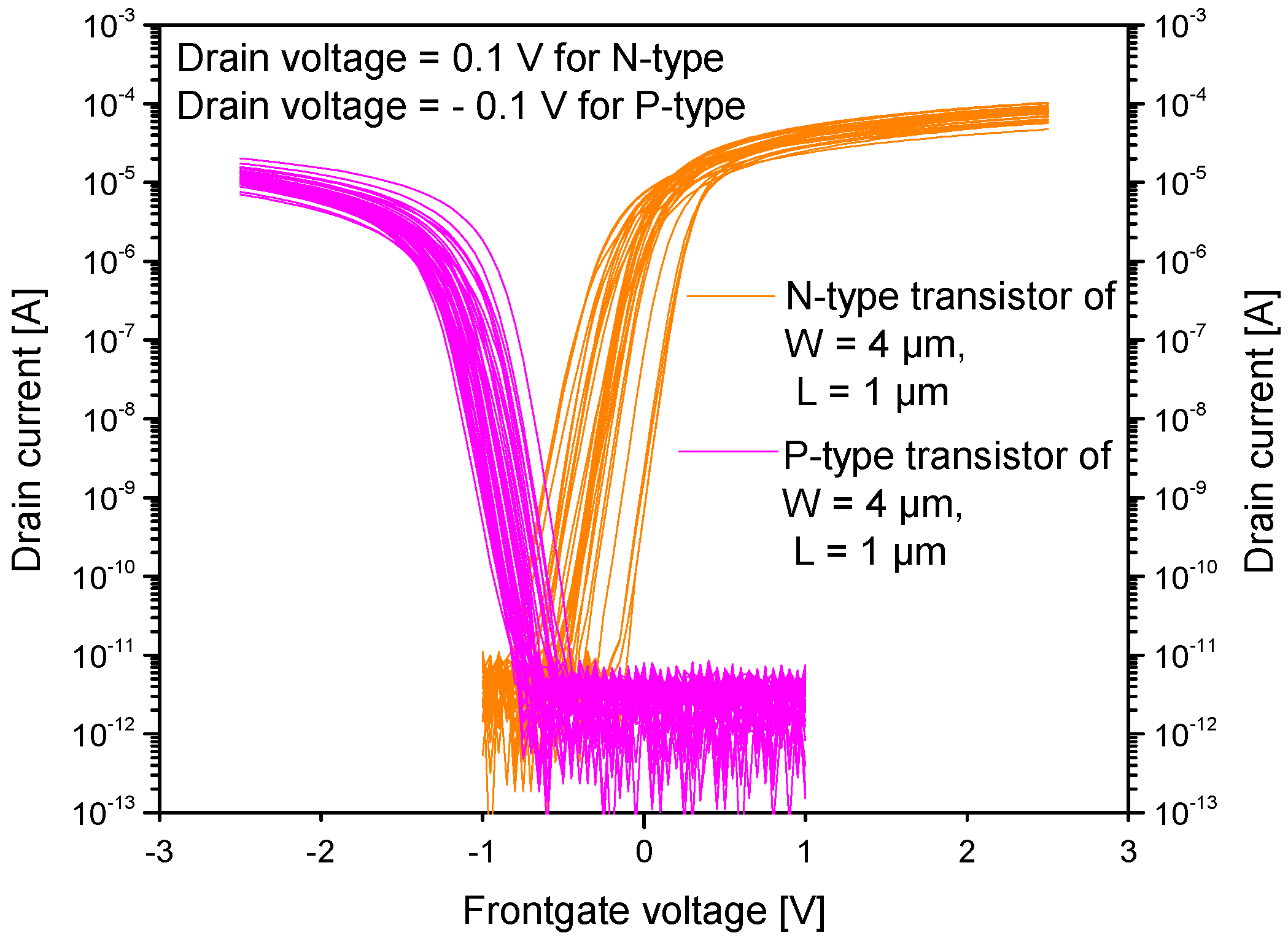

Figure 6 shows the wafer scale I

D-V

G transfer characteristics (at V

BG = 0 V) of standalone NMOS and PMOS transistors manufactured using the same fabrication process as the SiRi pixels. The NMOS and PMOS transistors have a SS of 60–65 mV/dec. The extracted V

TH for NMOS is in the range from −0.3 to 0.3 V while the PMOS transistor has V

TH in the range of −0.9 to −1.1 V.

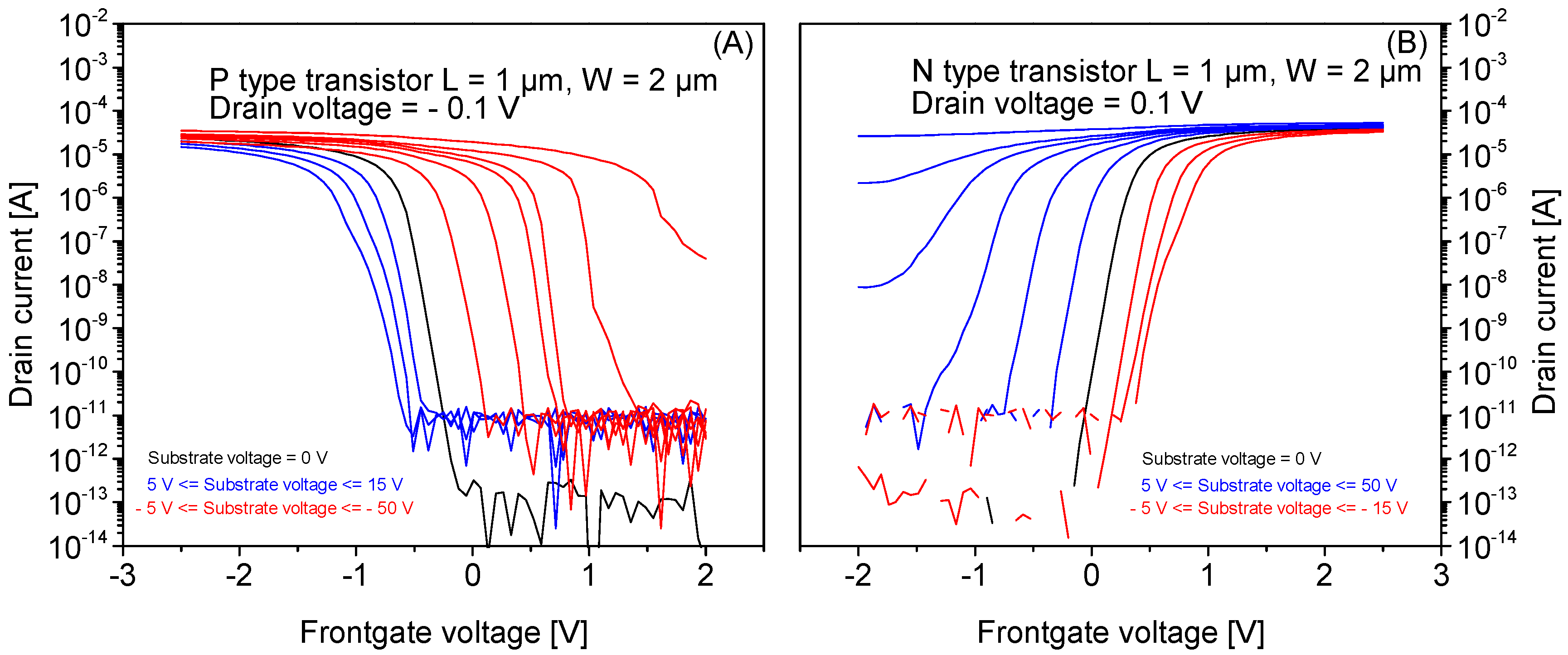

Figure 7A,B shows the I

D-V

G transfer characteristics of a single PMOS and NMOS device manufactured on SOI wafer at different V

BG.

In

Figure 7A, the black color I

D-V

G curve of the PMOS is at V

BG = 0 V. The positive V

BG values cause the I

D-V

G transfer characteristics to shift to the left side (blue color) of the I

D-V

G curve at V

BG = 0 V as the back interface is in accumulation. The V

TH decreases by ~20–25 mV for 1 V change in V

BG. The SS is only slightly influenced. The negative V

BG values cause the I

D-V

G transfer characteristics to shift more towards the right side (red color) of the I

D-V

G curve at V

BG = 0 V as the Si/BOX interface approaches inversion. At −50 V ≥ V

BG ≥ −25 V, the frontgate control over the channel is gradually lost causing the increase in SS. As a result, at V

BG values < −25 V, the transistor can no longer be turned off. For −25 V ≥ V

BG ≥ −5 V, the V

TH linearly depends on V

BG and changes by ~100 mV for −1 V change in V

BG.

Similarly, in

Figure 7B the black color I

D-V

G curve of the NMOS is at V

BG = 0 V. The negative V

BG values cause the I

D-V

G transfer characteristics to shift to the right side (red color) of the black curve as the back interface is in accumulation. The V

TH linearly increases by ~20−25 mV for 1 V change in V

BG. The SS is only slightly influenced. Whereas the positive V

BG values cause the I

D-V

G transfer characteristics to shift more towards the left side (blue color) of the I

D-V

G curve at V

BG = 0 V as the Si/BOX interface approaches inversion. At 50 V ≤ V

BG ≤ 15 V, the frontgate control over the channel is gradually lost causing the increase in SS. As a result, at V

BG values >25 V, the transistor can no longer be turned off. For 15 V ≤ V

BG ≤ 5 V, the V

TH linearly depends on V

BG and changes by ~100 mV for 1 V change in V

BG.

Thus, it was found that the backgate voltage strongly influences the SS and VTH of the MOSFETs and directly impacts the transfer characteristics. As a result, at VBG values ≥ 25 V for NMOS (or −25 V for PMOS), the transistor can no longer be turned off. Thus, it is concluded that, for stable operation of the SiRi pixel, it is important to restrict the VBG in voltage range from −10 to 10 V.

4.2. Backgate Mode of Operation or ID-VBG Transfer Characteristics of N- and P-Type SiRi Pixel Sensors

Figure 8A,B shows the wafer scale backgate mode I

D-V

BG transfer characteristics of P- and N-type SiRi pixels (L = 1 μm and W = 1 μm), respectively, with frontgate voltage of the control transistor fixed at 0 V.

In

Figure 8B, the N-type sensors conduct a current of value ≥ 1 nA from the source to the drain region when V

BG ≥ 15 V while the current values drop to a value of ≤ 1 pA when the V

BG is decreased to values lesser than 10 V confirming that the SiRi pixels exhibit characteristics similar to the N-type MOSFETs. The N-type pixel is turned ON as long as the control transistor is biased in the inversion region (V

G = 0 V). Similarly, in

Figure 8A, the P-type sensors conduct a current of value ≥ 10 nA from the source to the drain region when V

BG ≤ 10 V while the current values drop to a value of ≤ 1 pA when the V

BG is increased to values greater than 15 V confirming that the SiRi sensors exhibit characteristics similar to the P-type MOSFETs. The P-type pixel is turned ON as long as the control transistor is biased in the inversion region (V

G = 0 V). A SS value of 70–80 mV/dec and I

ON/I

OFF ≥ 10

6 was noted for both N- and P-type sensors.

The VTH of the N-type pixel was found to range from 12.5 to 15.5 V while the VTH of the P-type sensor was found to range from 10 to 15 V. This indicates that the number of charges per unit area in the BOX is 2.2 × 1012 cm−2. These first observations of high VTH variations also hint at the importance of the backgate interface between c-Si SiRi sensor/BOX layer.

4.3. Frontgate Mode of Operation or ID-VG Transfer Characteristics of N- and P-Type SiRi Pixel Sensors

Figure 8C,D shows the wafer scale frontgate mode I

D-V

G transfer characteristics of corresponding P- and N-type SiRi pixel devices (L = 1 μm and W = 1 μm), respectively. In

Figure 8C,D, the P-type SiRi pixel was biased with V

BG= −10 V and N-type SiRi pixel device was biased with V

BG= 25 V, respectively. The I

D-V

G transfer characteristics of N- and P-type SiRi pixel devices is similar to the I

D-V

G transfer characteristics of N- and P-type MOSFET devices, respectively. However, in

Figure 8B, the N-type SiRi has high V

TH in backgate mode due to the thick BOX layer. In particular, the N-type SiRi (

Figure 8B) is in the inversion region of operation at V

BG ≥ 20 V. Thus, to turn ON the N-type SiRi pixel in the frontgate mode, the SiRi sensor connected at the output should be biased at V

BG ≥ 20 V. When the N-type SiRi pixel sensor was biased with a V

BG = 25 V, it was observed that the pixel sensor could not be turned OFF (

Figure 8D). This behavior can be understood by referring to the influence of V

BG on the I

D-V

G transfer characteristics of N-type transistors that control the SiRi sensor device (

Figure 6). It can be noted that N-type standalone transistors have an average V

TH of ~0 V and variation of ±0.3 V. Applying a V

BG = 25 V to operate the N-type SiRi pixel sensor in the inversion region pushes the I

D-V

G transfer characteristics of the N-type control transistor to even stronger inversion region (

Figure 7B) where it can no longer be turned OFF. The V

TH of the N-type transistor shifts further to the left side from its ideal operating condition at V

BG = 0 V as it moves towards inversion. In the inversion region, the influence of the V

BG on the control transistor is stronger than that of the frontgate voltage (V

G). Since the NMOS transistor controls the N-type SiRi pixel, even the N-type pixels can no longer be turned OFF for V

BG ≥ 25 V.

Similarly, the P-type SiRi pixel (

Figure 8A) in backgate mode is in the inversion region of operation at V

BG ≤ 10 V. Thus, to turn ON the P-type SiRi pixel, the SiRi sensor connected at the output should be biased at V

BG ≤ 10 V. When the P-type SiRi pixel sensor was biased with a V

BG = −10 V, it was observed that the pixel sensor behaves similar to the P-type MOSFETs (

Figure 8C). This behavior is contrary to that of N-type SiRi pixel shown in

Figure 8D. This can be understood by referring to the influence of V

BG on the I

D-V

G transfer characteristics of P-type transistors that control the SiRi sensor device (

Figure 6). In

Figure 6, it can be noted that P-type standalone transistors have an average V

TH of ~−1.1 V and variation of ±0.1 V. Applying a V

BG = −10 V to operate the P-type SiRi pixel sensor in the inversion region pushes the I

D-V

G transfer characteristics of the P-type control transistor to strong inversion region (

Figure 7A). The V

TH of the P-type pixel sensors is shifted further to the right side from the V

TH of the P-type transistors (

Figure 8C). Particularly, it can be noted that the V

TH of the single P-type pixel sensors is ~0.5 V and variation of ± 0.2 V. However, because of operating the P-type pixels at V

BG = −10 V, a relatively low value, the P-type transistor can still be turned OFF. In

Figure 8C, the P-type pixels exhibit excellent I

ON/I

OFF ≥ 10

6, SS of 70–80 mV/dec and V

TH of 0.5 V (at V

BG = −10 V). However, note that the SiRi connected to the PMOS transistor also behaves as a resistor in series with the PMOS transistor. As a result, the P-type SiRi pixels have a flat saturation characteristic of the ON current. Nonetheless, when operating the P-type pixels for DNA detection or bio-experiments, it is expected to work in the subthreshold region of operation where there is exponential dependence of the drain current with respect to frontgate voltage (V

G). Hence, the resistance arising due to the SiRi pixel will not influence the detection mechanism.

Thus, from the results in

Figure 8C,D, it can be concluded that the operating voltage of the SiRi pixel sensors directly depends on the V

TH of the standalone SiRi sensors connected to the control FET. The quality of the backgate interface between SiRi sensor and BOX plays a key role in determining the operating voltage of the SiRi pixels. If the individual SiRis require larger voltages (>15 V) to turn ON, then the SiRi pixels cannot be turned OFF as the transistors controlling the SiRi sensors are in strong inversion region of operation. Further, the V

TH of the individual SiRi sensors depends on the thickness and quality of the BOX layer in the SOI wafer. Since the BOX layer is relatively thick (145 nm), the voltage required to turn ON and turn OFF the standalone SiRi sensors is also very high (25 V for N-type and −10 V for P-type SiRi). In addition, the fixed charges in the BOX layer will significantly impact the V

TH of the SiRi pixel sensors. A relatively small change of fixed charges of 3 × 10

11 cm

−2 would induce a V

TH shift of 2 V due to the BOX thickness of 145 nm. However, as noted shown in

Figure 8A,B, the V

TH shift is relatively larger (>15 V) indicating that number of fixed charges in the oxide is of the high order ~2.2 × 10

12 cm

−2. This issue of V

TH variation between devices can be overcome by employing SOI wafers with a thinner and high quality BOX layer or by replacing the BOX layer with a metal backgate.

Finally, as shown in

Table 3, it is found that the SiRi pixels operating in the frontgate mode of operation exhibit relatively lower V

TH variation in comparison with SiRi pixels operating in the backgate mode. Particularly, the V

TH of P-type pixel in the backgate mode operation was found to range from 10 to 15 V while it was reduced to a V

TH variation of just 0.3 to 0.7 V in the frontgate mode of operation. The reduction of the V

TH in the frontgate mode of operation is due to employing a PMOS transistor to control the SiRi. It can be seen in

Figure 6 and

Figure 8C that the V

TH of the P-type SiRi pixel follows the same V

TH variation of its respective control P-type transistor. Similarly, in

Table 3, the P-type SiRi pixels operating in the frontgate mode of operation exhibit relatively larger I

ON variation (4 × 10

−7 to 3 × 10

−6 A) in comparison with SiRi pixels operating in the backgate mode (10

−6 to 2.5 × 10

−6 A). We speculate this to arise on account of process variations in the channel resistance of the P-type SiRi that is connected to the P-type control transistor.

4.4. Influence of Backgate Voltage on the SiRi Pixel Sensors in Frontgate Mode of Operation

The mechanism of tuning the V

TH of the SiRi pixel by using the backgate bias can be exploited to match with the operating voltage of the control CMOS circuits. Therefore, we studied the influence of V

BG on the N- and P-type pixels in the frontgate mode operation.

Figure 9A shows the I

D-V

G frontgate transfer characteristics of a single P-type SiRi pixel device of W = 1 μm and L = 1 μm at different V

BG. A systematic V

TH shift of ~40 mV is observed for 1 V change in V

BG. The I

D of the pixel also increases by ~3–8 nA for 1 V change in V

BG.

Figure 9B shows the I

D-V

G frontgate transfer characteristics of a single N-type SiRi pixel device of W = 1 μm and L = 1 μm at different V

BG. Since the controlling NMOS transistor is in strong inversion region for 20 V ≤ V

BG ≤ 25 V, the N-type SiRi cannot be turned OFF.

In

Figure 8A, in the backgate mode, P-type SiRi pixel is operating in the inversion region at V

BG = −10 V. Further, in

Figure 8C, the P-type pixels can be switched ON by applying a V

BG= −10 V to the SiRi connected at the output. However, in

Figure 9A, i for −1 V ≥ V

BG ≥ 0 V, the P-type pixels are in OFF state as the P-type SiRi connected at the output of the pixel is in OFF state. For −4 V ≥ V

BG ≥ −2 V, the P-type SiRi at the output of the pixel is in the weak inversion region. Thus, the I

D of the P-type pixel is lower (50 nA). At the same time, the application of a V

BG = −4 V causes the V

TH of the PMOS control transistor to shift towards the right side as the transistor moves towards strong inversion (

Figure 7A).

A further increase of the V

BG (−20 V ≥ V

BG ≥ −6 V), causes the P-type SiRi at the output of the pixel to move towards the strong inversion. As a result, the I

D of the P-type pixel also increases 80 nA–0.16 μA (

Figure 9A). Concurrently, this increase in V

BG (−20 V ≥ V

BG ≥ −6 V) causes the V

TH of the PMOS control transistor to shift further towards the right side as the transistor moves towards even stronger inversion (

Figure 7A). Eventually, at V

BG ≤ −20 V, the control PMOS transistor can no longer be turned OFF. Since the P-type SiRi pixel is controlled by the PMOS transistor, even the P-type pixels can no longer be turned OFF for V

BG ≤ −20 V.

Note that, in

Figure 8C,D, the frontgate voltage (V

G) of the N- and P-type pixels is swept from −2.5 to 2.5 V. Further increase of the frontgate voltage than the aforementioned range (−2.5 to 2.5 V) will lead to the dielectric breakdown (4 nm SiO

2) in the control transistors. Thus, from this dependence of the N- and P-type SiRi pixels (

Figure 8D and

Figure 9A) on V

BG, it can be concluded that it is important to restrict the V

TH of the N- and P-type SiRi connected at the control FET to low values (5 V ≤ V

BG ≤ 10 V for N-type and −5 V ≥ V

BG ≥ −10 V for P-type sensors). As long as the V

BG value required to turn ON the standalone SiRi sensors is within the operating bounds (−2.5 to 2.5 V) of the transistor controlling them, then the SiRi pixel sensors can be switched ON or OFF. Otherwise, the large V

BG value applied to turn ON the SiRi sensors, will push the controlling transistor in the SiRi pixel device, towards stronger inversion region of operation where the influence of backgate voltage (V

BG) is greater than that of the frontgate (V

G). As a result, the SiRi pixel devices cease to switch OFF. The thickness and quality of the backgate interface or particularly BOX layer in this study will also strongly influence the V

BG required to bias the SiRi sensors.