Improved Current-Sharing Imbalance Control Model Based on Magnetic Ferrite Inductance and a Gate Drive Circuit

Abstract

:1. Introduction

2. Theoretical Basis and Experiments

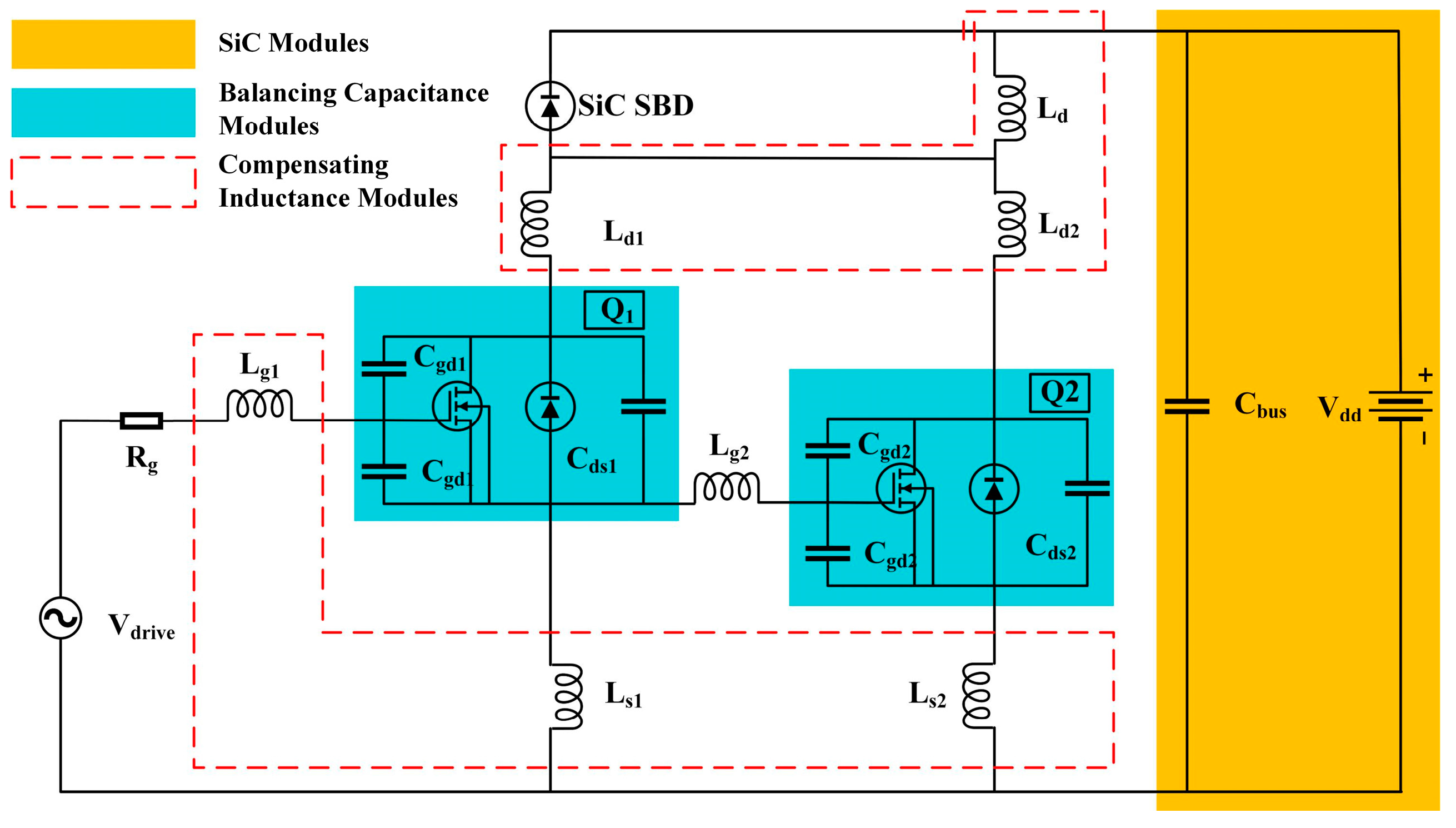

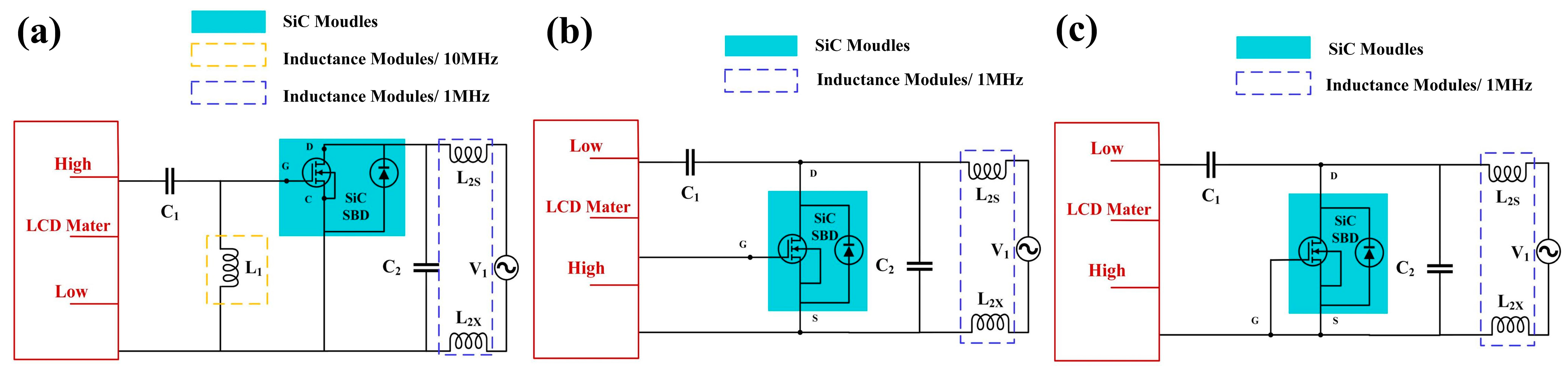

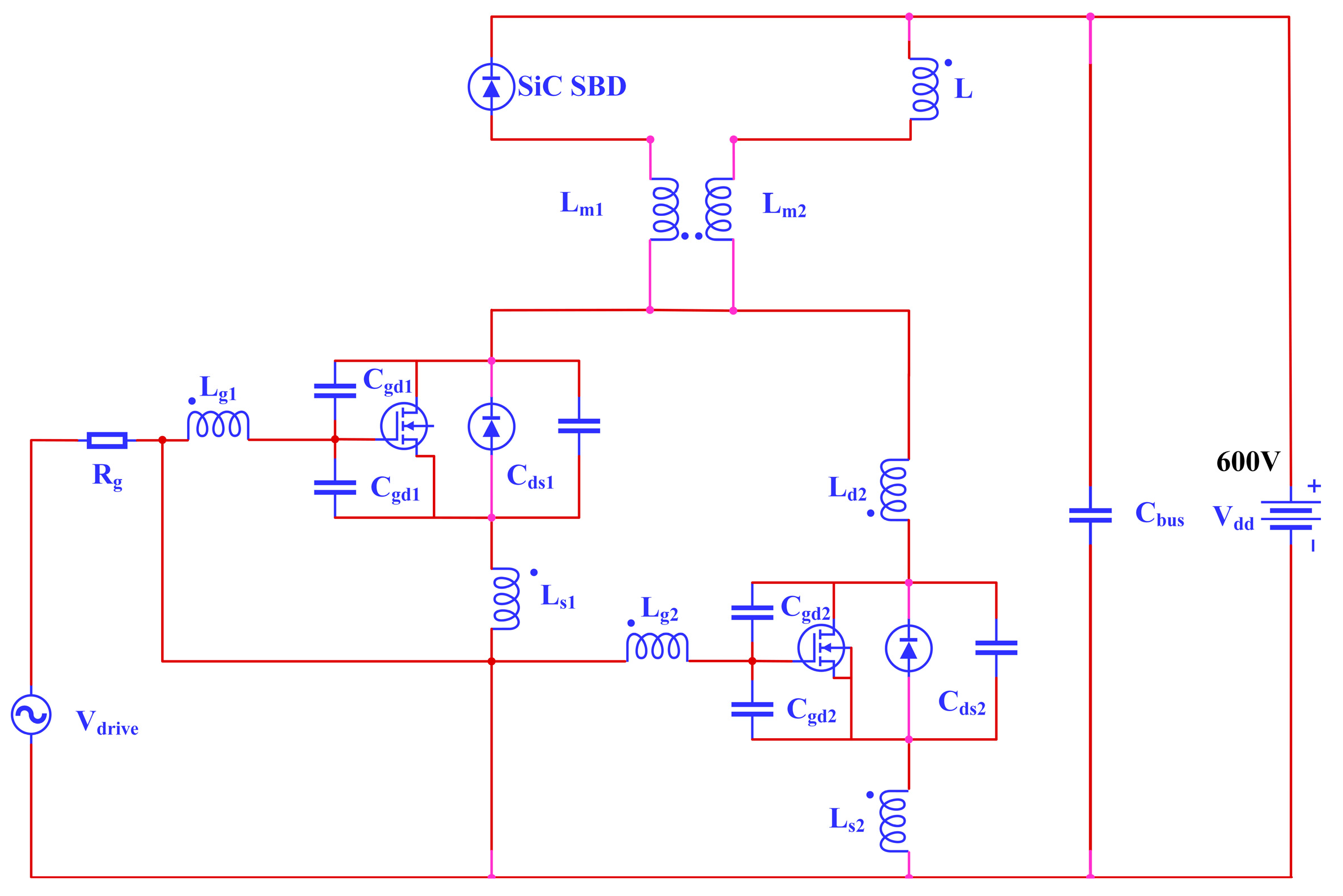

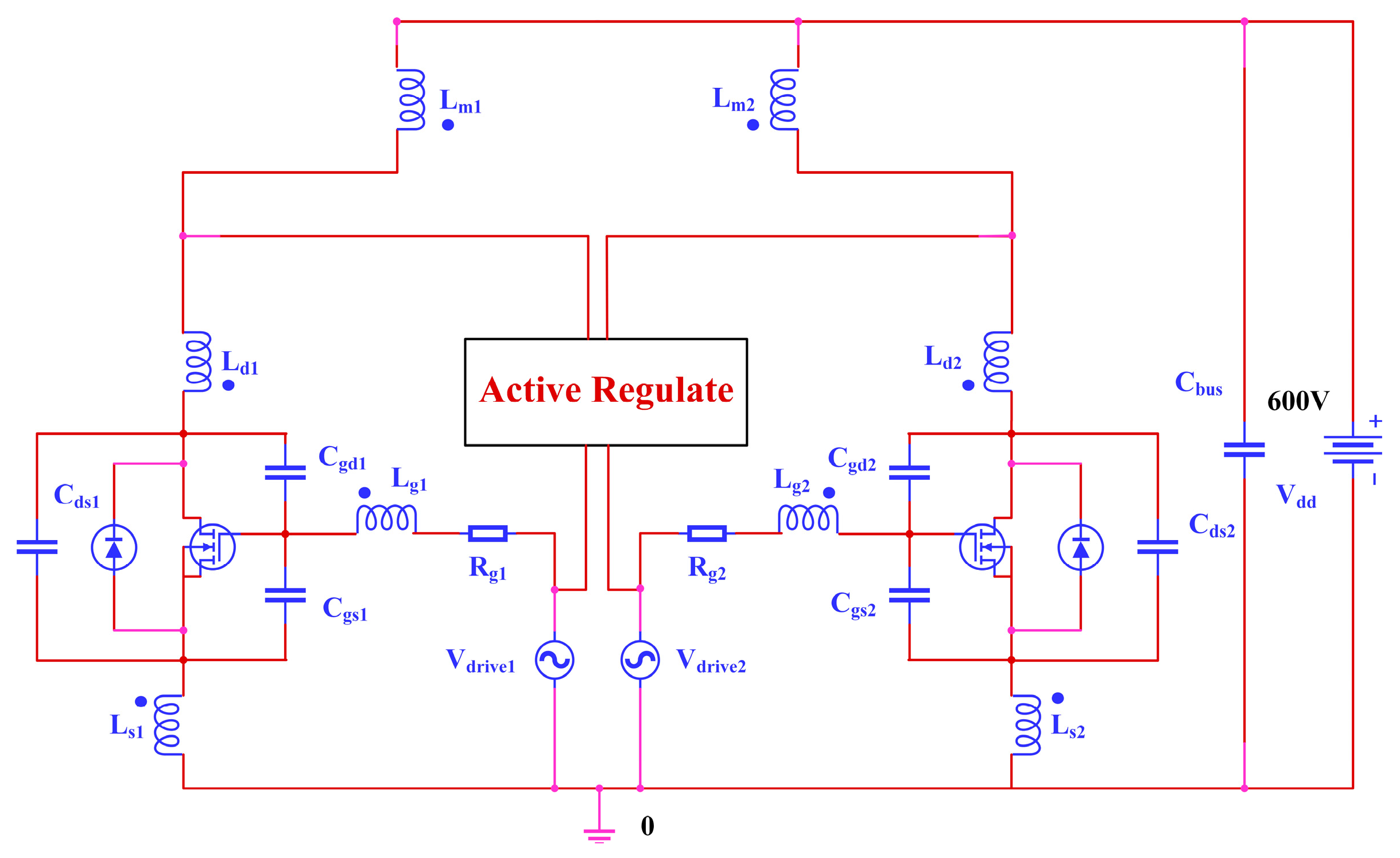

2.1. Design of the Improved Current-Sharing Imbalance Control Model

2.2. Principle of the Improved Current-Sharing imbalance Control Model

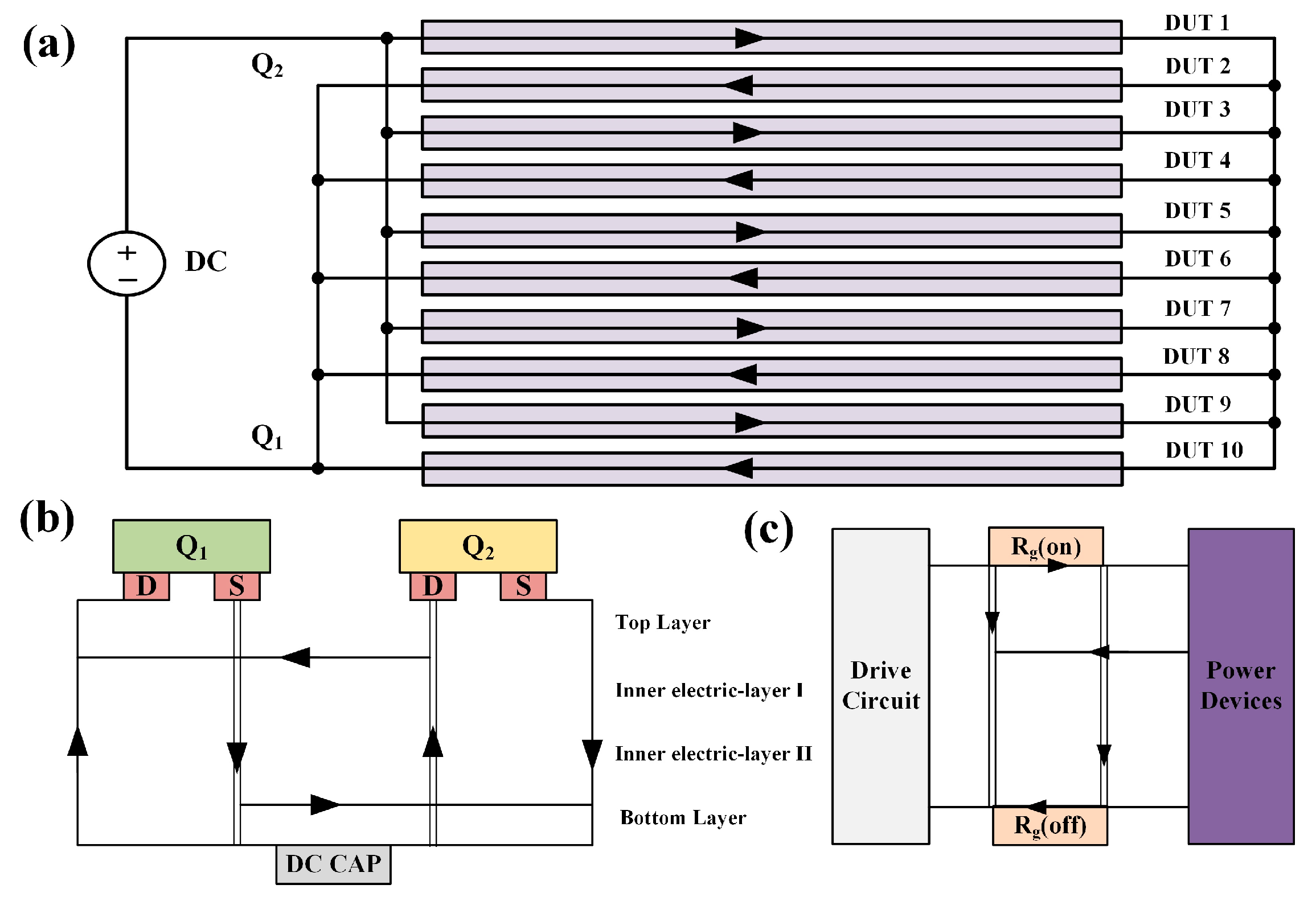

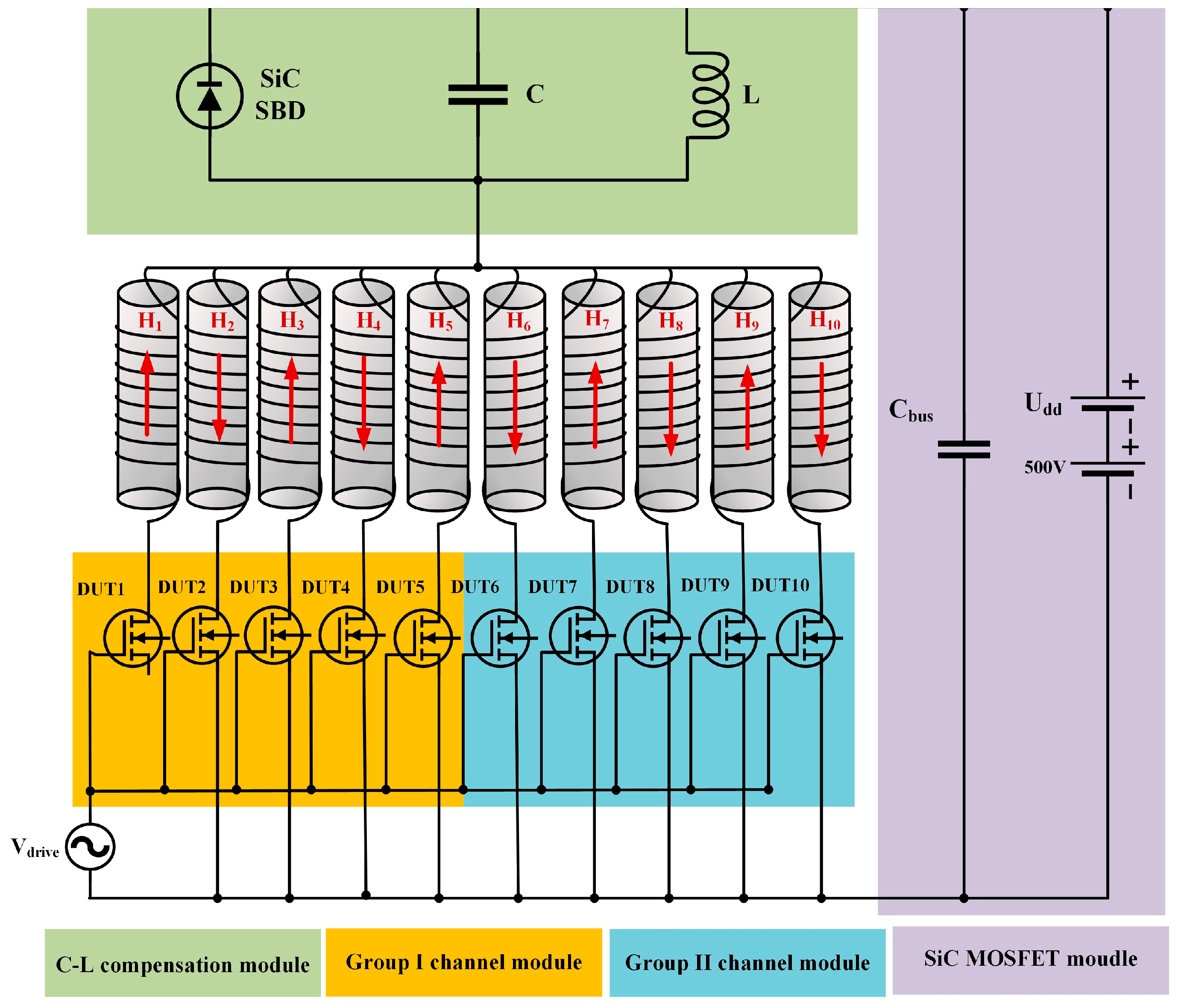

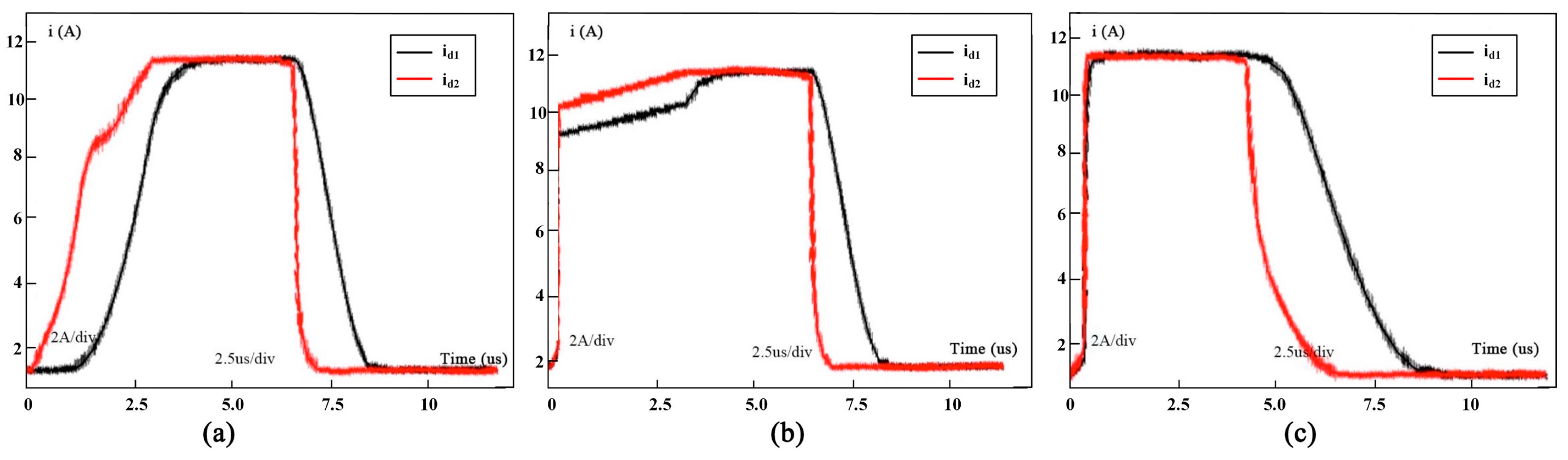

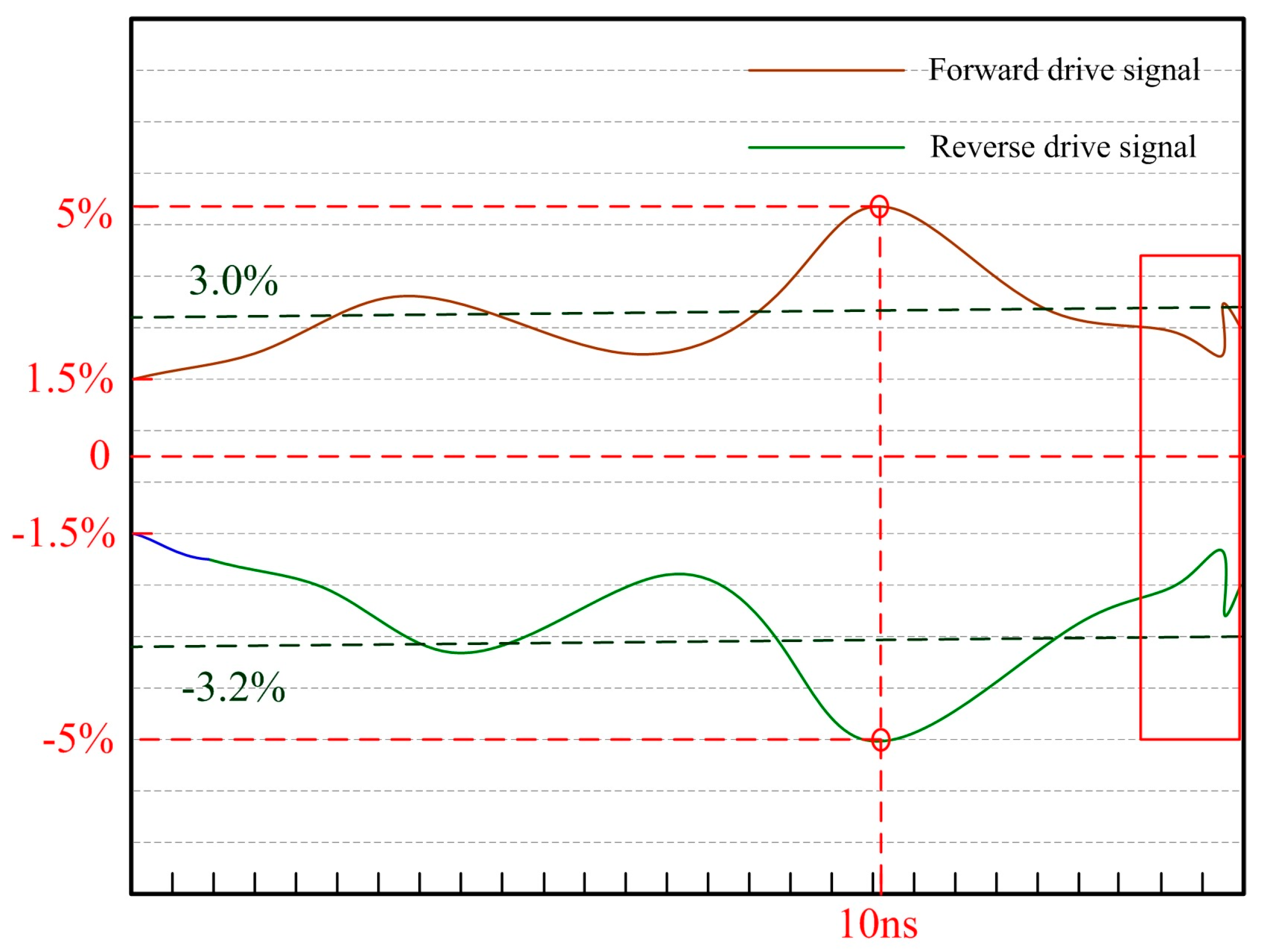

2.3. Improved Double-Pulse Detection Circuit Platform

3. Results and Discussion

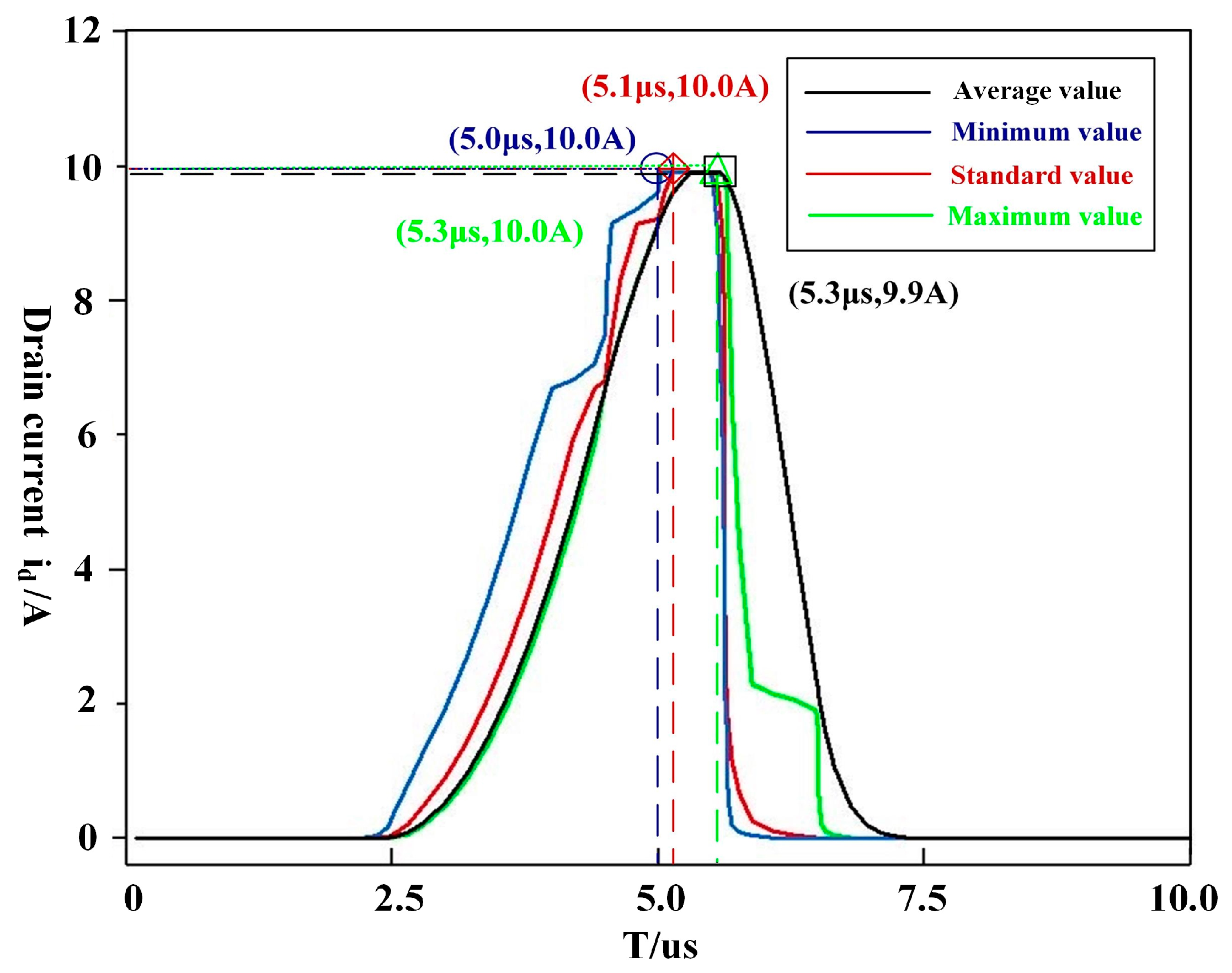

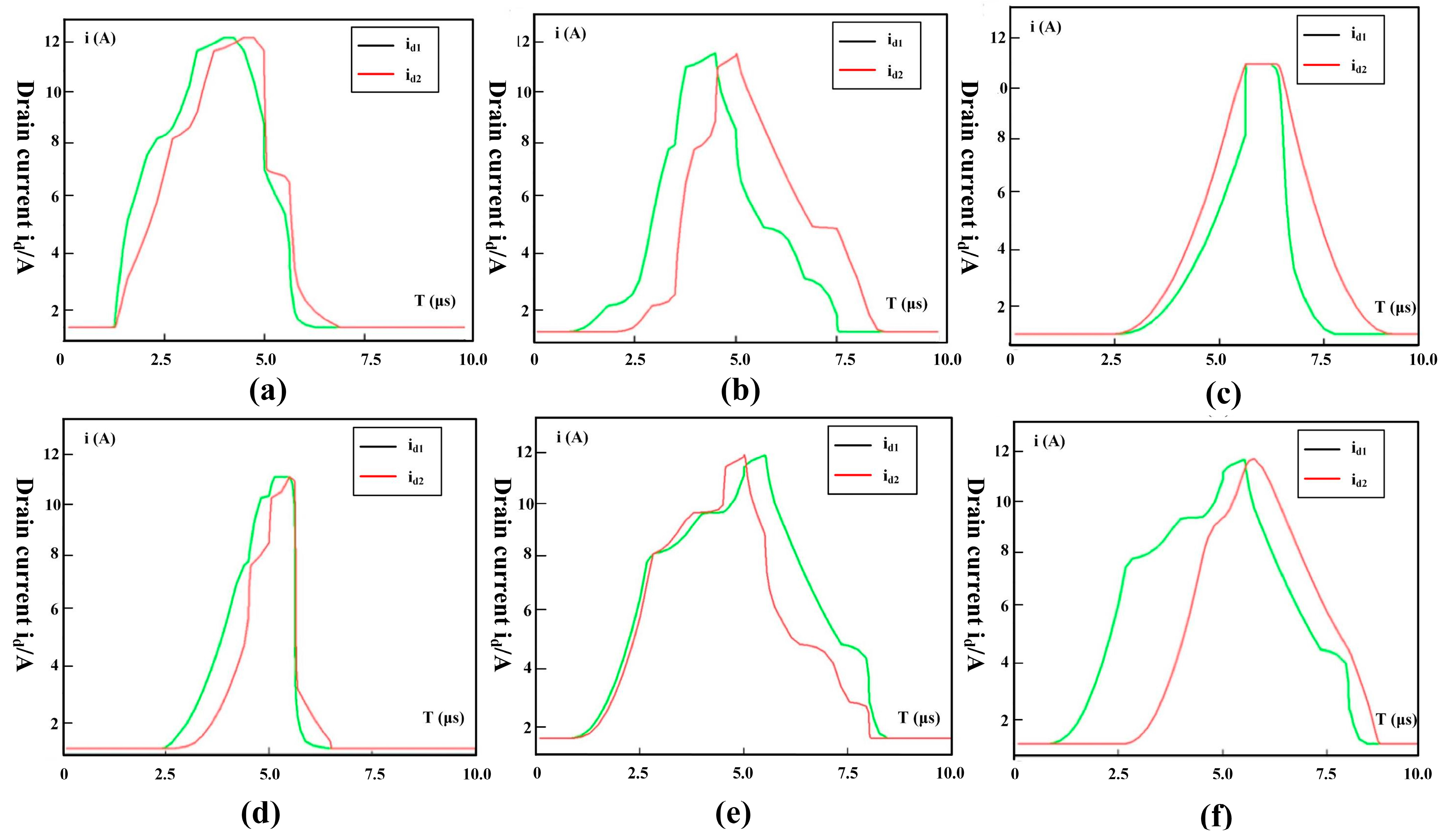

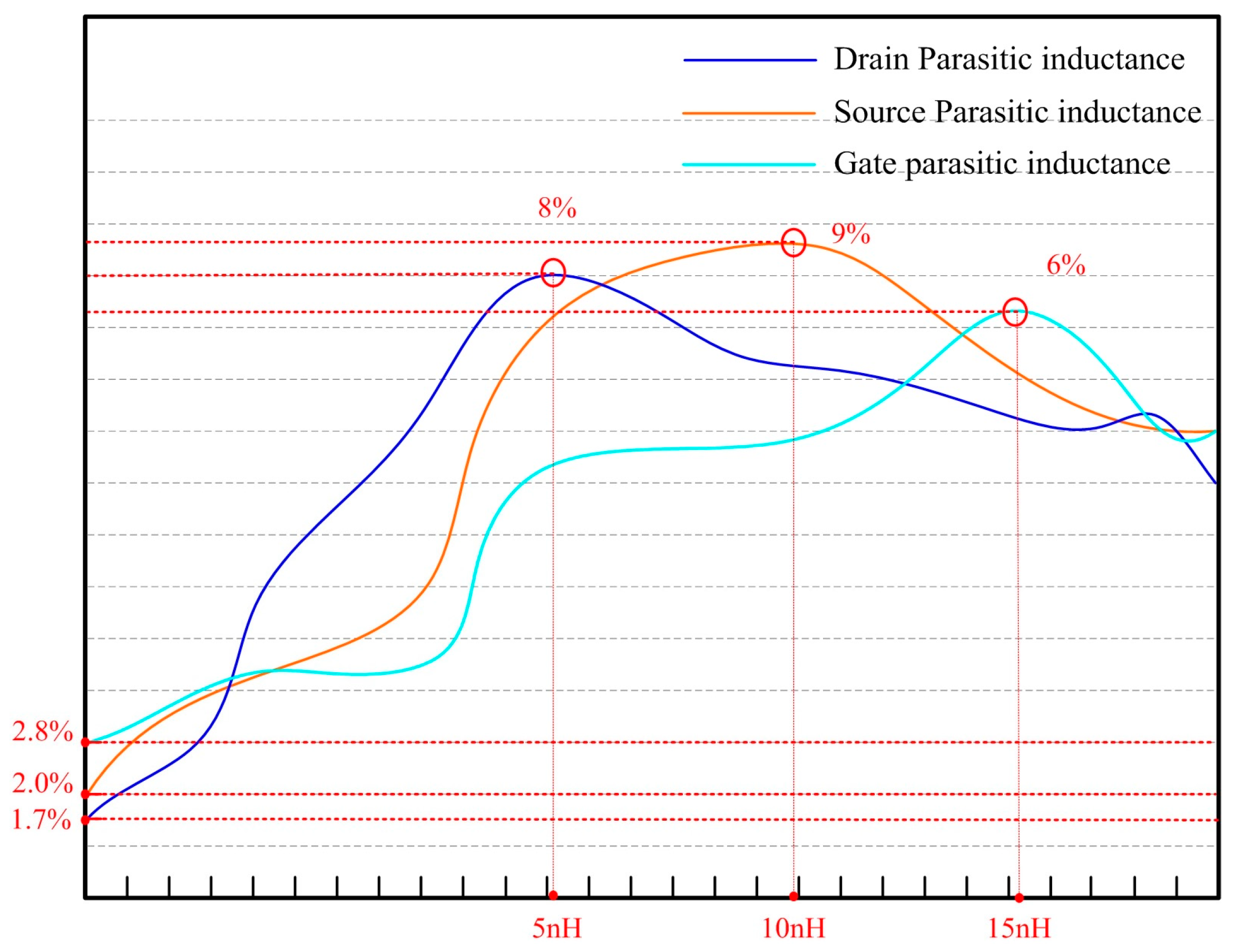

3.1. id/t Simulation on Different Lg

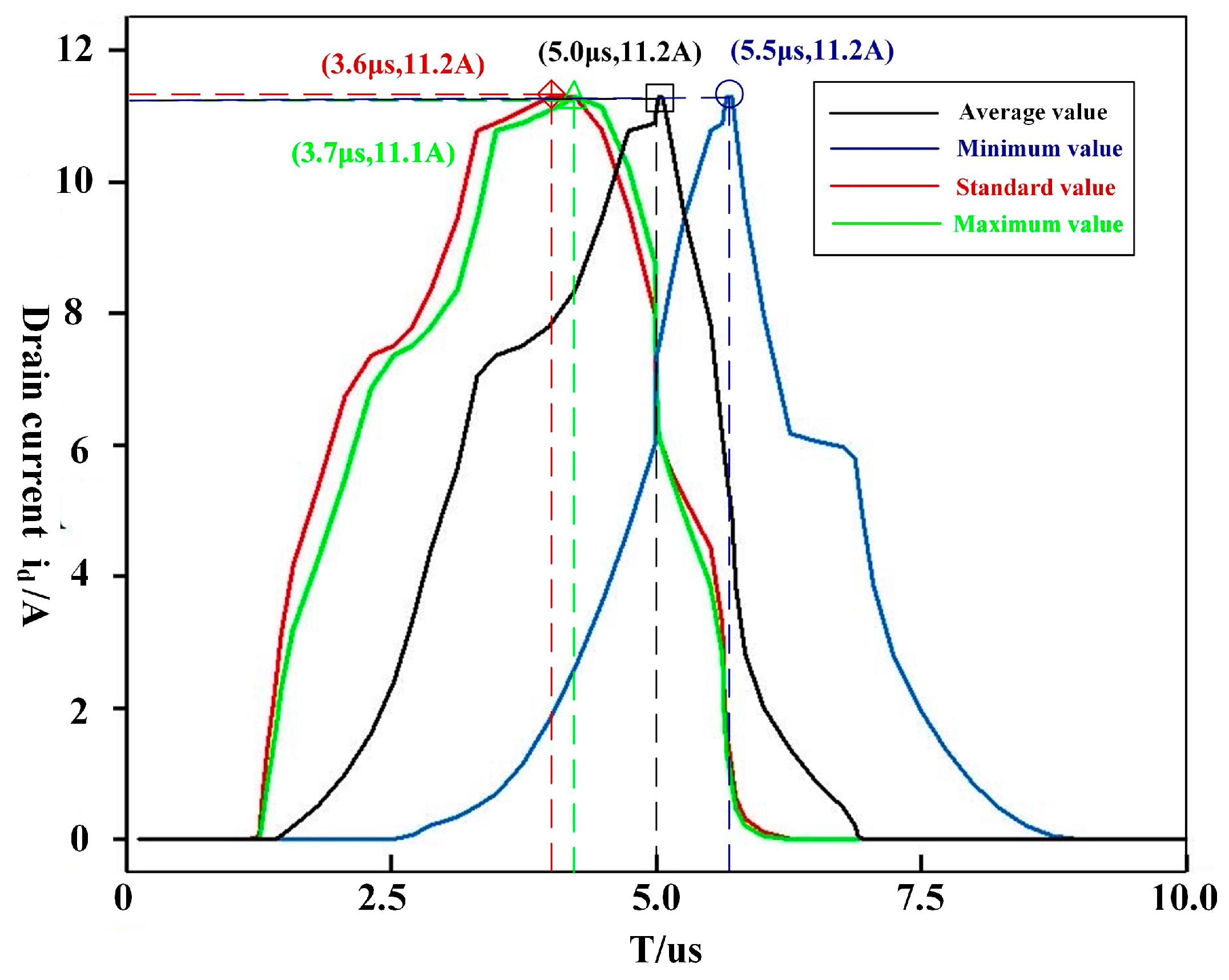

3.2. id/t Simulation on Different Ld

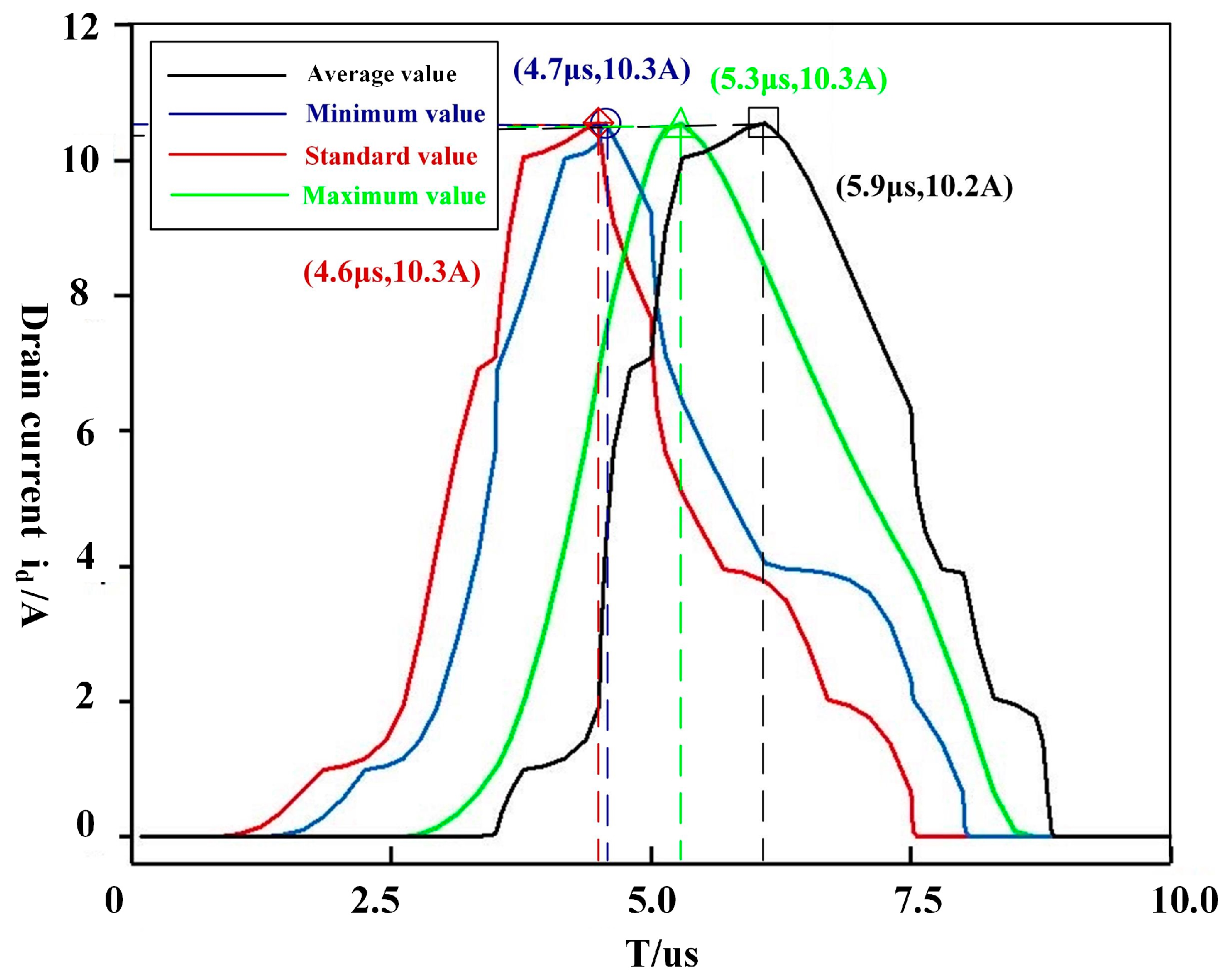

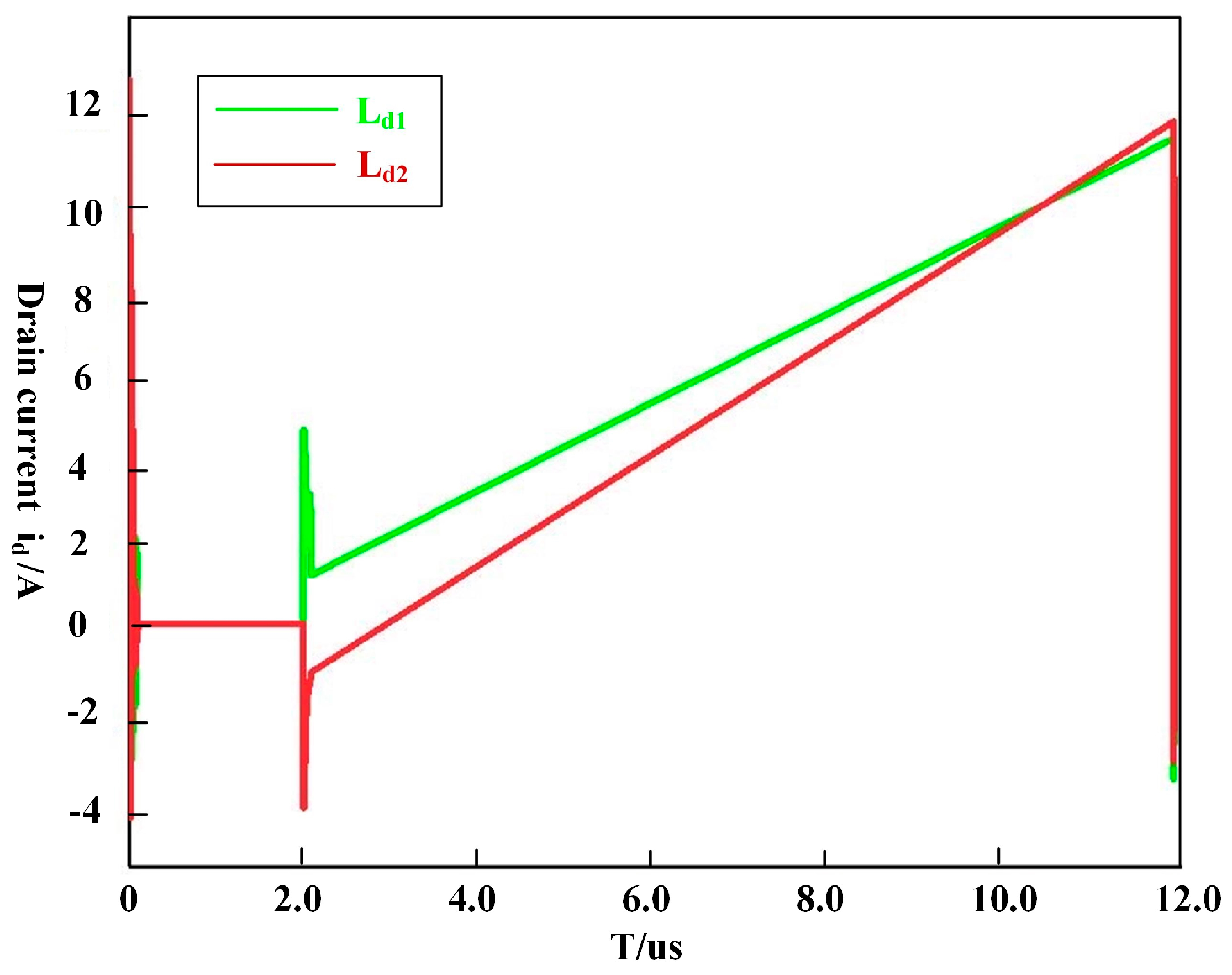

3.3. id/t Simulation on Different Ls

3.4. id/t Simulation on Different Cgs

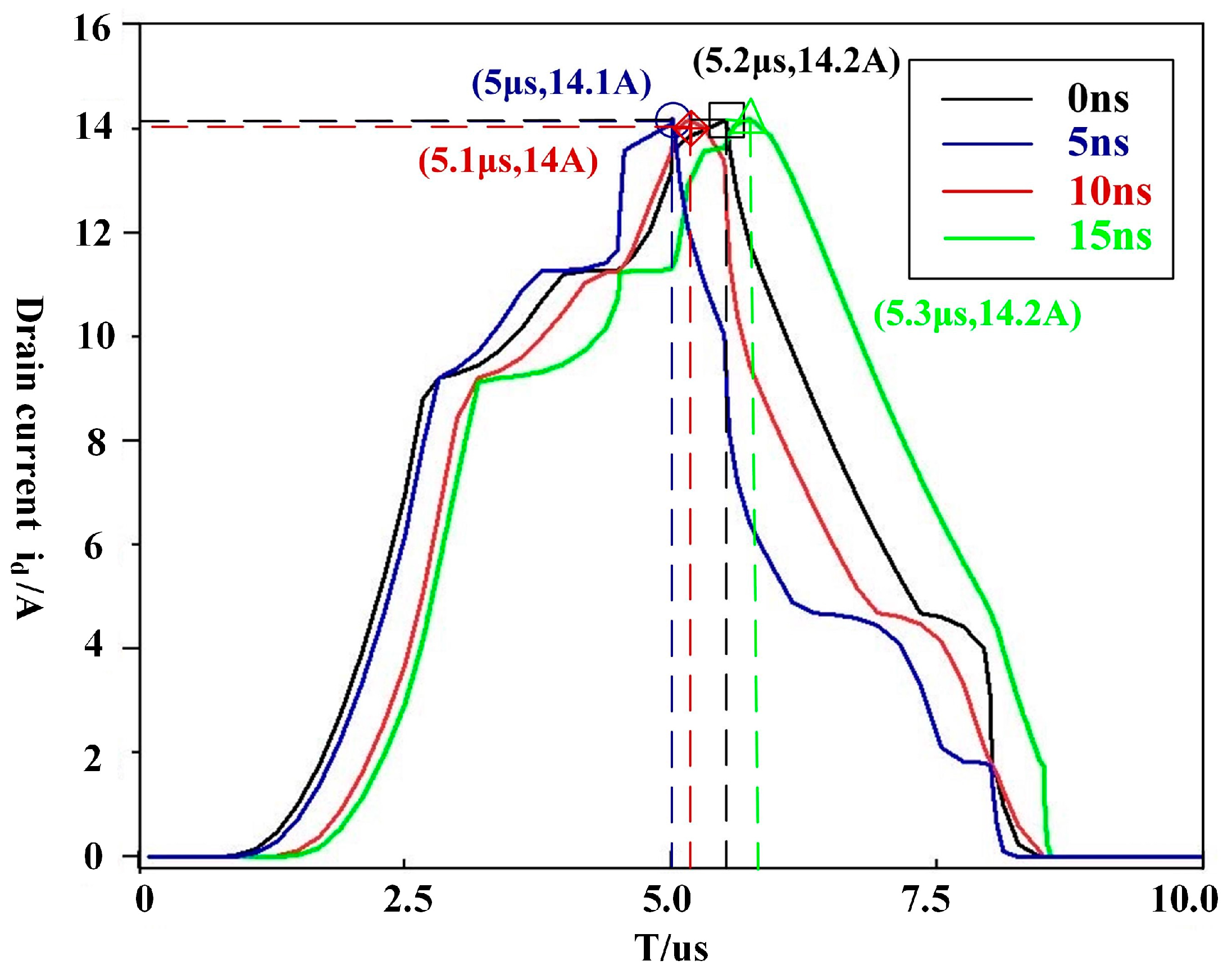

3.5. id/t Simulation on Different td

3.6. id/t Simulation on Different Von

3.7. id/t Simulation on Different Rg

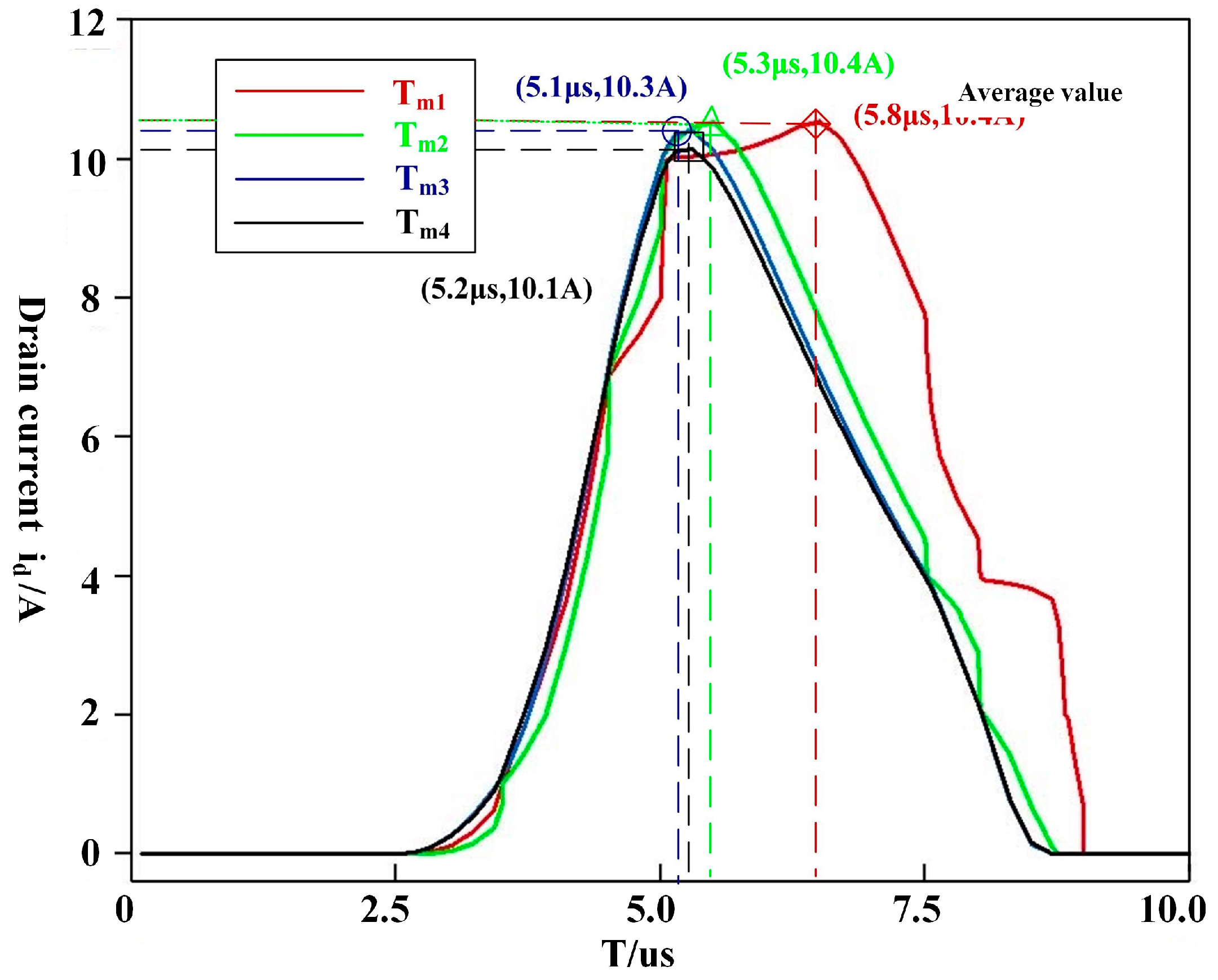

3.8. id/t Simulation on Different ΔTm

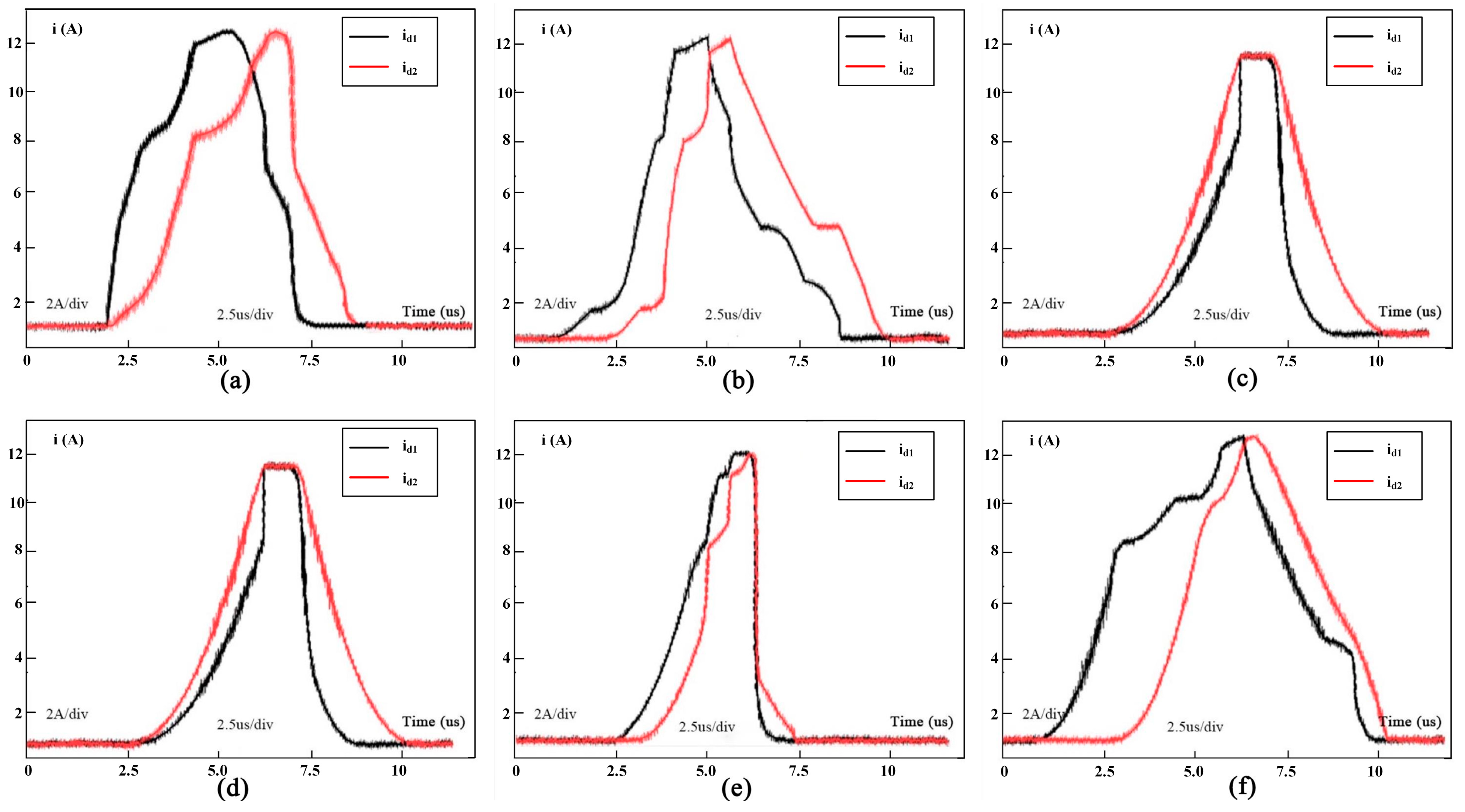

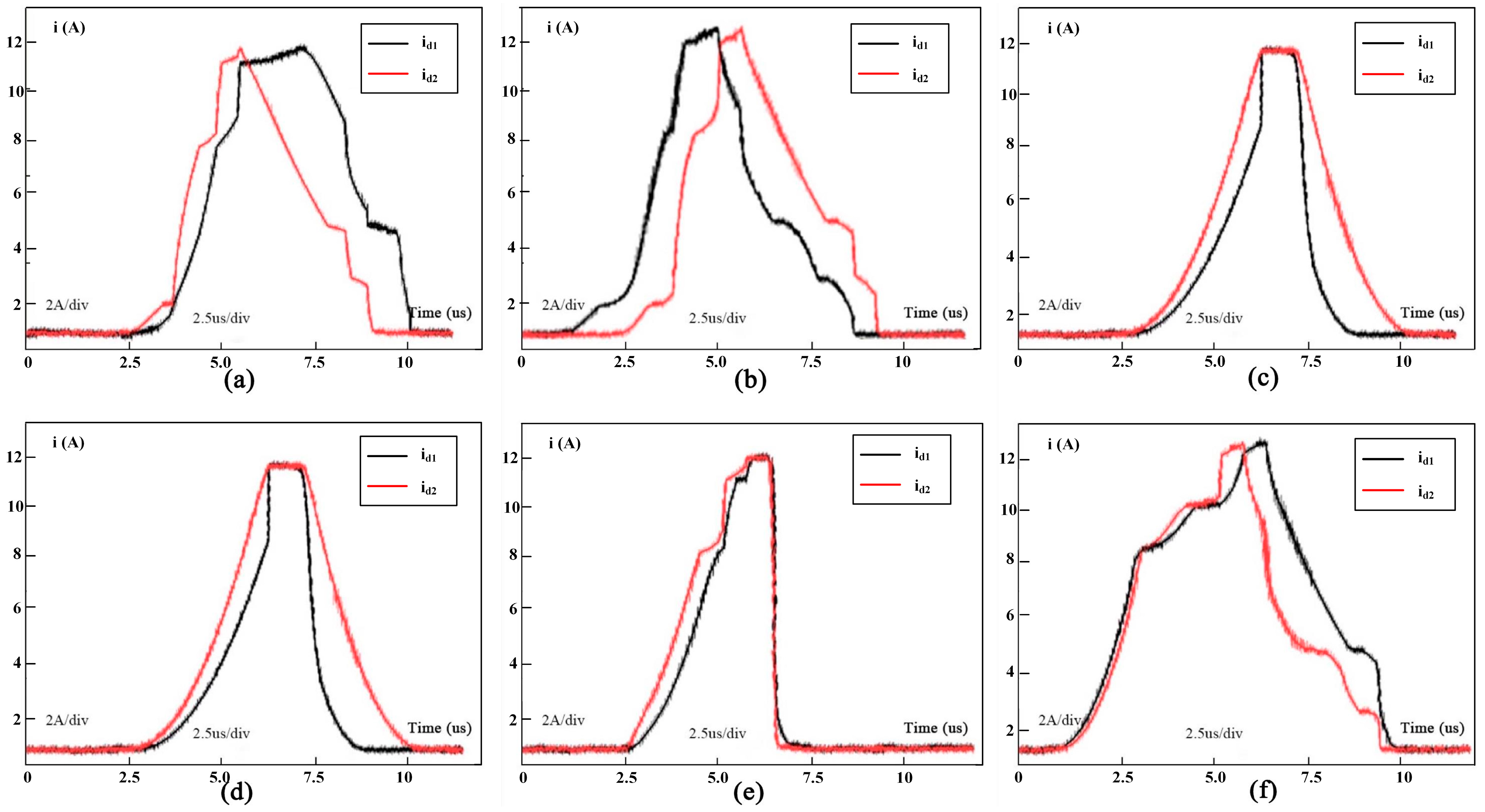

4. Joint Simulation of Multiple Parasitic Parameters in the Double-Pulse Test Circuit

5. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Matsui, K.; Murai, Y.; Watanabe, M.; Kaneko, M.; Ueda, F. A pulsewidth-modulated inverter with parallel connected transistors using current-sharing reactors. IEEE Tran. Power Electron. 1993, 8, 186–191. [Google Scholar] [CrossRef]

- Cooper, J.A.; Melloch, M.R.; Singh, R.; Agarwal, A.; Palmour, J.W. Status and prospects for SiC power MOSFETs. IEEE Trans. Electron. Devices 2002, 49, 658–664. [Google Scholar] [CrossRef]

- Li, H.; Munk-Nielsen, S.; Bȩczkowski, S.; Wang, X. A novel DBC layout for current imbalance mitigation in SiC MOSFET multichip power modules. IEEE Tran. Power Electron. 2016, 31, 8042–8045. [Google Scholar] [CrossRef]

- Miao, W.; Fang, L.; Xu, L. A double-end sourced wire-bonded multichip SiC MOSFET power module with improved dynamic current sharing. IEEE Trans. Emerg. Sel. Topics Power Electron. 2017, 5, 1828–1836. [Google Scholar]

- Lelis, A.; Habersat, D.; Urciuoli, D.; Schroen, E.; Nouketcha, F.; Green, R. Updated key issues for SiC MOSFET reliability. Meet. Abstr. 2020, MA2020-02, 1838. [Google Scholar] [CrossRef]

- Abuogo, J.; Zao, Z.; Ke, J. Linear regression model for screening SiC MOSFETs for paralleling to minimize transient current imbalance. IOP Conf. Ser. Mater. Sci. Eng. 2019, 533, 012011. [Google Scholar] [CrossRef]

- Sadik, D.P.; Colmenares, J.; Tolstoy, G.; Peftitsis, D.; Bakowski, M.; Rabkowski, J.; Nee, H.P. Short-Circuit Protection Circuits for Silicon-Carbide Power Transistors. IEEE Trans. Ind. Electron. 2016, 63, 1995–2004. [Google Scholar] [CrossRef]

- Liu, X.G.; He, J.; Gu, L.; Hao, H.K.; Zhao, A.Q.; Tan, Q.Y. Research on current imbalance law of bus-bar caused by inter-turn short circuit of dry-type air-core reactor. IOP Conf. Ser.: Earth Envmagnetic. Sci. 2018, 188, 012036. [Google Scholar] [CrossRef]

- Ji, S.; Laitinen, M.; Huang, X.; Sun, J.; Giewont, W.; Wang, F.; Tolert, L.M. Short-Circuit Characterization and Protection of 10-kV SiC MOSFET. IEEE Tran. Power Electron. 2019, 34, 1755–1767. [Google Scholar] [CrossRef]

- Zhang, H.; Guo, H.-X.; Zhang, F.-Q.; Pan, X.-Y.; Liu, Y.-T.; Gu, Z.-Q.; Ju, A.-A.; Ouyang, X.-P. Sensitivity of heavy-ion-induced single event burnout in SiC MOSFET. Chin. Phys. B 2020, 31, 018501. [Google Scholar] [CrossRef]

- Tega, N.; Sato, S.; Shima, A. Comparison of extremely high-temperature characteristics of planar and three-dimensional SiC MOSFETs. IEEE Electron Device Lett. 2019, 40, 1382–1384. [Google Scholar] [CrossRef]

- Zeng, Z.; Shao, W.; Hu, B.; Kang, S.; Liao, X.; Li, H.; Ran, L. Active current sharing of paralleled SiC MOSFETs by coupling inductors. Proc. CSEE 2017, 37, 2068–2080. [Google Scholar]

- Xun, Q.; Xun, B.; Li, Z.; Wang, P.; Cai, Z. Application of SiC power electronic devices in secondary power source for aircraft. Renew. Sust. Energ. Rev. 2017, 70, 1336–1342. [Google Scholar] [CrossRef]

- Hu, J.; Alatise, O.; Gonzalez, J.A.O.; Bonyadi, R.; Alexakis, P.; Ran, L.; Mawby, P. Robustness and Balancing of Parallel-Connected Power Devices: SiC Versus CoolMOS. IEEE Trans. Ind. Electron. 2016, 63, 2092–2102. [Google Scholar] [CrossRef]

- Lim, J.-K.; Peftitsis, D.; Rabkowski, J.; Bakowski, M.; Nee, H.-P. Analysis and experimental verification of the influence of fabrication process tolerances and circuit parasitics on transient current sharing of parallel-connected SiC JFETs. IEEE Tran. Power Electron. 2014, 29, 2180–2191. [Google Scholar] [CrossRef]

- Lu, Z.; Li, C.; Zhu, A.; Luo, H.; Li, C.; Li, C.; He, X. Medium voltage soft-switching DC/DC converter with series-connected SiC MOSFETs. IEEE Tran. Power Electron. 2021, 36, 1451–1462. [Google Scholar] [CrossRef]

- Bahmani, M.A.; Thiringer, T.; Rabiei, A.; Abdulahovic, T. Comparative study of a multi-MW high-power density DC transformer with an optimized high-frequency magnetics in all-DC offshore wind farm. IEEE Trans. Power Deliv. 2016, 31, 857–866. [Google Scholar] [CrossRef]

- Scheuermann, U. Reliability challenges of automotive power electronics. Microelectron. Reliab. 2009, 49, 1319–1325. [Google Scholar] [CrossRef]

- Ke, J.; Zhao, Z.; Sun, P.; Zou, Q.; Cui, X.; Yang, F. Influence of devices parameters on the current sharing of paralleled SiC MOSFETs using statistics analysis. Semicond. Tech. 2018, 43, 181–187. [Google Scholar]

- Li, Y.; Liang, M.; Chen, J.G.; Zheng, T.Q.; Guo, H.B. A low gate turn-off impedance driver for suppressing crosstalk of SiC MOSFET based on different discrete packages. IEEE Trans. Emerg. Sel. Topics Power Electron. 2019, 7, 353–365. [Google Scholar] [CrossRef]

- Bahman, A.S.; Iannuzzo, F.; Uhrenfeldt, C.; Blaabjerg, F.; Munk-Nielsen, S. Modeling of short-circuit-related thermal stress in aged IGBT modules. IEEE Trans. Ind. Appl. 2017, 53, 4788–4795. [Google Scholar] [CrossRef]

- Li, H.; Zhou, W.; Wang, X.; Munk-Nielsen, S.; Li, D.; Wang, Y.; Dai, X. Influence of paralleling dies and paralleling half-bridges on transient current distribution in multichip power modules. IEEE Tran. Power Electron. 2018, 33, 6483–6487. [Google Scholar] [CrossRef]

- Ji, S.; Zheng, S.; Wang, F.; Tolbert, L.M. Temperature-dependent characterization, modeling, and switching speed-limitation analysis of third-generation 10-kV SiC MOSFET. IEEE Tran. Power Electron. 2018, 33, 4317–4327. [Google Scholar] [CrossRef]

- Mao, Y.; Miao, Z.; Wang, C.; Ngo, K.D.T. Balancing of peak currents between paralleled SiC MOSFETs by drive-source resistors and coupled power-source inductors. IEEE Trans. Ind. Electron. 2017, 64, 8334–8343. [Google Scholar] [CrossRef]

- Mao, Y.; Miao, Z.; Wang, C.; Ngo, K.D.T. Passive Balancing of peak currents between paralleled MOSFETs with unequal threshold voltages. IEEE Tran. Power Electron. 2017, 32, 3273–3277. [Google Scholar] [CrossRef]

- Miao, Z.; Mao, Y.; Lu, G.-Q.; Ngo, K.D.T. Magnetic integration into a silicon carbide power module for current balancing. IEEE Tran. Power Electron. 2019, 34, 11026–11035. [Google Scholar] [CrossRef]

- Eni, E.P.; Bęczkowski, S.; Munk-Nielsen, S.; Kerekes, T.; Teodorescu, R.; Juluri, R.R.; Julsgaard, B.; VanBrunt, E.; Hull, B.; Sabri, S.; et al. Short-circuit degradation of 10-kV 10A SiC MOSFET. IEEE Tran. Power Electron. 2017, 32, 9342–9354. [Google Scholar] [CrossRef]

- Wang, J.; Jiang, X.; Li, Z.; Shen, Z. Short-circuit ruggedness and failure mechanisms of Si/SiC hybrid switch. IEEE Tran. Power Electron. 2019, 34, 2771–2780. [Google Scholar] [CrossRef]

- Lee, S.; Kim, K.; Shim, M.; Nam, I. A digital signal processing based detection circuit for short-circuit protection of SiC MOSFET. IEEE Tran. Power Electron. 2021, 36, 13379–13382. [Google Scholar] [CrossRef]

- Wei, J.; Liu, S.; Zhao, H.; Fu, H.; Zhang, X.; Li, S.; Sun, W. Verification of single-pulse avalanche failure mechanism for double-trench SiC power MOSFETs. IEEE Trans. Emerg. Sel. Topics Power Electron. 2021, 9, 2190–2200. [Google Scholar] [CrossRef]

| Physical Symbol | Physical Meaning | Typical Values | Test Conditions | Unit |

|---|---|---|---|---|

| Rdson | On resistance | 80 | Vds = 20 V id = 20 A | mΩ |

| Rg | Gate-drive resistance | 4.6 | Ω | |

| gm | Transconductance | 9.8 | S | |

| Ciss | Input capacitance | 950 | Vgs = 0 V Vds = 1000 Vf = 100 kHz Vac = 25 mV | pF |

| Coss | Output capacitance | 80 | pF | |

| Crss | Reverse transfer capacitance | 6.5 | pF | |

| Lg | Gate parasitic inductance | 15 | nH | |

| Ld | Drain parasitic inductance | 6 | nH | |

| Ls | Source parasitic inductance | 9 | nH | |

| Qgs | Gate–source charge | 10.8 | Vds = 800 V Vgs = 200 V id =20 A | nC |

| Qgd | Gate–drain charge | 18 | nC | |

| Qds | Drain–source charge | 49.2 | nC | |

| Cgs | Gate–source capacitance | 54 | pF | |

| Cgd | Gate–drain capacitance | 30 | pF | |

| Cds | Drain–source capacitance | 61.5 | pF |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tian, H.; Li, Y.; Zhang, Q.; Xiao, N.; Wang, J.; Liu, H.; Li, Y. Improved Current-Sharing Imbalance Control Model Based on Magnetic Ferrite Inductance and a Gate Drive Circuit. Machines 2023, 11, 197. https://doi.org/10.3390/machines11020197

Tian H, Li Y, Zhang Q, Xiao N, Wang J, Liu H, Li Y. Improved Current-Sharing Imbalance Control Model Based on Magnetic Ferrite Inductance and a Gate Drive Circuit. Machines. 2023; 11(2):197. https://doi.org/10.3390/machines11020197

Chicago/Turabian StyleTian, Haitao, Yuhong Li, Qiang Zhang, Ningru Xiao, Jingjing Wang, Hongwei Liu, and Yuqiang Li. 2023. "Improved Current-Sharing Imbalance Control Model Based on Magnetic Ferrite Inductance and a Gate Drive Circuit" Machines 11, no. 2: 197. https://doi.org/10.3390/machines11020197