Chip Appearance Inspection Method for High-Precision SMT Equipment

Abstract

:1. Introduction

- A multi-order fractional DWPD algorithm is proposed to extract features from chip images.

- The clustering algorithm based on the variational Bayesian Gaussian mixture model is adopted to select image features.

- A chip appearance defect-detection method based on the multi-order fractional DWPD is conducted.

2. Background

2.1. Discrete Wavelet Packet Decomposition

2.2. Multi-Order Fractional Discrete Wavelet Packet Decomposition

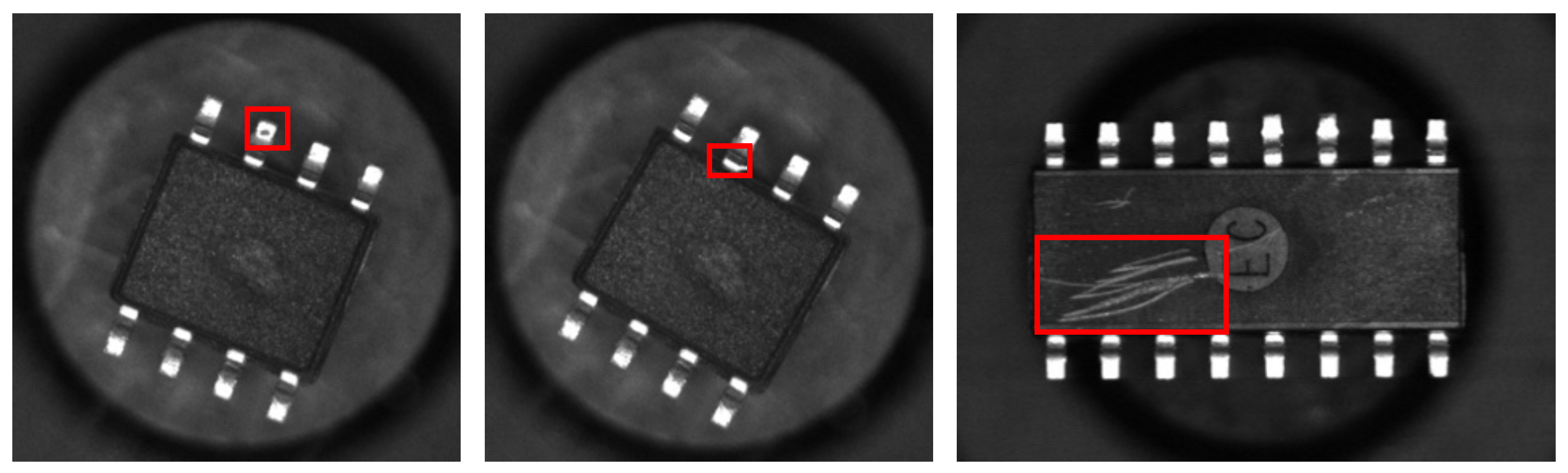

3. Chip Appearance Defect Detection Based on Multi-Order Fractional DWPD

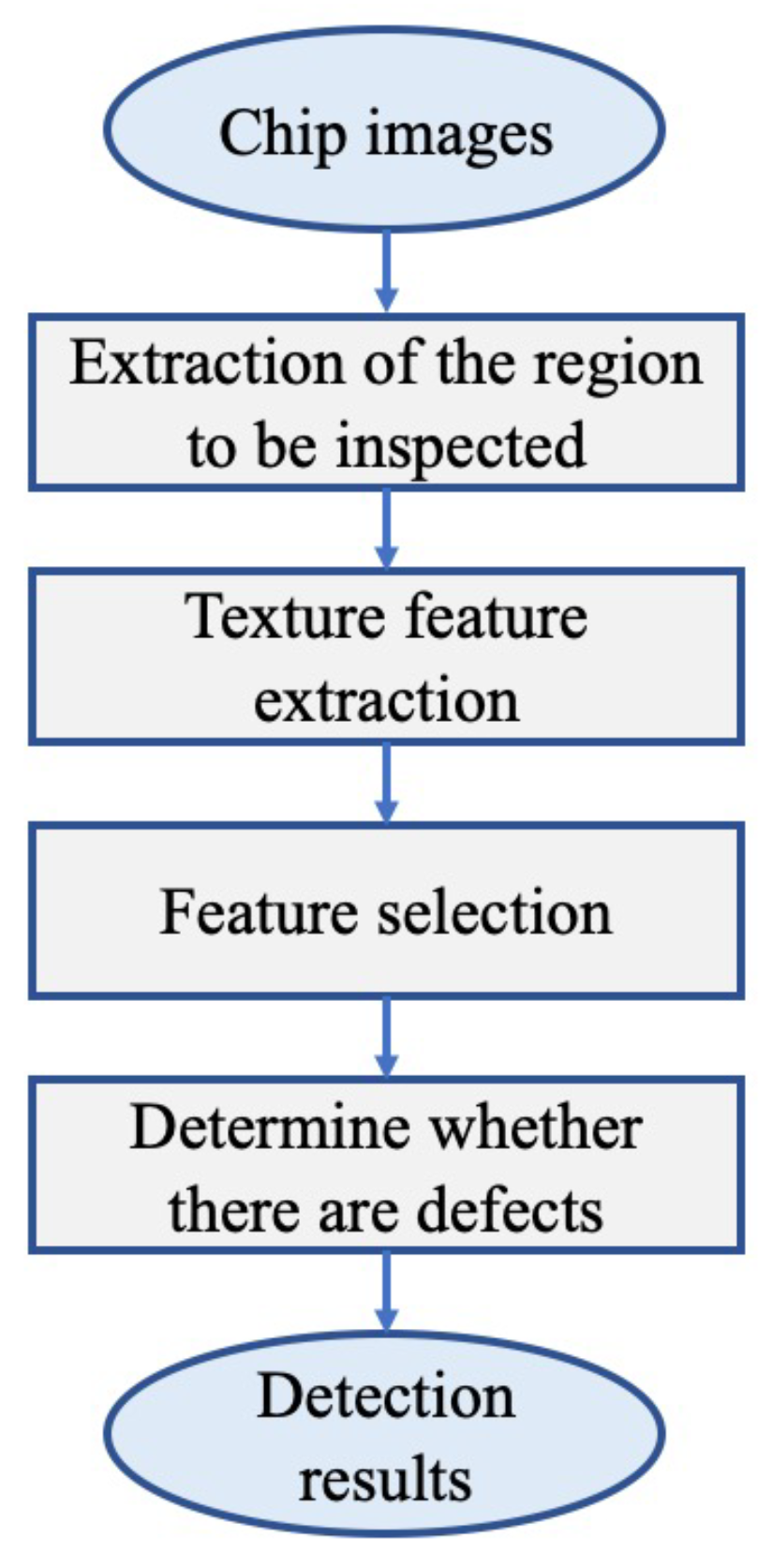

3.1. Steps of the Appearance Defect-Detection Method

- (1)

- Extract the lead and body regions from chip images using the image segmentation algorithm with the asymmetric Laplace mixture model [24] and connected-component labelling algorithm;

- (2)

- (3)

- Select the image features of the region to be inspected;

- (4)

- Determine whether the region to be inspected is defective with the support vector machine-based classifier and extracted image features.

3.2. Extraction Algorithm of the Region to Be Inspected

- (1)

- Classify pixels of the chip image into two categories using the image segmentation algorithm with the asymmetric Laplace mixture model, among which the one with a larger average grey value is the potential lead pixel of the chip image.

- (2)

- Calculate the connected components of potential lead pixels in the chip image using the connected-component labelling algorithm, and take these regions as the potential lead regions.

- (3)

- Estimate the bounding rectangles with rotation angles for each potential lead region, and calculate their rectangularity using the following equation:where is the area of the potential lead region, i.e., pixels, and is the area of the bounding rectangle with a rotation angle.

- (4)

- Identify the regions for which the size does not meet the standard or for which the rectangle is too small in the potential lead regions as jamming regions, and then, eliminate these regions from the potential lead regions. If the number of screened lead regions is inconsistent with that of the standard chip, the chip is considered to have the defect “the number of lead regions does not match”, and the subsequent defect-detection steps are stopped.

- (5)

- Estimate the bounding rectangle with a rotation angle of all lead pixels by taking the pixels in the screened lead region as the lead pixels of the chip, and take the position and rotation angle of the bounding rectangle as those of the chip in the image.

- (6)

- Rotate the chip image according to the rotation angle of the chip to make the chip horizontal in the image. The lead and body regions of the chip from the rotated image are extracted according to the parameters and position of the chip.

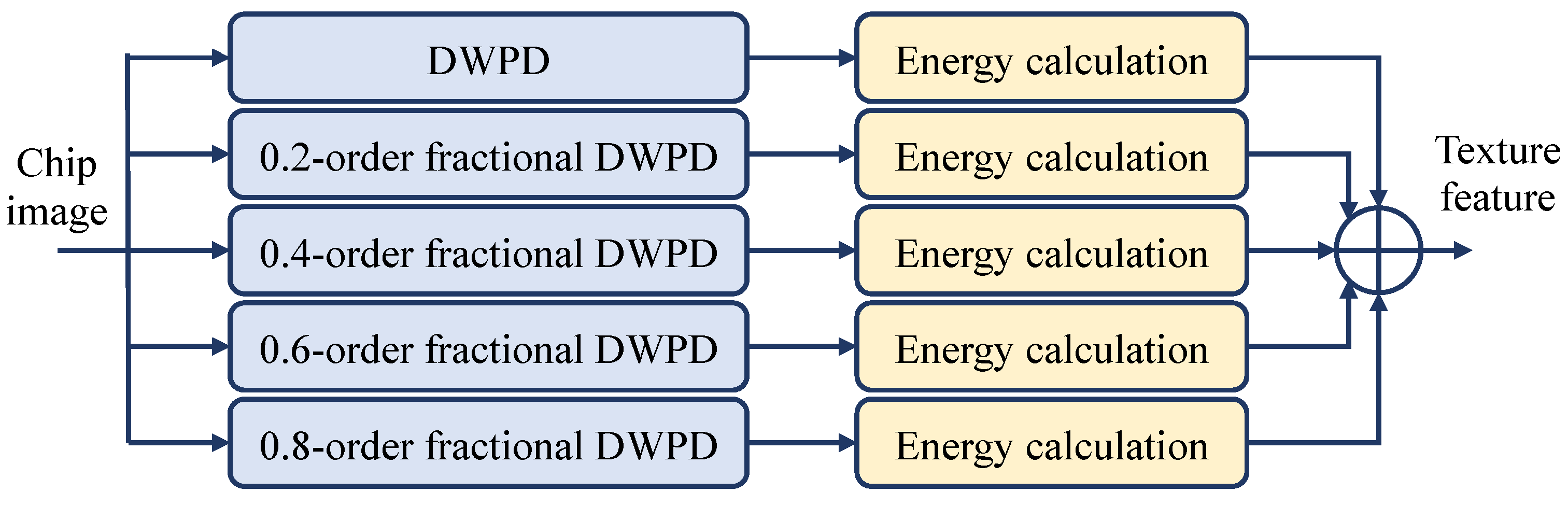

3.3. Texture Feature Extraction Based on Multi-Order Fractional DWPD

- (1)

- The first case: The chip image was decomposed using the traditional 2D DWPD algorithm.

- (2)

- The second case: The chip image was decomposed with the 2D multi-order fractional DWPD algorithm. Since the value range of the order of 2D multi-order fractional DWPD algorithm was within , the chip image was decomposed by the 2D fractional DWPD algorithm of 0.2-order, 0.4-order, 0.6-order, and 0.8-order.

3.4. Image Feature Selection Based on Variational Bayesian Algorithm

- (1)

- Cluster features with clustering algorithms such as k-means and minimum spanning tree so that the features of different classes are mutually independent.

- (2)

- Take the feature closest to the center of the class as the representative feature in each class, and compose the final feature subset of all the representative features of the class.

| Algorithm 1 Pseudcode of the proposed method. |

| Input: Chip image I |

| Output: Whether the chip is defective |

|

4. Experimental Verification

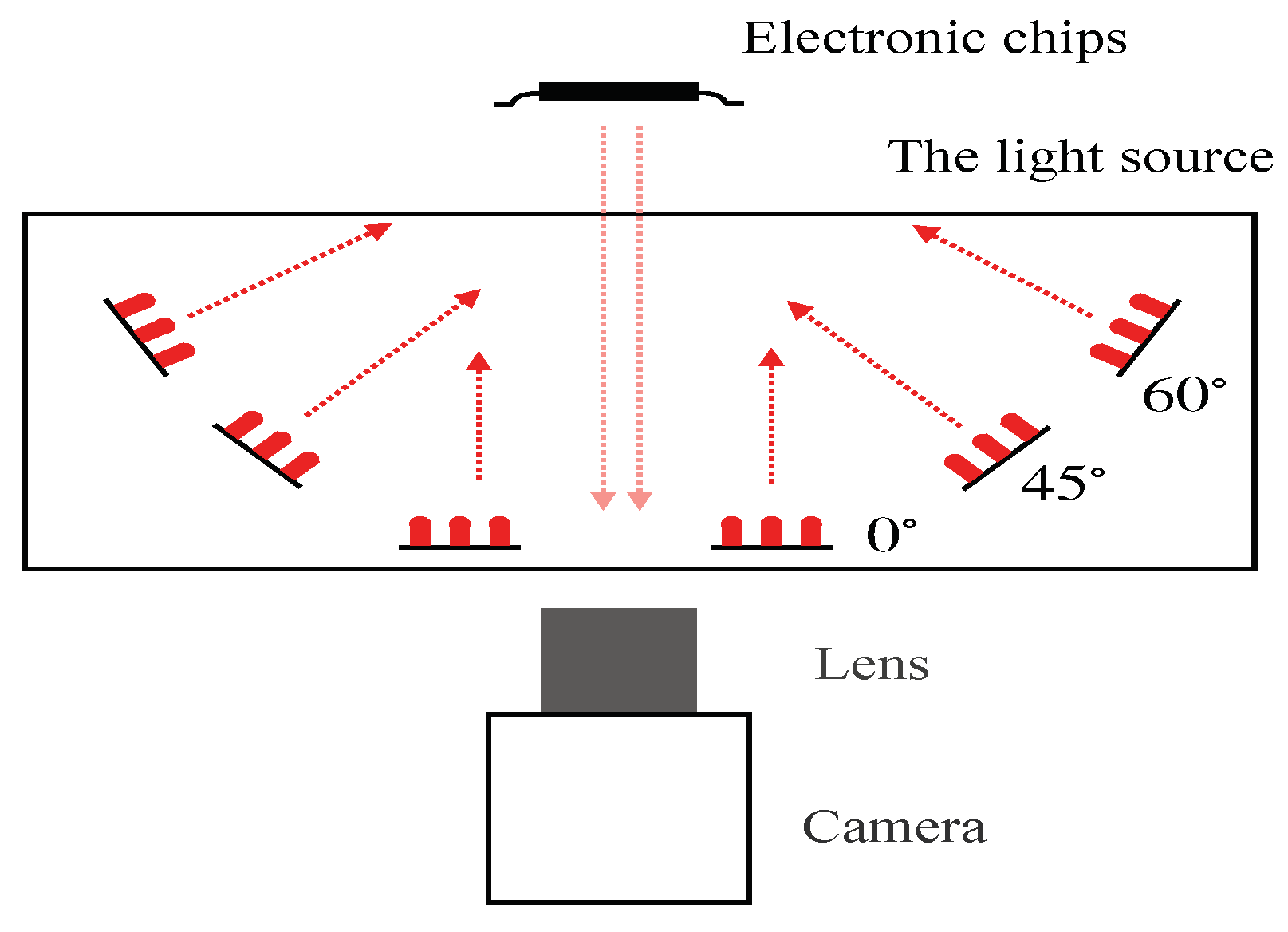

4.1. Experimental Design

4.2. Results and Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| SMT | Surface Mount Technology |

| WPD | Wavelet Packet Decomposition |

| DWT | Discrete Wavelet Transform |

| DWPD | Discrete Wavelet Packet Decomposition |

| CCD | Charge Coupled Device |

References

- Zhao, L.; Shi, P. Machine learning assisted aggregation schemes for optical cross-connect in hybrid electrical/optical data center networks. OSA Contin. 2020, 3, 2573–2590. [Google Scholar] [CrossRef]

- Gaggero, M.; Caviglione, L. Model predictive control for energy-efficient, quality-aware, and secure virtual machine placement. IEEE Trans. Autom. Sci. Eng. 2019, 16, 420–432. [Google Scholar] [CrossRef]

- Wang, H.; Zhou, A.; Hsu, C.-H.; Xiao, X.; Yang, F. Provision of data-intensive services through energy- and QoS-aware virtual machine placement in national cloud data centers. IEEE Trans. Emerg. Top. Comput. 2016, 4, 290–300. [Google Scholar] [CrossRef]

- Guo, Y.; Stolyar, A.L.; Walid, A. Shadow-routing based dynamic algorithms for virtual machine placement in a network cloud. IEEE Trans. Emerg. Top. Comput. 2018, 6, 209–220. [Google Scholar] [CrossRef]

- Xu, G. Appearance Inspection System of IC Chips Based on Machine Vision. Master’s Thesis, South China University of Technology, Guangzhou, China, 2010. [Google Scholar]

- Chao, Y. Research on Key Techniques for Semi-Conductor Chip Surface Defect Online Detection Based on Machine Vision. Ph.D. Thesis, Southeast University, Nanjing, China, 2017. [Google Scholar]

- Chen, K. Research on Key Technology for Integrated Circuit Chip Surface Defects Vision Detection. Ph.D. Thesis, Southeast University, Nanjing, China, 2016. [Google Scholar]

- Chen, J. Research and Development on the Stereo Vision Measurement System Based on IC Chip. Master’s Thesis, South China University of Technology, Guangzhou, China, 2012. [Google Scholar]

- Su, L.; Yu, X.; Li, K.; Pecht, M. Defect inspection of flip chip solder joints based on non-destructive methods: A review. Microelectron. Reliab. 2020, 110, 113657. [Google Scholar] [CrossRef]

- Czimmermann, T.; Ciuti, G.; Milazzo, M.; Chiurazzi, M.; Roccella, S.; Oddo, C.M.; Dario, P. Visual-based defect detection and classification approaches for industrial applications—A survey. Sensors 2020, 20, 1459. [Google Scholar] [CrossRef] [Green Version]

- Chen, X.; Zhao, C.; Chen, J.; Zhang, D.; Zhu, K.; Su, Y. K-means clustering with morphological filtering for silicon wafer grain defect detection. In Proceedings of the 2020 IEEE 4th Information Technology, Networking, Electronic and Automation Control Conference (ITNEC), Chongqing, China, 12–14 June 2020; pp. 1251–1255. [Google Scholar]

- Stefenon, S.F.; Ribeiro, M.H.D.M.; Nied, A.; Marianide, V.C.; Coelhobd, L.D.S.; da Rochaa, D.F.M.; Grebogifg, R.B.; Ruano, A.E.D. Wavelet group method of data handling for fault prediction in electrical power insulators. Int. J. Electr. Power Energy Syst. 2020, 123, 106269. [Google Scholar] [CrossRef]

- Frizzo Stefenon, S.; Zanetti Freire, R.; dos Santos Coelho, L.; Meyer, L.H.; Bartnik Grebogi, R.; Gouvêa Buratto, W.; Nied, A. Electrical insulator fault forecasting based on a wavelet neuro-fuzzy system. Energies 2020, 13, 484. [Google Scholar] [CrossRef] [Green Version]

- Arivazhagan, S.; Ganesan, L. Texture classification using wavelet transform. Pattern Recognit. Lett. 2003, 24, 1513–1521. [Google Scholar] [CrossRef]

- Huang, K.; Aviyente, S. Wavelet feature selection for image classification. IEEE Trans. Image Process. 2008, 17, 1709–1720. [Google Scholar] [CrossRef] [PubMed]

- Dua, S.; Acharya, U.R.; Chowriappa, P.; Sree, S.V. Wavelet-based energy features for glaucomatous image classification. IEEE Trans. Inf. Technol. Biomed. 2011, 16, 80–87. [Google Scholar] [CrossRef]

- Qian, Y.; Ye, M.; Zhou, J. Hyperspectral image classification based on structured sparse logistic regression and three-dimensional wavelet texture features. IEEE Trans. Geosci. Remote. Sens. 2012, 51, 2276–2291. [Google Scholar] [CrossRef] [Green Version]

- Chang, B.-M.; Tsai, H.-H.; Yen, C.-Y. SVM-PSO based rotation-invariant image texture classification in SVD and DWT domains. Eng. Appl. Artif. Intell. 2016, 52, 96–107. [Google Scholar] [CrossRef]

- Daubechies, I. Ten Lectures on Wavelets; Society for Industrial and Applied Mathematics: Philadelphia, PA, USA, 1992. [Google Scholar]

- Wang, X.; Xu, B.; Shi, P.; Li, S. Efficient learning control of uncertain fractional-order chaotic systems with disturbance. IEEE Trans. Neural Netw. Learn. Syst. 2020. [Google Scholar] [CrossRef]

- Tao, R.; Meng, X.; Wang, Y. Image encryption with multi-orders of fractional Fourier transforms. IEEE Trans. Inf. Forensics Secur. 2010, 5, 734–738. [Google Scholar] [CrossRef]

- Pei, S.-C.; Ding, J.-J. Closed-form discrete fractional and affine Fourier transforms. IEEE Trans. Signal Process. 2000, 48, 1338–1353. [Google Scholar]

- Bhatnagar, G.; Wu, Q.M.; Raman, B. Discrete fractional wavelet transform and its application to multiple encryption. Inf. Sci. 2013, 223, 297–316. [Google Scholar] [CrossRef]

- Sun, H.; Yang, X.Q.; Gao, H.J. A spatially constrained shifted asymmetric Laplace mixture model for the grayscale image segmentation. Neurocomputing 2019, 331, 50–57. [Google Scholar] [CrossRef]

- Hu, M.K. Visual pattern recognition by moment invariants. IRE Trans. Inf. Theory 1962, 8, 179–187. [Google Scholar]

- Dalal, N.; Triggs, B. Histograms of oriented gradients for human detection. In Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition, San Diego, CA, USA, 20–26 June 2005. [Google Scholar]

- Bhatnagar, G.; Raman, B.; Wu, Q.J. Robust watermarking using fractional wavelet packet transform. IET Image Process. 2012, 6, 386–397. [Google Scholar] [CrossRef]

- Bishop, C.M. Pattern Recognition and Machine Learning; Information Science and Statistics; Springer: Cambridge, UK, 2007; 738p. [Google Scholar]

- Mahabub, A.; Mahmud, M.I.; Hossain, M.F. A robust system for message filtering using an ensemble machine learning supervised approach. ICIC Express Lett. Part B Appl. 2019, 10, 805–811. [Google Scholar]

- Murata, M.; Orikane, K.; Akae, R. Automatic selection and analysis of verb and adjective synonyms from Japanese sentences using machine learning. Int. J. Innov. Comput. Inf. Control 2019, 15, 2135–2147. [Google Scholar]

- Ahmad, T.; Aziz, M.N. Data preprocessing and feature selection for machine learning intrusion detection systems. ICIC Express Lett. 2019, 13, 93–101. [Google Scholar]

- Lin, H.-D.; Chen, H.-L. Detection of surface flaws on textured LED lenses using wavelet packet transform based partial least squares techniques. Int. J. Innov. Comput. Inf. Control 2019, 15, 905–921. [Google Scholar]

- Wang, L.X.; Jiang, S.Y. Novel feature selection method based on feature clustering. Appl. Res. Comput. 2015, 32, 1305–1308. [Google Scholar]

- Song, Q.B.; Ni, J.J.; Wang, G.T. A fast clustering-based feature subset selection algorithm for high-dimensional data. IEEE Trans. Knowl. Data Eng. 2013, 25, 1–14. [Google Scholar] [CrossRef]

| Label | Light Sources of 0° | Light Sources of 45° | Light Sources of 60° |

|---|---|---|---|

| 1 | 6 | 8 | 9 |

| 2 | 6 | 8 | 11 |

| 3 | 6 | 10 | 9 |

| 4 | 6 | 10 | 11 |

| 5 | 9 | 8 | 9 |

| 6 | 9 | 8 | 11 |

| 7 | 9 | 10 | 9 |

| 8 | 9 | 10 | 11 |

| 9 | 12 | 8 | 9 |

| 10 | 12 | 8 | 11 |

| 11 | 12 | 10 | 9 |

| 12 | 12 | 10 | 11 |

| Category | Our Method | DWPD Based Method | Co-Occurrence Matrix Based Method |

|---|---|---|---|

| No defect | 91.25% | 90.00% | 88.75% |

| Pollutant on lead surface | 92.50% | 90.00% | 91.25% |

| Burr on lead edge | 83.75% | 82.50% | 85.00% |

| Category | Our Method | DWPD Based Method | Co-Occurrence Matrix Based Method |

|---|---|---|---|

| No defect | 93.75% | 92.50% | 91.25% |

| Scratch on body | 95.00% | 93.75% | 91.25% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, H.; Sun, H.; Shi, P. Chip Appearance Inspection Method for High-Precision SMT Equipment. Machines 2021, 9, 34. https://doi.org/10.3390/machines9020034

Zhang H, Sun H, Shi P. Chip Appearance Inspection Method for High-Precision SMT Equipment. Machines. 2021; 9(2):34. https://doi.org/10.3390/machines9020034

Chicago/Turabian StyleZhang, Huiyan, Hao Sun, and Peng Shi. 2021. "Chip Appearance Inspection Method for High-Precision SMT Equipment" Machines 9, no. 2: 34. https://doi.org/10.3390/machines9020034

APA StyleZhang, H., Sun, H., & Shi, P. (2021). Chip Appearance Inspection Method for High-Precision SMT Equipment. Machines, 9(2), 34. https://doi.org/10.3390/machines9020034