Electromagnetic Analysis of Vertical Resistive Memory with a Sub-nm Thick Electrode

Abstract

:1. Introduction

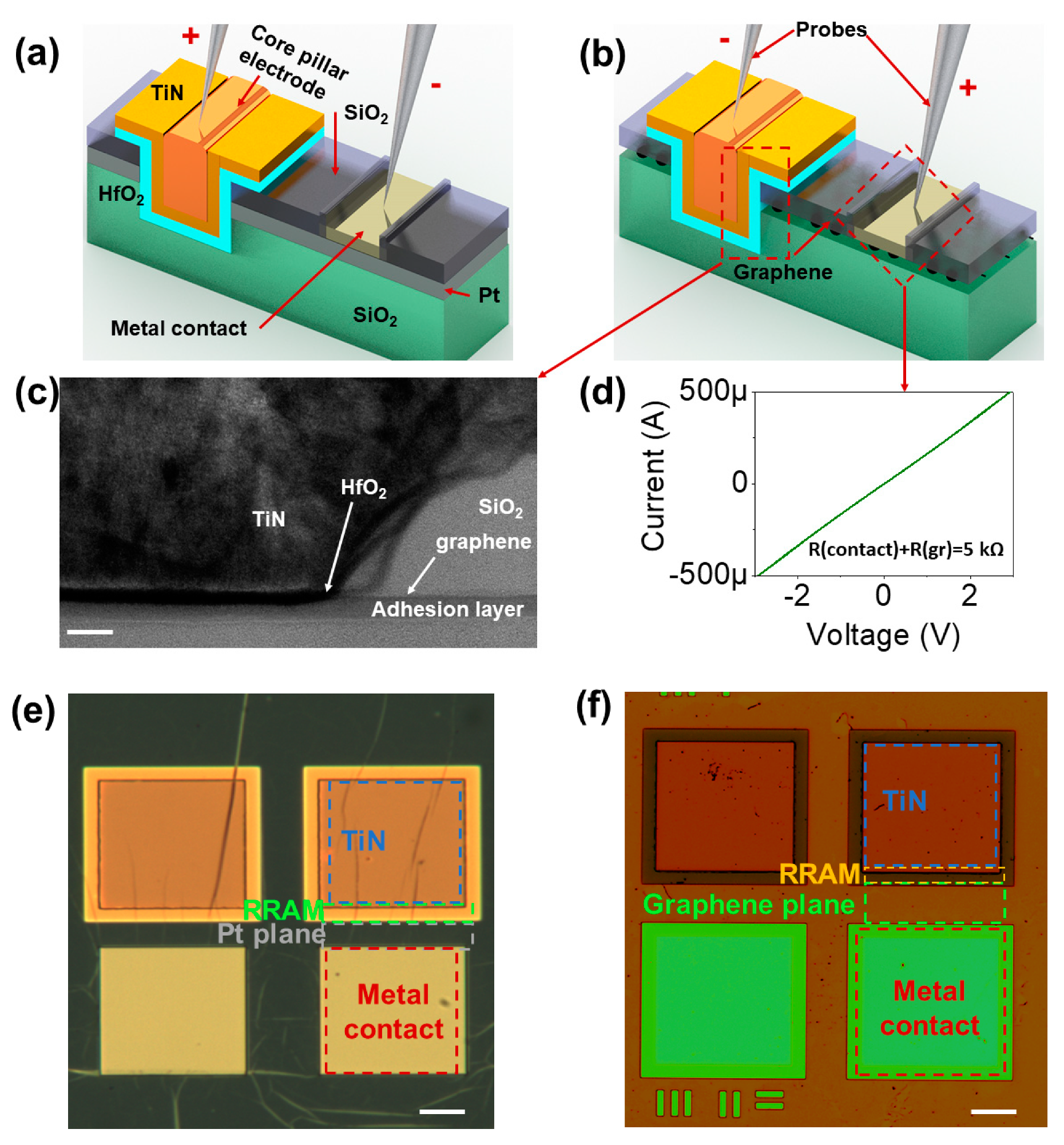

2. Materials and Methods

2.1. Fabrication

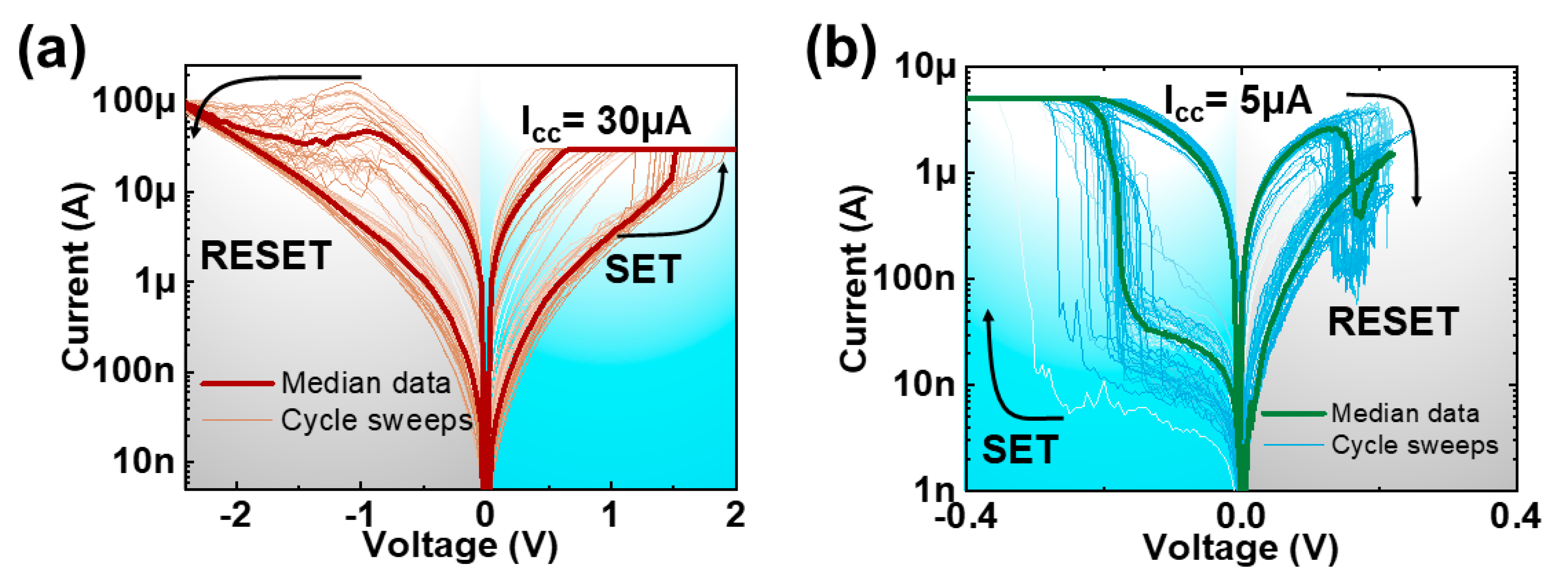

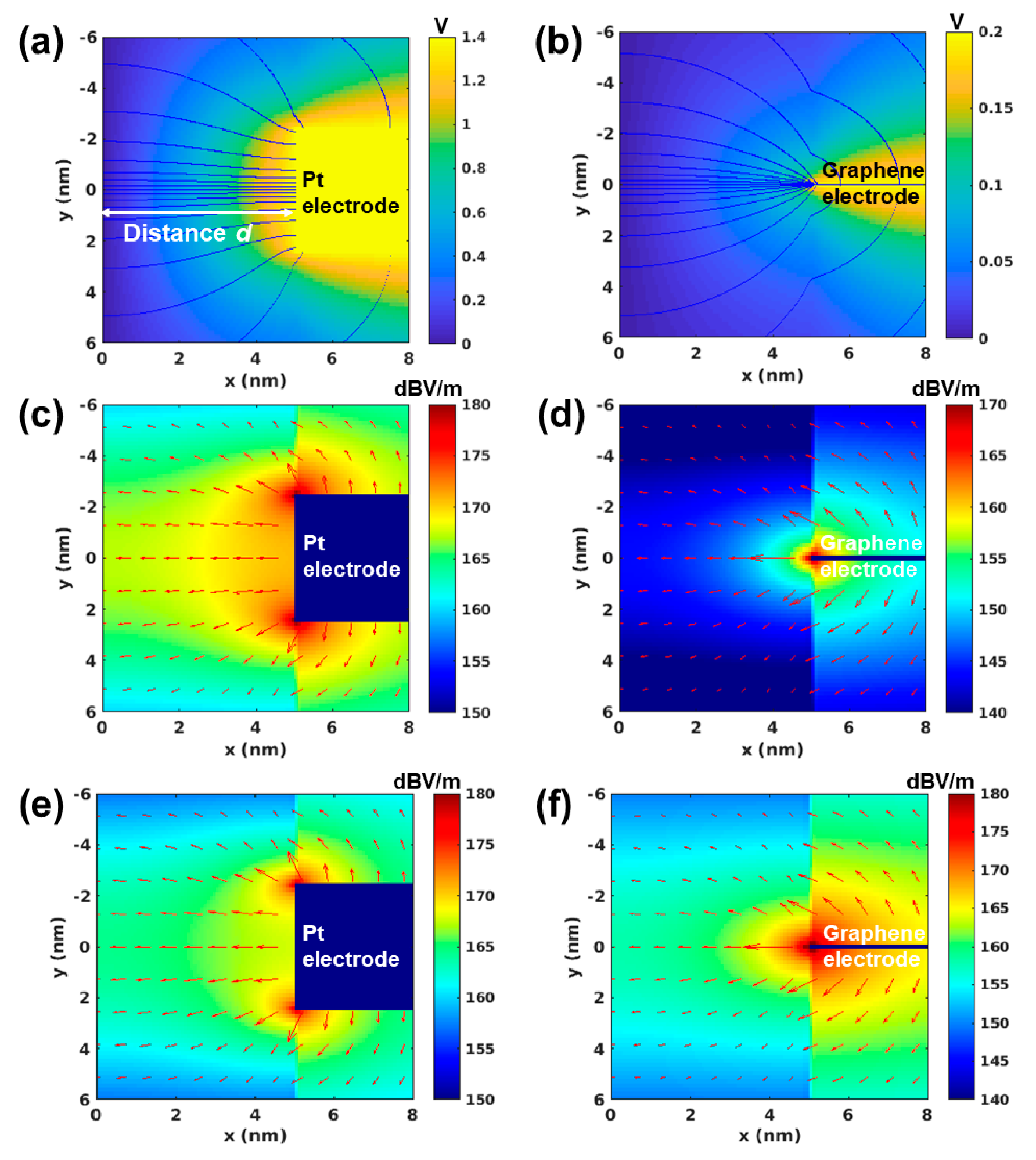

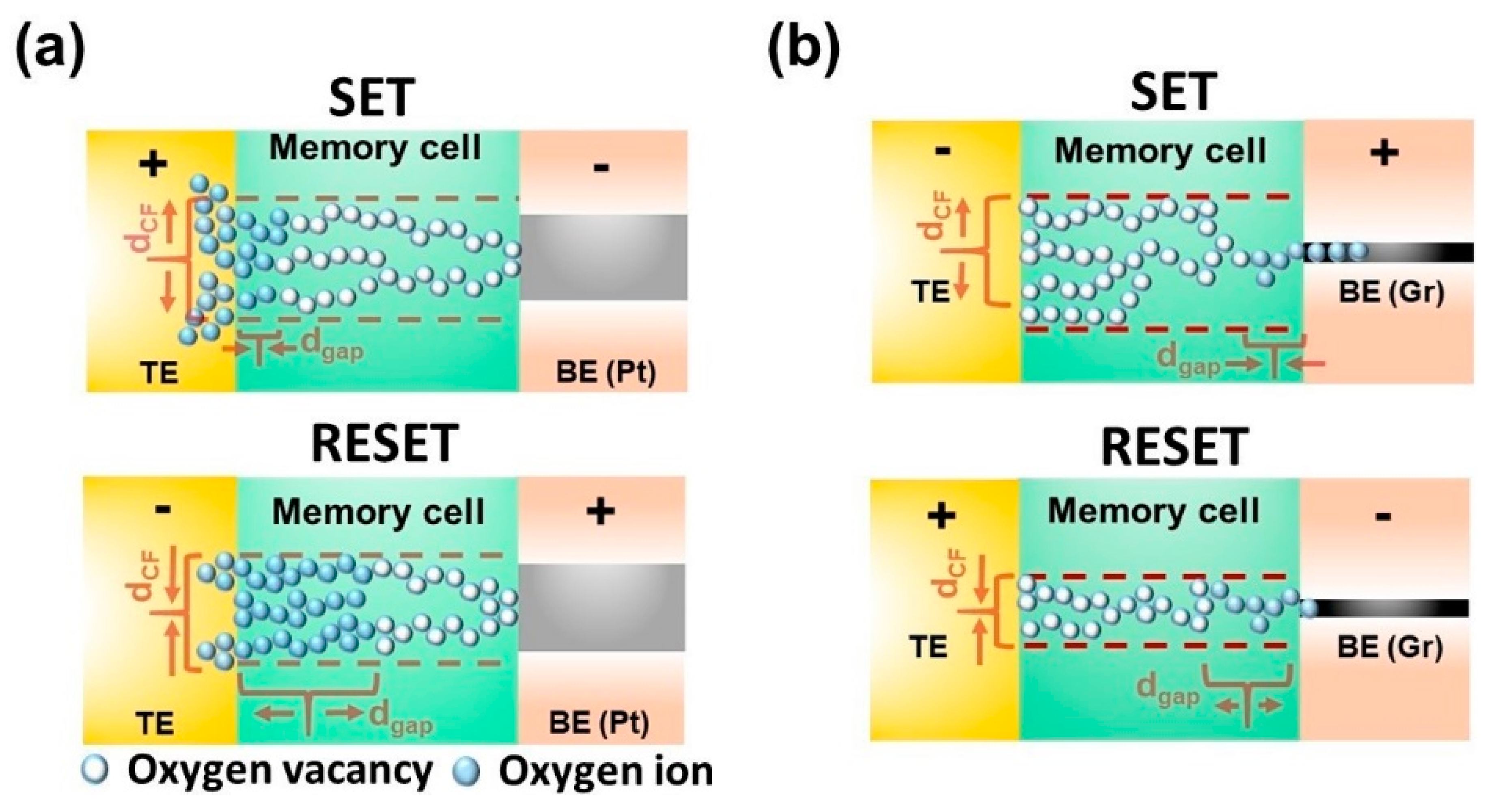

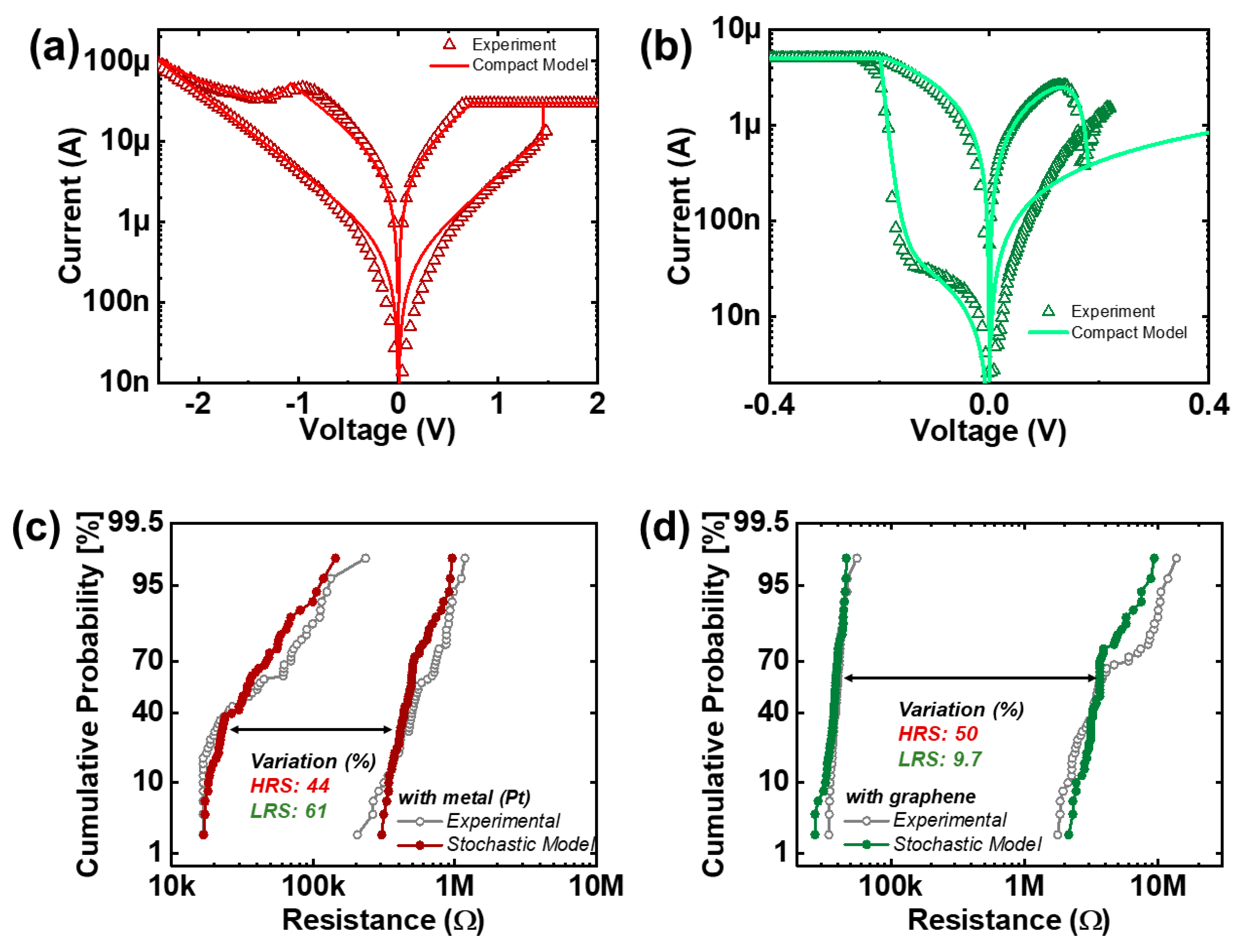

2.2. Device Characterization and Modeling

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Lecun, Y.; Bengio, Y.; Hinton, G. Deep learning. Nature 2015, 521, 436–444. [Google Scholar] [CrossRef] [PubMed]

- Krizhevsky, A.; Hinton, G.E. ImageNet Classification with Deep Convolutional Neural Networks. Commun. ACM 2017, 60, 84–90. [Google Scholar] [CrossRef]

- Grupp, L.M.; Davis, J.D.; Swanson, S. The Bleak Future of NAND Flash Memory. In Proceedings of the 10th USENIX Conference on File and Storage Technologies; USENIX Association, San Jose, CA, USA, 14–17 February 2012; p. 2. [Google Scholar]

- Pirovano, A.; Schuegraf, K. Memory grows up. Nat. Nanotechnol. 2010, 5, 177–178. [Google Scholar] [CrossRef]

- Upadhyay, N.K.; Jiang, H.; Wang, Z.; Asapu, S.; Xia, Q.; Yang, J.J. Emerging Memory Devices for Neuromorphic Computing. Adv. Mater. Technol. 2019, 1800589, 1–13. [Google Scholar] [CrossRef] [Green Version]

- Ielmini, D.; Ambrogio, S. Emerging neuromorphic devices. Nanotechnology 2019, 31, 92001. [Google Scholar] [CrossRef] [PubMed]

- Yu, S. Neuro-inspired computing with emerging nonvolatile memorys. Proc. IEEE 2018, 106, 260–285. [Google Scholar] [CrossRef]

- Wong, H.-S.P.; Lee, H.; Yu, S.; Chen, Y.; Wu, Y.; Chen, P.; Lee, B.; Chen, F.T.; Tsai, M. Metal–Oxide RRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

- Woo, J.; Yu, S. Resistive Memory-Based Analog Synapse: The Pursuit for Linear and Symmetric Weight Update. IEEE Nanotechnol. Mag. 2018, 12, 36–44. [Google Scholar] [CrossRef]

- Yu, S.; Chen, P. Emerging Memory Technologies: Recent Trends and Prospects. IEEE Solid-State Circuits Mag. 2016, 8, 43–56. [Google Scholar] [CrossRef]

- Wong, H.-S.P.; Salahuddin, S. Memory leads the way to better computing. Nat. Nanotechnol. 2015, 10, 191–194. [Google Scholar] [CrossRef] [Green Version]

- Chen, Y.Y.; Goux, L.; Pantisano, L.; Swerts, J.; Adelmann, C.; Mertens, S.; Afanasiev, V.V.; Wang, X.P.; Govoreanu, B.; Degraeve, R.; et al. Fully CMOS BEOL compatible HfO2 RRAM cell, with low (μA) program current, strong retention and high scalability, using an optimized plasma enhanced atomic layer deposition (PEALD) process for TiN electrode. In Proceedings of the 2011 IEEE International Interconnect Technology Conference, Dresden, Germany, 8–12 May 2011; pp. 1–3. [Google Scholar]

- Prezioso, M.; Merrikh-Bayat, F.; Hoskins, B.D.; Adam, G.C.; Likharev, K.K.; Strukov, D.B. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 2015, 521, 61–64. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Woo, J.; Peng, X.; Yu, S. Design Considerations of Selector Device in Cross-Point RRAM Array for Neuromorphic Computing. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–4. [Google Scholar]

- Woo, J. Impact of Selector Devices in Analog RRAM-Based Crossbar Arrays for Inference and Training of Neuromorphic System. IEEE Trans. Very Large Scale Integr. Syst. 2019, 27, 1–8. [Google Scholar] [CrossRef]

- Ielmini, D. Resistive Switching Memories Based on Metal Oxides: Mechanisms, Reliability and Scaling. Semicond. Sci. Technol. 2016, 31, 63002. [Google Scholar] [CrossRef]

- Yu, S.; Chen, H.-Y.; Gao, B.; Kang, J.; Wong, H.-S.P. HfOx-Based Vertical Resistive Switching Random Access Memory Suitable for Bit-Cost-Effective Three-Dimensional Cross-Point Architecture. ACS Nano 2013, 7, 2320–2325. [Google Scholar] [CrossRef] [PubMed]

- Chen, P.; Li, Z.; Yu, S. Design Tradeoffs of Vertical RRAM-Based 3-D Cross-Point Array. IEEE Trans. Very Large Scale Integr. Syst. 2016, 24, 3460–3467. [Google Scholar] [CrossRef]

- Jiang, Z.; Qin, S.; Li, H.; Fujii, S.; Lee, D.; Wong, S.; Wong, H.-S.P. Next-Generation Ultrahigh-Density 3-D Vertical Resistive Switching Memory (VRSM)—Part II: Design Guidelines for Device, Array, and Architecture. IEEE Trans. Electron Devices 2019, 66, 5147–5154. [Google Scholar] [CrossRef]

- Lee, S.; Sohn, J.; Jiang, Z.; Chen, H.-Y.; Philip Wong, H.-S. Metal oxide-resistive memory using graphene-edge electrodes. Nat. Commun. 2015, 6, 8407. [Google Scholar] [CrossRef] [Green Version]

- Sohn, J.; Lee, S.; Jiang, Z.; Chen, H.Y.; Wong, H.S.P. Atomically thin graphene plane electrode for 3D RRAM. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 5.3.1–5.3.4. [Google Scholar]

- Seo, S.; Lim, J.; Lee, S.; Alimkhanuly, B.; Kadyrov, A.; Jeon, D.; Lee, S. Graphene-Edge Electrode on a Cu-Based Chalcogenide Selector for 3D Vertical Memristor Cells. ACS Appl. Mater. Interfaces 2019, 11, 43466–43472. [Google Scholar] [CrossRef]

- Lee, S.; Lee, K.; Liu, C.-H.; Zhong, Z. Homogeneous bilayer graphene film based flexible transparent conductor. Nanoscale 2012, 4, 639–644. [Google Scholar] [CrossRef] [Green Version]

- Dai, L.; Niu, G.; Zhao, J.; Zhao, H.; Liu, Y.; Wang, Y.; Zhang, Y.; Wu, H.; Wang, L.; Pfützenreuter, D.; et al. Toward van der Waals epitaxy of transferable ferroelectric barium titanate films via a graphene monolayer. J. Mater. Chem. C 2020, 8, 3445–3451. [Google Scholar] [CrossRef]

- Novoselov, K.S.; Fal′ko, V.I.; Colombo, L.; Gellert, P.R.; Schwab, M.G.; Kim, K. A roadmap for graphene. Nature 2012, 490, 192–200. [Google Scholar] [CrossRef]

- Degraeve, R.; Fantini, A.; Raghavan, N.; Goux, L.; Clima, S.; Govoreanu, B.; Belmonte, A.; Linten, D.; Jurczak, M. Causes and consequences of the stochastic aspect of filamentary RRAM. Microelectron. Eng. 2015, 147, 171–175. [Google Scholar] [CrossRef]

- Jackson, J.D. Classical Electrodynamics, 3rd ed.; John Wiley and Sons (WIE): New York, NY, USA, 1998; pp. 79–84. [Google Scholar]

- Harrington, R.F. Field Computation by Moment Methods; Wiley-IEEE Press: Piscataway, NJ, USA, 1992; pp. 22–40. [Google Scholar]

- Chew, W.C. Waves and Fields in Inhomogeneous Media; Van Nostrand Reinhold: New York, NY, USA, 1990; pp. 271–323. [Google Scholar]

- Boyd, S.; Vandenberghe, L. Convex Optimization; Cambridge University Press: New York, NY, USA, 2004; pp. 127–189. [Google Scholar]

- Napolean, A.; Sivamangai, N.M.; Samuel, J.; John, V. Overview of Current Compliance Effect on Reliability of Nano Scaled Metal Oxide Resistive Random Access Memory Device. In Proceedings of the 2018 4th International Conference on Devices, Circuits and Systems (ICDCS), Coimbatore, Tamilnadu, India, 17–18 March 2018; pp. 290–296. [Google Scholar]

- Li, H.; Huang, P.; Gao, B.; Liu, X.; Kang, J.; Wong, H.S.P. Device and Circuit Interaction Analysis of Stochastic Behaviors in Cross-Point RRAM Arrays. IEEE Trans. Electron Devices 2017, 64, 4928–4936. [Google Scholar] [CrossRef]

- Woo, J.; Padovani, A.; Moon, K.; Kwak, M.; Larcher, L.; Hwang, H. Linking Conductive Filament Properties and Evolution to Synaptic Behavior of RRAM Devices for Neuromorphic Applications. IEEE Electron Device Lett. 2017, 38, 1220–1223. [Google Scholar] [CrossRef]

- Sun, T.; Yao, X.; Fabris, S. Effects of Thermal Electronic Excitations on the Diffusion of Oxygen Adatoms on Graphene. J. Phys. Chem. A 2016, 120, 2607–2613. [Google Scholar] [CrossRef] [PubMed]

- Tsetseris, L.; Logothetidis, S.; Pantelides, S.T. Migration of species in a prototype diffusion barrier: Cu, O, and H in TiN. Appl. Phys. Lett. 2009, 94, 161903. [Google Scholar] [CrossRef]

- Yu, S.; Gao, B.; Fang, Z.; Yu, H.; Kang, J.; Wong, H.P. A Neuromorphic Visual System Using RRAM Synaptic Devices with Sub-pJ Energy and Tolerance to Variability: Experimental Characterization and Large-Scale Modeling. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 10.4.1–10.4.4. [Google Scholar]

- Jiang, Z.; Yu, S.; Wu, Y.; Engel, J.H.; Guan, X.; Wong, H.P. Verilog-A compact model for oxide-based resistive random access memory (RRAM). In Proceedings of the 2014 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Yokohama, Japan, 9–11 September 2014; pp. 41–44. [Google Scholar]

- Guan, X.; Yu, S.; Wong, H.-S.P. A SPICE Compact Model of Metal Oxide Resistive Switching Memory With Variations. IEEE Electron Device Lett. 2012, 33, 1405–1407. [Google Scholar] [CrossRef]

- Jiang, Z.; Wong, H.-S.P. Stanford University Resistive-Switching Random Access Memory (RRAM) Verilog-A Model. Available online: https://nanohub.org/publications/19/1 (accessed on 23 November 2019).

- Yu, S.; Wong, H.P. A Phenomenological Model of Oxygen Ion Transport for Metal Oxide Resistive Switching Memory. In Proceedings of the 2010 IEEE International Memory Workshop, Seoul, Korea, 16–19 May 2010; pp. 1–4. [Google Scholar] [CrossRef]

- Jiang, Z.; Wu, Y.; Yu, S.; Yang, L.; Song, K.; Karim, Z.; Wong, H.S.P. A Compact Model for Metal–Oxide Resistive Random Access Memory with Experiment Verification. IEEE Trans. Electron Devices 2016, 63, 1884–1892. [Google Scholar] [CrossRef]

- McPherson, J.; Kim, J.-Y.; Shanware, A.; Mogul, H. Thermochemical description of dielectric breakdown in high dielectric constant materials. Appl. Phys. Lett. 2003, 82, 2121–2123. [Google Scholar] [CrossRef]

- Padovani, A.; Larcher, L.; Pirrotta, O.; Vandelli, L.; Bersuker, G. Microscopic Modeling of HfOx RRAM Operations: From Forming to Switching. IEEE Trans. Electron Devices 2015, 62, 1998–2006. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Alimkhanuly, B.; Kim, S.; Kim, L.-w.; Lee, S. Electromagnetic Analysis of Vertical Resistive Memory with a Sub-nm Thick Electrode. Nanomaterials 2020, 10, 1634. https://doi.org/10.3390/nano10091634

Alimkhanuly B, Kim S, Kim L-w, Lee S. Electromagnetic Analysis of Vertical Resistive Memory with a Sub-nm Thick Electrode. Nanomaterials. 2020; 10(9):1634. https://doi.org/10.3390/nano10091634

Chicago/Turabian StyleAlimkhanuly, Batyrbek, Sanghoek Kim, Lok-won Kim, and Seunghyun Lee. 2020. "Electromagnetic Analysis of Vertical Resistive Memory with a Sub-nm Thick Electrode" Nanomaterials 10, no. 9: 1634. https://doi.org/10.3390/nano10091634