Optimization of Structure and Electrical Characteristics for Four-Layer Vertically-Stacked Horizontal Gate-All-Around Si Nanosheets Devices

Abstract

1. Introduction

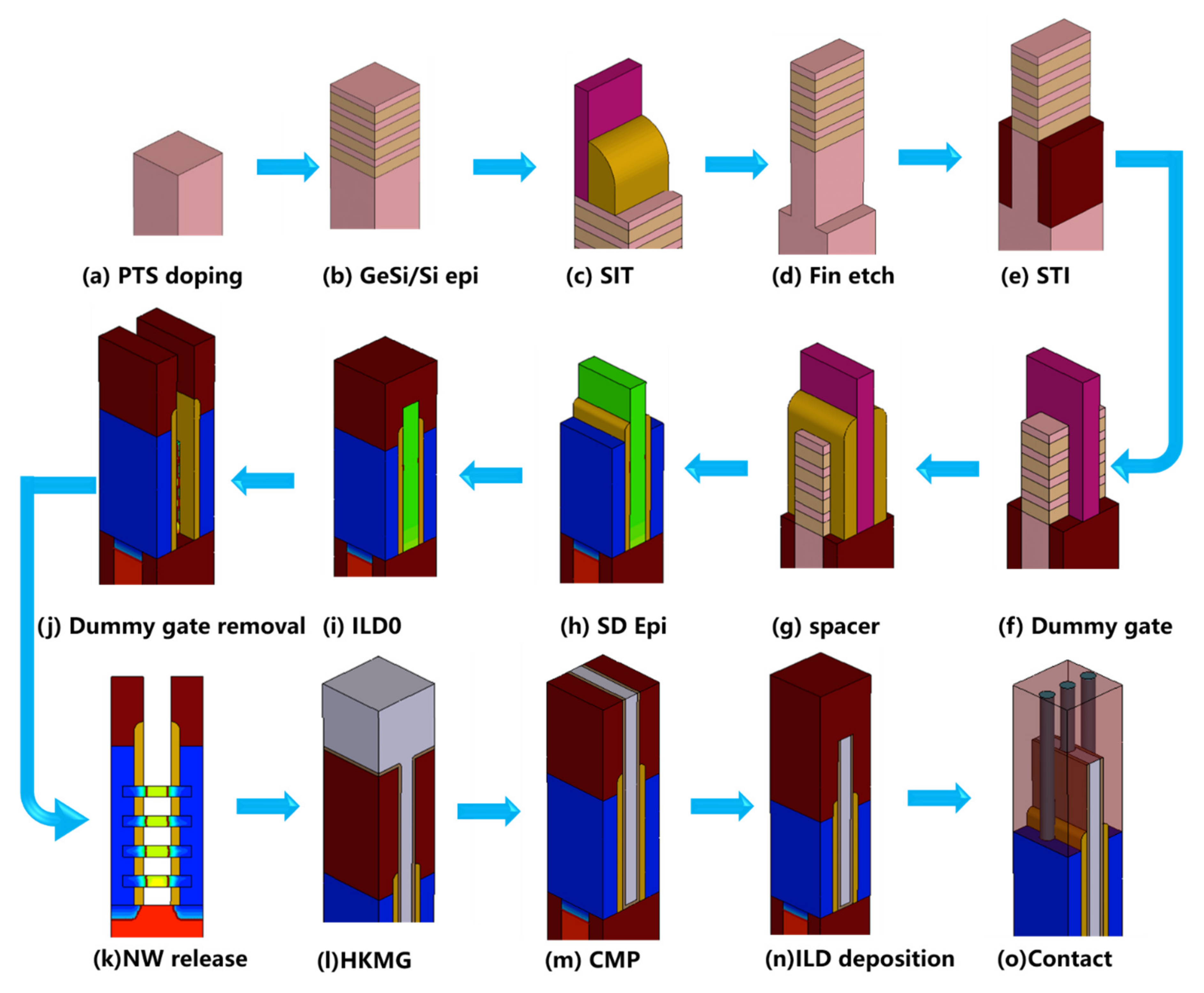

2. Materials and Methods

3. Results and Discussion

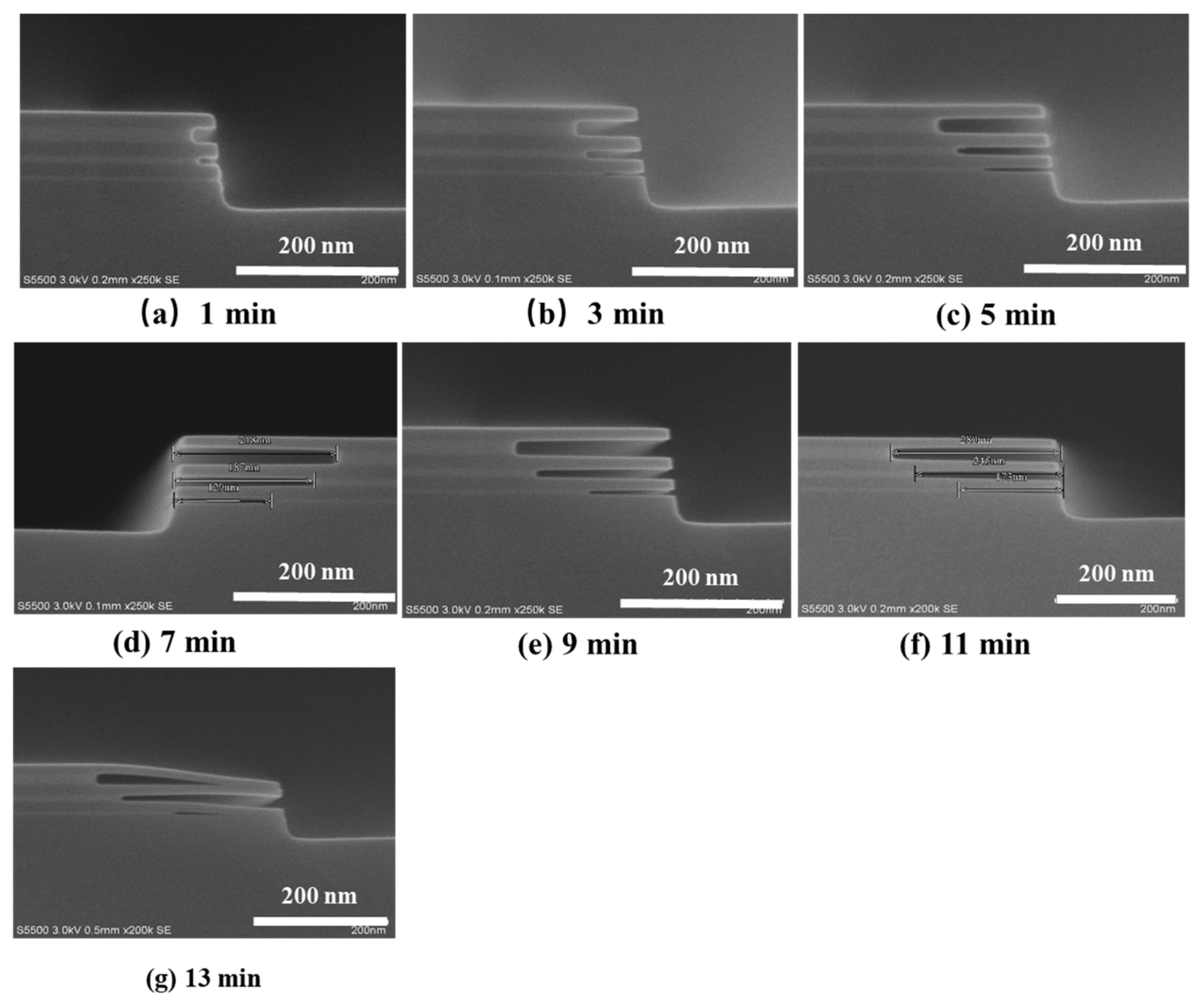

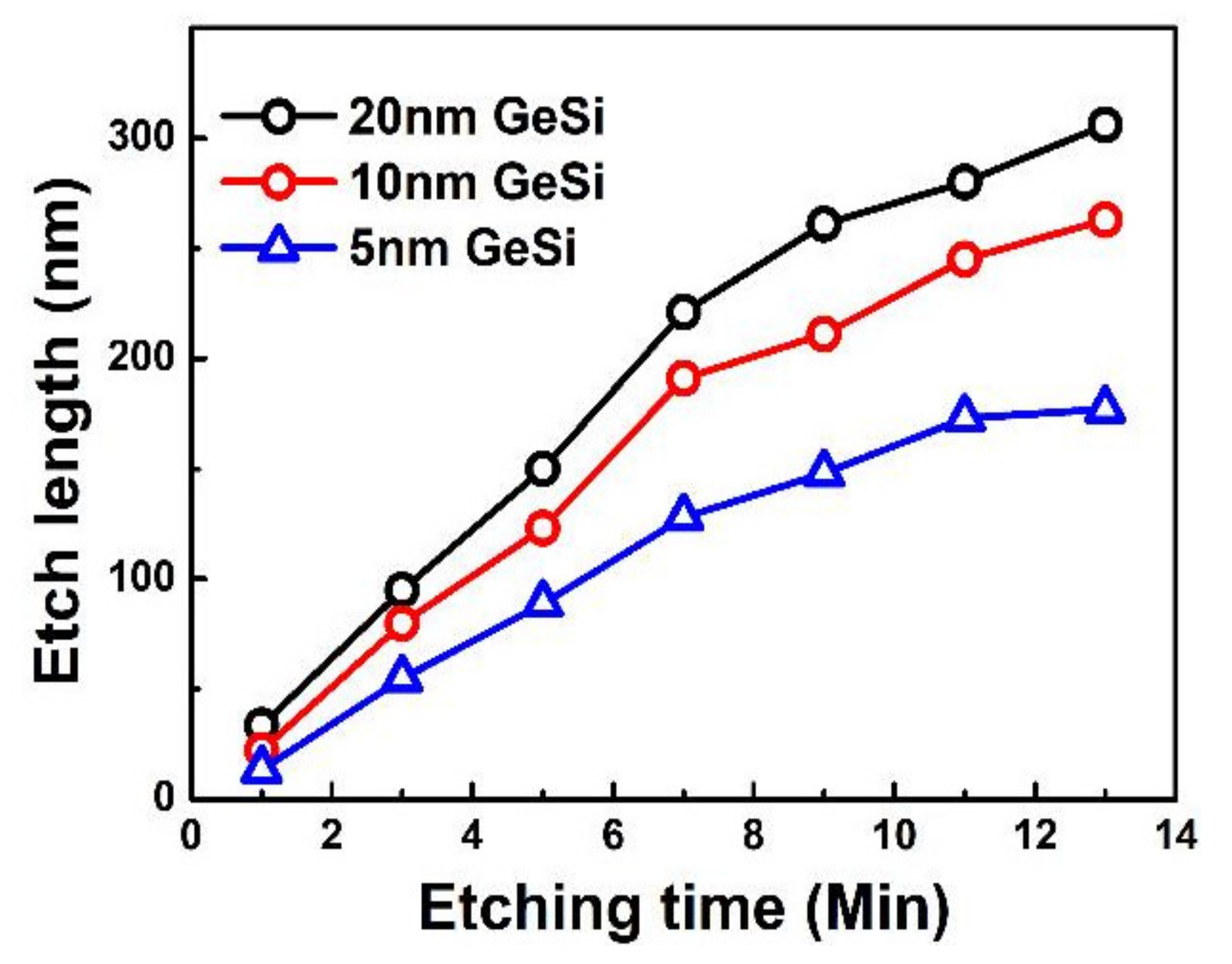

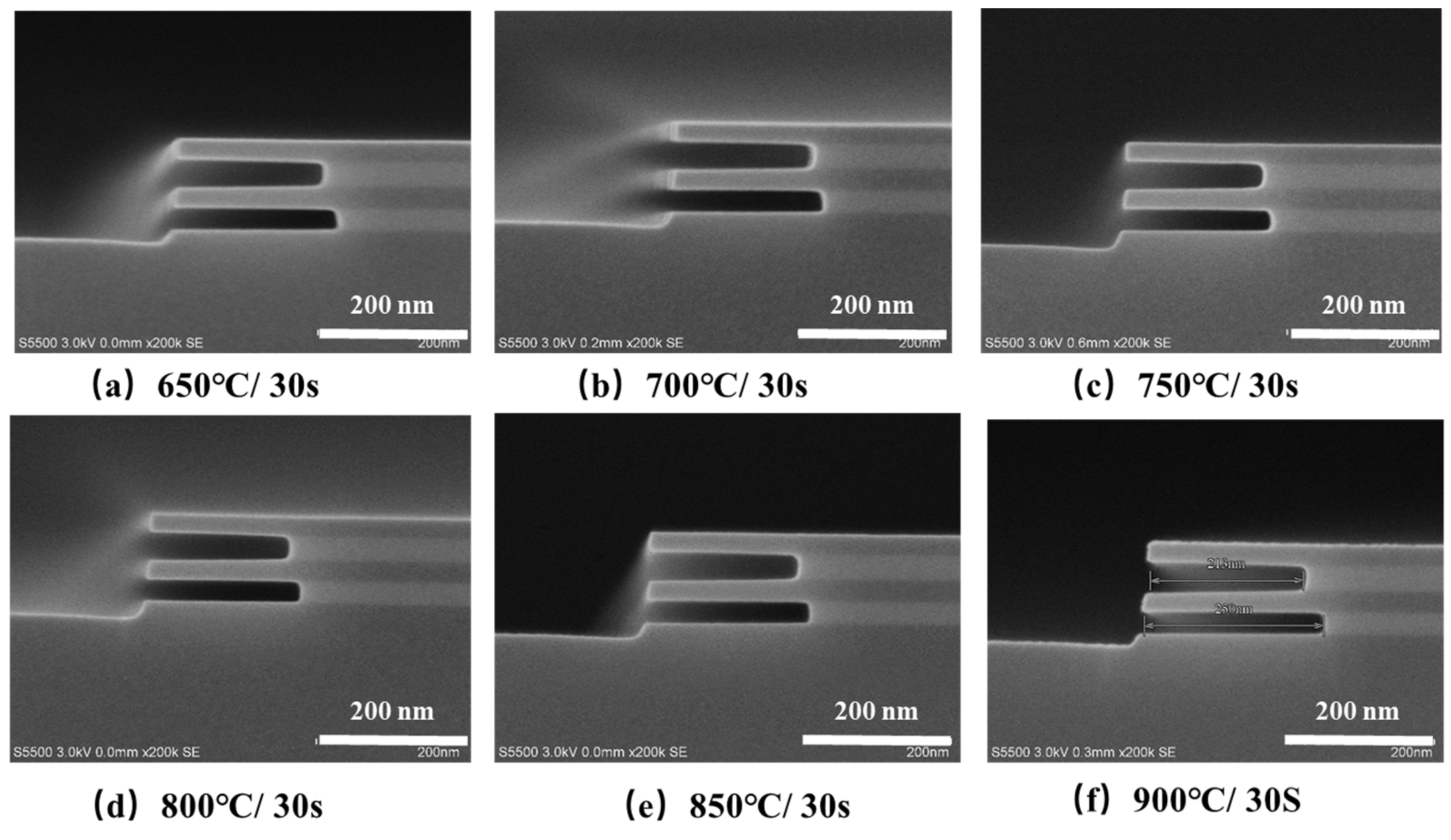

3.1. Optimization of NS Release Processes of Stacked GAA Si NS Devices

3.1.1. Effect of GeSi Thicknesses on NS Release in Stacked GeSi/Si Samples

3.1.2. Effect of Thermal Anneal on NS Release in Stacked GeSi/Si Samples

3.2. Device Fabrication and Structure Characterization

3.2.1. Process Monitoring of the Stacked Si NS Devices at Different Fabrication Stages

3.2.2. Structure Characterization of the Stacked GAA Si NS Devices

3.2.3. Si NS Channels Release Control with Different Etching Processes

3.3. Influence of GP Doping on Performance of Devices

3.3.1. Experimental Results of GP Doping on Performance of Devices

3.3.2. Simulation Results of GP Doping on Performance of p-Type Devices

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Natarajan, S.; Agostinelli, M.; Akbar, S.; Bost, M.; Bowonder, A.; Chikarmane, V.; Chouksey, S.; Dasgupta, A.; Fischer, K.; Fu, Q.; et al. A 14 nm logic technology featuring 2 nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm 2 SRAM cell size. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 71–73. [Google Scholar]

- Cho, H.-J.; Oh, H.S.; Nam, K.J.; Kim, Y.H.; Yeo, K.H.; Kim, W.D.; Chung, Y.S.; Nam, Y.S.; Kim, S.M.; Kwon, W.H.; et al. Si FinFET based 10 nm technology with multi Vt gate stack for low power and high performance applications. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Cheng, K.; Seo, S.; Faltermeier, J.; Lu, D.; Standaert, T.; Ok, I.; Khakifirooz, A.; Vega, R.; Levin, T.; Li, J.; et al. Bottom oxidation through STI (BOTS)—A novel approach toabricate dielectric isolated FinFETs on bulk substrates. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Zhang, Q.; Yin, H.; Luo, J.; Yang, H.; Meng, L.; Li, Y.; Wu, Z.; Zhang, Y.; Zhang, Y.; Qin, C.; et al. FOI FinFET with ultra-low parasitic resistance enabled by fully metallic source and drain formation on isolated bulk-fin. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 452–455. [Google Scholar]

- Radamson, H.H.; He, X.; Zhang, Q.; Liu, J.; Cui, H.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; Gao, J.; et al. Miniaturization of CMOS. Micromachines 2019, 10, 293. [Google Scholar] [CrossRef] [PubMed]

- Shirazi, S.G.; Karimi, G.R.; Mirzakuchaki, S. GAA CNT TFETs Structural Engineering: A Higher ON Current, Lower Ambipolarity. IEEE Trans. Electron Devices 2019, 66, 2822–2830. [Google Scholar] [CrossRef]

- Yin, X.; Xie, L.; Ai, X.Z.; Zhang, Y.B.; Jia, K.P.; Wu, Z.H.; Ma, X.L.; Zhang, Q.Z.; Mao, S.J.; Xiang, J.J.; et al. Vertical sandwich gate-all-around field-effect transistors with self-aligned high-k metal gates and small effective-gate-length variation. IEEE Electron Device Lett. 2019, 41, 8–11. [Google Scholar] [CrossRef]

- Song, Y.; Zhou, H.; Xu, Q.; Niu, J.; Yan, J.; Zhao, C.; Zhong, H. High-Performance Silicon Nanowire Gate-All-Around nMOSFETs Fabricated on BulkSubstrate Using CMOS-Compatible Process. IEEE Electron Device Lett. 2010, 31, 1377–1379. [Google Scholar] [CrossRef]

- Li, M.; Fan, J.; Xu, X.; Huang, R. Investigation on electrostatic discharge robustness of gate-all-around silicon nanowire transistors combined with thermal analysis. IEEE Electron Device Lett. 2017, 38, 1653–1656. [Google Scholar] [CrossRef]

- Huang, N.; Liu, W.; Li, Q.; Bai, W.; Yang, T. Investigation and optimization of electrical and thermal performance for 5-nm gaa vertically stacked nanowire fets. Microelectron. J. 2019, 95, 104679. [Google Scholar] [CrossRef]

- Bae, G.; Bae, D.-I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; et al. 3nm GAA Technology featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 28.7.1–28.7.4. [Google Scholar]

- Chu, C.; Wu, K.; Luo, G.L.; Chen, B.Y.; Chen, S.H.; Wu, W.F.; Yeh, W.K. Stacked ge-nanosheet gaa fets fabricated by ge/si multilayer epitaxy. IEEE Electron Device Lett. 2018, 39, 1133–1136. [Google Scholar] [CrossRef]

- Zhang, J.; Frougier, J.; Greene, A.; Miao, X.; Vega, R.; Montanini, P.; Durfee, C.; Gaul, A.; Pancharatnam, S.; Adams, C.; et al. Full Bottom Dielectric Isolation to Enable Stacked Nanosheet Transistor for Low Power and High Performance Applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 11.6.1–11.6.4. [Google Scholar]

- Barraud, S.; Previtali, B.; Vizioz, C.; Hartmann, J.M.; Sturm, J.; Lassarre, J.; Perrot, C.; Rodriguez, P.; Loup, V.; Magalhaes-Lucas, A.; et al. 7-Levels-Stacked Nanosheet GAA Transistors for High Performance Computing. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar]

- Zhang, Z.; Xu, G.; Zhang, Q.; Hou, Z.; Li, J.; Kong, Z.; Zhang, Y.K.; Xiang, J.J.; Xu, Q.X.; Wu, Z.H.; et al. Finfet with improved subthreshold swing and drain current using 3 nm ferroelectric hf0.5zr0.5o2. IEEE Electron Device Lett. 2019, 40, 367–370. [Google Scholar] [CrossRef]

- Xu, M.; Zhu, H.; Zhang, Y.; Xu, Q.; Zhang, Y.; Qin, C.; Zhang, Q.Z.; Yin, H.X.; Xu, G.B.; Chen, S.; et al. Two methods of tuning threshold voltage of bulk finfets with replacement high-k metal-gate stacks. Solid-State Electron. 2017, 129, 52–60. [Google Scholar] [CrossRef]

- Mertens, H.; Ritzenthaler, R.; Chasin, A.; Schram, T.; Kunnen, E.; Hikavyy, A.; Ragnarsson, L.-Å.; Dekkers, H.; Hopf, T.; Wostyn, K.; et al. Vertically stacked gate-all-around Si nanowire CMOS transistors with dual work function metal gates. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 524–527. [Google Scholar]

- Zhang, Q.; Tu, H.; Gu, S.; Zhang, Z.; Wang, G.; Wei, F.; Ma, T.D.; Zhao, H.B.; Wei, Q.H.; Yin, H.X.; et al. Influence of rapid thermal annealing on ge-si interdiffusion in epitaxial multilayer ge 0.3 si 0.7 /si superlattices with various gesi thicknesses. ECS J. Solid State Sci. Technol. 2018, 7, 671–676. [Google Scholar] [CrossRef]

- Li, C.; Zhu, H.; Zhang, Y.; Yin, X.; Jia, K.; Li, J.; Wang, G.L.; Kong, Z.Z.; Du, A.Y.; Yang, T.Z.; et al. Selective Digital Etching of Silicon−Germanium Using Nitric and Hydrofluoric Acids. ACS Appl. Mater. Interfaces 2020, 12, 48170–48178. [Google Scholar] [CrossRef] [PubMed]

- Li, J.; Li, Y.; Zhou, N.; Xiong, W.; Wang, G.; Zhang, Q.; Du, A.; Gao, J.; Kong, Z.; Lin, H.; et al. Study of Silicon Nitride Inner Spacer Formation in Process of Gate-all-around Nano-Transistors. Nanomaterials 2020, 10, 793. [Google Scholar] [CrossRef] [PubMed]

- Su, Y.; Lai, J.; Sun, L. Investigation of self-heating effects in vacuum gate dielectric gate-all-around vertically stacked silicon nanowire field effect transistors. IEEE Trans. Electron Devices 2020, 67, 4085–4091. [Google Scholar] [CrossRef]

- Xie, L.; Zhu, H.; Zhang, Y.; Ai, X.; Wang, G.; Li, J.; Du, A.; Kong, Z.; Yin, X.; Li, C.; et al. Strained Si0.2Ge0.8/Ge multilayer Stacks Epitaxially Grown on a Low-/High-Temperature Ge Buffer Layer and Selective Wet-Etching of Germanium. Nanomaterials 2020, 10, 1715. [Google Scholar] [CrossRef] [PubMed]

- Liu, H.; Li, Y.; Cheng, X.; Zan, Y.; Lin, H.X.; Kong, Z.Z.; Zhong, Z.Y.; Li, Y.; Wang, H.Y.; Xu, G.B.; et al. Fabrication and selective wet etching of si0.2ge0.8/ge multilayer for si0.2ge0.8 channel gate-all-around mosfets. Mater. Sci. Semicond. Process. 2020, 121, 105397. [Google Scholar] [CrossRef]

- Hu, R.; Xu, S.; Wang, J.; Shi, Y.; Yu, L. Unprecedented uniform 3d growth integration of 10-layer stacked si nanowires on tightly confined sidewall grooves. Nano Lett. 2020, 20, 10. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Q.; Tu, H.; Zhang, Z.; Li, J.; Wei, F.; Wang, G.L.; Han, J.H.; Zhao, H.B.; Zhang, Y.K.; Li, Y.L.; et al. Optimization of zero-level interlayer dielectric materials for gate-all-around silicon nanowire channel fabrication in a replacement metal gate process. Mater. Sci. Semicond. Process. 2021, 121, 105434. [Google Scholar] [CrossRef]

- Sung, P.J.; Chang, S.W.; Kao, K.H.; Wu, C.T.; Chao, T.S. Fabrication of vertically stacked nanosheet junctionless field-effect transistors and applications for the cmos and cfet inverters. IEEE Trans. Electron Devices 2020, 67, 9. [Google Scholar] [CrossRef]

- Kim, S.; Kim, M.; Ryu, D.; Lee, K.; Park, B.G. Investigation of electrical characteristic behavior induced by channel-release process in stacked nanosheet gate-all-around mosfets. IEEE Trans. Electron Devices 2020, 67, 6. [Google Scholar] [CrossRef]

- International Roadmap for Devices and systems 2017 Edition More Moore. Available online: https://irds.ieee.org/images/files/pdf/2017/2017IRDS_MM.pdf (accessed on 30 December 2018).

- Yao, J.X.; Li, J.; Luo, K.; Yu, J.H.; Zhang, Q.Z.; Hou, Z.H.; Gu, J.; Yang, W.; Wu, Z.H.; Yin, H.X.; et al. Physical insights on quantum confinement and carrier mobility in si, sige, ge gate-all-around nsfet for 5nm technology node. IEEE J. Electron Devices Soc. 2018, 6, 841–848. [Google Scholar] [CrossRef]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, H.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T230–T231. [Google Scholar]

| Parameters of GAA Si NS Devices | Values |

|---|---|

| Type | p-type |

| Stacks of NS channels | 4 |

| Lg (nm) | 12 |

| NS thickness (nm) | 5 |

| Wideness of NSs (nm) | 20 |

| EOT (nm) | 1 |

| Spacing between NSs (nm) | 8 nm |

| Nch (cm−3) | 1 × 1015 |

| NSD (cm−3) | 3 × 1020 |

| Thickness of spacers (nm) | 4 nm |

| Ref. | (30 IBM) 2017 VLSI | (11 Samsung) 2018 IEDM | (12 NNDL) 2018 EDL | (13 IBM) 2019 IEDM | (14 CEA Leti) 2020 VLSI | (IMECAS) This Work |

|---|---|---|---|---|---|---|

| Channel | Stacked Si NS | Stacked Si NS | Stacked Ge NS | Stacked Si NS | Stacked Si NS | Stacked Si NS |

| N/P type | N/P | N/P | N/P | N/P | N | N/P |

| Fin/Sub. | GeSi/Si stack on Si | - | Ge/Si stack on SOI | SiGe/Si stack on Si | SiGe/Si stack on SOI | SiGe/Si stack on Si |

| Num. of Stacked NSs | 3 | - | 3 | 3 | 7 | 4 |

| STI Annael | ≤900 °C | - | - | ≤900 °C | - | ≤850 °C |

| Release | In RMG | In RMG | In RMG | In RMG | In RMG | In RMG |

| NS forming | SiGe etch | - | Si etch | SiGe etch | SiGe etch | SiGe etch |

| NS Width/Thickness | ~25/6 nm | - | ~90/40 nm | - | ~30/10 nm | 30/6 nm |

| Lg | 12 nm | - | 90 nm | 12 nm | 45 nm | 25.8 nm |

| SS (mV/dec) | 75(N)/85 (P) | 65(N)/67 (P) | 140(N)/130(P) | 73(N)/74 (P) | 64(N) | 71.2(N)/78.7 (P) |

| DIBL (mV/V) | 32(N)/24 (P) | 20(N)/24 (P) | - | 32(N)/35 (P) | 10(N) | 9 (N)/22 (P) |

| ION/IOFF | ~104 | ~105 | ~104 | ~106 | ~105 | 3.15 × 105 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Q.; Gu, J.; Xu, R.; Cao, L.; Li, J.; Wu, Z.; Wang, G.; Yao, J.; Zhang, Z.; Xiang, J.; et al. Optimization of Structure and Electrical Characteristics for Four-Layer Vertically-Stacked Horizontal Gate-All-Around Si Nanosheets Devices. Nanomaterials 2021, 11, 646. https://doi.org/10.3390/nano11030646

Zhang Q, Gu J, Xu R, Cao L, Li J, Wu Z, Wang G, Yao J, Zhang Z, Xiang J, et al. Optimization of Structure and Electrical Characteristics for Four-Layer Vertically-Stacked Horizontal Gate-All-Around Si Nanosheets Devices. Nanomaterials. 2021; 11(3):646. https://doi.org/10.3390/nano11030646

Chicago/Turabian StyleZhang, Qingzhu, Jie Gu, Renren Xu, Lei Cao, Junjie Li, Zhenhua Wu, Guilei Wang, Jiaxin Yao, Zhaohao Zhang, Jinjuan Xiang, and et al. 2021. "Optimization of Structure and Electrical Characteristics for Four-Layer Vertically-Stacked Horizontal Gate-All-Around Si Nanosheets Devices" Nanomaterials 11, no. 3: 646. https://doi.org/10.3390/nano11030646

APA StyleZhang, Q., Gu, J., Xu, R., Cao, L., Li, J., Wu, Z., Wang, G., Yao, J., Zhang, Z., Xiang, J., He, X., Kong, Z., Yang, H., Tian, J., Xu, G., Mao, S., Radamson, H. H., Yin, H., & Luo, J. (2021). Optimization of Structure and Electrical Characteristics for Four-Layer Vertically-Stacked Horizontal Gate-All-Around Si Nanosheets Devices. Nanomaterials, 11(3), 646. https://doi.org/10.3390/nano11030646