Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD

Abstract

:1. Introduction

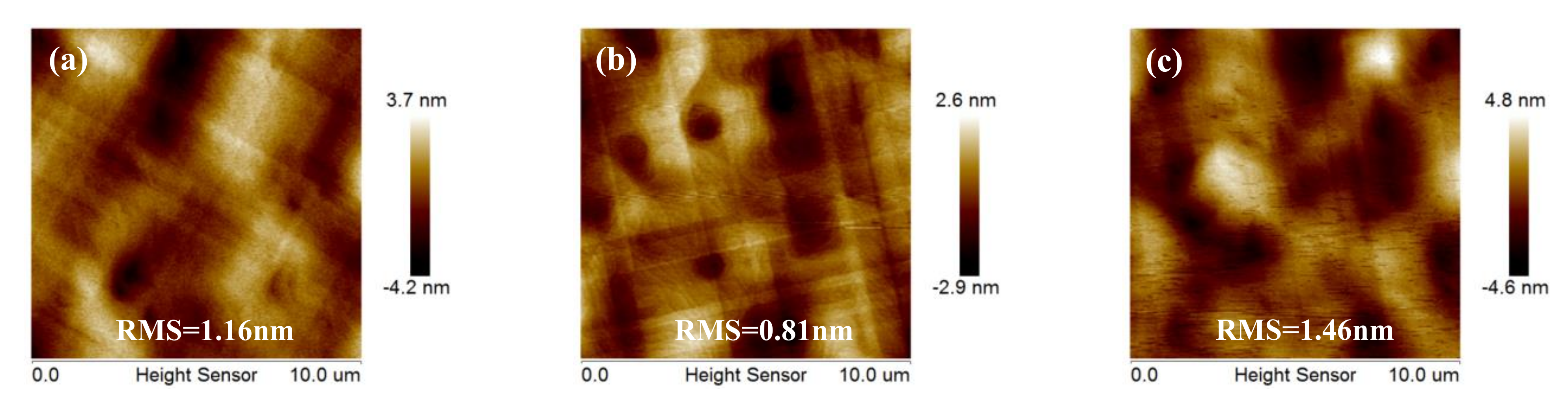

2. Materials and Methods

3. Results and Discussion

3.1. Initial Steps of Ge on Si

3.2. Optimization of LT-Ge Buffer Layer Thickness

3.3. Optimization of High Growth Temperature for Ge

3.4. Optimization of Thickness for the Quality of Ge

3.5. Optimization of Post Annealing Conditions

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhao, X.; Moeen, M.; Toprak, M.S.; Wang, G.; Luo, J.; Ke, X.; Li, Z.; Liu, D.; Wang, W.; Zhao, C.; et al. Design impact on the performance of Ge PIN photodetectors. J. Mater. Sci. Mater. Electron. 2019, 31, 18–25. [Google Scholar] [CrossRef]

- Feng, N.-N.; Feng, D.; Liao, S.; Wang, X.; Dong, P.; Liang, H.; Kung, C.-C.; Qian, W.; Fong, J.; Shafiiha, R.; et al. 30GHz Ge electro-absorption modulator integrated with 3μm silicon-on-insulator waveguide. Opt. Express 2011, 19, 7062–7067. [Google Scholar] [CrossRef] [PubMed]

- Hartmann, J.M.; Abbadie, A.; Papon, A.M.; Holliger, P.; Rolland, G.; Billon, T.; Fédéli, J.M.; Rouvière, M.; Vivien, L.; Laval, S. Reduced pressure–chemical vapor deposition of Ge thick layers on Si(001) for 1.3–1.55-μm photodetection. J. Appl. Phys. 2004, 95, 5905–5913. [Google Scholar] [CrossRef]

- Radamson, H.; Thylén, L. Monolithic Nanoscale Photonics–Electronics Integration in Silicon and Other Group IV Elements; Elsevier BV: Amsterdam, The Netherlands, 2015; ISBN 978–012–419–975–0. [Google Scholar]

- Chaisakul, P.; Marris-Morini, D.; Frigerio, J.; Chrastina, D.; Rouifed, M.-S.; Cecchi, S.; Crozat, P.; Isella, G.; Vivien, L. Integrated germanium optical interconnects on silicon substrates. Nat. Photon 2014, 8, 482–488. [Google Scholar] [CrossRef]

- Radamson, H.H.; Zhang, Y.; He, X.; Cui, H.; Li, J.; Xiang, J.; Liu, J.; Gu, S.; Wang, G. The Challenges of Advanced CMOS Process from 2D to 3D. Appl. Sci. 2017, 7, 1047. [Google Scholar] [CrossRef]

- Radamson, H.H.; Zhu, H.; Wu, Z.; He, X.; Lin, H.; Liu, J.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; et al. State of the Art and Future Perspectives in Advanced CMOS Technology. Nanomaterials 2020, 10, 1555. [Google Scholar] [CrossRef]

- Wang, G.; Kolahdouz, M.; Luo, J.; Qin, C.; Gu, S.; Kong, Z.; Yin, X.; Xiong, W.; Zhao, X.; Liu, J.; et al. Growth of SiGe layers in source and drain regions for 10 nm node complementary metal-oxide semiconductor (CMOS). J. Mater. Sci. Mater. Electron. 2019, 31, 26–33. [Google Scholar] [CrossRef]

- Saraswat, K.; Chui, C.O.; Krishnamohan, T.; Kim, D.; Nayfeh, A.; Pethe, A. High performance germanium MOSFETs. Mater. Sci. Eng. B 2006, 135, 242–249. [Google Scholar] [CrossRef]

- Radamson, H.H.; Kolahdouz, M. Selective epitaxy growth of Si1−xGex layers for MOSFETs and FinFETs. J. Mater. Sci. Mater. Electron. 2015, 26, 4584–4603. [Google Scholar] [CrossRef]

- CorClaeys, C.; Simoen, E. Germanium-Based Technologies: From Materials to Devices; Elsevier BV: Amsterdam, The Netherlands, 2017; ISBN 9780080449531. [Google Scholar]

- Radamson, H.H.; Simoen, E.; Luo, J.; Zhao, C. Past, Present and Future of CMOS; Elsevier, Ltd.: Amsterdam, The Netherlands, 2018; pp. 95–114. ISBN 978-008-102-139-2. [Google Scholar]

- Wang, X.; Xiang, J.; Han, K.; Wang, S.; Luo, J.; Zhao, C.; Ye, T.; Radamson, H.H.; Simoen, E.; Wang, W. Physically Based Evaluation of Effect of Buried Oxide on Surface Roughness Scattering Limited Hole Mobility in Ultrathin GeOI MOSFETs. IEEE Trans. Electron Devices 2017, 64, 1–6. [Google Scholar] [CrossRef]

- Abouzaid, O.; Mehdi, H.; Martin, M.; Moeyaert, J.; Salem, B.; David, S.; Souifi, A.; Chauvin, N.; Hartmann, J.-M.; Ilahi, B.; et al. O-Band Emitting InAs Quantum Dots Grown by MOCVD On A 300 mm Ge-Buffered Si (001) Substrate. Nanomaterials 2020, 10, 2450. [Google Scholar] [CrossRef]

- Xiong, W.; Wang, G.; Du, Y.; Lin, H.; Zhao, X.; Yu, J.; Kong, Z.; Dong, Y.; Jiang, H.; Tao, Y.; et al. Integration of silicon nitride waveguide in Ge-on-insulator substrates for monolithic solutions in optoelectronics. J. Mater. Sci. Mater. Electron. 2021, 32, 6133–6140. [Google Scholar] [CrossRef]

- Bogumilowicz, Y.; Hartmann, J.; Rochat, N.; Salaun, A.; Martin, M.; Bassani, F.; Baron, T.; David, S.; Bao, X.-Y.; Sanchez, E. Threading dislocations in GaAs epitaxial layers on various thickness Ge buffers on 300 mm Si substrates. J. Cryst. Growth 2016, 453, 180–187. [Google Scholar] [CrossRef]

- Merckling, C.; Waldron, N.; Jiang, S.; Guo, W.; Richard, O.; Douhard, B.; Moussa, A.; Vanhaeren, D.; Bender, H.; Collaert, N.; et al. Selective area growth of InP in shallow trench isolation on large scale Si(001) wafer using defect confinement technique. J. Appl. Phys. 2013, 114, 033708. [Google Scholar] [CrossRef]

- Alharthi, B.; Dou, W.; Grant, P.C.; Grant, J.M.; Morgan, T.; Mosleh, A.; Li, B.; Mortazavi, M.; Naseem, H.; Yu, S.-Q. Low temperature epitaxy of high-quality Ge buffer using plasma enhancement via UHV-CVD system for photonic device applications. Appl. Surf. Sci. 2019, 481, 246–254. [Google Scholar] [CrossRef]

- Michel, J.; Liu, J.; Kimerling, L.C. High-performance Ge-on-Si photodetectors. Nat. Photon. 2010, 4, 527–534. [Google Scholar] [CrossRef]

- Halbwax, M.; Rouviere, M.; Zheng, Y.; Débarre, D.; Nguyen, L.H.; Cercus, J.-L.; Clerc, C.; Yam, V.; Laval, S.; Cassan, E.; et al. UHV-CVD growth and annealing of thin fully relaxed Ge films on (001)Si. Opt. Mater. 2005, 27, 822–826. [Google Scholar] [CrossRef]

- Yoon, T.-S.; Liu, J.; Noori, A.M.; Goorsky, M.S.; Xie, Y.-H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Appl. Phys. Lett. 2005, 87, 12104. [Google Scholar] [CrossRef]

- Bogumilowicz, Y.; Hartmann, J.; Di Nardo, C.; Holliger, P.; Papon, A.-M.; Rolland, G.; Billon, T. High-temperature growth of very high germanium content SiGe virtual substrates. J. Cryst. Growth 2006, 290, 523–531. [Google Scholar] [CrossRef]

- Yamamoto, Y.; Zaumseil, P.; Schubert, M.A.; Tillack, B. Influence of annealing conditions on threading dislocation density in Ge deposited on Si by reduced pressure chemical vapor deposition. Semicond. Sci. Technol. 2018, 33, 124007. [Google Scholar] [CrossRef]

- Yamamoto, Y.; Corley, C.; Schubert, M.A.; Zoellner, M.; Tillack, B. Threading Dislocation Reduction of Ge by Introducing a SiGe/Ge Superlattice. ECS J. Solid State Sci. Technol. 2021, 10, 034005. [Google Scholar] [CrossRef]

- Tao, K.; Wang, J.; Jiang, S.; Jia, R.; Jin, Z.; Liu, X. High-quality Ge-rich SiGe thin films epitaxially grown on Si at low temperature by a two-step approach. CrystEngComm 2019, 21, 6623–6629. [Google Scholar] [CrossRef]

- Nayfeh, A.; Chui, C.O.; Saraswat, K.C.; Yonehara, T. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Appl. Phys. Lett. 2004, 85, 2815–2817. [Google Scholar] [CrossRef] [Green Version]

- Miao, Y.-H.; Hu, H.-Y.; Li, X.; Song, J.-J.; Xuan, R.-X.; Zhang, H.-M. Evaluation of threading dislocation density of strained Ge epitaxial layer by high resolution x-ray diffraction. Chin. Phys. B 2017, 26, 127309. [Google Scholar] [CrossRef]

- Kim, H.-W.; Shin, K.W.; Lee, G.-D.; Yoon, E. High quality Ge epitaxial layers on Si by ultrahigh vacuum chemical vapor deposition. Thin Solid Films 2009, 517, 3990–3994. [Google Scholar] [CrossRef]

- Sakai, A.; Tatsumi, T. Ge growth on Si using atomic hydrogen as a surfactant. Appl. Phys. Lett. 1994, 64, 52–54. [Google Scholar] [CrossRef]

- Hartmann, J.; Damlencourt, J.-F.; Bogumilowicz, Y.; Holliger, P.; Rolland, G.; Billon, T. Reduced pressure-chemical vapor deposition of intrinsic and doped Ge layers on Si(001) for microelectronics and optoelectronics purposes. J. Cryst. Growth 2005, 274, 90–99. [Google Scholar] [CrossRef]

- Tan, Y.; Tan, C. Growth and characterization of germanium epitaxial film on silicon (001) using reduced pressure chemical vapor deposition. Thin Solid Films 2012, 520, 2711–2716. [Google Scholar] [CrossRef]

- Lee, K.H.; Bao, S.; Chong, G.Y.; Tan, Y.H.; Fitzgerald, E.A.; Tan, C.S. Defects reduction of Ge epitaxial film in a germanium-on-insulator wafer by annealing in oxygen ambient. APL Mater. 2015, 3, 016102. [Google Scholar] [CrossRef]

- Hartmann, J.; Abbadie, A.; Barnes, J.; Fédéli, J.; Billon, T.; Vivien, L. Impact of the H2 anneal on the structural and optical properties of thin and thick Ge layers on Si; Low temperature surface passivation of Ge by Si. J. Cryst. Growth 2010, 312, 532–541. [Google Scholar] [CrossRef]

- Hartmann, J.; Aubin, J. Assessment of the growth/etch back technique for the production of Ge strain-relaxed buffers on Si. J. Cryst. Growth 2018, 488, 43–50. [Google Scholar] [CrossRef]

- Wang, G.; Luo, J.; Qin, C.; Liang, R.; Xu, Y.; Liu, J.; Li, J.; Yin, H.; Yan, J.; Zhu, H.; et al. Integration of Highly Strained SiGe in Source and Drain with HK and MG for 22 nm Bulk PMOS Transistors. Nanoscale Res. Lett. 2017, 12, 1–7. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Wang, G. Investigation on SiGe Selective Epitaxy for Source and Drain Engineering in 22 nm CMOS Technology Node and Beyond; Metzler, J.B., Ed.; Springer: Singapore, 2019; Volume 9, ISBN 978-981-15-0045-9. [Google Scholar]

- Shin, K.W.; Kim, H.-W.; Kim, J.; Yang, C.; Lee, S.; Yoon, E. The effects of low temperature buffer layer on the growth of pure Ge on Si(001). Thin Solid Films 2010, 518, 6496–6499. [Google Scholar] [CrossRef]

- Ni, W.-X.; Ekberg, J.; Joelsson, K.; Radamson, H.; Henry, A.; Shen, G.-D.; Hansson, G. A silicon molecular beam epitaxy system dedicated to device-oriented material research. J. Cryst. Growth 1995, 157, 285–294. [Google Scholar] [CrossRef]

- Ayers, J. The measurement of threading dislocation densities in semiconductor crystals by X-ray diffraction. J. Cryst. Growth 1994, 135, 71–77. [Google Scholar] [CrossRef]

- Hansson, G.V.; Radamsson, H.H.; Ni, W.-X. Strain and relaxation in Si-MBE structures studied by reciprocal space mapping using high resolution X-ray diffraction. J. Mater. Sci. Mater. Electron. 1995, 6, 292–297. [Google Scholar] [CrossRef]

- Wang, T.; Zhang, Y.-W.; Chua, S. Dislocation evolution in epitaxial multilayers and graded composition buffers. Acta Mater. 2001, 49, 1599–1605. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Du, Y.; Kong, Z.; Toprak, M.S.; Wang, G.; Miao, Y.; Xu, B.; Yu, J.; Li, B.; Lin, H.; Han, J.; et al. Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD. Nanomaterials 2021, 11, 928. https://doi.org/10.3390/nano11040928

Du Y, Kong Z, Toprak MS, Wang G, Miao Y, Xu B, Yu J, Li B, Lin H, Han J, et al. Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD. Nanomaterials. 2021; 11(4):928. https://doi.org/10.3390/nano11040928

Chicago/Turabian StyleDu, Yong, Zhenzhen Kong, Muhammet S. Toprak, Guilei Wang, Yuanhao Miao, Buqing Xu, Jiahan Yu, Ben Li, Hongxiao Lin, Jianghao Han, and et al. 2021. "Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD" Nanomaterials 11, no. 4: 928. https://doi.org/10.3390/nano11040928

APA StyleDu, Y., Kong, Z., Toprak, M. S., Wang, G., Miao, Y., Xu, B., Yu, J., Li, B., Lin, H., Han, J., Dong, Y., Wang, W., & Radamson, H. H. (2021). Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD. Nanomaterials, 11(4), 928. https://doi.org/10.3390/nano11040928